# High Performance, Polyphase Energy Metering AFE

Data Sheet ADE9078

#### **FEATURES**

7 high performance analog-to-digital converters (ADCs)

101 dB signal-to-noise ratio (SNR)

10,000:1 dynamic range

Wide input range: ±1 V, 0.707 V rms full scale

Differential inputs

±25 ppm/°C maximum channel temperature drift (including ADC, internal V<sub>REF</sub>, and PGA drift) enabling Class 0.2 meters with standard external components

**Power quality measurements**

Line frequency: 1 measurement per phase Zero crossing detection, zero-crossing timeout Phase angle measurements

Supports current transformers (CTs) and Rogowski coil (di/dt) sensors

Multiple range phase/gain compensation for CTs Digital integrator for Rogowski coils

Flexible waveform buffer

Advanced metrology feature set

Able to resample waveform to ensure 64 points per line cycle for ease of external harmonic analysis

Events can trigger waveform storage

Simplifies data collection for IEC 61000-4-7 harmonic analysis

Total active power, volt-amperes reactive (VAR), voltamperes (VA), watthour, VAR-hour, and VA-hour Fundamental VAR and VAR-hour Current and voltage rms per phase (xIRMS, xVRMS) Supports active energy standards: IEC 62053-21,

IEC 62053-22; EN50470-3; OIML R46, ANSI C12.20

Supports reactive energy standards: IEC 62053-23, IEC 62053-4

High speed communication port 10 MHz serial peripheral interface (SPI)

#### **APPLICATIONS**

Polyphase meters

Power quality monitoring

Protective device

#### **GENERAL DESCRIPTION**

The ADE9078<sup>1</sup> is a highly accurate, fully integrated energy metering device. Interfacing with both current transformer (CT) and Rogowski coil sensors, the ADE9078 enables users to develop a 3-phase metrology platform, which achieves high performance for Class 1 up to Class 0.2 meters.

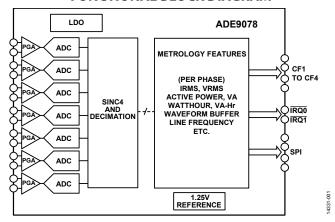

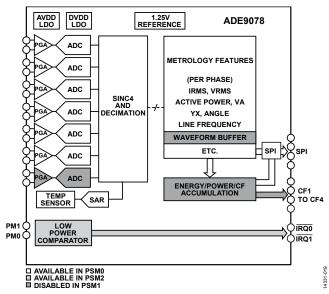

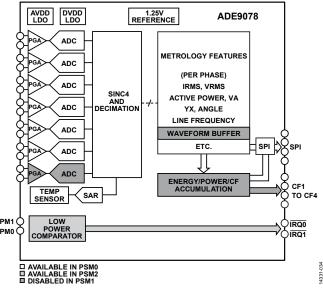

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

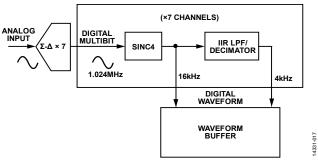

The ADE9078 integrates seven high performances ADCs and a flexible DSP core. An integrated high end reference ensures low drift over temperature with a combined drift of less than ±25 ppm/°C maximum per channel, each of which includes a programmable gain amplifier (PGA) and ADC.

The ADE9078 offers an integrated flexible waveform buffer that stores samples at a fixed data rate or a sampling rate that varies based on line frequency to ensure 64 points per line cycle. These two options make it easy to implement harmonic analysis in an external processor according to IEC 61000-4-7.

Two power modes are provided to enable detection of meter tampering: PSM2 uses a low power comparator to compare current channels to a threshold and indicates whether it is exceeded on the  $\overline{IRQ0}$  and  $\overline{IRQ1}$  outputs; PSM1 enables fast measurement of current and voltage rms (xVRMS and xIRMS), active power, and VAR during a tamper.

The ADE9078 allows advanced and highly accurate energy measurements, enabling one platform to cover a wide range of meters, through a combination of various high end metrology features and superior analog performance.

$<sup>^{1}\</sup> Protected\ by\ U.S.\ Patents\ 5,952,849;\ 6,873,065;\ 7,075,329;\ 6,262,600;\ 7,489,526;\ 7,558,080.\ Other\ patents\ are\ pending.$

# **TABLE OF CONTENTS**

| Features                                                                     | 1            |

|------------------------------------------------------------------------------|--------------|

| Applications                                                                 | 1            |

| General Description                                                          | 1            |

| Functional Block Diagram                                                     | 1            |

| Revision History                                                             | 3            |

| Specifications                                                               | 4            |

| Timing Characteristics                                                       | 7            |

| Absolute Maximum Ratings                                                     | 9            |

| Thermal Resistance                                                           | 9            |

| ESD Caution                                                                  | 9            |

| Pin Configuration and Function Descriptions                                  | . 10         |

| Typical Performance Characteristics                                          | . 12         |

| Total Energy Linearity over Supply and Temperature                           | . 12         |

| Fundamental Energy Linearity with Fifth Harmonic over Supply and Temperature | . 13         |

| Total Energy Error over Frequency                                            | . 14         |

| RMS Linearity over Temperature and RMS Error over Frequency                  |              |

| Energy Linearity Repeatability                                               |              |

| Total Energy and RMS Linearity with Integrator On                            |              |

| Total Energy Error over Frequency with Integrator On                         |              |

| Test Circuit                                                                 |              |

| Terminology                                                                  |              |

| Theory Of Operation                                                          |              |

| ADC                                                                          |              |

| Crystal Oscillator/External Clock                                            |              |

| Power Management                                                             |              |

| Measurements (Normal Mode)                                                   |              |

| Measurements (PSM1)                                                          |              |

| Measurements (PSM2)                                                          |              |

| Key Features                                                                 |              |

| Flexible Waveform Buffer with Resampling                                     |              |

| Multipoint Phase/Gain Calibration                                            |              |

| RMS of Sum of Instantaneous Currents Measurement                             |              |

| Tamper Modes                                                                 |              |

| 1                                                                            | . 55         |

| Power Hactor                                                                 | 55           |

| Power Factor                                                                 |              |

| Zero-Crossing Timeout Detection                                              | . 55         |

|                                                                              | . 55<br>. 55 |

| Quick Start                                                                  | 56  |

|------------------------------------------------------------------------------|-----|

| Applications Information                                                     |     |

| Non-Blondel Compliant Meters                                                 |     |

| Applying the ADE9078 to a 4-Wire Wye Service                                 |     |

| Applying the ADE9078 to a 3-Wire Delta Service                               |     |

|                                                                              |     |

| Applying the ADE9078 to a Non-Blondel Compliant, 4-W Wye Service             |     |

| Applying the ADE9078 to a Non-Blondel Compliant, 4-W Delta Service           |     |

| Service Type Summary                                                         | 60  |

| Accessing On-Chip Data                                                       | 62  |

| SPI Protocol Overview                                                        | 62  |

| SPI Write                                                                    | 63  |

| SPI Read                                                                     | 63  |

| SPI Burst Read                                                               | 63  |

| SPI Protocol CRC                                                             | 64  |

| Additional Communication Verification Registers                              | 64  |

| CRC of Configuration Registers                                               | 65  |

| Configuration Lock                                                           | 65  |

| Waveform Buffer                                                              | 66  |

| Fixed Data Rate Waveforms                                                    | 67  |

| Fixed Data Rate Waveforms Filling and Trigger-Based Modes                    | 68  |

| Resampled Waveforms                                                          | 70  |

| Configuring the Waveform Buffer                                              | 70  |

| Burst Read Waveform Buffer Samples from SPI                                  | 71  |

| Interrupts/Events                                                            | 74  |

| Interrupts (IRQ0 and IRQ1)                                                   | 74  |

| EVENT                                                                        | 74  |

| Status Bits in Additional Registers                                          | 74  |

| Troubleshooting                                                              | 75  |

| SPI Does Not Work                                                            | 75  |

| PSM2_CFG Register Value Is Not Retained When Going from PSM2 or PSM3 to PSM0 | 75  |

| Register Information                                                         | 76  |

| Register Details                                                             | 88  |

| Outline Dimensions                                                           | 107 |

| Ordering Guide                                                               | 107 |

# **REVISION HISTORY**

8/2016—Revision 0: Initial Version

# **SPECIFICATIONS**

$V_{DD}$  = 2.7 V to 3.63 V, GND = AGND = DGND = 0 V, on-chip reference, CLKIN = 12.288 MHz crystal (XTAL),  $T_{MIN}$  to  $T_{MAX}$  = -40°C to +85°C for minimum and maximum specifications,  $T_A$  = 25°C (typical) for typical specifications.

Table 1.1

| Parameter                                                                              | Min Typ Max    | Unit    | Test Conditions/Comments                                                                                                                                                                                                                                                                            |

|----------------------------------------------------------------------------------------|----------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACCURACY                                                                               |                |         | Measurement error per phase                                                                                                                                                                                                                                                                         |

| Total Active Energy                                                                    | 0.1            | %       | Over a dynamic range of 5000 to 1, 10 sec accumulation; gain compensation only                                                                                                                                                                                                                      |

|                                                                                        | 0.2            | %       | Over a dynamic range of 10,000 to 1, 20 sec accumulation; gain compensation only                                                                                                                                                                                                                    |

| Total Reactive Energy                                                                  | 0.1            | %       | Over a dynamic range of 5000 to 1, 10 sec accumulation; gain compensation only                                                                                                                                                                                                                      |

|                                                                                        | 0.2            | %       | Over a dynamic range of 10,000 to 1, 20 sec accumulation; gain compensation only                                                                                                                                                                                                                    |

| Total Apparent Energy                                                                  | 0.1            | %       | Over a dynamic range of 1000 to 1, 2 sec accumulation                                                                                                                                                                                                                                               |

|                                                                                        | 0.5            | %       | Over a dynamic range of 5000 to 1, 10 sec accumulation                                                                                                                                                                                                                                              |

| Fundamental Reactive                                                                   | 0.1            | %       | Over a dynamic range of 5000 to 1, 2 sec accumulation                                                                                                                                                                                                                                               |

|                                                                                        | 0.2            | %       | Over a dynamic range of 10,000 to 1, 20 sec accumulation                                                                                                                                                                                                                                            |

| IRMS, VRMS                                                                             | 0.1            | %       | Over a dynamic range of 1000 to 1                                                                                                                                                                                                                                                                   |

|                                                                                        | 0.5            | %       | Over a dynamic range of 5000 to 1                                                                                                                                                                                                                                                                   |

| Active Power, VAR                                                                      | 0.2            | %       | Over a dynamic range of 5000 to 1, 1 sec accumulation                                                                                                                                                                                                                                               |

| Power Factor (PF)                                                                      | ±0.001         |         | Over a dynamic range of 5000 to 1                                                                                                                                                                                                                                                                   |

| 64-Point per Line Cycle<br>Resampled Data                                              | 0.1            | %       | An FFT is performed to receive the magnitude response; this error is the worst case error in the fundamental magnitude caused by resampling algorithm distortion; input signal is 50 Hz fundamental on voltage channel and fundamental with ninth harmonic at half of full scale on current channel |

|                                                                                        | 0.3            | %       | An FFT is performed to receive the magnitude response; this error is the magnitude error of ninth harmonic caused by the resampling algorithm distortion input signal is 50 Hz fundamental with ninth harmonic at half of full scale on current channel                                             |

|                                                                                        | <del>-72</del> | dB      | Amplitude of highest spur; input signal is 50 Hz fundamental and ninth harmonic at half of full scale on the current channel                                                                                                                                                                        |

|                                                                                        | 3              | %       | An FFT is performed to receive the magnitude response; this error is the magnitude error of 31st harmonic caused by resampling algorithm distortion; input signal is 50 Hz fundamental with 31st harmonic at half of full scale on the current channel                                              |

|                                                                                        | -38            | dB      | Amplitude of highest spur; input signal is 50 Hz fundamental and 31st harmonic at half of full scale on the current channel                                                                                                                                                                         |

| Line Period Measurement                                                                | 0.001          | Hz      | Resolution at 50 Hz                                                                                                                                                                                                                                                                                 |

| Current to Current, Voltage to<br>Voltage, and Voltage to<br>Current Angle Measurement | 0.036          | Degrees | Resolution at 50 Hz; voltage and current at 1/10 <sup>th</sup> of full scale                                                                                                                                                                                                                        |

| PSM1 IRMS                                                                              | 0.2            | %       | Accuracy achieved 40 ms after entering PSM1 mode at 600:1                                                                                                                                                                                                                                           |

Rev. 0 | Page 4 of 107

| Parameter                                                                     | Min     | Тур        | Max     | Unit   | Test Conditions/Comments                                                                               |

|-------------------------------------------------------------------------------|---------|------------|---------|--------|--------------------------------------------------------------------------------------------------------|

| PSM1 Active Power                                                             |         | 0.2        |         | %      | Accuracy achieved 40 ms after entering PSM1 mode at 600:1                                              |

| PSM2 Peak Current Detection                                                   |         | 5          |         | %      | Accuracy of current detection threshold, achieved 120 ms after entering PSM2 mode at 660:1             |

| ADC                                                                           |         |            |         |        | See the ADC section                                                                                    |

| PGA Gain Settings (GAIN)                                                      |         | 1, 2, or 4 |         | V/V    | PGA gain setting is referred to as GAIN                                                                |

| Differential Input Voltage Range<br>(VxP – VxN, IxP – IxN)                    | -1/GAIN |            | +1/GAIN | V      | $0.707 \text{ V rms}$ ; when $V_{REF} = 1.25 \text{ V}$ , this voltage corresponds to 53 million codes |

| Maximum Operating Voltage on<br>Analog Input Pins (VxP, VxN,<br>IxP, and IxN) | -0.6    |            | 0.6     | V      | Voltage on the pin with respect to ground (GND = AGND = DGND = REFGND), $V_{REF}$ = 1.25 V             |

| Signal-to-Noise Ratio (SNR) <sup>2</sup>                                      |         |            |         |        | $V_{IN}$ = full scale/gain; see the Terminology section                                                |

| PGA = 1                                                                       |         | 101        |         | dB     | 4 kSPS sinc4 + infinite impulse response<br>(IIR) low-pass filter (LPF) output                         |

|                                                                               |         | 97         |         | dB     | 16 kSPS sinc4 output                                                                                   |

| PGA = 4                                                                       |         | 97         |         | dB     | 4 kSPS sinc4 + IIR LPF output                                                                          |

|                                                                               |         | 94         |         | dB     | 16 kSPS sinc4 output                                                                                   |

| Total Harmonic Distortion (THD) <sup>2</sup>                                  |         |            |         |        | See the Terminology section                                                                            |

| PGA = 1                                                                       |         | -106       |         | dB     | 4 kSPS sinc4 + IIR LPF output                                                                          |

|                                                                               |         | -106       |         | dB     | 16 kSPS sinc4 output                                                                                   |

| PGA = 4                                                                       |         | -115       |         | dB     | 4 kSPS sinc4 + IIR LPF output                                                                          |

|                                                                               |         | -112       |         | dB     | 16 kSPS sinc4 output                                                                                   |

| Signal-to-Noise and Distortion<br>Ratio (SINAD) <sup>2</sup>                  |         |            |         |        | See the Terminology section                                                                            |

| PGA = 1                                                                       |         | 100        |         | dB     | 4 kSPS sinc4 + IIR LPF output                                                                          |

|                                                                               |         | 96         |         | dB     | 16 kSPS sinc4 output                                                                                   |

| PGA = 4                                                                       |         | 96         |         | dB     | 4 kSPS sinc4 + IIR LPF output                                                                          |

|                                                                               |         | 93         |         | dB     | 16 kSPS sinc4 output                                                                                   |

| Spurious-Free Dynamic Range<br>(SFDR) <sup>2</sup>                            |         |            |         |        | See the Terminology section                                                                            |

| PGA = 1                                                                       |         | 110        |         | dB     | 4 kSPS sinc4 + IIR LPF output                                                                          |

| Output Pass Band (-0.1 dB)                                                    |         |            |         |        | See the Terminology section                                                                            |

| Sinc4 Outputs                                                                 |         | 0.672      |         | kHz    | 16 kSPS sinc4 output                                                                                   |

| Sinc4 + IIR LPF Outputs                                                       |         | 0.672      |         | kHz    | 4 kSPS output                                                                                          |

| Output Bandwidth (-3 dB) <sup>2</sup>                                         |         |            |         |        | See the Terminology section                                                                            |

| Sinc4 Outputs                                                                 |         | 3.6325     |         | kHz    | 16 kSPS sinc4 output                                                                                   |

| Sinc4 + IIR LPF Outputs                                                       |         | 1.6        |         | kHz    | 4 kSPS output                                                                                          |

| Crosstalk <sup>2</sup>                                                        |         | -120       |         | dB     | See the Terminology section, at 50 Hz and 60 Hz                                                        |

| AC Power Supply Rejection<br>Ratio (AC PSRR) <sup>2</sup>                     |         | -120       |         | dB     | See the Terminology section, at 50 Hz and 60 Hz                                                        |

| AC Common-Mode Rejection<br>Ratio (AC CMRR) <sup>2</sup>                      |         | -115       |         | dB     | At 100 Hz and 120 Hz                                                                                   |

| Gain Error                                                                    |         | ±0.3       | ±1      | %      | See the Terminology section                                                                            |

| Gain Drift <sup>2</sup>                                                       |         | ±3         |         | ppm/°C | See the Terminology section                                                                            |

| Offset                                                                        |         | ±0.36      | ±3.8    | mV     | See the Terminology section                                                                            |

| Offset Drift <sup>2</sup>                                                     |         | 0          | ±6      | μV/°C  | See the Terminology section                                                                            |

| Parameter                                                                    | Min    | Тур       | Max    | Unit   | Test Conditions/Comments                                                                                                                                                     |

|------------------------------------------------------------------------------|--------|-----------|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Channel Drift (PGA, ADC,<br>Internal Voltage Reference)                      |        | ±7        | ±25    | ppm/°C | PGA = 1, internal V <sub>REF</sub>                                                                                                                                           |

|                                                                              |        | ±7        | ±25    | ppm/°C | PGA = 2, internal V <sub>REF</sub>                                                                                                                                           |

|                                                                              |        | ±7        | ±25    | ppm/°C | PGA = 4, internal V <sub>REF</sub>                                                                                                                                           |

| Differential Input Impedance (DC)                                            | 330    | 366       |        | kΩ     | See the Terminology section, PGA = 1                                                                                                                                         |

|                                                                              | 160    | 180       |        | kΩ     | PGA = 2                                                                                                                                                                      |

|                                                                              | 80     | 90        |        | kΩ     | PGA = 4                                                                                                                                                                      |

| INTERNAL VOLTAGE REFERENCE                                                   |        |           |        |        | Nominal 1.25 V ±1 mV                                                                                                                                                         |

| Voltage Reference                                                            |        | 1.250     |        | V      | T <sub>A</sub> = 25°C, REF pin                                                                                                                                               |

| Temperature Coefficient <sup>2</sup>                                         |        | ±5        | ±20    | ppm/°C | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                                                                                                                                |

| EXTERNAL VOLTAGE REFERENCE                                                   |        |           |        |        |                                                                                                                                                                              |

| External Voltage Reference Input<br>Voltage (REF)                            |        | 1.2, 1.25 |        | V      | REFGND must be tied to GND, AGND, and DGND; 1.25 V external reference is preferred; the full-scale values mentioned in this data sheet are for a voltage reference of 1.25 V |

| Average Reference Current                                                    |        | 120       |        | μA/V   |                                                                                                                                                                              |

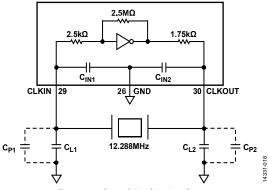

| CRYSTAL OSCILLATOR                                                           |        |           |        |        | CLKIN = 12.288 MHz ± 30 ppm (see the Crystal Oscillator/External Clock section)                                                                                              |

| Input Clock Frequency                                                        | 12.165 | 12.288    | 12.411 | MHz    |                                                                                                                                                                              |

| Internal Capacitance on CLKIN<br>and CLKOUT                                  |        | 4         |        | pF     |                                                                                                                                                                              |

| Internal Feedback Resistance<br>Between CLKIN and CLKOUT                     |        | 2.5       |        | ΜΩ     |                                                                                                                                                                              |

| Transconductance (g <sub>m</sub> )                                           |        | 9         |        | mA/V   |                                                                                                                                                                              |

| EXTERNAL CLOCK INPUT                                                         |        |           |        |        |                                                                                                                                                                              |

| Input Clock Frequency                                                        | 12.165 | 12.288    | 12.411 | MHz    |                                                                                                                                                                              |

| Duty Cycle <sup>2</sup>                                                      | 45:55  | 50:50     | 55:45  | %      |                                                                                                                                                                              |

| CLKIN Logic Inputs                                                           |        |           |        |        | 3.3 V tolerant                                                                                                                                                               |

| Input Voltage                                                                |        |           |        |        |                                                                                                                                                                              |

| High, V <sub>INH</sub>                                                       | 1.2    |           |        | V      | $V_{DD} = 2.7 \text{ V to } 3.63 \text{ V}$                                                                                                                                  |

| Low, V <sub>INL</sub>                                                        |        |           | 0.5    | V      | $V_{DD} = 2.7 \text{ V to } 3.63 \text{ V}$                                                                                                                                  |

| LOGIC INPUTS                                                                 |        |           |        |        |                                                                                                                                                                              |

| PM0, PM1, $\overline{\text{RESET}}$ , MOSI, SCLK, and $\overline{\text{SS}}$ |        |           |        |        |                                                                                                                                                                              |

| Input Voltage                                                                |        |           |        |        |                                                                                                                                                                              |

| High, V <sub>INH</sub>                                                       | 2.4    |           |        | V      | $V_{DD} = 2.7 \text{ V to } 3.63 \text{ V}$                                                                                                                                  |

| Low, V <sub>INL</sub>                                                        |        |           | 0.8    | V      | $V_{DD} = 2.7 \text{ V to } 3.63 \text{ V}$                                                                                                                                  |

| Input Current, I <sub>IN</sub>                                               |        |           | 15     | μΑ     | $V_{IN} = 0 V$                                                                                                                                                               |

| Internal Capacitance, C <sub>IN</sub>                                        |        |           | 10     | pF     |                                                                                                                                                                              |

| LOGIC OUTPUTS                                                                |        |           |        |        |                                                                                                                                                                              |

| MISO, $\overline{IRQ0}$ , and $\overline{IRQ1}$                              |        |           |        |        | $V_{DD} = 2.97 \text{ V to } 3.63 \text{ V}$                                                                                                                                 |

| Output Voltage                                                               |        |           |        |        |                                                                                                                                                                              |

| High, V <sub>он</sub>                                                        | 2.4    |           |        | V      | I <sub>SOURCE</sub> = 4 mA                                                                                                                                                   |

| Low, V <sub>OL</sub>                                                         |        |           | 0.8    | V      | $I_{SINK} = 4 \text{ mA}$                                                                                                                                                    |

| Internal Capacitance, C <sub>IN</sub>                                        |        |           | 10     | pF     |                                                                                                                                                                              |

| CF1, CF2, CF3, and CF4                                                       |        |           |        | [ ]    | $V_{DD} = 2.97 \text{ V to } 3.63 \text{ V}$                                                                                                                                 |

| Output Voltage                                                               |        |           |        |        |                                                                                                                                                                              |

| High, V <sub>он</sub>                                                        | 2.4    |           |        | V      | $I_{SOURCE} = 8 \text{ mA}$                                                                                                                                                  |

| Low, V <sub>OL</sub>                                                         |        |           | 0.8    | V      | $I_{SINK} = 8 \text{ mA}$                                                                                                                                                    |

| Internal Capacitance, C <sub>IN</sub>                                        |        |           | 10     | pF     |                                                                                                                                                                              |

| Parameter                                       | Min | Тур  | Max  | Unit | Test Conditions/Comments                                                                       |

|-------------------------------------------------|-----|------|------|------|------------------------------------------------------------------------------------------------|

| LOGIC OUTPUTS                                   |     |      |      |      |                                                                                                |

| MISO, $\overline{IRQ0}$ , and $\overline{IRQ1}$ |     |      |      |      | $V_{DD} = 2.7 \text{ V}$                                                                       |

| Output Voltage                                  |     |      |      |      |                                                                                                |

| High, V <sub>он</sub>                           | 2.4 |      |      | V    | I <sub>SOURCE</sub> = 1 mA                                                                     |

| Low, V <sub>OL</sub>                            |     |      | 0.8  | V    | I <sub>SINK</sub> = 4 mA                                                                       |

| CF1, CF2, CF3, and CF4                          |     |      |      |      | $V_{DD} = 2.7 \text{ V}$                                                                       |

| Output Voltage                                  |     |      |      |      |                                                                                                |

| High, V <sub>OH</sub>                           | 2.4 |      |      | V    | Isource = 3 mA                                                                                 |

| Low, V <sub>OL</sub>                            |     |      | 0.8  | V    | I <sub>SINK</sub> = 8 mA                                                                       |

| LOW DROPOUT REGULATORS (LDOs)                   |     |      |      |      |                                                                                                |

| AVDD                                            |     | 1.9  |      | V    | See the Power-On Sequence section                                                              |

| DVDD                                            |     | 1.7  |      | V    |                                                                                                |

| POWER SUPPLY                                    |     |      |      |      | For specified performance                                                                      |

| VDD                                             | 2.7 | 3.3  | 3.63 | V    |                                                                                                |

| Supply Current (VDD)                            |     |      |      |      | $V_{DD} = 3.63 \text{ V}$                                                                      |

| Power Save Mode 0 (PSM0)                        |     | 10   | 12   | mA   | Normal mode, seven ADCs enabled                                                                |

|                                                 |     | 9.5  | 11   | mA   | Normal mode, seven ADCs enabled, total reactive power computation disabled                     |

|                                                 |     | 10.5 | 12   | mA   | Normal mode, seven ADCs enabled, waveform buffer enabled                                       |

|                                                 |     | 10   | 11.6 | mA   | Normal mode, six ADCs enabled                                                                  |

| Power Save Mode 1 (PSM1)                        |     | 9    | 10.6 | mA   | Fast rms, active power, and total reactive power measurement within 30 ms for tamper detection |

| Power Save Mode 2 (PSM2)                        |     | 115  | 200  | μΑ   | Compares current to threshold, AVDD = $0 \text{ V}$ , DVDD = $0 \text{ V}$                     |

| Power Save Mode 3 (PSM3)                        |     | 50   | 200  | nA   | Idle, $AVDD = 0 V$ , $DVDD = 0 V$                                                              |

<sup>&</sup>lt;sup>1</sup> Throughout this data sheet, multifunction pins, such as CF3/ZX, are referred to either by the entire pin name or by a single function of the pin, for example, CF3, when only that function is relevant. <sup>2</sup> Tested during device characterization.

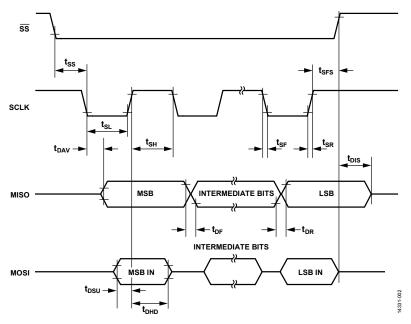

# **TIMING CHARACTERISTICS**

Table 2.

| Parameter                              | Symbol                  | Min 1 | Гур Мах | Unit |

|----------------------------------------|-------------------------|-------|---------|------|

| SS to SCLK Edge                        | t <sub>SS</sub>         | 10    |         | ns   |

| SCLK Frequency                         |                         |       | 10      | MHz  |

| SCLK Low Pulse Width                   | <b>t</b> s∟             | 40    |         | ns   |

| SCLK High Pulse Width                  | tsн                     | 40    |         | ns   |

| Data Output Valid After SCLK Edge      | t <sub>DAV</sub>        |       | 40      | ns   |

| Data Input Setup Time Before SCLK Edge | t <sub>DSU</sub>        | 10    |         | ns   |

| Data Input Hold Time After SCLK Edge   | <b>t</b> <sub>DHD</sub> | 10    |         | ns   |

| Data Output Fall Time                  | t <sub>DF</sub>         |       | 10      | ns   |

| Data Output Rise Time                  | t <sub>DR</sub>         |       | 10      | ns   |

| SCLK Fall Time                         | t <sub>SF</sub>         |       | 10      | ns   |

| SCLK Rise Time                         | <b>t</b> <sub>SR</sub>  |       | 10      | ns   |

| MISO Disable After SS Rising Edge      | t <sub>DIS</sub>        |       | 100     | ns   |

| SS High After SCLK Edge                | t <sub>SFS</sub>        | 0     |         | ns   |

Figure 2. SPI Interface Timing

# ABSOLUTE MAXIMUM RATINGS

$T_A = 25$ °C, unless otherwise noted.

Table 3.

| Parameter                                                                                    | Rating                                     |

|----------------------------------------------------------------------------------------------|--------------------------------------------|

| VDD to GND                                                                                   | −0.3 V to +3.96 V                          |

| Analog Input Voltage to GND,<br>IAP, IAN, IBP, IBN, ICP, ICN, VAP, VAN<br>VBP, VBN, VCP, VCN | -1.9 V to +2 V                             |

| Reference Input Voltage to REFGND                                                            | -0.3 V to +2 V                             |

| Digital Input Voltage to GND                                                                 | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| Digital Output Voltage to GND                                                                | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| Operating Temperature                                                                        |                                            |

| Industrial Range                                                                             | −40°C to +85°C                             |

| Storage Temperature Range                                                                    | −65°C to +150°C                            |

| Lead Temperature (Soldering, 10 sec) <sup>1</sup>                                            | 260°C                                      |

| ESD                                                                                          |                                            |

| Human Body Model <sup>2</sup>                                                                | 4 kV                                       |

| Machine Model <sup>3</sup>                                                                   | 200 V                                      |

| Field Induced Charged Device Model<br>(FICDM) <sup>4</sup>                                   | 1.25 kV                                    |

<sup>&</sup>lt;sup>1</sup> Analog Devices recommends that reflow profiles used in soldering RoHS compliant devices conform to J-STD-020D.1 from JEDEC. Refer to JEDEC for the latest revision of this standard.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment.

Careful attention to PCB thermal design is required.

**Table 4. Thermal Resistance**

| Package Type         | θ <sub>JA</sub> | θις  | Unit |

|----------------------|-----------------|------|------|

| CP-40-7 <sup>1</sup> | 27.14           | 3.13 | °C/W |

$<sup>^1</sup>$  Test Condition 1: The junction to air measurement uses a 2S2P JEDEC test board with 4  $\times$  4 standard JEDEC vias. The junction to case measurement uses a 1S0P JEDEC test board with 4  $\times$  4 standard JEDEC vias. See JEDEC standard JESD51-2.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>2</sup> Applicable standard: ANSI/ESDA/JEDEC JS-001-2014.

<sup>&</sup>lt;sup>3</sup> Applicable standard: JESD22-A115-A (ESD machine model standard of JEDEC).

$<sup>^{\</sup>rm 4}$  Applicable Standard JESD22-C101F (ESD FICDM standard of JEDEC).

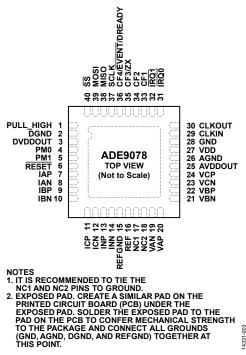

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

**Table 5. Pin Function Descriptions**

| Pin No. | Mnemonic  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | PULL_HIGH | Pull High. Tie this pin to VDD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2       | DGND      | Digital Ground. This pin provides the ground reference for the digital circuitry in the ADE9078. Because the digital return currents in the ADE9078 are small, it is acceptable to connect this pin to the analog ground plane of the whole system. Connect all grounds (GND, AGND, DGND, and REFGND) together at one point.                                                                                                                                                                                                                                               |

| 3       | DVDDOUT   | 1.8 V Output of the Digital Low Dropout Regulator (LDO). Decouple this pin with a 0.1 $\mu$ F ceramic capacitor in parallel with a ceramic 4.7 $\mu$ F capacitor.                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4       | PM0       | Power Mode Pin 0. PM0, combined with PM1, defines the power mode. For normal operation, PM0 and PM1 must be grounded (see the Power Modes section).                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5       | PM1       | Power Mode Pin 1. PM1 combined with PM0, defines the power mode. For normal operation, PM0 and PM1 must be grounded (see the Power Modes section).                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6       | RESET     | Reset Input, Active Low. This pin must stay low for at least 1 µs to trigger a hardware reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7, 8    | IAP, IAN  | Analog Inputs, Channel IA. The IAP (positive) and IAN (negative) inputs are fully differential voltage inputs with a maximum differential level of $\pm 1$ V. This channel also has an internal PGA of 1, 2, or 4.                                                                                                                                                                                                                                                                                                                                                         |

| 9, 10   | IBP, IBN  | Analog Inputs, Channel IB. The IBP (positive) and IBN (negative) inputs are fully differential voltage inputs with a maximum differential level of $\pm 1$ V. This channel also has an internal PGA of 1, 2, or 4.                                                                                                                                                                                                                                                                                                                                                         |

| 11, 12  | ICP, ICN  | Analog Inputs, Channel IC. The ICP (positive) and ICN (negative) inputs are fully differential voltage inputs with a maximum differential level of $\pm 1$ V. This channel also has an internal PGA of 1, 2, or 4.                                                                                                                                                                                                                                                                                                                                                         |

| 13, 14  | INP, INN  | Analog Inputs, Channel IN. The INP (positive) and INN (negative) inputs are fully differential voltage inputs with a maximum differential level of $\pm 1$ V. This channel also has an internal PGA of 1, 2, or 4.                                                                                                                                                                                                                                                                                                                                                         |

| 15      | REFGND    | Ground Reference, Internal Voltage Reference. Connect all grounds (GND, AGND, DGND, and REFGND) together at one point.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 16      | REF       | Voltage Reference. The REF pin provides access to the on-chip voltage reference. The on-chip reference has a nominal value of 1.25 V. An external reference of 1.2 V to 1.25 V can also be connected at this pin. In either case, decouple REF to REFGND with 0.1 $\mu$ F ceramic capacitor in parallel with a ceramic 4.7 $\mu$ F capacitor. After reset, the on-chip reference is enabled. To use the internal voltage reference with external circuits, a buffer is required. The full-scale values mentioned in this data sheet are for a voltage reference of 1.25 V. |

| 17      | NC1       | No Connection. It is recommended to tie this pin to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 18      | NC2       | No Connection. It is recommended to tie this pin to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Pin No. | Mnemonic         | Description                                                                                                                                                                                                                                                                                                                                                 |

|---------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19, 20  | VAN, VAP         | Analog Inputs, Channel VA. The VAP (positive) and VAN (negative) inputs are fully differential voltage inputs with a maximum differential level of $\pm 1$ V. This channel also has an internal PGA of 1, 2, or 4.                                                                                                                                          |

| 21, 22  | VBN, VBP         | Analog Inputs, Channel VB. The VBP (positive) and VBN (negative) inputs are fully differential voltage inputs with a maximum differential level of $\pm 1$ V. This channel also has an internal PGA of 1, 2, or 4.                                                                                                                                          |

| 23, 24  | VCN, VCP         | Analog Inputs, Channel VC. The VCP (positive) and VCN (negative) inputs are fully differential voltage inputs with a maximum differential level of $\pm 1$ V. This channel also has an internal PGA of 1, 2, or 4.                                                                                                                                          |

| 25      | AVDDOUT          | 1.9 V Output of the Analog Low Dropout Regulator (LDO). Decouple AVDDOUT with a 0.1 μF ceramic capacitor in parallel with a ceramic 4.7 μF capacitor. Do not connect external active circuitry to this pin.                                                                                                                                                 |

| 26      | AGND             | Analog Ground Reference. Connect all grounds (GND, AGND, DGND, and REFGND) together at one point.                                                                                                                                                                                                                                                           |

| 27      | VDD              | Supply Voltage. The VDD pin provides the supply voltage. Decouple VDD to GND with a ceramic 0.1 $\mu$ F capacitor in parallel with a ceramic 10 $\mu$ F capacitor.                                                                                                                                                                                          |

| 28      | GND              | Supply Ground Reference. Connect all grounds (GND, AGND, DGND, and REFGND) together at one point.                                                                                                                                                                                                                                                           |

| 29      | CLKIN            | Crystal/Clock Input. Connect a crystal across CLKIN and CLKOUT to provide a clock source. See the Crystal Selection section for details on choosing a suitable crystal. Alternatively, an external clock can be provided at this logic input.                                                                                                               |

| 30      | CLKOUT           | Crystal Output. Connect a crystal across CLKIN and CLKOUT to provide a clock source. When using CLKOUT to drive external circuits, connect an external buffer. When using an external clock on CLKIN, leave CLKOUT unconnected.                                                                                                                             |

| 31      | ĪRQ0             | Interrupt Request Output. This pin is an active low logic output. See the Interrupts/Events section for information about events that trigger interrupts.                                                                                                                                                                                                   |

| 32      | ĪRQ1             | Interrupt Request Output. This pin is an active low logic output. See the Interrupts/Events section for information about events that trigger interrupts.                                                                                                                                                                                                   |

| 33      | CF1              | Calibration Frequency (CF) Logic Output 1. The CF1, CF2, CF3, and CF4 outputs provide power information based on the CFxSEL bits in the CFMODE register. Use these outputs for operational and calibration purposes. Scale the full-scale output frequency by writing to the CFxDEN registers (see the Digital to Frequency Conversion—CFx Output section). |

| 34      | CF2              | CF Logic Output 2. This pin indicates CF2.                                                                                                                                                                                                                                                                                                                  |

| 35      | CF3/ZX           | CF Logic Output 3/Zero Crossing. This pin indicates CF3 or zero crossing.                                                                                                                                                                                                                                                                                   |

| 36      | CF4/EVENT/DREADY | CF Logic Output 4/Event Pin/Data Ready. This pin indicates CF4, events, or when new data is ready.                                                                                                                                                                                                                                                          |

| 37      | SCLK             | Serial Clock Input for the SPI Port. All serial data transfers synchronize to this clock (see the Accessing On-Chip Data section). The SCLK pin has a Schmitt trigger input for use with a clock source that has a slow edge transition time, for example, optoisolator outputs.                                                                            |

| 38      | MISO             | Data Output for the SPI Port.                                                                                                                                                                                                                                                                                                                               |

| 39      | MOSI             | Data Input for the SPI Port.                                                                                                                                                                                                                                                                                                                                |

| 40      | SS               | Slave Select for the SPI Port.                                                                                                                                                                                                                                                                                                                              |

|         | EP               | Exposed Pad. Create a similar pad on the printed circuit board (PCB) under the exposed pad. Solder the exposed pad to the pad on the PCB to confer mechanical strength to the package and connect all grounds (GND, AGND, DGND, and REFGND) together at this point.                                                                                         |

# TYPICAL PERFORMANCE CHARACTERISTICS

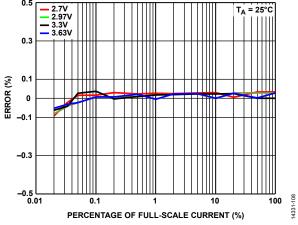

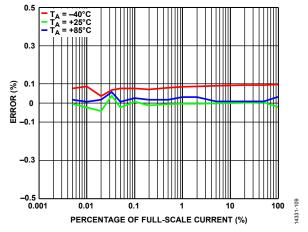

#### **TOTAL ENERGY LINEARITY OVER SUPPLY AND TEMPERATURE**

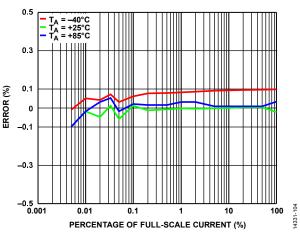

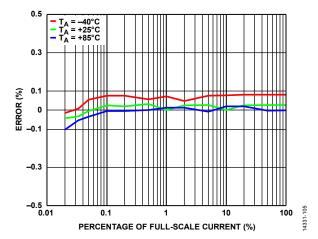

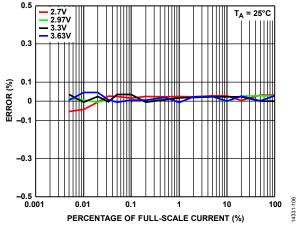

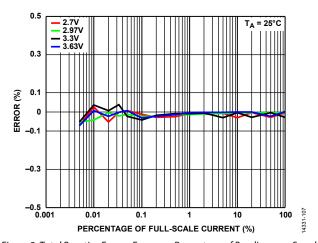

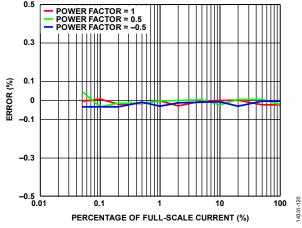

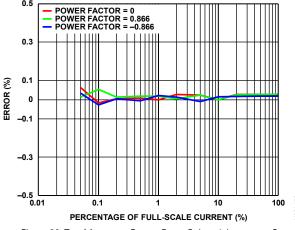

Sinusoidal voltage with an amplitude of 50% of full scale and a frequency of 50 Hz; sinusoidal current with variable amplitudes from 100% of full scale down to 0.005% or 0.02% of full scale and with a frequency of 50 Hz; integrator off.

Figure 4. Total Active Energy Error as a Percentage of Reading over Temperature, PF = 1

Figure 5. Total Reactive Energy Error as a Percentage of Reading over Temperature, PF = 0

Figure 6. Total Apparent Energy Error as a Percentage of Reading over Temperature, PF = 1

Figure 7. Total Active Energy Error as a Percentage of Reading over Supply Voltage, PF = 1,  $T_A = 25$ °C

Figure 8. Total Reactive Energy Error as a Percentage of Reading over Supply Voltage, PF = 0,  $T_A = 25^{\circ}$

Figure 9. Total Apparent Energy Error as a Percentage of Reading over Supply Voltage, PF = 1,  $T_A = 25^{\circ}$

## FUNDAMENTAL ENERGY LINEARITY WITH FIFTH HARMONIC OVER SUPPLY AND TEMPERATURE

Fundamental voltage component in phase with fifth harmonic; current with a 50 Hz component that has variable amplitudes from 100% of full scale down to 0.005% of full scale and a fifth harmonic with a constant amplitude of 40% of fundamental; integrator off.

Figure 10. Fundamental Reactive Energy Error as a Percentage of Reading over Temperature, PF = 0

Figure 11. Fundamental Reactive Energy Error as a Percentage of Reading over Supply Voltage, PF = 0,  $T_A = 25^{\circ}$

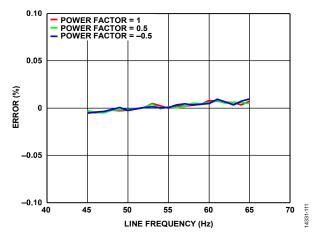

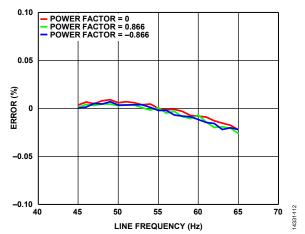

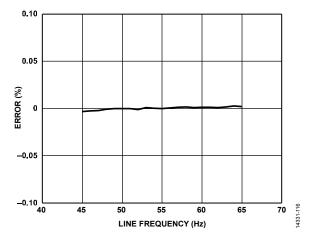

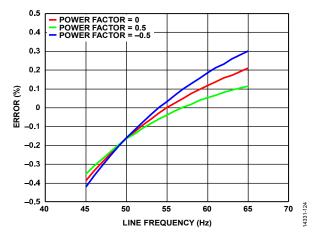

# **TOTAL ENERGY ERROR OVER FREQUENCY**

Sinusoidal voltage with a constant amplitude of 50% of full scale; sinusoidal current with a constant amplitude of 10% of full scale; variable frequency between 45 Hz and 65 Hz; integrator off.

Figure 12. Total Active Energy Error as a Percentage of Reading vs. Line Frequency, PF = -0.5, +0.5, and +1

Figure 13. Total Reactive Energy Error as a Percentage of Reading vs. Line Frequency, PF = -0.866, 0, and +0.866

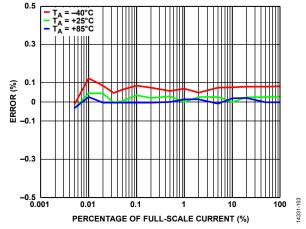

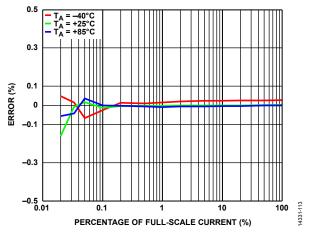

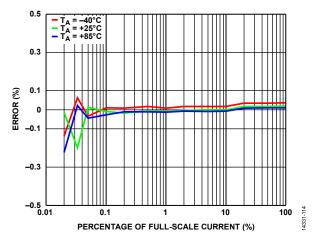

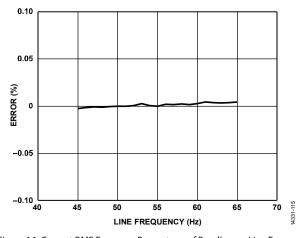

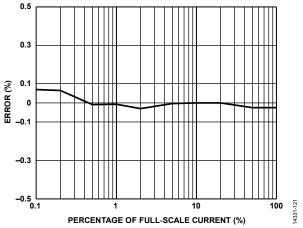

## RMS LINEARITY OVER TEMPERATURE AND RMS ERROR OVER FREQUENCY

Sinusoidal current and voltage with variable amplitudes from 100% of full scale down to 0.02% of full scale using a frequency of 50 Hz; variable frequency between 45 Hz and 65 Hz; sinusoidal current amplitude of 10% of full scale and voltage amplitude of 50% of full scale; integrator off.

Figure 14. Current RMS Error as a Percentage of Reading over Temperature

Figure 15. Voltage RMS Error as a Percentage of Reading over Temperature

Figure 16. Current RMS Error as a Percentage of Reading vs. Line Frequency

Figure 17. Voltage RMS Error as a Percentage of Reading vs. Line Frequency

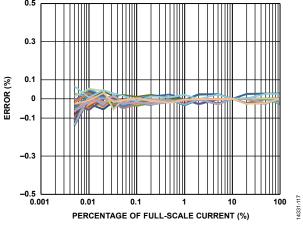

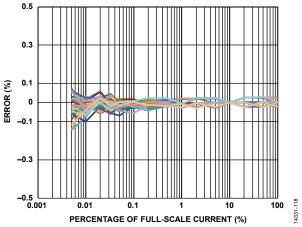

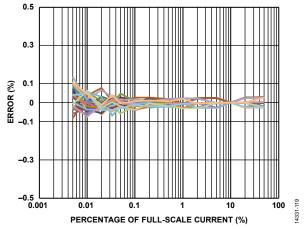

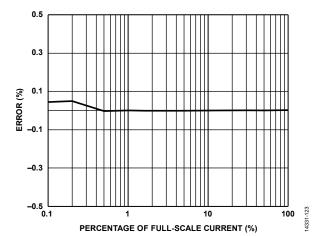

#### **ENERGY LINEARITY REPEATABILITY**

Sinusoidal voltage with an amplitude of 50% of full scale and a frequency of 50 Hz; sinusoidal current with variable amplitudes from 100% of full scale down to 0.005% of full scale and with a frequency of 50 Hz. For Figure 20, besides the fundamental component, the voltage contained a fifth harmonic with a constant amplitude of 40% of fundamental, and the current contained a fifth harmonic with a constant amplitude of 40% of fundamental. Integrator off. Measurements at 25°C repeated 30 times.

Figure 18. Total Active Energy Error as a Percentage of Reading, PF = 1 (Standard Deviation  $\sigma$  = 0.03% at 0.01% of Full-Scale Current)

Figure 19. Total Reactive Energy Error as a Percentage of Reading, PF = 0 (Standard Deviation  $\sigma$  = 0.04% at 0.01% of Full-Scale Current)

Figure 20. Fundamental Reactive Energy Error as a Percentage of Reading, PF = 0 (Standard Deviation  $\sigma = 0.04\%$  at 0.01% of Full-Scale Current)

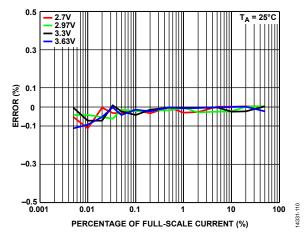

#### TOTAL ENERGY AND RMS LINEARITY WITH INTEGRATOR ON

Sinusoidal voltage with an amplitude of 50% of full scale and a frequency of 50 Hz; gain of current channel set to 4; sinusoidal current with variable amplitudes from 100% of full scale down to 0.05% or 0.1% of full scale and with a frequency of 50 Hz; full scale at gain of 4 = (full scale at gain of 1)/4, high-pass corner frequency of 4.97 Hz.

Figure 21. Total Active Energy Error, Gain = 4, Integrator On

Figure 22. Total Reactive Energy Error, Gain = 4, Integrator On

Figure 23. Total Apparent Energy Error, Gain = 4, Integrator On

Figure 24. Total RMS Current Error, Gain = 4, Integrator On

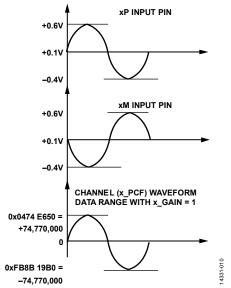

# TOTAL ENERGY ERROR OVER FREQUENCY WITH INTEGRATOR ON

Sinusoidal voltage with a constant amplitude of 50% of full scale; gain of current channel set to 4; sinusoidal current with a constant amplitude of 10% of full scale; variable frequency between 45 Hz and 65 Hz, gigh-pass corner frequency of 4.97 Hz.

Figure 25. Total Active Energy Error as a Percentage of Reading vs. Line Frequency, Gain = 4, Integrator On

Figure 26. Total Reactive Energy Error as a Percentage of Reading vs. Line Frequency, Gain = 4, Integrator On

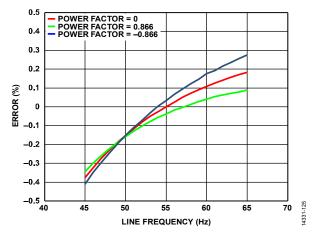

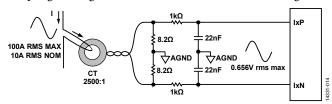

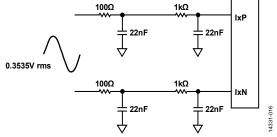

# **TEST CIRCUIT**

# **TERMINOLOGY**

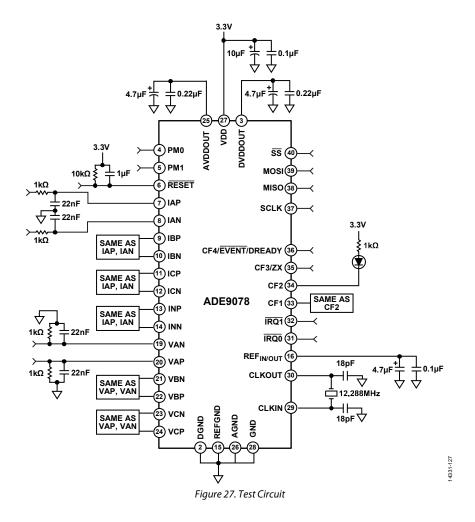

# Differential Input Voltage Range and Maximum Operating Voltage on VxP, VxN, IxP, and IxN Analog Input Pins

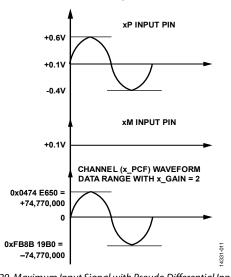

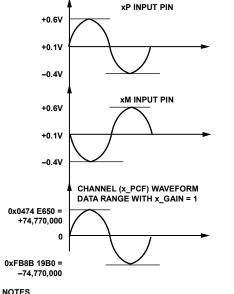

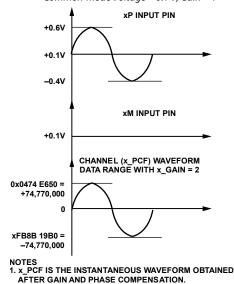

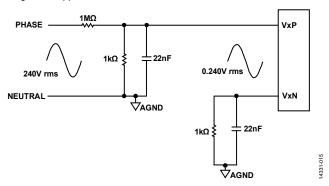

The differential input range describes the maximum difference between the IxP and IxN or VxP and VxN pins. The maximum operating voltage given in Table 1 describes the maximum voltage that can be present on each pin, including any common-mode voltage. Figure 28 illustrates the maximum input between xP and xM, which is seen in the application when a current transformer with center tapped burden resistor is used. Figure 29 illustrates the maximum input voltage range between xP and xN when a pseudo differential input is applied, as is commonly seen when sensing the line voltage.

Figure 28. Maximum Input Signal with Differential Antiphase Input with Common-Mode Voltage = 0.1 V Gain = 1

Figure 29. Maximum Input Signal with Pseudo Differential Input with Common-Mode Voltage = 0.1 V, Gain = 2 (x\_GAIN = 2)

#### Crosstalk

Crosstalk is measured by grounding one channel and applying a full-scale 50 Hz or 60 Hz signal on all the other channels. The crosstalk is equal to the ratio between the grounded ADC output value and its ADC full-scale output value. The ADC outputs are acquired for 100 sec. Crosstalk is expressed in decibels.

#### Differential Input Impedance (DC)

The differential input impedance represents the impedance between the pair IxP and IxN or VxP and VxN. It varies with the PGA gain selection as indicated in Table 1.

#### **ADC Offset**

ADC offset is the difference between the average measured ADC output code with both inputs connected to GND and the ideal ADC output code of zero. ADC offset is expressed in microvolts.

#### **ADC Offset Drift over Temperature**

The ADC offset drift is the change in offset over temperature. It is measured at  $-40^{\circ}$ C,  $+25^{\circ}$ C, and  $+85^{\circ}$ C. The offset drift over temperature is computed as follows:

$$\max\left(\left|\frac{Offset\left(-40^{\circ}C\right) - Offset\left(25^{\circ}C\right)}{\left(-40^{\circ}C - 25^{\circ}C\right)}\right|, \left|\frac{Offset\left(85^{\circ}C\right) - Offset\left(25^{\circ}C\right)}{\left(85^{\circ}C - 25^{\circ}C\right)}\right|\right)$$

Offset drift is expressed in µV/°C.

#### **Gain Error**

The gain error in the ADCs represents the difference between the measured ADC output code (minus the offset) and the ideal output code when an external voltage reference of 1.2 V is used (see the Voltage Reference section). The difference is expressed as a percentage of the ideal code. It represents the overall gain error of one channel.

#### **Gain Drift over Temperature**

This temperature coefficient includes the temperature variation of the ADC gain while using an external voltage reference of 1.2 V. It represents the overall temperature coefficient of one current or voltage channel. With an external voltage reference of 1.2 V in use, the ADC gain is measured at  $-40^{\circ}$ C,  $+25^{\circ}$ C, and  $+85^{\circ}$ C. Then the temperature coefficient is computed as follows:

$$\max \left( \frac{|\mathit{Gain}(-40^{\circ}C) - \mathit{Gain}(25^{\circ}C)|}{|\mathit{Gain}(25^{\circ}C) \times (-40^{\circ}C - 25^{\circ}C)|}, \frac{|\mathit{Gain}(85^{\circ}C) - \mathit{Gain}(25^{\circ}C)|}{|\mathit{Gain}(25^{\circ}C) \times (85^{\circ}C - 25^{\circ}C)|} \right)$$

Gain drift is measured in ppm/°C

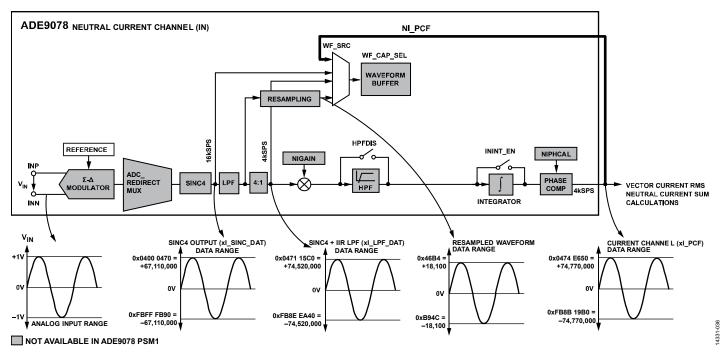

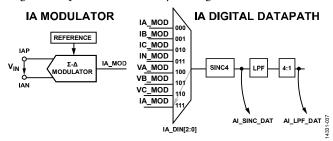

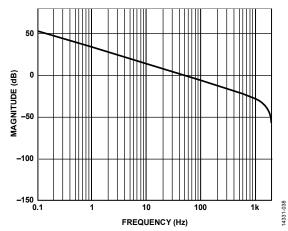

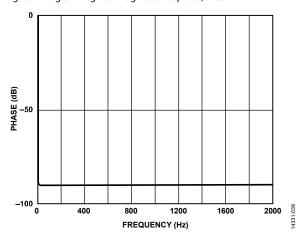

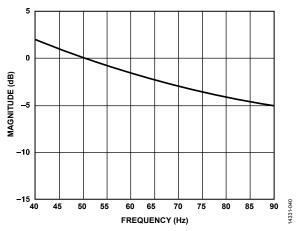

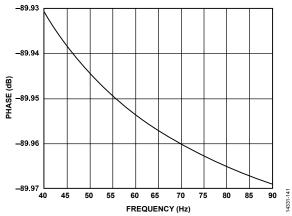

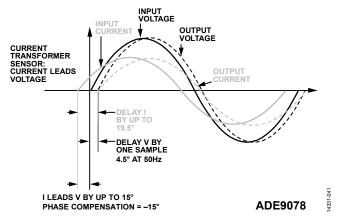

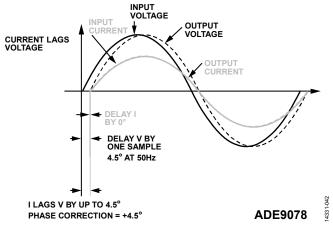

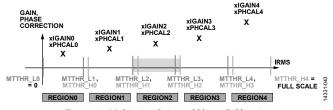

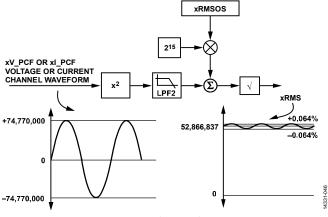

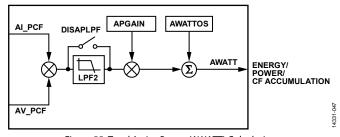

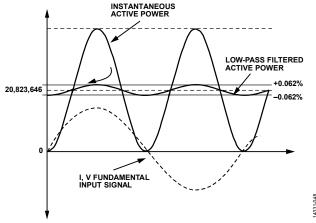

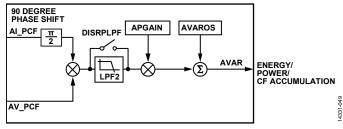

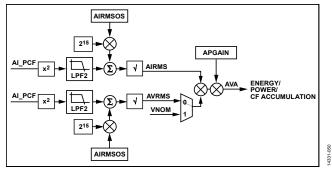

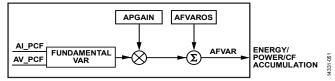

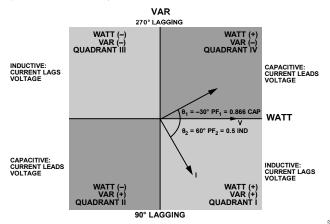

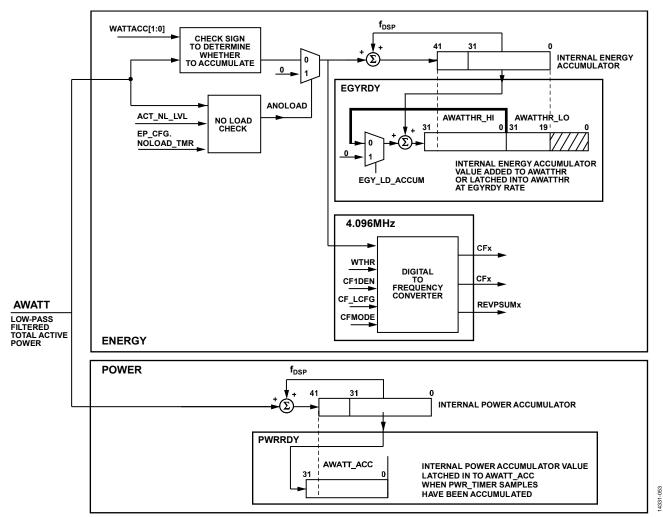

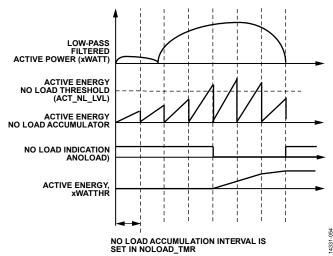

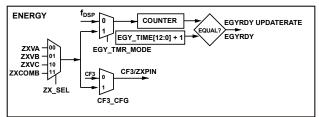

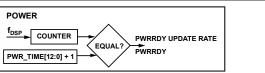

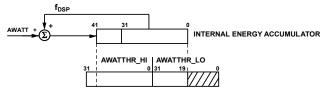

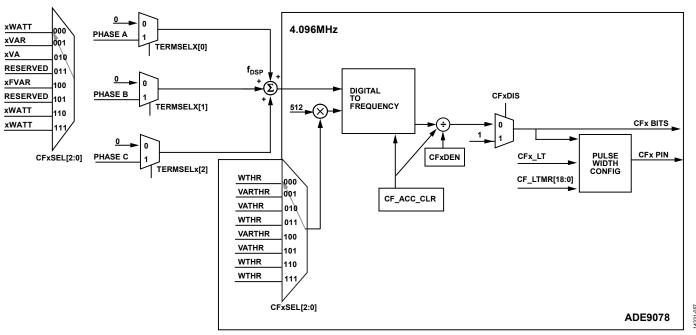

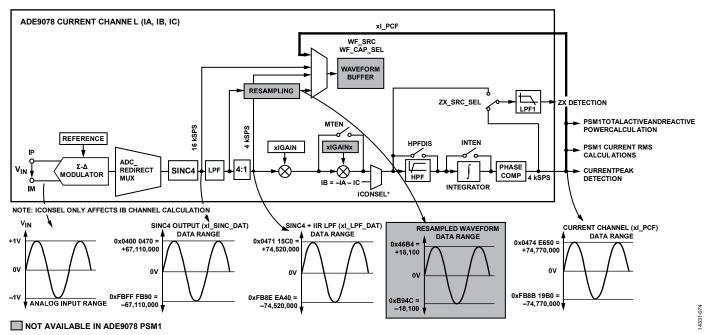

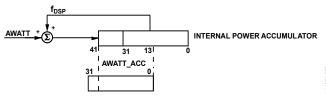

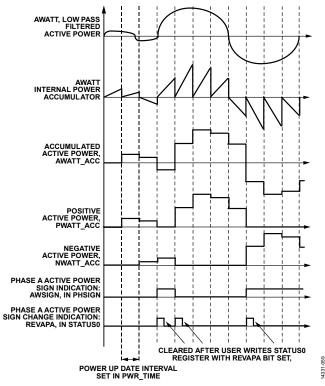

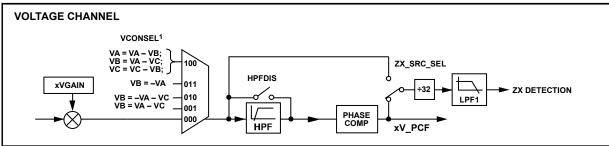

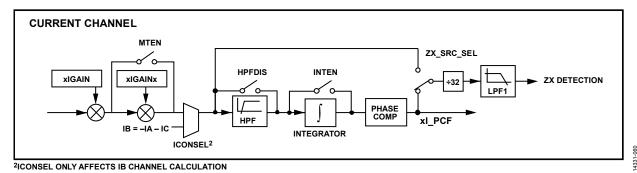

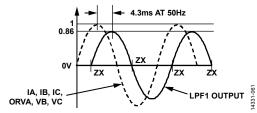

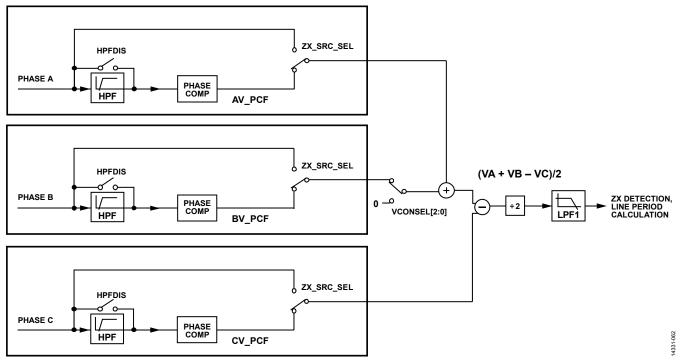

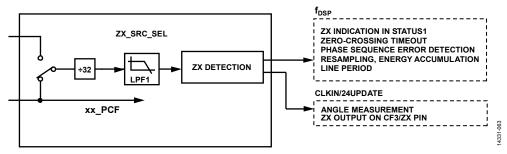

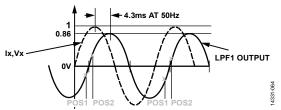

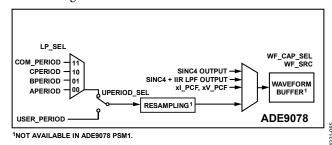

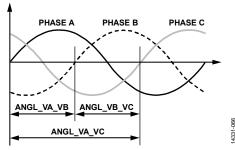

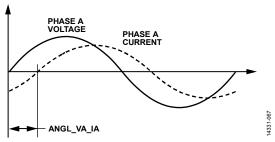

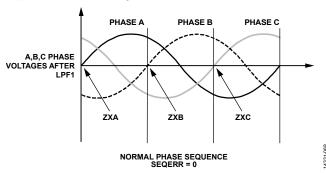

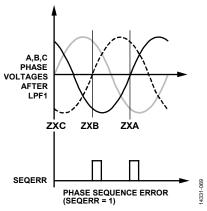

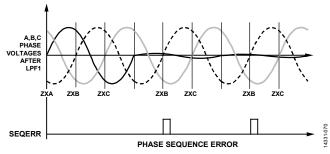

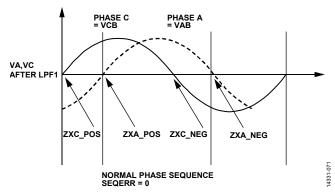

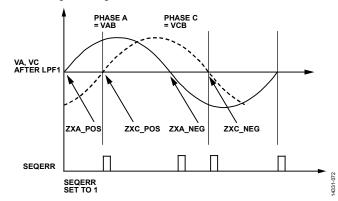

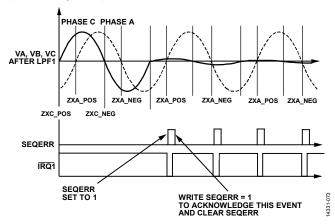

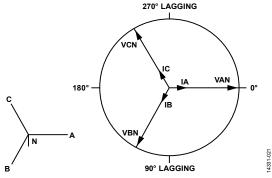

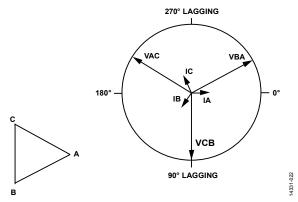

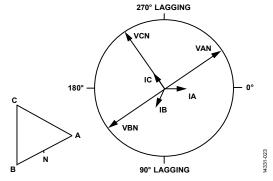

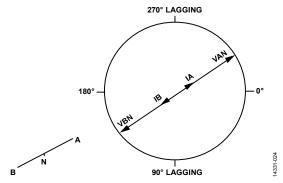

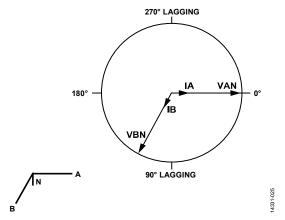

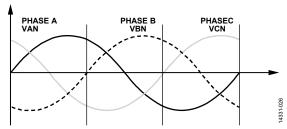

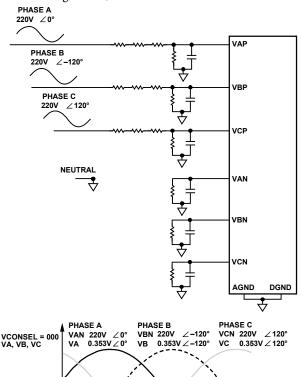

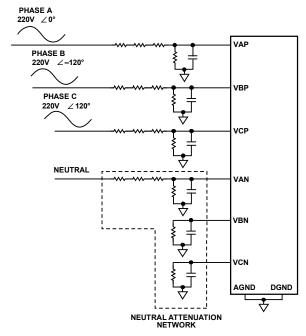

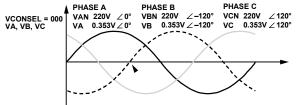

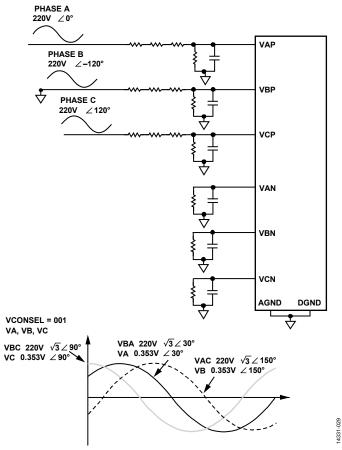

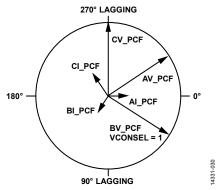

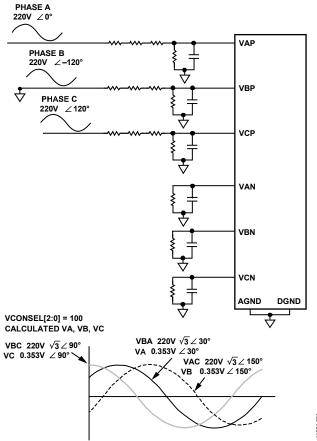

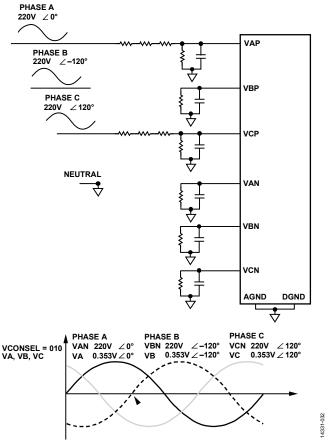

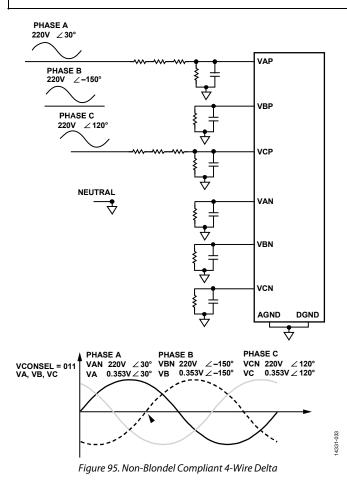

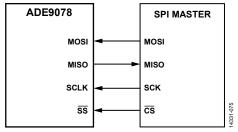

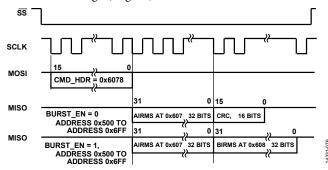

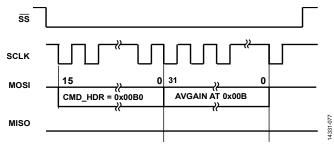

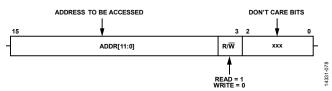

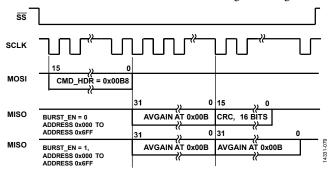

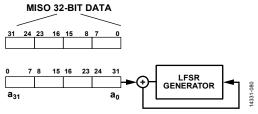

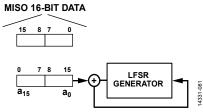

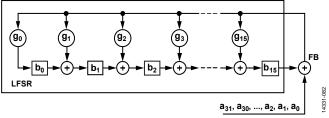

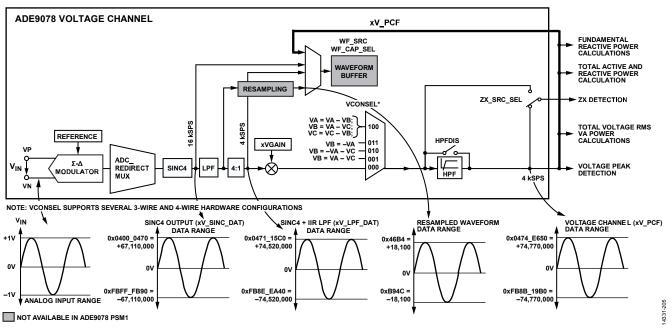

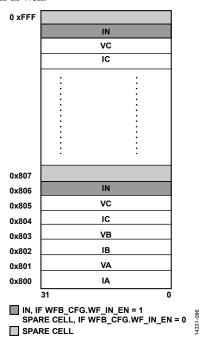

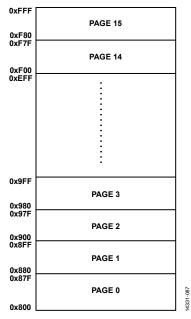

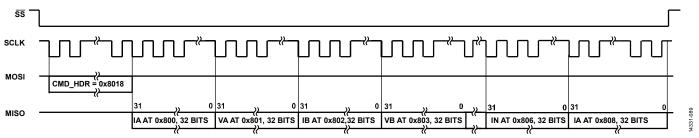

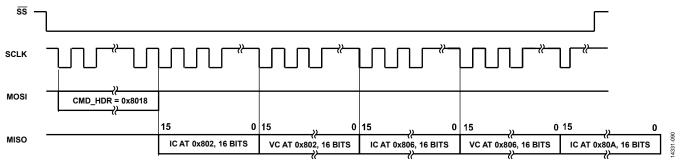

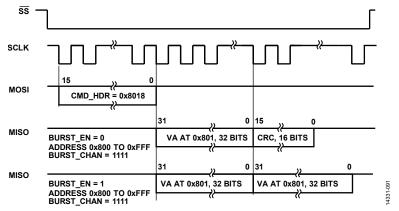

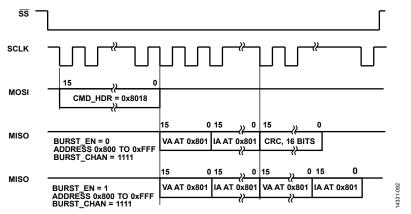

#### **AC Power Supply Rejection (PSRR)**