## ANALOG DEVICES

# ±0.1°C Accuracy, 16-Bit, Digital I<sup>2</sup>C Temperature Sensor for VSM Applications

### **Data Sheet**

## ADT7422

#### **FEATURES**

Accuracy meets clinical thermometry specification of the ASTM E1112 when soldered onto the final PCB ±0.1°C from 25°C to 50°C at 3.0 V ±0.25°C from -20°C to +105°C at 2.7 V to 3.3 V Ultralow temperature drift: 0.0073°C National Institute of Standards and Technology (NIST) traceable or equivalent Fast first temperature conversion at power-up of 6 ms Simple implementation No temperature calibration or correction required No linearity correction required Low power 140 µW typical at 3.0 V in 1 SPS mode 6 μW typical at 3.0 V in shutdown mode **Programmable interrupts Critical overtemperature interrupt Overtemperature and undertemperature interrupt** I<sup>2</sup>C-compatible interface 16-lead, 4 mm × 4 mm, RoHS compliant LFCSP

#### **APPLICATIONS**

Vital signs monitoring (VSM) Medical equipment Resistance temperature detector (RTD) and thermistor replacement Food transportation and storage Thermocouple cold junction compensation Environmental monitoring and heating, ventilation, and air conditioning (HVAC)

Laser diode temperature control

#### **GENERAL DESCRIPTION**

The ADT7422 is a high accuracy, digital I<sup>2</sup>C temperature sensor designed to meet the clinical thermometry specification of the ASTM E1112 standards when soldered onto the final printed circuit board (PCB).

The ADT7422 contains an internal band gap reference, a temperature sensor, and a precision analog-to-digital converter (ADC). The ADT7422 provides a 16-bit temperature result with a resolution of 0.0078°C and an accuracy of up to  $\pm 0.1°C$  across the temperature range of 25°C to 50°C without the need for calibration after the PCB soldering process.

Operating at 3.0 V, the average supply current is typically 210  $\mu$ A. The ADT7422 has a shutdown mode that powers down the device and offers a shutdown current of typically 2.0  $\mu$ A at 3.0 V. The ADT7422 is rated for operation over the -40°C to +125°C temperature range.

Pin A0 and Pin A1 are available for address selection and provide four possible I<sup>2</sup>C addresses for the ADT7422. The CT pin is an open-drain output that becomes active when the temperature exceeds a programmable critical temperature limit. The INT pin is also an open-drain output that becomes active when the temperature exceeds a programmable limit. The INT pin and CT pin can operate in comparator and interrupt event modes.

#### **PRODUCT HIGHLIGHTS**

- 1. No calibration or correction required by the user.

- 2. Low power consumption.

- 3. Long-term stability and reliability.

- 4. High accuracy for industrial, instrumentation, and medical applications.

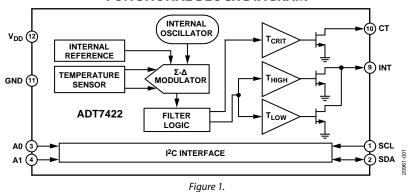

#### FUNCTIONAL BLOCK DIAGRAM

#### Rev. A

#### Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2020 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

## **TABLE OF CONTENTS**

| Features                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Applications 1                                                                                                                                         |

| General Description 1                                                                                                                                  |

| Product Highlights 1                                                                                                                                   |

| Functional Block Diagram 1                                                                                                                             |

| Revision History 2                                                                                                                                     |

| Specifications                                                                                                                                         |

| I <sup>2</sup> C Timing Specifications4                                                                                                                |

| Absolute Maximum Ratings 5                                                                                                                             |

| Thermal Resistance 5                                                                                                                                   |

| ESD Caution                                                                                                                                            |

| Pin Configuration and Function Descriptions                                                                                                            |

|                                                                                                                                                        |

| Typical Performance Characteristics7                                                                                                                   |

| Typical Performance Characteristics                                                                                                                    |

|                                                                                                                                                        |

| Theory of Operation                                                                                                                                    |

| Theory of Operation    9      Circuit Information    9      Converter Details    9      Normal Mode    9      One Shot Mode    9      1 SPS Mode    11 |

| Theory of Operation                                                                                                                                    |

| Theory of Operation9Circuit Information9Converter Details9Normal Mode9One Shot Mode91 SPS Mode11Shutdown Mode11Fault Queue11                           |

| Theory of Operation9Circuit Information9Converter Details9Normal Mode9One Shot Mode91 SPS Mode11Shutdown Mode11Fault Queue11Temperature Data Format12  |

| Temperature Value Registers                    | . 13 |

|------------------------------------------------|------|

| Status Register                                | . 14 |

| Configuration Register                         | . 14 |

| THIGH Setpoint Registers                       | . 15 |

| TLOW Setpoint Registers                        | . 15 |

| T <sub>CRIT</sub> Setpoint Registers           | . 10 |

| T <sub>HYST</sub> Setpoint Register            | . 15 |

| ID Register                                    | . 15 |

| Serial Interface                               | . 16 |

| Serial Bus Address                             | . 16 |

| Writing Data                                   | . 17 |

| Reading Data                                   | . 18 |

| Reset                                          | . 19 |

| General Call                                   | . 19 |

| INT and CT Outputs                             | . 20 |

| Undertemperature and Overtemperature Detection | . 20 |

| Applications Information                       | . 22 |

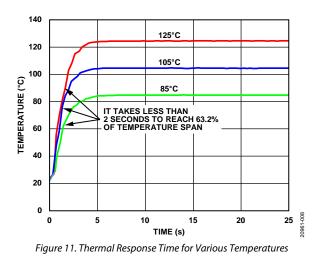

| Thermal Response Time                          | . 22 |

| Supply Decoupling                              | . 22 |

| Powering from a Switching Regulator            | . 22 |

| Temperature Measurement                        | . 22 |

| Quick Guide to Measuring Temperature           | . 22 |

| Outline Dimensions                             | . 23 |

| Ordering Guide                                 | . 23 |

#### **REVISION HISTORY**

| 4/2020—Rev. 0 to Rev. A                                    |

|------------------------------------------------------------|

| Changes to Data Sheet Title, Features Section, and General |

| Description Section                                        |

| Change to Accuracy Parameter, Table 1 3                    |

#### 1/2020—Revision 0: Initial Version

## **SPECIFICATIONS**

$T_A = -40$ °C to +125°C,  $V_{DD} = 2.7$  V to 3.3 V, unless otherwise noted.

#### Table 1.

| Parameter                                     | Symbol          | Min                        | Тур       | Max                 | Unit | Test Conditions/Comments                                             |

|-----------------------------------------------|-----------------|----------------------------|-----------|---------------------|------|----------------------------------------------------------------------|

| TEMPERATURE SENSOR AND ADC                    |                 |                            |           |                     |      |                                                                      |

| Accuracy <sup>1</sup>                         |                 |                            |           | ±0.1 <sup>2</sup>   | °C   | $T_A = 25^{\circ}C$ to 50°C, $V_{DD} = 3.0$ V                        |

|                                               |                 |                            |           | ±0.25               | °C   | $T_A = -20^{\circ}$ C to $+105^{\circ}$ C, $V_{DD} = 2.7$ V to 3.3 V |

|                                               |                 |                            |           | ±0.50               | °C   | $T_A = -40^{\circ}$ C to $+125^{\circ}$ C, $V_{DD} = 2.7$ V to 3.3 V |

| ADC Resolution                                |                 |                            | 13        |                     | Bits | Twos complement temperature value of the sign bit plus 12 ADC bits   |

|                                               |                 |                            | 16        |                     | Bits | Twos complement temperature value of the sign bit plus 15 ADC bit    |

| Temperature Resolution                        |                 |                            |           |                     |      |                                                                      |

| 13-Bit                                        |                 |                            | 0.0625    |                     | °C   | 13-bit resolution (sign + 12 bits)                                   |

| 16-Bit                                        |                 |                            | 0.0078125 |                     | °C   | 16-bit resolution (sign + 15 bits)                                   |

| Temperature Conversion Time                   |                 |                            | 240       |                     | ms   | Continuous conversion and one-shot<br>conversion modes               |

| Fast Temperature Conversion Time              |                 |                            | 6         |                     | ms   | First conversion on power-up only                                    |

| 1 SPS Mode Conversion Time                    |                 |                            | 60        |                     | ms   | Conversion time for 1 SPS mode                                       |

| Temperature Hysteresis <sup>3</sup>           |                 |                            | ±0.002    |                     | °C   | Temperature cycle = 25°C to 125°C to 25°C                            |

| Repeatability                                 |                 |                            | ±0.015    |                     | °C   | $T_A = 25^{\circ}C$ , average of 10 readings                         |

| Drift <sup>4</sup>                            |                 |                            | 0.0073    |                     | °C   | 500-hour stress test at 150°C                                        |

| DC Power Supply Rejection Ratio<br>(PSRR)     |                 |                            | 0.1       |                     | °C/V | $T_A = 25^{\circ}C$                                                  |

| DIGITAL OUTPUTS (CT, INT, SDA—<br>OPEN-DRAIN) |                 |                            |           |                     |      |                                                                      |

| High Output Leakage Current                   | I <sub>OH</sub> |                            | 0.1       | 5                   | μA   | CT pin and INT pin pulled up to $V_{DD}$                             |

| Output Low Voltage                            | Vol             |                            |           | 0.4                 | V    | Low output leakage current $(I_{OL}) = 1$ mA at 3.3 V                |

| Output High Voltage                           | V <sub>OH</sub> | $0.7 \times V_{DD}$        |           |                     | v    |                                                                      |

| Output Capacitance                            | COUT            |                            | 2         |                     | рF   |                                                                      |

| DIGITAL INPUTS (SCL, SDA, A0, A1)             |                 |                            |           |                     |      |                                                                      |

| Input Current                                 |                 |                            |           | ±1                  | μA   | Input voltage ( $V_{IN}$ ) = 0 V to $V_{DD}$                         |

| Input Low Voltage                             | VIL             |                            |           | $0.3 \times V_{DD}$ | V    | SCL and SDA only                                                     |

|                                               |                 |                            |           | 0.4                 | V    | A0 and A1 only                                                       |

| Input High Voltage                            | VIH             | $0.7 \times V_{\text{DD}}$ |           |                     | v    | SCL and SDA only                                                     |

|                                               |                 | 2                          |           |                     | V    | A0 and A1 only                                                       |

| SCL and SDA Glitch Rejection                  |                 |                            | 50        |                     | ns   | Input filtering suppresses noise spikes of <50 ns                    |

| Pin Capacitance                               |                 |                            | 2         | 10                  | pF   |                                                                      |

| POWER REQUIREMENTS                            |                 |                            |           |                     | · ·  |                                                                      |

| Supply Voltage                                |                 | 2.7                        | 3.0       | 3.3                 | v    |                                                                      |

| Supply Current                                |                 |                            | 210       | 265                 | μA   | $V_{DD} = 3.3$ V while converting, I <sup>2</sup> C inactive         |

| 1 SPS Current                                 |                 |                            | 46        |                     | μA   | $V_{DD} = 3.3$ V in 1 SPS mode, $T_A = 25^{\circ}C$                  |

| Shutdown Current                              |                 |                            | 2.0       | 15                  | μA   | $V_{DD} = 3.3 \text{ V}$                                             |

| Power Dissipation Normal Mode                 |                 |                            | 700       |                     | μW   | $V_{DD} = 3.3 \text{ V}, T_A = 25^{\circ}\text{C}$                   |

| Power Dissipation 1 SPS                       |                 |                            | 140       |                     | μW   | $V_{DD} = 3.0 \text{ V}, \text{ T}_{A} = 25^{\circ}\text{C}$         |

| Power Dissipation Shutdown Mode               |                 |                            | 6         |                     | μW   | $V_{DD} = 3.0 \text{ V}, \text{ T}_{A} = 25^{\circ}\text{C}$         |

<sup>1</sup> The accuracy specification includes repeatability. <sup>2</sup> These limits represent a 3-signa distribution when devices are soldered to the PCB using a 16-point rolling average filter with a 300 ms sample period with the device in continuous conversion mode.

<sup>3</sup> The temperature hysteresis specification does not include repeatability. <sup>4</sup> Drift includes solder heat resistance and lifetime test performed as per JEDEC Standard JESD22-A108.

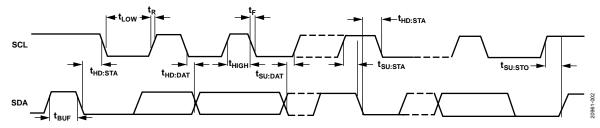

#### I<sup>2</sup>C TIMING SPECIFICATIONS

$T_A = -40^{\circ}$ C to  $+125^{\circ}$ C,  $V_{DD} = 2.7$  V to 3.3 V, unless otherwise noted. All input signals are specified with rise time ( $t_R$ ) = fall time ( $t_F$ ) = 5 ns (10% to 90% of  $V_{DD}$ ) and timed from a voltage level of 1.6 V.

#### Table 2.

| Parameter                                        | Symbol              | Min  | Тур | Max | Unit | Test Conditions/Comments                         |

|--------------------------------------------------|---------------------|------|-----|-----|------|--------------------------------------------------|

| SERIAL INTERFACE                                 |                     |      |     |     |      | See Figure 2. Sample tested during               |

|                                                  |                     |      |     |     |      | development to ensure compliance.                |

| SCL Frequency                                    |                     | 0    |     | 400 | kHz  |                                                  |

| SCL High Pulse Width                             | thigh               | 0.6  |     |     | μs   |                                                  |

| SCL Low Pulse Width                              | t <sub>LOW</sub>    | 1.3  |     |     | μs   |                                                  |

| SCL and SDA Rise Time                            | t <sub>R</sub>      |      |     | 0.3 | μs   |                                                  |

| SCL and SDA Fall Time                            | t⊧                  |      |     | 0.3 | μs   |                                                  |

| Hold Time (Start Condition)                      | thd:sta             | 0.6  |     |     | μs   | After this period, the first clock is generated. |

| Setup Time (Start Condition)                     | t <sub>su:sta</sub> | 0.6  |     |     | μs   | Relevant for repeated start condition.           |

| Data Setup Time                                  | tsu:dat             | 0.02 |     |     | μs   |                                                  |

| Setup Time (Stop Condition)                      | t <sub>su:sto</sub> | 0.6  |     |     | μs   |                                                  |

| Data Hold Time (Master)                          | t <sub>HD:DAT</sub> | 0.03 |     |     | μs   |                                                  |

| Bus Free Time (Between Stop and Start Condition) | <b>t</b> BUF        | 1.3  |     |     | μs   |                                                  |

| Capacitive Load for Each Bus Line                | C <sub>B</sub>      |      |     | 400 | рF   |                                                  |

#### **Timing Diagram**

Figure 2. Serial Interface Timing Diagram

## **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 3.

| Parameter                                    | Rating                              |

|----------------------------------------------|-------------------------------------|

| V <sub>DD</sub> to GND                       | –0.3 V to +7 V                      |

| SDA Voltage to GND                           | $-0.3$ V to $V_{\text{DD}}$ + 0.3 V |

| SCL Output Voltage to GND                    | $-0.3$ V to $V_{\text{DD}}$ + 0.3 V |

| A0 Input Voltage to GND                      | -0.3 V to V <sub>DD</sub> + 0.3 V   |

| A1 Input Voltage to GND                      | -0.3 V to V <sub>DD</sub> + 0.3 V   |

| CT and INT Output Voltage to GND             | $-0.3$ V to $V_{\text{DD}}$ + 0.3 V |

| Operating Temperature Range                  | -40°C to +125°C                     |

| Storage Temperature Range                    | -65°C to +150°C                     |

| Maximum Junction Temperature                 | 150°C                               |

| ESD                                          |                                     |

| Human Body Model (HBM)                       | 2 kV                                |

| Field Induced Charge Device Model<br>(FICDM) | 1 kV                                |

| Reflow Soldering (Pb-Free)                   | JEDEC J-STD-020                     |

| Peak Temperature                             | 260°C                               |

| Time at Peak Temperature                     | 10 sec to 40 sec                    |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to PCB design and operating environment. Close attention to PCB thermal design is required.  $\theta_{IA}$  and  $\theta_{IC}$  are specified for a device soldered on a JEDEC 4-layer test board for surface-mount packages with 16 thermal vias. The values listed in Table 4 are based on simulated data.

#### Table 4. Thermal Resistance

| Package Type | θ」Α | οıc | Unit |

|--------------|-----|-----|------|

| CP-16-17     | 37  | 33  | °C/W |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

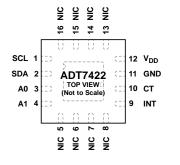

## **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

NOTES

1. NIC = NOT INTERNALLY CONNECTED. THE NIC PINS ARE NOT BONDED TO THE DIE INTERNALLY. 2. EXPOSED PAD. TO ENSURE CORRECT OPERATION, EITHER LEAVE THE EXPOSED PAD FLOATING OR CONNECT THE EXPOSED PAD TO GROUND. SOLDER THE EXPOSED PAD TO A PAD ON THE PCB TO CONFER MECHANICAL STRENGTH TO THE PACKAGE.

Figure 3. Pin Configuration

#### **Table 5. Pin Function Descriptions**

| Pin No.          | Mnemonic        | Description                                                                                                                                                                                                        |  |

|------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1                | SCL             | I <sup>2</sup> C Serial Clock Input, Open-Drain Configuration. The serial clock is used to clock in and clock out data to and from any register of the ADT7422. A pull-up resistor of typically 10 kΩ is required. |  |

| 2                | SDA             | $I^2C$ Serial Data Input/Output, Open-Drain Configuration. Serial data to and from the device is provided this pin. A pull-up resistor of typically 10 k $\Omega$ is required.                                     |  |

| 3                | A0              | I <sup>2</sup> C Serial Bus Address Selection Pin, Logic Input. Connect this pin to GND or V <sub>DD</sub> to set an I <sup>2</sup> C address.                                                                     |  |

| 4                | A1              | I <sup>2</sup> C Serial Bus Address Selection Pin, Logic Input. Connect this pin to GND or V <sub>DD</sub> to set an I <sup>2</sup> C address.                                                                     |  |

| 5 to 8, 13 to 16 | NIC             | Not Internally Connected. The NIC pins are not bonded to the die internally.                                                                                                                                       |  |

| 9                | INT             | Overtemperature and Undertemperature Indicator, Logic Output, Open-Drain Configuration. Power-up default setting is an active low comparator interrupt. A pull-up resistor of typically 10 k $\Omega$ is required. |  |

| 10               | СТ              | Critical Overtemperature Indicator, Logic Output, Open-Drain Configuration. Power-up default polarity is active low. A pull-up resistor of typically 10 k $\Omega$ is required.                                    |  |

| 11               | GND             | Analog and Digital Ground.                                                                                                                                                                                         |  |

| 12               | V <sub>DD</sub> | Positive Supply Voltage (2.7 V to 3.3 V). The supply can be decoupled with a 0.1 µF ceramic capacitor to ground.                                                                                                   |  |

|                  | EPAD            | Exposed Pad. To ensure correct operation, either leave the exposed pad floating or connect the exposed pad to ground. Solder the exposed pad to a pad on the PCB to confer mechanical strength to the package.     |  |

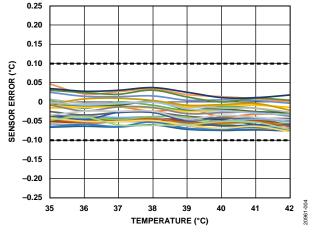

## **TYPICAL PERFORMANCE CHARACTERISTICS**

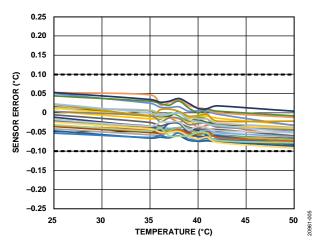

Figure 4. VSM Temperature Range of the EVAL-ADT7422MBZ Post Soldering to JEDEC J-STD-020, V<sub>DD</sub> = 3 V

Figure 5. Narrow Temperature Range of the EVAL-ADT7422MBZ Post Soldering to JEDEC J-STD-020,  $V_{DD} = 3 V$

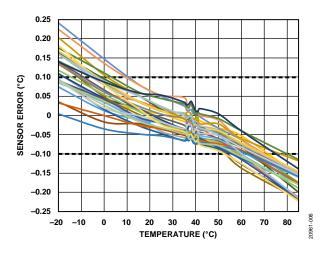

Figure 6. Wide Temperature Range of the EVAL-ADT7422MBZ Post Soldering to JEDEC J-STD-020,  $V_{DD} = 3 V$

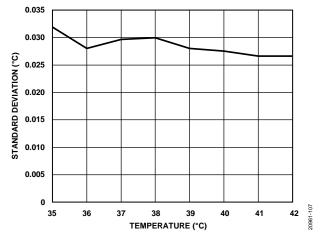

Figure 7. Standard Deviation of the EVAL-ADT7422MBZ Post Soldering to JEDEC J-STD-020,  $V_{DD} = 3 V$

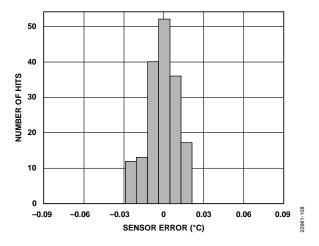

Figure 8. Histogram Distribution of Factory Calibration Error at 38°C for 170 Devices,  $V_{DD} = 3 V$

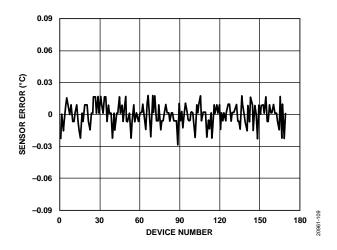

Figure 9. Factory Calibration Error at  $38^{\circ}$ C for 170 Devices,  $V_{DD} = 3 V$

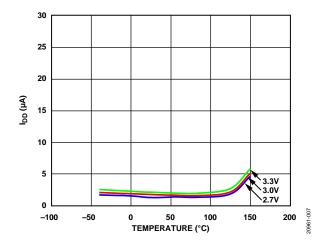

Figure 10. Shutdown Operating Supply Current (I<sub>DD</sub>) vs. Temperature for Various Voltages

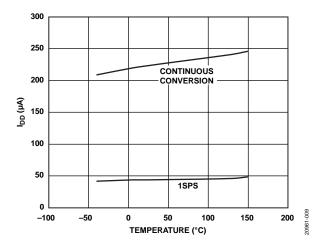

Figure 12. IDD vs. Temperature at 3 V

## THEORY OF OPERATION CIRCUIT INFORMATION

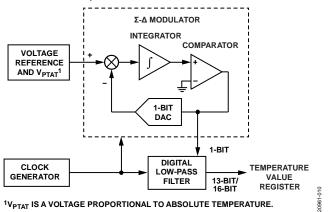

The ADT7422 is a high accuracy, digital I<sup>2</sup>C temperature sensor that uses a 16-bit ADC to monitor and digitize the temperature to 0.0078°C of resolution. The ADC resolution, by default, is set to 13 bits (0.0625°C). An internal temperature sensor generates a voltage proportional to absolute temperature, which is compared to an internal voltage reference and input into a precision digital modulator (see Figure 13).

The internal temperature sensor has high accuracy and linearity over the entire rated temperature range without needing correction or calibration by the user.

The sensor output is digitized by a  $\Sigma$ - $\Delta$  modulator, also known as the charge balance type ADC. This type of converter utilizes time domain oversampling and a high accuracy comparator to deliver 16 bits of resolution in a compact circuit.

#### **CONVERTER DETAILS**

The  $\Sigma$ - $\Delta$  modulator consists of an input sampler, a summing network, an integrator, a comparator, and a 1-bit digital-to-analog converter (DAC). This architecture creates a negative feedback loop and minimizes the integrator output by changing the duty cycle of the comparator output in response to input voltage changes. The comparator samples the output of the integrator at a higher rate than the input sampling frequency. This oversampling spreads the quantization noise over a wider band than that of the input signal, which improves overall noise performance and increases accuracy.

Figure 13.  $\Sigma$ - $\Delta$  Modulator

The ADT7422 can operate in four operating modes: normal, one shot, 1 SPS, and shutdown.

#### NORMAL MODE

In normal mode (default power-up mode) the ADT7422 runs an automatic conversion sequence. During this automatic conversion sequence, a conversion typically takes 240 ms to complete. The ADT7422 continuously converts during the sequence and as soon as one temperature conversion is complete, another temperature conversion begins. Each temperature conversion result is stored in the 16-bit temperature value register, which consists of the 8-bit temperature value most significant byte register and the 8-bit temperature value least significant byte register (see Table 13), and is available through the I<sup>2</sup>C interface. In continuous conversion mode, the read operation provides the most recent converted result.

At power-up, the first conversion is a fast conversion and typically takes 6 ms. If the temperature exceeds 147°C, the CT pin asserts low. If the temperature exceeds 64°C, the INT pin asserts low. Fast conversion temperature accuracy is typically within ±5°C.

The conversion clock for the device is generated internally. No external clock is required except when reading from and writing to the serial port.

The measured temperature value is compared with a critical temperature limit (stored in the 16-bit  $T_{CRIT}$  setpoint read/write register), a high temperature limit (stored in the 16-bit  $T_{HIGH}$  setpoint read/write register), and a low temperature limit (stored in the 16-bit  $T_{LOW}$  setpoint read/write register). If the measured value exceeds these limits, the INT pin is activated. If the measured value exceeds the  $T_{CRIT}$  limit, the CT pin is activated. The INT pin and CT pin are programmable for both polarity via the configuration register (Register Address 0x03) and interrupt mode via the configuration register (Register Address 0x03).

#### **ONE SHOT MODE**

To enable one shot mode, set Bit 6 to 0 and Bit 5 to 1 in the configuration register (Register Address 0x03). When this mode is enabled, the ADT7422 immediately completes a conversion and then goes into shutdown mode.

Wait for a minimum of 240 ms after writing to the operation mode bits before reading back the temperature from the temperature value at Register Address 0x00 and Register Address 0x01, as shown in Table 13. This time ensures that the ADT7422 has time to power up and complete a conversion.

To obtain an updated temperature conversion, reset Bit 6 to 0 and Bit 5 to 1 in the configuration register (Register Address 0x03).

One shot mode is useful when a circuit design priority is to reduce power consumption.

#### **T**<sub>CRIT</sub> SETPOINT REGISTERS

The  $T_{CRIT}$  setpoint most significant byte register and the  $T_{CRIT}$  setpoint least significant byte register store the critical overtemperature limit value. A critical overtemperature event occurs when the temperature value stored in the temperature value register exceeds the value stored in this register. The CT pin is activated if a critical overtemperature event occurs. The temperature is stored in twos complement format with the MSB being the temperature sign bit.

When reading from this register, the 8 MSBs (Bit 15 to Bit 8) are read first from Register Address 0x08 ( $T_{CRIT}$  setpoint most significant byte register), and then the 8 LSBs (Bit 7 to Bit 0) are read from Register Address 0x09 ( $T_{CRIT}$  setpoint least significant byte register). Only Register Address 0x08 ( $T_{CRIT}$  setpoint most significant byte register) must be loaded into the address pointer register because the address pointer auto-increments to Register Address 0x09 ( $T_{CRIT}$  setpoint least significant byte register).

The default setting for the  $T_{CRIT}$  setpoint register is 147°C.

#### Table 6. T<sub>HIGH</sub> Setpoint Most Significant Byte Register (Register Address 0x04)

| Bit    | Default Value | Туре | Name                        | Description                                                          |

|--------|---------------|------|-----------------------------|----------------------------------------------------------------------|

| [15:8] | 0x20          | R/W  | THIGH most significant byte | MSBs of the overtemperature limit, stored in twos complement format. |

#### Table 7. T<sub>HIGH</sub> Setpoint Least Significant Byte Register (Register Address 0x05)

| Bit   | Default Value | Туре | Name                         | Description                                                          |

|-------|---------------|------|------------------------------|----------------------------------------------------------------------|

| [7:0] | 0x00          | R/W  | THIGH least significant byte | LSBs of the overtemperature limit, stored in twos complement format. |

#### Table 8. TLOW Setpoint Most Significant Byte Register (Register Address 0x06)

| Bit    | Default Value | Туре | Name                                   | Description                                                           |

|--------|---------------|------|----------------------------------------|-----------------------------------------------------------------------|

| [15:8] | 0x05          | R/W  | T <sub>LOW</sub> most significant byte | MSBs of the undertemperature limit, stored in twos complement format. |

#### Table 9. TLOW Setpoint Least Significant Byte Register (Register Address 0x07)

| Bit   | Default Value | Туре | Name                        | Description                                                           |

|-------|---------------|------|-----------------------------|-----------------------------------------------------------------------|

| [7:0] | 0x00          | R/W  | TLOW least significant byte | LSBs of the undertemperature limit, stored in twos complement format. |

#### Table 10. TCRIT Setpoint Most Significant Byte Register (Register Address 0x08)

| Bit    | Default Value | Туре | Name                                    | Description                                                                   |

|--------|---------------|------|-----------------------------------------|-------------------------------------------------------------------------------|

| [15:8] | 0x49          | R/W  | T <sub>CRIT</sub> most significant byte | MSBs of the critical overtemperature limit, stored in twos complement format. |

#### Table 11. T<sub>CRIT</sub> Setpoint Least Significant Byte Register (Register Address 0x09)

| Bit   | Default Value | Туре | Name                                     | Description                                                                   |

|-------|---------------|------|------------------------------------------|-------------------------------------------------------------------------------|

| [7:0] | 0x80          | R/W  | T <sub>CRIT</sub> least significant byte | LSBs of the critical overtemperature limit, stored in twos complement format. |

## ADT7422

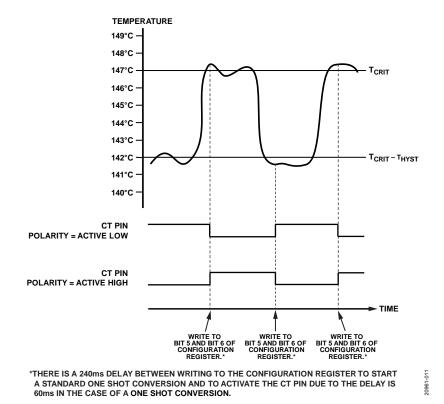

#### CT and INT Operation in One Shot Mode

See Figure 14 for more information on one shot mode CT pin operation for  $T_{CRIT}$  overtemperature events when one of the limits is exceeded. Note that in interrupt mode, a read from any register resets the INT pin and CT pin.

In comparator mode, if the temperature drops below  $T_{HIGH} - T_{HYST}$  or goes above  $T_{LOW} + T_{HYST}$ , a write to the operation mode bits (Register Address 0x03, Bits[6:5]) resets the INT pin.

In comparator mode, if the temperature drops below  $T_{CRIT} - T_{HYST}$ , a write to the operation mode bits (Register Address 0x03, Bits[6:5]) resets the CT pin (see Figure 14).

When using one shot mode, ensure that the appropriate refresh rate is used for the given application.

#### **1 SPS MODE**

In 1 SPS mode, the device performs one measurement per second. A conversion typically takes 60 ms and the device remains in the idle state for the remaining 940 ms period. To enable 1 SPS mode, write 1 to Bit 6 and 0 to Bit 5 of the configuration register (Register Address 0x03).

#### SHUTDOWN MODE

To place the ADT7422 in shutdown mode, write 1 to Bit 6 and Bit 5 of the configuration register (Register Address 0x03), in which case the entire IC is shut down and no further conversions are initiated until the ADT7422 is taken out of shutdown mode. To take the ADT7422 out of shutdown mode, write 0 to Bit 6 and Bit 5 in the configuration register (Register Address 0x03). The ADT7422 typically takes 1 ms (with a 0.1  $\mu F$  decoupling capacitor) to exit shutdown mode. The conversion result from the last conversion prior to shutdown can still be read from the ADT7422 when the device is in shutdown mode. When the device is taken out of shutdown mode, the internal clock starts and a conversion is initiated.

#### **FAULT QUEUE**

Bit 0 and Bit 1 of the configuration register (Register Address 0x03) are used to set up a fault queue. The queue can facilitate up to four fault events to prevent false tripping of the INT pin and CT pin when the ADT7422 is used in a noisy temperature environment. The number of faults set in the queue must occur consecutively to set the INT and CT outputs. For example, if the number of faults set in the queue is four, four consecutive temperature conversions must occur with each result exceeding a temperature limit in any of the limit registers before the INT pin and CT pin are activated. If two consecutive temperature conversions exceed a temperature limit and the third conversion does not, the fault count is reset back to zero.

Figure 14. One Shot CT Pin

#### **TEMPERATURE DATA FORMAT**

One LSB of the ADC corresponds to 0.0625°C in 13-bit mode or 0.0078°C in 16-bit mode. The ADT7422 can measure a temperature range of 255°C, and is guaranteed to measure a low value temperature limit of -40°C to a high value temperature limit of +125°C. The temperature measurement result is stored in the 16-bit temperature value register and is compared with the high temperature limits stored in the 16-bit T<sub>CRIT</sub> setpoint register (consisting of the 8-bit T<sub>CRIT</sub> setpoint most significant byte register and the 8-bit T<sub>CRIT</sub> setpoint least significant byte register) and the 16-bit THIGH setpoint register (consisting of the 8-bit T<sub>HIGH</sub> setpoint most significant byte register and the 8-bit T<sub>HIGH</sub> setpoint least significant byte register). The temperature value is also compared to the low temperature limit stored in the  $T_{\rm LOW}$  setpoint register, which consists of the 8-bit  $T_{\rm LOW}$  setpoint most significant byte register and the 8-bit TLOW setpoint least significant byte register.

Temperature data in the temperature value register, the  $T_{CRIT}$  setpoint register, the  $T_{HIGH}$  setpoint register, and the  $T_{LOW}$  setpoint register are represented by a 13-bit twos complement word. The MSB is the temperature sign bit. The three LSBs, Bits[2:0], at power-up, are not part of the temperature conversion result and are flag bits for  $T_{CRIT}$ ,  $T_{HIGH}$ , and  $T_{LOW}$ . Table 12 shows the 13-bit temperature data format without Bits[2:0].

To extend the number of bits in the temperature data-word to 16 bits (twos complement), set Bits[7:1] in the configuration register (Register Address 0x03). When using a 16-bit temperature data value, Bits[2:0] are not used as flag bits and are the LSB bits of the temperature value instead. The power-on default setting has a 13-bit temperature data value.

A 2-byte read is required to read back the temperature from the temperature value register. The ADT7422 can still be used with a 9-bit temperature data format if the last four LSBs of the 13-bit temperature value are ignored. These four LSBs are Bits[6:3] in Table 12.

| Table 12. 15-Dit Temperature Data Format |                                       |                                 |  |  |  |

|------------------------------------------|---------------------------------------|---------------------------------|--|--|--|

| Temperature                              | Digital Output (Binary)<br>Bits[15:3] | Digital Output<br>(Hexadecimal) |  |  |  |

| -40°C                                    | 1 1101 1000 0000                      | 0x1D80                          |  |  |  |

| –25°C                                    | 1 1110 0111 0000                      | 0x1E70                          |  |  |  |

| –0.0625°C                                | 1 1111 1111 1111                      | 0x1FFF                          |  |  |  |

| 0°C                                      | 0 0000 0000 0000                      | 0x000                           |  |  |  |

| +0.0625°C                                | 0 0000 0000 0001                      | 0x001                           |  |  |  |

| +25°C                                    | 0 0001 1001 0000                      | 0x190                           |  |  |  |

| +105°C                                   | 0 0110 1001 0000                      | 0x690                           |  |  |  |

| +125°C                                   | 0 0111 1101 0000                      | 0x7D0                           |  |  |  |

| +150°C                                   | 0 1001 0110 0000                      | 0x960                           |  |  |  |

#### Table 12. 13-Bit Temperature Data Format

#### **TEMPERATURE CONVERSION FORMULAS**

#### 16-Bit Temperature Data Format

Use the following formulas to calculate the measured temperatures in °C from the ADT7422 output codes in 16-bit format:

*Positive Temperature = ADC Code* (Decimal)/128

*Negative Temperature* = (*ADC Code* (Decimal) – 65,536)/128

where *ADC Code* uses all 16 bits of the data byte, including the sign bit.

*Negative Temperature* = (*ADC Code* (Decimal) – 32,768)/128

where Bit 15 (sign bit) is removed from the ADC code.

#### 13-Bit Temperature Data Format

Use the following formulas to calculate the measured temperatures in °C from the ADT7422 output codes in 13-bit format:

*Positive Temperature = ADC Code* (Decimal)/16

Negative Temperature = (ADC Code (Decimal) - 8192)/16

where *ADC Code* uses the first 13 MSBs of the data byte, including the sign bit.

*Negative Temperature* = (*ADC Code* (Decimal) – 4096)/16

where Bit 15 (sign bit) is removed from the ADC code.

#### 10-Bit Temperature Data Format

Use the following formulas to calculate the measured temperatures in °C from the ADT7422 output codes in 10-bit format:

*Positive Temperature = ADC Code* (Decimal)/2

*Negative Temperature* = (*ADC Code* (Decimal) – 1024)/2

where *ADC Code* uses all 10 bits of the data byte, including the sign bit.

*Negative Temperature* = (*ADC Code* (Decimal) – 512)/2

where Bit 9 (sign bit) is removed from the ADC code.

#### 9-Bit Temperature Data Format

Use the following formulas to calculate the measured temperatures in °C from the ADT7422 output codes in 9-bit format:

*Positive Temperature = ADC Code* (Decimal)

*Negative Temperature = ADC Code* (Decimal) – 512

where *ADC Code* uses all nine bits of the data byte, including the sign bit.

*Negative Temperature = ADC Code* (Decimal) – 256

where Bit 8 (sign bit) is removed from the ADC code.

## REGISTERS

The ADT7422 contains 13 registers, as shown in Table 13, and the address pointer register. The registers include the following:

- Nine temperature registers

- One status register

- One ID register

- One configuration register

- One address pointer register

- One software reset

All registers are 8 bits wide. The temperature value registers, the status register, and the ID register are read only. The software reset register is a write only register. At power-up, the address pointer register is loaded with 0x00 and points to the temperature value most significant byte register (Register Address 0x00) (see Table 13).

#### Table 13. Registers

| Register<br>Address | Description                                       | Power-On<br>Default |  |  |  |  |  |

|---------------------|---------------------------------------------------|---------------------|--|--|--|--|--|

| 0x00                | Temperature value most significant byte           | 0x00                |  |  |  |  |  |

| 0x01                | Temperature value least significant byte          | 0x00                |  |  |  |  |  |

| 0x02                | Status                                            | 0x00                |  |  |  |  |  |

| 0x03                | Configuration                                     | 0x00                |  |  |  |  |  |

| 0x04                | THIGH setpoint most significant byte              | 0x20 (64°C)         |  |  |  |  |  |

| 0x05                | T <sub>HIGH</sub> setpoint least significant byte | 0x00 (64°C)         |  |  |  |  |  |

| 0x06                | T <sub>LOW</sub> setpoint most significant byte   | 0x05 (10°C)         |  |  |  |  |  |

| 0x07                | TLOW setpoint least significant byte              | 0x00 (10°C)         |  |  |  |  |  |

| 0x08                | T <sub>CRIT</sub> setpoint most significant byte  | 0x49 (147°C)        |  |  |  |  |  |

| 0x09                | TCRIT setpoint least significant byte             | 0x80 (147°C)        |  |  |  |  |  |

| 0x0A                | T <sub>HYST</sub> setpoint                        | 0x05 (5°C)          |  |  |  |  |  |

| 0x0B                | ID                                                | 0xCB                |  |  |  |  |  |

| 0x0C                | Reserved                                          | 0xXX                |  |  |  |  |  |

| 0x0D                | Reserved                                          | 0xXX                |  |  |  |  |  |

| 0x2E                | Reserved                                          | 0xXX                |  |  |  |  |  |

| 0x2F                | Software reset                                    | 0xXX                |  |  |  |  |  |

#### ADDRESS POINTER REGISTER

The address pointer register is always the first register written to during a write to the ADT7422. Set the address point register to the address of the register to which the write or read transaction is intended. Table 13 shows the register address of each register on the ADT7422. The default value of the address pointer register is 0x00.

#### Table 14. Address Pointer Register

| P7   | P6   | P5   | P4   | P3   | P2   | P1   | P0   |

|------|------|------|------|------|------|------|------|

| ADD7 | ADD6 | ADD5 | ADD4 | ADD3 | ADD2 | ADD1 | ADD0 |

#### **TEMPERATURE VALUE REGISTERS**

The temperature value consists of two bytes, one most significant byte and one least significant byte. These values can be read in two separate 1-byte reads or in a single 2-byte read. Only the address of the most significant byte must be loaded into the address pointer register for a 2-byte read. After the most significant byte is read, the address pointer is auto-incremented so that the least significant byte can be read within the same transaction.

Bit 0 to Bit 2 are event alarm flags for the  $T_{\rm LOW}$ ,  $T_{\rm HIGH}$ , and  $T_{\rm CRIT}$  setpoint most significant byte registers and least significant byte registers. When the ADC is configured to convert the temperature to a 16-bit digital value, Bit 0 to Bit 2 are no longer used as flag bits and are used as the LSBs for the extended digital value instead.

#### Table 15. Temperature Value Most Significant Byte Register (Register Address 0x00)

| Bit    | Default Value | Туре | Name | Description                                                          |

|--------|---------------|------|------|----------------------------------------------------------------------|

| [14:8] | 0000000       | R    | Temp | Temperature value in twos complement format                          |

| 15     | 0             | R    | Sign | Sign bit, indicates if the temperature value is negative or positive |

#### Table 16. Temperature Value Least Significant Byte Register (Register Address 0x01)

| Bit   | Default<br>Value | Туре | Name                        | Description                                                                                                                                                                                 |

|-------|------------------|------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | 0                | R    | T <sub>LOW</sub> flag/LSB0  | Flags a $T_{LOW}$ event if the configuration register, Register Address 0x03, Bit 7 = 0 (13-bit resolution). When the temperature value is below $T_{LOW}$ , this bit is set to 1.          |

|       |                  |      |                             | Contains the least significant bit, Bit 0, of the 15-bit temperature value if the configuration register, Register Address 0x03, Bit 7 = 1 (16-bit resolution).                             |

| 1     | 0                | R    | Т <sub>нібн</sub> flag/LSB1 | Flags a T <sub>HIGH</sub> event if the configuration register, Register Address 0x03, Bit 7 = 0 (13-bit resolution). When the temperature value is above $T_{HIGH}$ , this bit is set to 1. |

|       |                  |      |                             | Contains the least significant bit, Bit 1, of the 15-bit temperature value if the configuration register, Register Address 0x03, Bit 7 = 1 (16-bit resolution).                             |

| 2     | 0                | R    | T <sub>CRIT</sub> flag/LSB2 | Flags a $T_{CRIT}$ event if the configuration register, Register Address 0x03, Bit 7 = 0 (13-bit resolution). When the temperature value exceeds $T_{CRIT}$ , this bit is set to 1.         |

|       |                  |      |                             | Contains the least significant bit, Bit 2, of the 15-bit temperature value if the configuration register, Register Address 0x03, Bit $7 = 1$ (16-bit resolution).                           |

| [7:3] | 00000            | R    | Temp                        | Temperature value in twos complement format.                                                                                                                                                |

#### **STATUS REGISTER**

This 8-bit read only register reflects the status of the overtemperature and undertemperature interrupts that can cause the CT pin and INT pin to go active. The status register also reflects the status of a temperature conversion operation. The interrupt flags in this register are reset by a read operation to the status register and/or when the temperature value returns within the temperature limits, including hysteresis. The  $\overline{\text{RDY}}$  bit is reset after a read from the temperature value registers. In one shot mode and 1 SPS mode, the  $\overline{\text{RDY}}$  bit is reset after a write to the operation mode bits in the configuration register.

#### **CONFIGURATION REGISTER**

This 8-bit read/write register stores various configuration modes for the ADT7422, including shutdown mode, overtemperature and undertemperature interrupts, one shot mode, continuous conversion mode, interrupt pins polarity, and overtemperature fault queues.

| Bit   | Default<br>Value | Туре | Name              | Description                                                                                                                                                                                                                                                                                   |

|-------|------------------|------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [3:0] | 0000             | R    | Unused            | Reads back 0.                                                                                                                                                                                                                                                                                 |

| 4     | 0                | R    | TLOW              | This bit is set to 1 when the temperature goes below the $T_{LOW}$ temperature limit. The bit clears to 0 when the status register is read and/or when the temperature measured goes back above the limit set in the setpoint $T_{LOW} + T_{HYST}$ registers.                                 |

| 5     | 0                | R    | Тнібн             | This bit is set to 1 when the temperature goes above the $T_{HIGH}$ temperature limit. The bit clears to 0 when the status register is read and/or when the temperature measured goes back below the limit set in the setpoint $T_{HIGH} - T_{HYST}$ registers.                               |

| 6     | 0                | R    | T <sub>CRIT</sub> | This bit is set to 1 when the temperature goes above the $T_{CRIT}$ temperature limit. This bit clears to 0 when the status register is read and/or when the temperature measured goes back below the limit set in the setpoint $T_{CRIT} - T_{HYST}$ registers.                              |

| 7     | 1                | R    | RDY               | This bit goes low when the temperature conversion result is written into the temperature value register. It is reset to 1 when the temperature value register is read. In one shot and 1 SPS modes, this bit is reset after a write to the operation mode bits in the configuration register. |

#### Table 17. Status Register (Register Address 0x02)

| Table 18. Configu | uration Register | (Register A  | Address 0x03) |

|-------------------|------------------|--------------|---------------|

| Tuble 10. Comig   | aracion regioter | (Itegioter I | iaareoo onooj |

| Bit   | Default<br>Value | Туре | Name             | Description                                                                                                                                                                                   |

|-------|------------------|------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                  |      |                  |                                                                                                                                                                                               |

| [1:0] | 00               | R/W  | Fault queue      | These two bits set the number of undertemperature/overtemperature faults that can occur before setting the INT pin and CT pin. This helps to avoid false triggering due to temperature noise. |

|       |                  |      |                  | 00 = 1 fault (default).                                                                                                                                                                       |

|       |                  |      |                  | 01 = 2 faults.                                                                                                                                                                                |

|       |                  |      |                  | 10 = 3 faults.                                                                                                                                                                                |

|       |                  |      |                  | 11 = 4 faults.                                                                                                                                                                                |

| 2     | 0                | R/W  | CT pin polarity  | This bit selects the output polarity of the CT pin.                                                                                                                                           |

|       |                  |      |                  | 0 = active low.                                                                                                                                                                               |

|       |                  |      |                  | 1 = active high.                                                                                                                                                                              |

| 3     | 0                | R/W  | INT pin polarity | This bit selects the output polarity of the INT pin.                                                                                                                                          |

|       |                  |      |                  | 0 = active low.                                                                                                                                                                               |

|       |                  |      |                  | 1 = active high.                                                                                                                                                                              |

| 4     | 0                | R/W  | INT/CT mode      | This bit selects between comparator mode and interrupt mode.                                                                                                                                  |

|       |                  |      |                  | 0 = interrupt mode.                                                                                                                                                                           |

|       |                  |      |                  | 1 = comparator mode.                                                                                                                                                                          |

| [6:5] | 00               | R/W  | Operation mode   | These two bits set the operational mode for the ADT7422.                                                                                                                                      |

|       |                  |      |                  | 00 = continuous conversion (default). When one conversion is finished, the ADT7422 starts another.                                                                                            |

|       |                  |      |                  | 01 = one shot. Conversion time is typically 240 ms.                                                                                                                                           |

|       |                  |      |                  | 10 = 1 SPS mode. Conversion time is typically 60 ms. This operational mode reduces the average current consumption.                                                                           |

|       |                  |      |                  | 11 = shutdown. All circuitry except interface circuitry is powered down.                                                                                                                      |

| 7     | 0                | R/W  | Resolution       | This bit sets up the resolution of the ADC when converting.                                                                                                                                   |

|       |                  |      |                  | 0 = 13-bit resolution. Sign bit + 12 bits gives a temperature resolution of 0.0625°C.                                                                                                         |

|       |                  |      |                  | 1 = 16-bit resolution. Sign bit + 15 bits gives a temperature resolution of 0.0078°C.                                                                                                         |

#### T<sub>HIGH</sub> SETPOINT REGISTERS

The  $T_{HIGH}$  setpoint most significant byte register and the  $T_{HIGH}$  setpoint least significant byte register store the overtemperature limit value. An overtemperature event occurs when the temperature value stored in the temperature value register exceeds the value stored in this register. The INT pin is activated if an overtemperature event occurs. The temperature is stored in twos complement format with the most significant byte being the temperature sign bit.

When reading from this register, the 8 MSBs (Bit 15 to Bit 8) are read first from Register Address 0x04, and then the 8 LSBs (Bit 7 to Bit 0) are read from Register Address 0x05 ( $T_{HIGH}$  setpoint least significant byte register). Only Register Address 0x04 ( $T_{HIGH}$  setpoint most significant byte register) must be loaded into the address pointer register because the address pointer auto-increments to Register Address 0x05 ( $T_{HIGH}$  setpoint least significant byte register).

The default setting for the T<sub>HIGH</sub> setpoint register is 64°C.

#### **TLOW SETPOINT REGISTERS**

The  $T_{LOW}$  setpoint most significant byte register and the  $T_{LOW}$  setpoint least significant byte register store the undertemperature limit value. An undertemperature event occurs when the temperature value stored in the temperature value register is less than the value stored in this register. The INT pin is

activated if an undertemperature event occurs. The temperature is stored in twos complement format with the MSB being the temperature sign bit.

When reading from this register, the 8 MSBs (Bit 15 to Bit 8) are read first from Register Address 0x06 and then the 8 LSBs (Bit 7 to Bit 0) are read from Register Address 0x07. Only Register Address 0x06 ( $T_{LOW}$  setpoint most significant byte register) must be loaded into the address pointer register because the address pointer auto-increments to Register Address 0x07 ( $T_{LOW}$  setpoint least significant byte register).

The default setting for the T<sub>LOW</sub> setpoint register is 10°C.

#### T<sub>HYST</sub> SETPOINT REGISTER

This 8-bit read/write register stores the temperature hysteresis value for the  $T_{HIGH}$ ,  $T_{LOW}$ , and  $T_{CRIT}$  temperature limits. The temperature hysteresis value is stored in straight binary format using the four LSBs. Increments are possible in steps of 1°C from 0°C to 15°C. The value in this register is subtracted from the  $T_{HIGH}$  and  $T_{CRIT}$  values and added to the  $T_{LOW}$  value to implement hysteresis.

#### **ID REGISTER**

This 8-bit read only register stores the manufacture ID in Bit 3 to Bit 7 and the silicon revision in Bit 0 to Bit 2. The default setting for the ID register is 0xCB.

| Bit   | Default Value | Туре | Name              | Description                                                                                       |  |  |  |  |  |  |

|-------|---------------|------|-------------------|---------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| [3:0] | 0101          | R/W  | T <sub>HYST</sub> | Hysteresis value, from 0°C to 15°C. Stored in straight binary format. The default setting is 5°C. |  |  |  |  |  |  |

| [7:4] | 0000          | R/W  | Not applicable    | Not used.                                                                                         |  |  |  |  |  |  |

| Bit   | Default Value | Default Value Type Name |                | Description                                          |  |  |

|-------|---------------|-------------------------|----------------|------------------------------------------------------|--|--|

| [2:0] | 011           | R                       | Revision ID    | Contains the silicon revision identification number. |  |  |

| [7:3] | 11001         | R                       | Manufacture ID | Contains the manufacture identification number.      |  |  |

## **SERIAL INTERFACE**

Control of the ADT7422 is carried out via the I<sup>2</sup>C-compatible serial interface. The ADT7422 is connected to this bus as a slave and is under the control of a master device.

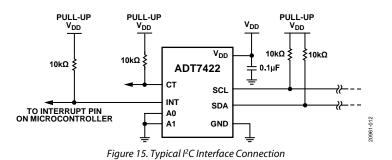

Figure 15 shows a typical I<sup>2</sup>C interface connection.

#### SERIAL BUS ADDRESS

Like most I<sup>2</sup>C-compatible devices, the ADT7422 has a 7-bit serial address. The five MSBs of this address for the ADT7422 are hardwired internally to 10010. Pin A1 and Pin A0 set the two LSBs. These pins can be configured two ways, low and high, to give four different address options. Table 21 shows the different bus address options available. The recommended pull-up resistor value on the SDA and SCL lines is 10 k $\Omega$ .

#### Table 21. I<sup>2</sup>C Bus Address Options

| A6 | A5 | A4 | A3 | A2 | A1 | A0 | Hexadecimal |

|----|----|----|----|----|----|----|-------------|

| 1  | 0  | 0  | 1  | 0  | 0  | 0  | 0x48        |

| 1  | 0  | 0  | 1  | 0  | 0  | 1  | 0x49        |

| 1  | 0  | 0  | 1  | 0  | 1  | 0  | 0x4A        |

| 1  | 0  | 0  | 1  | 0  | 1  | 1  | 0x4B        |

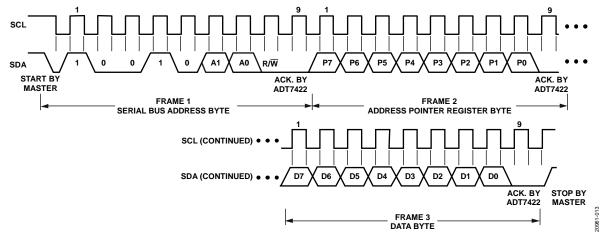

The serial bus protocol operates as follows:

1. The master establishes a start condition to initiate data transfer, defined as a high to low transition on the serial data line (SDA) while the serial clock line (SCL) remains high. The start condition indicates that an address and data stream follow. All slave peripherals connected to the serial bus respond to the start condition and shift in the next 8 bits consisting of a 7-bit address (MSB first) plus a read/write (R/W) bit. The R/W bit determines whether data is written to or read from the slave device.

- 2. The peripheral with the address corresponding to the transmitted address responds by pulling the data line low during the low period before the ninth clock pulse known as the acknowledge bit. All other devices on the bus then remain idle while the selected device waits for data to be read from or written to it. If the  $R/\overline{W}$  bit is set to 0, the master writes to the slave device. If the  $R/\overline{W}$  bit is set to 1, the master reads from the slave device.

- 3. Data is sent over the serial bus in sequences of nine clock pulses 8 bits of data followed by an acknowledge bit from the receiver of data. Transitions on the data line must occur during the low period of the clock signal and remain stable during the high period as a low to high transition when the clock is high, which can be interpreted as a stop signal.

- 4. When all data bytes have been read or written, stop conditions are established. In write mode, the master pulls the data line high during the 10<sup>th</sup> clock pulse to assert a stop condition. In read mode, the master device pulls the data line high during the low period before the ninth clock pulse. This is known as a no acknowledge. The master first takes the data line low during the low period before the 10<sup>th</sup> clock pulse, then high during the 10<sup>th</sup> clock pulse to assert a stop condition.

It is not possible to mix reads and writes in one operation because the type of operation is determined at the beginning of the process and cannot subsequently be changed without starting a new operation.

#### WRITING DATA

It is possible to write either a single byte of data or two bytes of data to the ADT7422, depending on which registers are to be written.

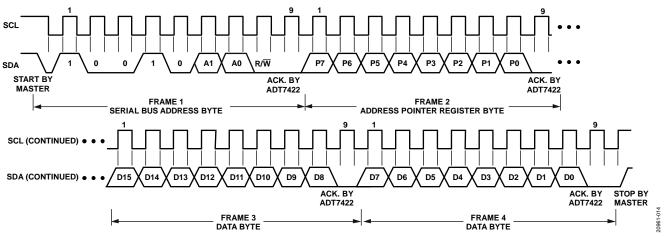

Writing a single byte of data requires the serial bus address (the data register address that is written to the address pointer register) followed by the data byte written to the selected data register. This sequence is shown in Figure 16.

For the  $T_{HIGH}$  setpoint,  $T_{LOW}$  setpoint, and  $T_{CRIT}$  setpoint registers, it is possible to write to both the most significant byte

and the least significant byte registers in the same write transaction. Writing two bytes of data to these registers requires the serial bus address (the data register address of the most significant byte register that is written to the address pointer register) followed by the two data bytes written to the selected data register. This sequence is shown in Figure 17.

If more than the required number of data bytes is written to a register, the register ignores these extra data bytes. A start or repeated start is required to write to a different register.

Figure 16. Writing to a Register Followed by a Single Byte of Data

Figure 17. Writing to a Register Followed by Two Bytes of Data

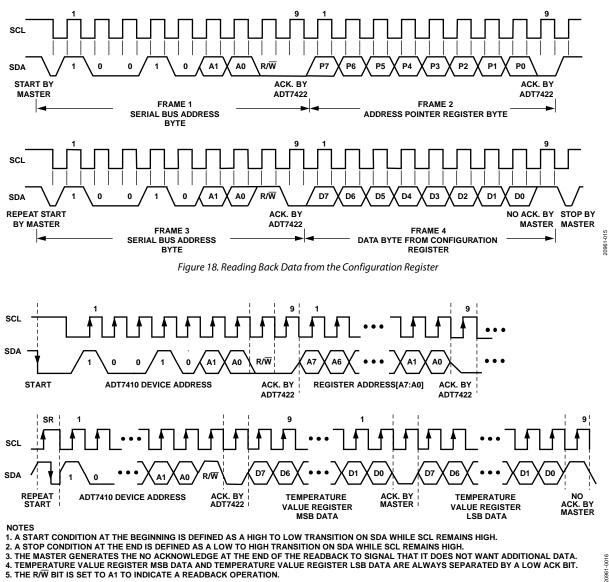

#### **READING DATA**

Reading data from the ADT7422 is done in a single-byte data operation for the configuration register, the status register, the T<sub>HYST</sub> setpoint register, and the ID register. A two-byte data read operation is needed for the temperature value register, T<sub>HIGH</sub> setpoint register, T<sub>LOW</sub> setpoint register, and the T<sub>CRIT</sub> setpoint register. Reading back the contents of the 8-bit configuration register is shown in Figure 18. Reading back the contents of the temperature value register is shown in Figure 19.

Reading back from any register first requires a single-byte write operation to the address pointer register. This operation sets up the address of the register that is going to be read from. In the

case of reading back from the 2-byte registers, the address pointer automatically increments from the most significant byte register address to the least significant byte register address.

To read from another register, execute another write to the address pointer register to set up the relevant register address. Therefore, block reads are not possible because there is no I<sup>2</sup>C address pointer auto-increment except when reading back from a 16-bit register. If the address pointer register has previously been set up with the address of the register that is going to receive a read command, there is no need to repeat a write operation to set up the register address again.

3. THE MASTER GENERATES THE NO ACKNOWLEDGE AT THE END OF THE READBACK TO SIGNAL THAT IT DOES NOT WANT ADDITIONAL DATA. A TEMPERATURE VALUE REGISTER MSB DATA AND TEMPERATURE VALUE REGISTER LSB DATA ARE ALWAYS SEPARATED BY A LOW ACK BIT. 5. THE R/W BIT IS SET TO A1 TO INDICATE A READBACK OPERATION.

Figure 19. Reading Back Data from the Temperature Value Register

#### RESET

To reset the ADT7422 without having to reset the entire  $I^2C$  bus, an explicit reset command is provided. This command uses a particular address pointer word as a command word to reset the device and upload all default settings. The ADT7422 does not respond to (does not acknowledge) the  $I^2C$  bus commands while the default values upload for approximately 200 µs. Use the following sequence to perform a reset:

- 1. Write to the ADT7422 using the appropriate address.

- 2. Read the acknowledge bit.

- 3. Set the register address to 0x2F.

- 4. Read the acknowledge bit.

- 5. Apply stop condition.

- 6. Wait 200 μs for the device to reset the registers to the default power-up settings.

#### **GENERAL CALL**

When a master issues a slave address consisting of seven 0s with the 8<sup>th</sup> bit ( $R/\overline{W}$  bit) set to 0, the address is known as the general call address. The general call address is for addressing every device connected to the I<sup>2</sup>C bus. The ADT7422 acknowledges this address and reads in the following data byte.

If the second byte is 0x06, the ADT7422 resets completely and uploads all default values. The ADT7422 does not respond to (does not acknowledge) the  $I^2C$  bus commands while the default values upload for approximately 200  $\mu$ s.

The ADT7422 does not acknowledge any other general call commands.

## INT AND CT OUTPUTS

The INT pin and CT pin are open-drain outputs, and both require a 10 k $\Omega$  pull-up resistor to V<sub>DD</sub>. The ADT7422 must be fully powered up to V<sub>DD</sub> before reading the INT and CT data.

## UNDERTEMPERATURE AND OVERTEMPERATURE DETECTION

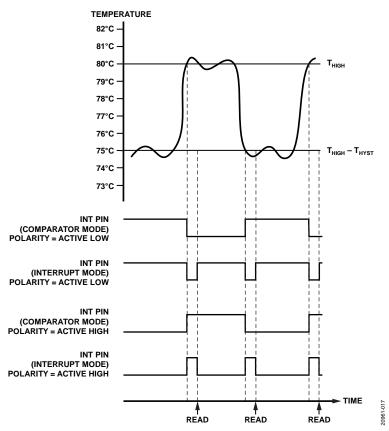

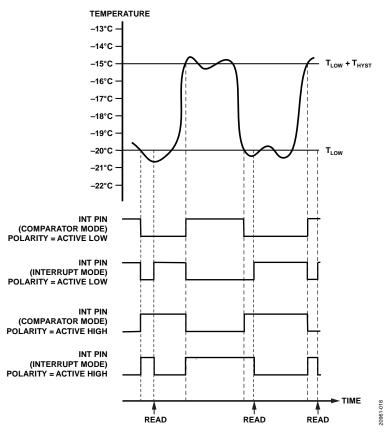

The INT pin and CT pin have two undertemperature/overtemperature modes: comparator mode and interrupt mode. The interrupt mode is the default power-up overtemperature mode. The INT output pin becomes active when the temperature is greater than the temperature stored in the  $T_{\rm HIGH}$  setpoint register or less than the temperature stored in the  $T_{\rm LOW}$  setpoint register. How the INT pin reacts after this event depends on the overtemperature mode selected.

Figure 20 shows the comparator and interrupt modes for events exceeding the  $T_{HIGH}$  limit with both pin polarity settings. Figure 21 shows the comparator and interrupt modes for events exceeding the  $T_{LOW}$  limit with both pin polarity settings.

#### **Comparator Mode**

In comparator mode, the INT pin returns to inactive status when the temperature drops below the  $T_{\rm HIGH}$  –  $T_{\rm HYST}$  limit or rises above the  $T_{\rm LOW}$  +  $T_{\rm HYST}$  limit.

Placing the ADT7422 in shutdown mode does not reset the INT state in comparator mode.

#### Interrupt Mode

In interrupt mode, the INT pin goes inactive when any ADT7422 register is read. When the INT pin is reset, it only goes active again when the temperature is either greater than the temperature stored in the  $T_{\rm HIGH}$  setpoint register, or less than the temperature stored in the  $T_{\rm LOW}$  setpoint register.

Placing the ADT7422 in shutdown mode resets the INT pin in interrupt mode.

Figure 20. INT Output Temperature Response Diagram for T<sub>HIGH</sub> Overtemperature Events

Figure 21. INT Output Temperature Response Diagram for  $T_{LOW}$  Undertemperature Events

## APPLICATIONS INFORMATION THERMAL RESPONSE TIME

Thermal response is a function of the thermal mass of the temperature sensor and is heavily influenced by the mass of the object the IC is mounted to. For example, a large PCB containing large amounts of copper tracking can act as a large heat sink and slow the thermal response. For a faster thermal response, it is recommended to mount the sensor on the smallest PCB possible.

Figure 11 shows the typical response time of less than two seconds to reach 63.2% of the temperature span. The temperature value is read back as a 16-bit value through the digital interface. The response time includes all delays incurred on the chip during signal processing.

#### SUPPLY DECOUPLING

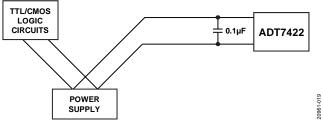

The ADT7422 must have a decoupling capacitor connected between  $V_{\rm DD}$  and GND. Otherwise, incorrect temperature readings are obtained. A 0.1  $\mu F$  decoupling capacitor, such as a high frequency ceramic type, must be used and mounted as close as possible to the  $V_{\rm DD}$  pin of the ADT7422.

If possible, power the ADT7422 directly from the system power supply. This arrangement, shown in Figure 22, isolates the analog section from the logic-switching transients. If a separate power supply trace is not available, generous supply bypassing still reduces supply line induced errors. Local supply bypassing consisting of a 0.1  $\mu$ F ceramic capacitor is critical for the temperature accuracy specifications to be achieved.

Figure 22. Use of Separate Traces to Reduce Power Supply Noise

#### **POWERING FROM A SWITCHING REGULATOR**

Precision analog devices such as the ADT7422 require a well filtered power source. If the ADT7422 is powered from a switching regulator, noise may be generated above 50 kHz that can affect the temperature accuracy specifications. To prevent this issue, use an RC filter between the power supply and the ADT7422 V<sub>DD</sub> pin. Carefully consider the value of the components used to ensure that the peak value of the supply noise is less than 1 mV. Mount the RC filter as far away from the ADT7422 as possible to ensure that the thermal mass is kept as low as possible.

#### **TEMPERATURE MEASUREMENT**

The ADT7422 accurately measures and converts the temperature at the surface of the semiconductor chip. Thermal paths run through the leads, the exposed pad, and the plastic package. When the ADT7422 is used to measure the temperature of a nearby heat source, the thermal impedance between the heat source and the ADT7422 must be considered because it impacts the accuracy and thermal response of the measurement.