# 8-Lead SOIC Amplifier Evaluation Board User Guide

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

### **Universal Evaluation Board for Single, 8-Lead SOIC Operational Amplifiers**

### **FEATURES**

Enables quick breadboarding/prototyping

User defined circuit configuration

Edge mounted Subminiature Version A (SMA) connector

provisions

Easy connection to test equipment and other circuits

#### **GENERAL DESCRIPTION**

The SO8 SINGLE AMP evaluation board aids in the evaluation of single, 8-lead SOIC operational amplifiers. The SO8 SINGLE AMP evaluation board is a bare board with no components soldered on, which enables users to prototype a variety of operational amplifier circuits. The SO8 SINGLE AMP evaluation board supports any of the Analog Devices, Inc., single operational amplifiers in 8-lead SOIC packages with and without a dedicated feedback pin, an exposed paddle, and an external compensation pin.

The 6-layer evaluation board accepts edge mounted SMA connectors on both inputs and outputs to allow an efficient connection to test equipment and other circuitry.

Optimized power and ground planes ensure low noise and high speed operation. Component placement and power supply bypassing are optimized for maximum circuit flexibility and performance. The evaluation board accepts 0402 or 0603 surfacemount technology (SMT) components, 1206 bypass capacitors, and 100 mil headers.

All components are placed on the primary side. No components are placed on the secondary side.

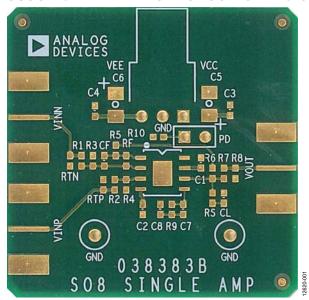

### **SO8 SINGLE AMP EVALUATION BOARD IMAGES**

Figure 1. SO8 SINGLE AMP Evaluation Board, Primary Side

Figure 2. SO8 SINGLE AMP Evaluation Board, Secondary Side

### UG-755

## 8-Lead SOIC Amplifier Evaluation Board User Guide

### **TABLE OF CONTENTS**

| Features                                       | 1 |

|------------------------------------------------|---|

| General Description                            | 1 |

| SO8 SINGLE AMP Evaluation Board Images         | 1 |

| Revision History                               | 2 |

| Schematic, Assembly Drawings, and Board Layout | 3 |

| Board Assembly                                 | 4 |

| Amplifiers with No Dedicated Feedback Pin      | 4 |

| REVISION HISTORY                               |   |

| 8/2020—Rev. 0 to Rev. A                        |   |

| Changes to Figure 3                            | 3 |

| Amplifiers with De  | edicated Feedback Pin  | 4 |

|---------------------|------------------------|---|

| Amplifiers with Ext | ernal Compensation Pin | 4 |

| -                   | assing                 |   |

| 11                  | Stack-Up               |   |

|                     | n                      |   |

| Rill of Materials   |                        | 5 |

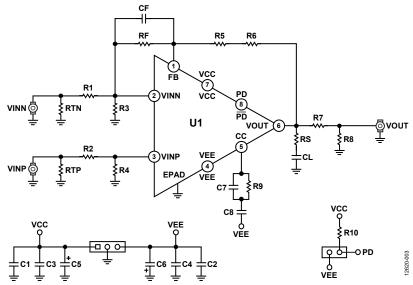

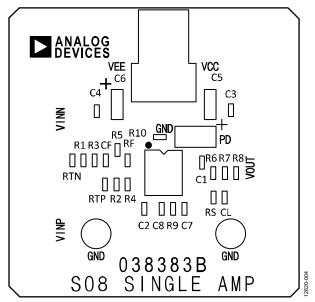

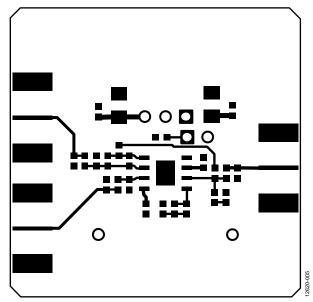

### SCHEMATIC, ASSEMBLY DRAWINGS, AND BOARD LAYOUT

Figure 3. SO8 SINGLE AMP Evaluation Board Schematic

Figure 4. Board Assembly Drawing, Primary Side

Figure 5. Board Layout Pattern, Primary Side

### **BOARD ASSEMBLY**

### **AMPLIFIERS WITH NO DEDICATED FEEDBACK PIN**

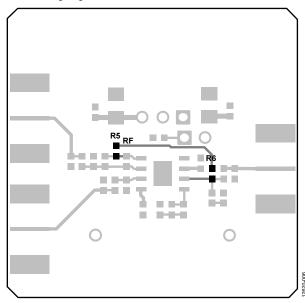

Pin 1 of these amplifiers is a no connect (NC). Place 0  $\Omega$  resistors at locations R5 and R6 to complete the external path from the output pin, Pin 6, to the feedback resistor, RF.

Figure 6. External Feedback Connections

### **AMPLIFIERS WITH DEDICATED FEEDBACK PIN**

High speed amplifiers with a dedicated feedback pin provide an internal connection between the output pin, Pin 6, and the feedback pin, Pin 1. To ensure optimum performance, do not install R5 and R6.

### **AMPLIFIERS WITH EXTERNAL COMPENSATION PIN**

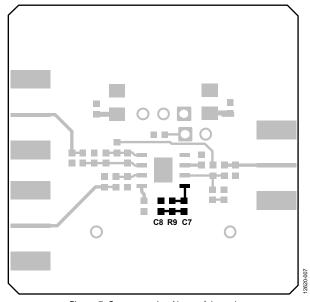

Pin 5 of these amplifiers accepts an external compensation network. The compensation network is referenced to the VEE pin.

Figure 7. Compensation Network Location

### **POWER SUPPLY BYPASSING**

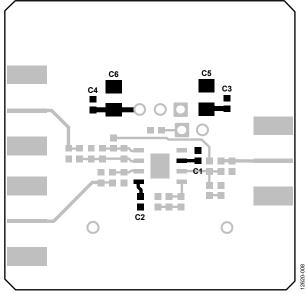

Internal power planes provide adequate interplanar capacitance for certain applications. External bypass capacitors, C1 and C2, provide additional high frequency bypassing at the amplifier power pins. The C3, C4, C5, and C6 Capacitors provide additional board level bypassing.

Figure 8. Bypass Capacitor Locations

### **EVALUATION BOARD STACK-UP**

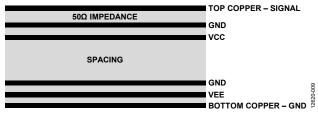

This 6-layer FR4 board design provides optimized high speed and low noise performance. First ground layer is spaced to provide 50  $\Omega$  controlled impedance with the primary layer to optimize high frequency performance.

The VCC layer is sandwiched with the GND layer to provide mechanical stability and distributed interplanar capacitance between VCC and GND.

The bottom three layers sandwich the VEE plane layers between two GND layers, generating distributed interplanar capacitance.

Figure 9. Stack-Up