# EVM3820-QV-00A

6V Input, 1.2 MHz, 2A Module Synchronous Step-Down Converter with Integrated Inductor Evaluation Board

#### DESCRIPTION

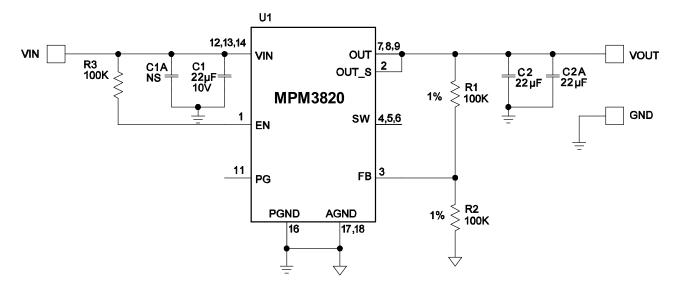

EVM3820-QV-00A The is used for demonstrating the performance of MPS's MPM3820 a low voltage high switching frequency step-down switcher with built-in power MOSFETs and power inductor. MPM3820 provides up to 2A continuous highly efficient output with constant-on-time control for fast loop response.

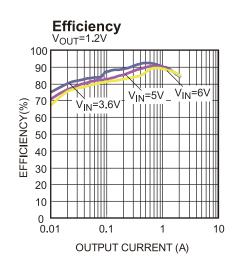

High power efficiency over a wide load range is achieved by scaling down the switching frequency at light load to reduce the switching related loss by constant on time control. Short circuit and thermal shutdown provides reliable, fault-tolerant operation.

MPM3820 is available in QFN 3.0x5.0x1.6mm package.

#### **ELECTRICAL SPECIFICATION**

| Parameter      | Symbol           | Value | Units |

|----------------|------------------|-------|-------|

| Input Voltage  | V <sub>IN</sub>  | 2.7-6 | V     |

| Output Voltage | V <sub>OUT</sub> | 1.2   | V     |

| Output Current | I <sub>OUT</sub> | 2     | Α     |

### **FEATURES**

- Wide 2.7V to 6V Operating Input Range

- Fixed and Adjustable Output from 0.6V

- 3.0mm x 5.0mm x 1.6mm QFN Package

- Total Solution Size 8.5mm x 4.5 mm

- Up to 2A Continuous Output Current

- 100% Duty Cycle in Dropout

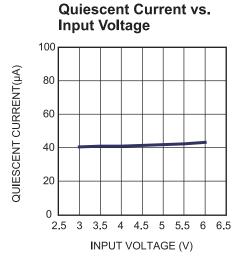

- Ultra Low IQ: 40µA

- EN and Power Good for Power Sequencing

- Cycle-by-Cycle Over-Current Protection

- Short Circuit Protection with Hiccup Mode

- Adjustable Output Only Needs 4 External Components - 2 Ceramic Capacitors and FB Divider Resistors

- Fixed Output Only Needs Input and Output Capacitors

#### **APPLICATIONS**

- Low Voltage I/O System Power

- LDO Replacement

- Power for Portable Products

- Storage (SSD/HDD)

- Space-limited Applications

All MPS parts are lead-free and adhere to the RoHS directive. For MPS green status, please visit MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology", are Registered Trademarks of Monolithic Power Systems, Inc.

#### EVM3820-QV-00A EVALUATION BOARD

| Board Number   | MPS IC Number |  |  |

|----------------|---------------|--|--|

| EVM3820-QV-00A | MPM3820GQV    |  |  |

### **EVALUATION BOARD SCHEMATIC**

### **EVM3820-QV-00A BILL OF MATERIALS**

| Qty | RefDes     | Value | Description            | Package        | Manufacturer | Manufacturer P/N |

|-----|------------|-------|------------------------|----------------|--------------|------------------|

| 3   | C1, C2,C2A | 22µF  | Ceramic Cap., 10V, X5R | SM0805         | TDK          | C2012X5R1A226K   |

| 0   | C1A        | NS    |                        |                |              |                  |

| 1   | R1         | 100k  | Film Res., 1%          | SM0603         | Any          |                  |

| 1   | R2         | 100k  | Film Res.,1%           | SM0603         | Any          |                  |

| 1   | R3         | 100k  | Film Res., 5%          | SM0603         | Yageo        | RC0603FR-07100KL |

| 1   | U1         |       | COT Buck               | QFN<br>3.0*5.0 | MPS          | MPM3820GQV       |

### **EVB TEST RESULTS**

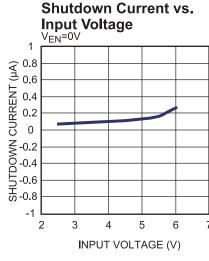

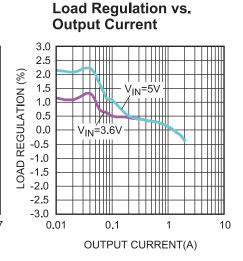

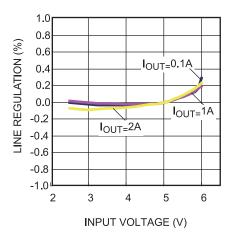

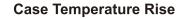

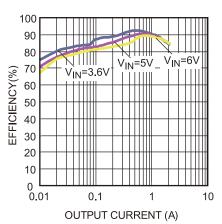

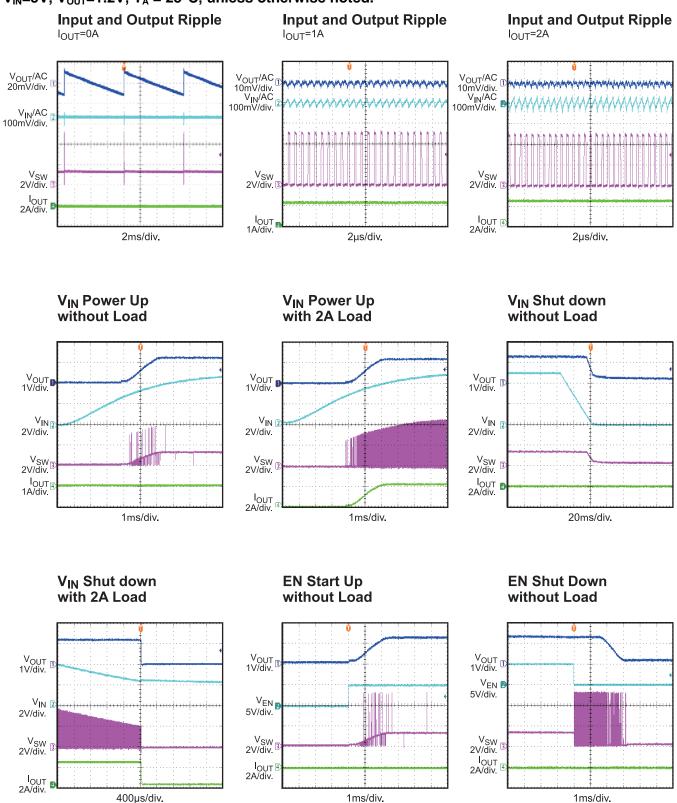

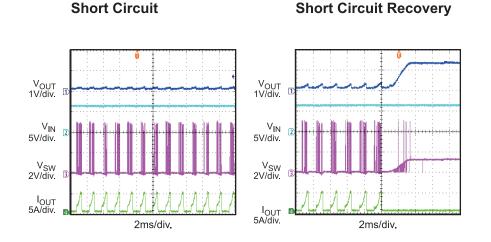

Performance waveforms are tested on the evaluation board.  $V_{\text{IN}}$ =5V,  $V_{\text{OUT}}$ =1.2V,  $T_{\text{A}}$  = 25°C, unless otherwise noted.

Line Regulation vs. Input Voltage

### Efficiency

# **EVB TEST RESULTS** (continued)

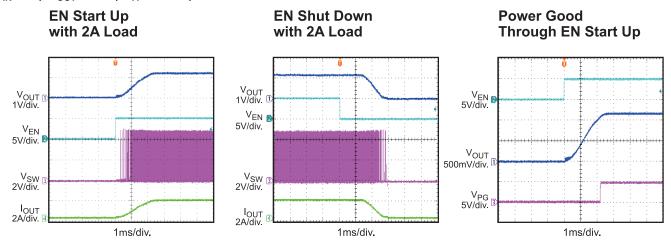

Performance waveforms are tested on the evaluation board.  $V_{IN}=5V$ ,  $V_{OUT}=1.2V$ ,  $T_A=25^{\circ}C$ , unless otherwise noted.

# **EVB TEST RESULTS** (continued)

Performance waveforms are tested on the evaluation board.  $V_{IN}$ =5V,  $V_{OUT}$ =1.2V,  $T_A$  = 25°C, unless otherwise noted.

© 2014 MPS. All Rights Reserved.

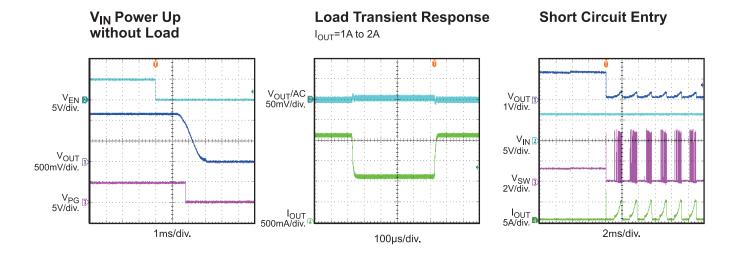

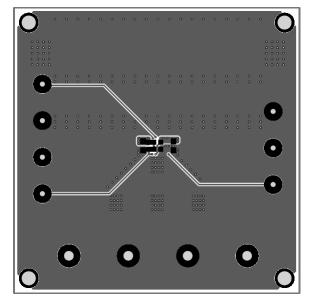

### PRINTED CIRCUIT BOARD LAYER

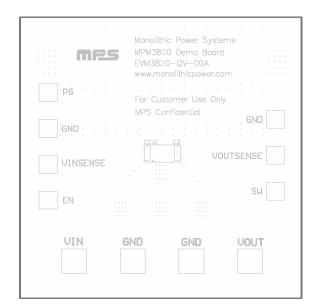

Figure 1: Top Silk Layer

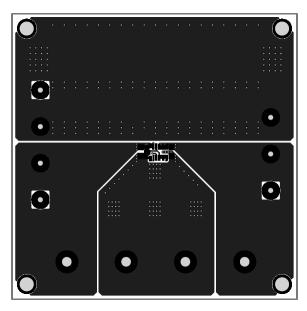

Figure 3: Bottom Silk Layer

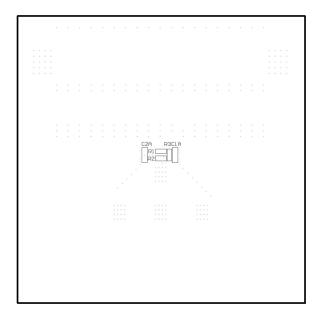

Figure 2: Top Layer

Figure 4: Bottom Layer