# 256 Kbit (32 K×8) 串行(I<sup>2</sup>C)F-RAM

### 特性

- 256 Kbit 铁电随机存储器(F-RAM)被逻辑组织为 32 K × 8 □ 高耐久性: 100 万亿(10<sup>14</sup>)次的读 / 写操作

- □ 151 年的数据保留时间 (请参考数据保留时间与耐久性表)

- □ NoDelay™ 写操作

- □可靠性较高的高级铁电工艺

- 快速的双线串行接口 (I<sup>2</sup>C)

- □ 最大频率为 3.4 MHz

- □可以直接替代串行 EEPROM 的器件

- □ 支持 100 kHz 和 400 kHz 频率的传统时序

- 器件 ID

- □制造商 ID 和产品 ID

- 低功耗

- □ 当频率为 100 kHz 时,活动电流为 175 mA

- □ 待机电流为 150 mA

- □ 睡眠模式电流为 8 mA

- 工作电压较低: V<sub>DD</sub> = 2.0 V 到 3.6 V

- 工业温度范围: -40 °C 到 +85 °C

- ■8引脚小外型集成电路 (SOIC) 封装

- 符合有害性物质限制 (RoHS)

### 功能概述

FM24V02A 是使用高级铁电工艺的 256 Kbit 非易失性存储器。 F-RAM 是非易失性的;与 RAM 相同,它能够执行读和写操作。 它提供 151 年的可靠数据保留时间,同时解决了由 EEPROM 和 其他非易失性存储器所造成的复杂性、开销和系统级可靠性等问 题。

与 EEPROM 不同,FM24V02A 以总线速度执行写操作。并不会产生写延迟。在每个字节成功传输到器件后,数据立即被写入到存储器阵列。这时,可以开始执行下一个总线周期而不需要数据轮询。此外,与其他非易失性存储器相比,该产品提供了更多的擦写次数。在写操作期间,F-RAM的功耗也远远低于 EEPROM,因为写电路不需要高电源电压。FM24V02A 能够支持 10<sup>14</sup> 读/写周期,或支持比 EEPROM 多 1 亿次的写周期。

由于具有这些特性,因此 FM24V02A 适用于需要频繁或快速写入的非易失性存储器应用。应用的范围包括从数据采集(其中写周期数量是非常重要的)到满足工业控制(其中 EEPROM 的较长写时间会使数据丢失)。通过各特性的组合,系统可以更频繁地进行数据写入而只需要较少的开销。

FM24V02A 使用硬件直接替代串行(I2C) EEPROM 时,可为用户带来极大的方便。该器件包含一个只读的器件 ID,通过该ID,主机可以确定制造商、产品容量和产品版本。在 -40 °C 到+85 °C 的工业温度范围内,该器件规范受保证。

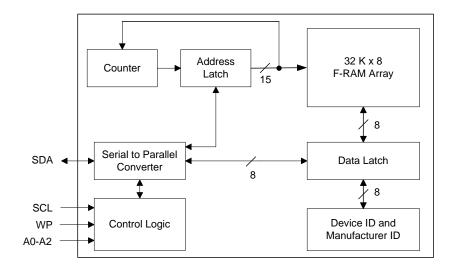

# 逻辑框图

# 目录

| 引脚分配         | 3  |

|--------------|----|

| 引脚定义         |    |

| 概述           |    |

| 存储器架构        | 4  |

| 双线接口         | 4  |

| STOP事件(P)    | 4  |

| START事件(S)   |    |

| 数据/地址传输      | 5  |

| 确认/否认        | 5  |

| 高速模式(Hs模式)   | 6  |

| 从设备地址        | 6  |

| 寻址概述         | 6  |

| 数据传输         | 6  |

| 存储器操作        | 6  |

| 写操作          | 6  |

| 读操作          | 7  |

| 睡眠模式         | 9  |

| <b>界</b> 件ID | 10 |

| <b>冣</b> ᄌ铡疋伹 |    |

|---------------|----|

| 工作范围          | 11 |

| 直流电气特性        | 11 |

| 数据保留时间与耐久性    | 12 |

| 电容            | 12 |

| 热电阻           | 12 |

| 交流测试负载和波形     | 12 |

| 交流测试条件        | 12 |

| 交流开关特性        | 13 |

| 电源循环时序        | 14 |

| 订购信息          | 15 |

| 订购代码定义        | 15 |

| <b>时装图</b>    | 16 |

| 宿略语           | 17 |

| 文档规范          | 17 |

| 测量单位          | 17 |

| 文档修订记录页       | 18 |

| 当住 解压方安和注律信息  | 10 |

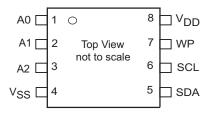

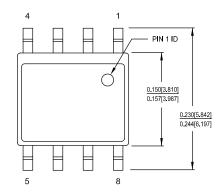

# 引脚分配

图 1. 8 引脚 SOIC 的引脚分配

# 引脚定义

| 引脚名称            | I/O 类型 | 说明                                                                                                            |

|-----------------|--------|---------------------------------------------------------------------------------------------------------------|

| A0-A2           | 输入     | 器件选择地址 0-2。使用这些引脚可选择同一个双线总线上最多 8 个相同类型器件中的一个。要选择器件,三个引脚的地址必须与从设备地址内的对应位相匹配。内部下拉地址引脚。                          |

| SDA             | 输入/输出  | <b>串行数据地址</b> 。这是双线接口的双向引脚。它是开漏引脚,用以与双线总线上其他器件执行 "与"运算。输入缓冲区包含一个用以实现抗噪能力的施密特触发器;输出驱动器包括下降沿的斜率控制。需要使用一个外部上拉电阻。 |

| SCL             | 输入     | <b>串行时钟</b> 。是指双线接口的串行时钟引脚。器件的数据从下降沿上输出,并从上升沿上输入。 <b>SCL</b> 输入也可包含一个用来实现抗噪能力的施密特触发器输入。                       |

| WP              | 输入     | <b>写保护</b> 。当与 $V_{DD}$ 连接时,整个存储器映射中的地址均受写保护。当 $WP$ 接地时,可对所有地址进行写操作。内部下拉该引脚。                                  |

| V <sub>SS</sub> | 电源     | 器件的接地引脚。必须连接至系统地面端。                                                                                           |

| $V_{DD}$        | 电源     | 器件的电源输入。                                                                                                      |

### 概述

FM24V02A 是一个串行的 F-RAM 存储器。该存储器阵列被逻辑组织为  $32,768 \times 8$  位,并可通过行业标准的双线( $I^2$ C)接口访问。F-RAM 和串行 EEPROM 的功能操作是相同的。FM24V02A与具有相同引脚分配的串行 EEPROM的主要区别在于 F-RAM 具有更好的写性能、高耐久性以及低功耗。

### 存储器架构

访问 FM24V02A 时,用户寻址每 8 个数据位的 32K 地址。这些 8 数据位被连续移入或移出。通过使用具有一个从设备地址(以 与其他非存储器设备区分开来)和一个 2 字节地址的双线协议,可以访问这些地址。该地址范围的高 MSB 位的值是 '无需关注'的。 15 位的完整地址独立指定每个字节的地址。

存储器的访问时间几乎为零,该时间小于串行协议所需要的时间。因此,该存储器以双线总线的速度进行读 / 写操作。与串行EEPROM 不同,不必轮询器件的就绪条件,因为写操作是以总

线速度进行的。新的总线数据操作移入器件前,需要完成写操作。第6页上的存储器操作中详细介绍了该功能。

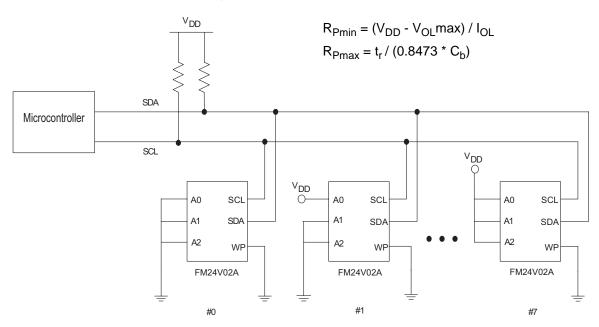

### 双线接口

FM24V02A采用了使用几个引脚或较少电路板空间的双向I2C总线协议。图2显示的是在基于微控制器系统上使用FM24V02A的典型系统配置。许多用户已对行业标准的双线总线很熟悉,但在本章节仍然对此进行了说明。

按约定,将数据发送到总线的任意设备称为发送器,而接收数据的目标设备称为接收器。控制总线的器件就是主设备。主设备负责给所有操作生成时钟信号。在总线上被控制的任何器件又称从设备。FM24V02A总是从设备。

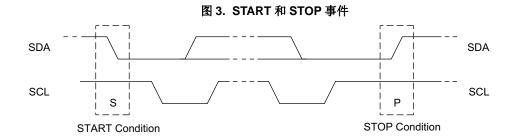

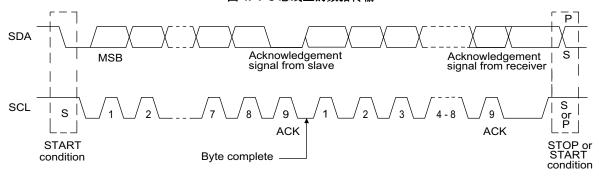

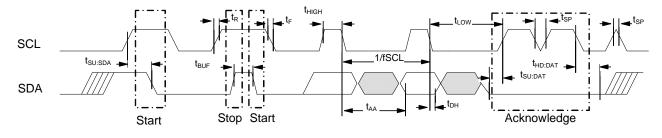

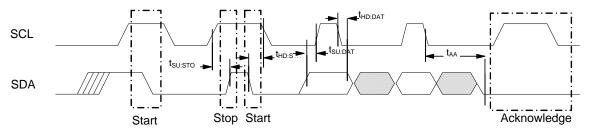

总线协议由 SDA 和 SCL 信号上的切换状态控制。共有四种条件,其中包括:启动(START)、停止(STOP)、数据位和确认。图 3 和第 5 页上的图 4 说明了指定四种状态的信号条件。"电气规范"一节中已对时序图进行了详细介绍。

#### 图 2. 使用串行 (I<sup>2</sup>C) F-RAM 的系统配置

#### STOP 事件 (P)

总线主设备将 SDA 从低电平切换至高电平(同时 SCL 信号为高电平)时,表示 STOP 事件。使用 FM24V02A 的所有操作要以 STOP 事件结束。当激活 STOP 事件时,正在运行的某个操作将被终止。主设备需要控制 SDA(并非存储器读取操作),以激活 STOP 事件。

### START 事件 (S)

总线主设备将 SDA 从高电平切换至低电平(同时 SCL 信号为高电平)时,表示发生 START 事件。发送所有指令之前,需要生成一个 START 事件。随时激活 START 事件,便可终止正在运行的操作。使用 START 事件终止某个操作会使 FM24V02A 准备执行新操作

在操作过程中,如果电源下降到比指定的  $V_{DD}$  更小的值,则在执行其他操作前,系统需要发出 START 事件。

图 4. I<sup>2</sup>C 总线上的数据传输

#### 数据/地址传输

当 SCL 信号为高电平时,会进行所有数据的传输(包括地址)。除了在上述3种事件下,SCL为高电平时也不能更改 SDA 信号。

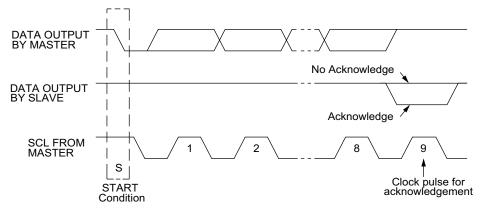

#### 确认/否认

在任何数据传输中,第8个数据位被传输之后,会发生确认事件。 在该状态中,发送器应该释放 SDA 总线,以允许接收器驱动该 信号。接收器将 SDA 信号置于低电平,以确认收到字节。如果 接收器不将 SDA 信号置于低电平,则会发生否认事件,并终止 操作。 接收器确认失败的原因有两个,第一个是字节传输失败。在这种情况下,否认事件终止当前操作,以便再次对器件进行寻址。这样允许最后字节在通信错误事件发生时恢复。

第二个也是最常见的原因是接收器不确认故意终止操作。比如,在读取操作过程中,只要接收器发出确认(和时钟信号)数据包,FM24V02A会持续将数据放置在总线上。当读操作已完成,且不需要发送任何数据时,接收器不必确认最后的字节。如果接收器确认了最后一个字节,在主设备正在发出新指令(如停止事件)时,FM24V02A会尝试在下一个时钟周期内驱动总线。

图 5. 在 I<sup>2</sup>C 总线上确认

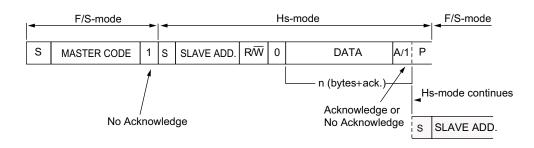

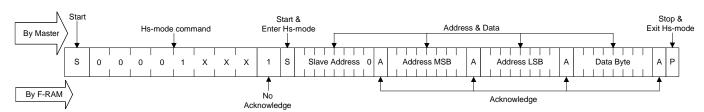

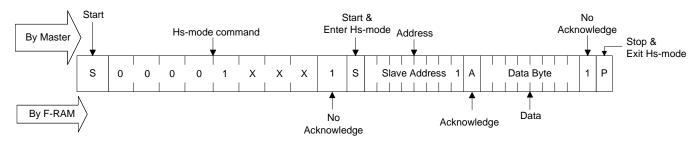

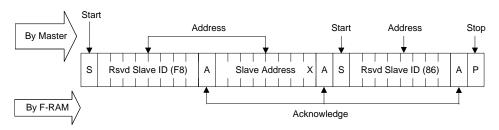

#### 高速模式 (Hs 模式)

FM24V02A 支持 3.4 MHz 的高速模式。必须生成主设备代码 (00001XXXb),以将器件置于高速模式。主设备和从设备间的

通信将被启用,以达到最高速率 3.4 MHz。STOP 事件将退出高速模式。支持单字节和多字节读写。

#### 图 6. 高速模式下的数据传输格式

#### 从设备地址

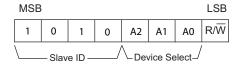

发出 START 事件后, FM24V02A 所期望接收的第一个字节是从设备地址。如图 7 中所示, 从设备地址包括器件类型或从设备ID、器件选择地址位以及一个指定读/写操作的位。

对于 FM24V02A,位 7-4 是设备类型(从设备 ID),并且应该将其设置为 1010b。这些位允许同一个地址范围的双线总线具有不同的功能类型。位 3-1 是器件选择地址位。它们要符合于外部地址引脚的对应值,以选择器件。通过对每个器件分配不同的地址,多达 8 个 FM24V02A 器件可以常驻于同一个双线总线上。位 0 是读 / 写位(R/W)。 R/W = '1'表示读操作, R/W = '0'表示写操作。

#### 图 7. 存储器从设备地址

#### 寻址概述

FM24V02A(如接收器)确认从设备地址后,主设备可以将存储器地址放置在总线上,以实现写操作。该地址需要使用两个字节。15位的完整地址被内部锁存。每个访问操作均使所锁存的地址值自动递增。当前地址是保留在锁存器中的值,无论它是新写入的值还是最后的访问操作后的地址。只要保持电源或在写入新的值前,仍会保留当前地址。读操作一直使用当前地址。通过执行如下解释的写操作,可以加载某个随机读取地址。

传输每个数据字节后,执行确认条件前,FM24V02A 会增加内部地址锁存器。这样可以访问下一个连续字节而无需额外地址。达到最后地址(7FFFh)之后,地址锁存将翻转为0000h。单个读或写操作访问的字节数量不受限制。

#### 数据传输

地址字节被发送后,可以开始进行总线主设备与FM24V02A之间的数据传输。对于读操作,FM24V02A 将 8 个数据位置于总线上,然后等待主设备发出确认信号。如果主设备发出了确认信号,FM24V02A 将传输下一个连续字节。如果不发生确认事件,FM24V02A 将终止读操作。对于写操作,FM24V02A 将接收来自主设备的 8 个数据位,然后发出确认信号。所有数据传输操作都优先发送 MSB(最高有效位)。

## 存储器操作

FM24V02A的操作方式被设计为与其他双线接口存储器产品的操作方式相同。主要差异是由于 F-RAM 技术的更高性能和写入功能引起的。这些改进使得 FM24V02A 与具有相同配置的 EEPROM 之间在写操作中存在一些差异。下面内容对读和写的完成操作进行了加以说明。

#### 写操作

所有写操作都从从设备地址开始,然后轮到存储器地址。通过设置从设备地址的 LSB(R/W 位)为'0',总线主设备将指示一个写操作。寻址之后,总线主设备将每一个数据字节发送到存储器内,然后存储器生成一个确认事件。可以写入任意连续字节数量。如果达到地址范围的最后地址,地址计数器将从 7FFFh 返回到 0000h。

与其他非易失性存储器技术不同,使用 F-RAM 技术时没有写操作延迟。因为基础存储器的读写访问时间相等,所以用户体验到总线上没有延迟。整个存储器周期的发生时间短于单个总线时钟周期。因此,完成某个写入操作后,可以立即发生任何读或写操作。不需要使用数据应答轮询技术(EEPROM 使用该技术来确定写操作是否完成),并且会始终返回就绪条件。

在内部中,传输第8个数据位后,会发生实际存储器写操作。发出确认条件前,会完成该操作。因此,如果用户需要中止写操作而不修改存储器内容,应该通过发生第8个数据位前使用START事件或STOP事件来实现该操作。FM24V02A不使用页面缓冲区。

通过使用 WP 引脚可以对存储器阵列进行写保护。将 WP 引脚设置为高电平条件( $V_{DD}$ ),便可对所有地址进行写保护。FM24V02A将不确认被写入到保护地址的数据字节。此外,如果尝试写入这些地址,地址计数器将不增加。将 WP 引脚设置为低电平状态( $V_{SS}$ ),便可禁用写保护。 WP 被内部下拉。

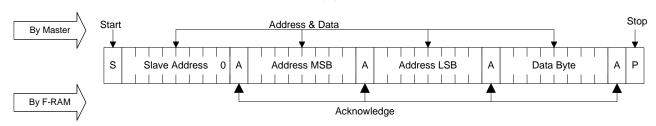

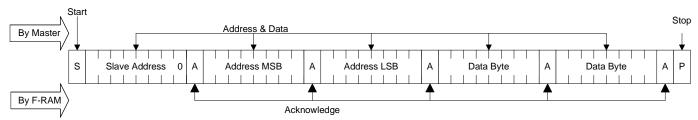

图 8 和图 9 显示的是全速模式下的单字节和多字节写周期。图 10 则显示高速模式下的单字节写周期

#### 图 8. 单字节写入

#### 图 9. 多字节写入

#### 图 10. 高速模式下的字节写入

# 读操作

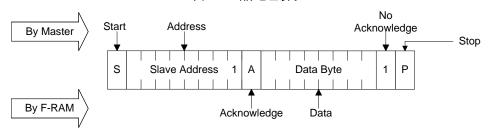

读操作具有两种基本类型。它们分别是当前地址读取和选择性地址读取。对于当前地址读取,FM24V02A 使用内部地址锁存器来提供地址。对于选择性地址读取,用户执行将地址设置为指定值的流程。

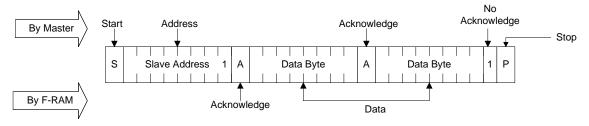

#### 当前地址和连续读取

如上面所述, FM24V02A 通过使用内部锁存器给读操作提供地址。进行读操作时,当前地址读取会将地址锁存器中现有的值作为起始地址使用。系统从最后操作的随后地址开始读取。

为执行当前地址读取,总线主设备提供具有 LSB 设为'1'的从设备地址。这指示请求了一个读操作。接收完整从设备地址后,FM24V02A 在下一个时钟上将从当前地址开始移出数据。当前地址是内部地址锁存器中所保留的值。

从当前地址开始,总线主设备可以读取任意字节数。因此,一个连续读取仅是进行多字节传输的当前地址读取。传输每个字节后,内部地址计数器会增加。

**注意**:每次总线主设备确认某个字节时,会指示 FM24V02A 可以读取下一个连续字节。

可以通过四种方式进行适当地终止读操作。不适当地终止读操作 将导致总线冲突,比如 FM24V02A 尝试读取总线上的额外数据。 四种有效方法是:

- 1. 总线主设备在第 9 个时钟周期内发送一个否认条件,并在第 10 个时钟周期内发送 STOP 事件。下面框图描述了该操作。这是首选的方法。

- 2. 总线主设备在第 9 个时钟周期发送否认条件,并在第 10 个时钟周期内发送 START 事件。

- 3. 总线主设备在第 9 个时钟周期发送 STOP 事件。

- 4. 总线主设备在第 9 个时钟周期发送 START 事件。

如果内部地址达到 7FFFh, 它将在下一个读周期中返回 0000h。图 11 和图 12 显示的是当前地址读取的正确操作。

### 图 11. 当前地址读取

### 图 12. 连续读取

### 图 13. 高速模式下的当前地址读取

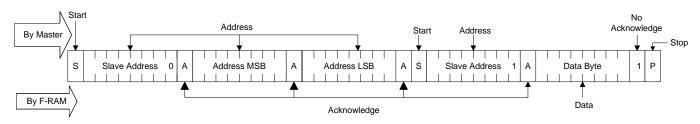

#### 选择性 (随机) 读取

通过一种简单的技术,用户可以选择一个随机地址位置作为读操作的起始地址。该技术使用写操作的前三个字节来设置后续读操作随后的内部地址。

为执行一个选择性读取,总线主设备发出具有 LSB (R/W) 被设置为 0 的从设备地址。这样表示一个写操作。根据写协议,总线主设备 会 发 送 被 加 载 到 内 部 地 址 锁 存 器 中 的 地 址 字 节。FM24V02A 确认地址后,总线主设备将发出启动事件。这样会中止写操作,同时允许通过将从设备地址的 LSB 设置为 '1' 来发出读指令。该操作现在是当前地址读取。

#### 图 14. 选择性 (随机) 读取

#### 睡眠模式

低功耗模式又称为睡眠模式可以在FM24V02A器件上实现。当睡眠指令86h被输入时,器件会进入低功耗模式。按照以下操作可以进入睡眠模式:

- 1. 主设备发送 START 指令。

- 2. 主设备发送保留的从设备 ID 0xF8。

- 3. FM24V02A 发送 ACK。

- 4. 主设备将所需识别的从设备的从设备地址发送到 I<sup>2</sup>C 总线。 最后一位是"无需关注"的值(R/W 位)。一个器件必须 确认该字节(该字节包含 I<sup>2</sup>C 总线从设备地址)。

- 5. FM24V02A 发送 ACK。

- 6. 主设备发送 Re-START (重新启动)指令。

- 7. 主设备发送保留的从设备 ID 0x86。

- 8. FM24V02A 发送 ACK。

- 9. 主设备发送 STOP,以确保器件进入睡眠模式。

一旦进入睡眠模式,器件消耗  $I_{ZZ}$  电流,但是器件继续监控  $I^2C$  引脚。一旦主设备发送了 FM24V02A 所确认的从设备地址,器件将"唤醒",并在  $t_{REC}$  (最长为 400~ms) 时间内准备好执行正常的操作。主设备可以发送读或写指令,并寻找 ACK,这是确定器件何时就绪的另一种方法。正在唤醒器件时,它会 NACK 主设备,直到它就绪为止。

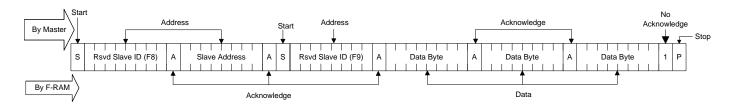

## 器件 ID

FM24V02A 器件提供数据的三个字节 (即制造商 ID、产品 ID 和芯片版本)来识别器件。器件 ID 是只读的。可以按照下面步骤访问器件 ID:

- 1. 主设备发送 START 指令。

- 2. 主设备发送保留的从设备 ID 0xF8。

- 3. FM24V02A 发送 ACK。

- 4. 主设备将所需识别的从设备的从设备<u>地</u>址发送到 I<sup>2</sup>C 总线。 最后一位是"无需关注"的值(R/W 位)。一个器件必须 确认该字节(该字节包含 I<sup>2</sup>C 总线从设备地址)。

- 5. FM24V02A 发送 ACK。

注意:发送 NACK 指令可以随时停止器件 ID 的读取。

O.T.W.Z.TVOZ/T/交送/TOTTs

- 6. 主设备发送 Re-START (重新启动)指令。

- 7. 主设备发送保留的从设备 ID 0xF9。

- 8. FM24V02A 发送 ACK。

- 9. 可以执行器件 ID 读取,首先是 12 个制造商位,其次是 9 个器件标识位和最后是 3 个芯片版本位。

- 10.主设备通过 NACK 最后字节可以结束器件 ID 读序列,从而复位从设备状态机,并允许主设备发送 STOP 指令。

| 表 1. | 器件ID | ) |

|------|------|---|

|------|------|---|

|                  | 器               | 件 ID 说明       |              |              |

|------------------|-----------------|---------------|--------------|--------------|

| 器件 ID<br>(3 个字节) | 23–12<br>(12 位) | 11-8<br>(4 位) | 7–3<br>(5 位) | 2-0<br>(3 位) |

| (3小子山)           | 制造商 ID          | 产品 ID         |              |              |

|                  | 型塩油 10          | 容量            | 变量           | 芯片版本         |

| 004201h          | 00000000100     | 0010          | 00000        | 001          |

注意:产品 ID 位 0 和位 4 均被保留。

图 16. 读取器件 ID

# 最大额定值

超过最大额定值可能会缩短设备的使用寿命。这些用户指导未经 过测试。 存放温度 ......-55 °C 至 +125 °C 最高结温.......95℃ 与 V<sub>SS</sub> 相对的 V<sub>DD</sub> 上的供电电压 ......-1.0 V 到 +4.5 V 输入电压 \* ......-1.0 V 到 + 4.5 V 和  $V_{IN}$  <  $V_{DD}$  + 1.0 V 直流电压应用在 高阻 (High Z) 状态下的输出 ......-0.5 V 到 V<sub>DD</sub>+ 0.5 V 处于接地电位的任何引脚上的 瞬变电压(< 20 ns).....-2.0 V 到 V<sub>DD</sub> + 2.0 V 封装功率散耗能力 (T<sub>A</sub> = 25 °C)......1.0 W

| 表面贴装铅焊温度 (3秒)+260℃                                          |

|-------------------------------------------------------------|

| 静电放电电压<br>人体模型(JEDEC Std JESD22-A114-B)2 kV                 |

| 充电器件模型(JEDEC 标准 JESD22-C101-A)500 V                         |

| 栓锁电流> 140 mA                                                |

| * 例外: " $V_{IN}$ < $V_{DD}$ + 1.0 V" 的限制并不适用于 SCL 和 SDA 输入。 |

# 工作范围

| 范围  | 环境温度 (T <sub>A</sub> ) | $V_{DD}$      |

|-----|------------------------|---------------|

| 工业级 | -40°C 至 +85°C          | 2.0 V 至 3.6 V |

# 直流电气特性

适用条件为工作范围

| 参数                             | 说明                   | 测试条件                                                                                        | 最小值                   | 典型值 [1] | 最大值                           | 单位     |

|--------------------------------|----------------------|---------------------------------------------------------------------------------------------|-----------------------|---------|-------------------------------|--------|

| $V_{DD}$                       | 电源                   |                                                                                             | 2.0                   | 3.3     | 3.6                           | V      |

| I <sub>DD</sub>                | V <sub>DD</sub> 平均电流 | SCL 在 f <sub>SCL</sub> = 100 kH                                                             | <u> </u>              | _       | 175                           | μΑ     |

|                                |                      | $V_{DD}$ = 0.2 V 与 $V_{SS}$ 之 $f_{SCL}$ = 1 MHz 间进行切换,                                      | -                     | _       | 400                           | μΑ     |

|                                |                      | 其他输入的电压为<br>V <sub>SS</sub> 或 V <sub>DD</sub> – 0.2 V。                                      | _                     | _       | 1000                          | μА     |

| I <sub>SB</sub>                | V <sub>CC</sub> 待机电流 | SCL = SDA = V <sub>DD</sub> 。所有其他输入的<br>电压为 V <sub>SS</sub> 或 V <sub>DD</sub> 。已发出停止指<br>令。 | _                     | 90      | 150                           | μА     |

| I <sub>ZZ</sub>                | 睡眠模式电流               | SCL = SDA = V <sub>DD</sub> 。所有其他输入的<br>电压为 V <sub>SS</sub> 或 V <sub>DD</sub> 。已发出停止指<br>令。 | _                     | 5       | 8                             | μΑ     |

| I <sub>LI</sub>                | 输入漏电流(除WP和A2-A0外)    | $V_{SS} \le V_{IN} \le V_{DD}$                                                              | -1                    | -       | +1                            | μΑ     |

|                                | 输入漏电流(用于WP和A2-A0)    |                                                                                             | -1                    | _       | +100                          | μΑ     |

| $I_{LO}$                       | 输出漏电流                | $V_{SS} \le V_{OUT} \le V_{DD}$                                                             | -1                    | ı       | +1                            | μΑ     |

| $V_{IH}$                       | 输入高电平电压 (SDL, SDA)   |                                                                                             | $0.7 \times V_{DD}$   | -       | V <sub>DD</sub> (max)+<br>0.3 | \<br>\ |

|                                | 输入高电平电压(WP, A2-A0)   |                                                                                             | $0.7 \times V_{DD}$   | -       | $V_{DD} + 0.3$                | V      |

| $V_{IL}$                       | 输入低电平电压              |                                                                                             | - 0.3                 | ı       | $0.3 \times V_{DD}$           | V      |

| $V_{OL}$                       | 输出低电平电压              | $I_{OL} = 3 \text{ mA}$                                                                     | -                     | ı       | 0.4                           | V      |

|                                |                      | $I_{OL} = 6 \text{ mA}$                                                                     | -                     | ı       | 0.6                           | V      |

| R <sub>in</sub> <sup>[2]</sup> | 输入电阻 (WP, A2-A0)     | $V_{IN} = V_{IL(Max)}$                                                                      | 50                    | 1       | _                             | kΩ     |

|                                |                      | $V_{IN} = V_{IHIH(Min)}$                                                                    | 1                     | 1       | _                             | МΩ     |

| V <sub>hys</sub>               | 施密特触发器输入电压迟滞         | f <sub>SCL</sub> = 1 MHz                                                                    | $0.05 \times V_{DD}$  | ı       | _                             | V      |

|                                |                      | f <sub>SCL</sub> = 3.4 MH.                                                                  | 0.1 × V <sub>DD</sub> | -       | _                             | V      |

### 注释:

- 典型值要求条件为:环境温度为 25°C, V<sub>DD</sub> = V<sub>DD</sub> (典型值)。并非 100% 经过了测试。

当输入电压低于 V<sub>IL</sub> 时,输入下拉电路会较强 (50 kΩ);输入电压高于 V<sub>IH</sub> 时,输入下拉电路较弱 (1 MΩ)。

# 数据保留时间与耐久性

| 参数              | 说明     | 测试条件                   | 最小值              | 最大值 | 单位 |

|-----------------|--------|------------------------|------------------|-----|----|

| $T_{DR}$        | 数据保留时间 | $T_A = 85$ °C          | 10               | 1   | 年  |

|                 |        | T <sub>A</sub> = 75 °C | 38               | 1   |    |

|                 |        | $T_A = 65$ °C          | 151              | 1   |    |

| NV <sub>C</sub> | 擦写次数   | 在工作温度范围内               | 10 <sup>14</sup> | _   | 周期 |

# 电容

| 参数 [3]          | 说明              | 测试条件                                                                    | 最大值 | 单位 |

|-----------------|-----------------|-------------------------------------------------------------------------|-----|----|

| C <sub>IO</sub> | 输入/输出引脚的电容(SDA) | T <sub>A</sub> = 25 ℃、f = 1 MHz、V <sub>DD</sub> = V <sub>DD</sub> (典型值) | 8   | pF |

| C <sub>I</sub>  | 输入引脚电容          |                                                                         | 6   | pF |

# 热电阻

| 参数 [3]            | 说明            | 测试条件                        | 8 引脚 SOIC | 单位   |

|-------------------|---------------|-----------------------------|-----------|------|

| $\Theta_{JA}$     | 热电阻 (结温至环境温度) | 根据 EIA/JESD51 的要求,测试条件应遵循热阻 | 146       | °C/W |

| $\Theta_{\sf JC}$ | 热电阻 (结温至壳温)   | 的标准测试方法和过程。                 | 48        | °C/W |

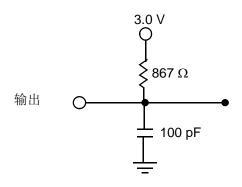

# 交流测试负载和波形

图 17. 交流测试负载和波形

# 交流测试条件

| 输入脉冲电平      | V <sub>DD</sub> 的 10%和 90% |

|-------------|----------------------------|

| 输入上升和下降时间   | 10 ns                      |

| 输入和输出时序参考电平 | 0.5 × V <sub>DD</sub>      |

| 输出负载电容      | 100 pF                     |

#### 注释

3. 这些参数仅通过设计保证,并未经过测试。

文档编号: 001-93810 版本\*A 页 12/19

# 交流开关特性

适用条件为工作范围

| 参数 [4]                          | 备用参数                 | NA NE                                               | 全速模式 [6]                       |     | 高速模式 [6] |     | 34 th |

|---------------------------------|----------------------|-----------------------------------------------------|--------------------------------|-----|----------|-----|-------|

|                                 |                      | 说明                                                  | 最小值                            | 最大值 | 最小值      | 最大值 | 単位    |

| f <sub>SCL</sub> <sup>[5]</sup> |                      | SCL 时钟频率                                            | _                              | 1.0 | _        | 3.4 | MHz   |

| t <sub>SU; STA</sub>            |                      | 用于重复 Start 的 Start 事件建立时间                           | 260                            | _   | 160      | _   | ns    |

| t <sub>HD;STA</sub>             |                      | Start 事件的保持时间                                       | 260                            | _   | 160      | _   | ns    |

| $t_{LOW}$                       |                      | 时钟为低电平的周期                                           | 500                            | _   | 160      | _   | ns    |

| t <sub>HIGH</sub>               |                      | 时钟为高电平的周期                                           | 260                            | _   | 60       | _   | ns    |

| t <sub>SU;DAT</sub>             | t <sub>SU;DATA</sub> | 数据输入的建立时间                                           | 50                             | _   | 10       | _   | ns    |

| t <sub>HD;DAT</sub>             | t <sub>HD;DATA</sub> | 数据输入的保持时间                                           | 0                              | _   | 0        | 70  | ns    |

| t <sub>DH</sub>                 |                      | 从在 V <sub>IL</sub> 时的 SCL 到数据输出的保留时间                | 0                              | _   | 0        | _   | ns    |

| t <sub>R</sub> <sup>[7]</sup>   | t <sub>r</sub>       | 输入上升时间                                              | _                              | 120 | 10       | 80  | ns    |

| t <sub>F</sub> <sup>[7]</sup>   | t <sub>f</sub>       | 输入下降时间                                              | 20 * (V <sub>DD</sub> / 5.5 V) | 120 | 10       | 80  | ns    |

| t <sub>SU;STO</sub>             |                      | STOP 事件的建立时间                                        | 260                            | -   | 160      | _   | ns    |

| t <sub>AA</sub>                 | t <sub>VD;DATA</sub> | 从 SCL 为低电平到 SDA 数据输出有效的时间                           | -                              | 450 | _        | 130 | ns    |

| t <sub>VD;ACK</sub>             |                      | ACK 输出的有效时间                                         | -                              | 450 | -        | 130 | ns    |

| t <sub>OF</sub> <sup>[7]</sup>  |                      | 从 V <sub>IH</sub> min 到 V <sub>IL</sub> max 的输出下降时间 | 20 * (V <sub>DD</sub> / 5.5 V) | 120 | _        | 80  | ns    |

| t <sub>BUF</sub>                |                      | 新传输发生前总线处于闲置状态的时间                                   | 500                            | _   | 300      | _   | ns    |

| t <sub>SP</sub>                 |                      | 在 SCL、 SDA 上的噪声抑制时间常量                               | 0                              | 50  | _        | 5   | ns    |

图 18. 读取总线时序图

### 图 19. 写入总线时序图

#### 注释:

- 5. 与速度相关的规范由特性线上的各点保证,这些点位于工作频率为 DC 至 f<sub>SCL</sub> (最大值)的连续曲线上。

6. 总线负载 (Cb) 的注意事项;对于 I<sup>2</sup>C 时钟频率 (SCL) 1 MHz, Cb < 550 pF;对于 3.4 MHz 的 SCL, Cb < 100 pF。</li>

7. 这些参数仅通过设计保证,并未经过测试。

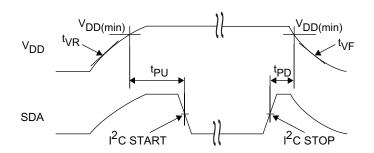

# 电源循环时序

适用条件为工作范围

| 参数                    | 说明                                                 | 最小值 | 最大值 | 单位   |

|-----------------------|----------------------------------------------------|-----|-----|------|

| t <sub>PU</sub>       | 从加电 V <sub>DD</sub> (min) 到第一次访问 (发生 START 事件)的时间  | 250 | _   | μs   |

| t <sub>PD</sub>       | 从最后一次访问 (发生 STOP 事件)到断电 (V <sub>DD</sub> (min))的时间 | 0   | -   | μs   |

| t <sub>VR</sub> [8、9] | V <sub>DD</sub> 加电升降斜率                             | 50  | -   | μs/V |

| t <sub>VF</sub> [8、9] | V <sub>DD</sub> 断电升降斜率                             |     | -   | μs/V |

| t <sub>REC</sub>      | 从睡眠模式恢复的时间                                         | _   | 400 | μs   |

图 20. 电源循环时序

### 注释:

- 8. 在 V<sub>DD</sub> 波形的任何位置测量斜率。 9. 这些参数仅通过设计保证,并未经过测试。

# 订购信息

| 订购代码       | 封装图      | 封装类型      | 工作范围 |

|------------|----------|-----------|------|

| FM24V02A-G | 51-85066 | 8 引脚 SOIC | 工业级  |

这些器件都是无铅的。要了解这些器件的供应情况,请联系赛普拉斯本地销售代表。

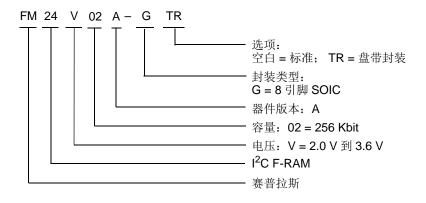

## 订购代码定义

# 封装图

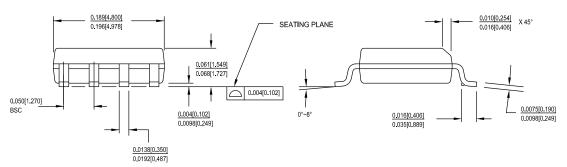

### 图 21. 8 引脚 SOIC(150 mils)封装外形, 51-85066

- 1. DIMENSIONS IN INCHES[MM] MIN. MAX.

- PIN 1 ID IS OPTIONAL,

ROUND ON SINGLE LEADFRAME

RECTANGULAR ON MATRIX LEADFRAME

- 3. REFERENCE JEDEC MS-012

- 4. PACKAGE WEIGHT 0.07gms

| PART #  |               |  |

|---------|---------------|--|

| S08.15  | STANDARD PKG  |  |

| SZ08.15 | LEAD FREE PKG |  |

| SW8.15  | LEAD FREE PKG |  |

51-85066 \*H

# 缩略语

| 缩略语              | 说明          |  |  |  |

|------------------|-------------|--|--|--|

| ACK              | 确认          |  |  |  |

| CMOS             | 互补金属氧化物半导体  |  |  |  |

| EIA              | 电子工业联盟      |  |  |  |

| I <sup>2</sup> C | 内部集成电路      |  |  |  |

| I/O              | 输入/输出       |  |  |  |

| JEDEC            | 联合电子器件工程委员会 |  |  |  |

| LSB              | 最低有效位       |  |  |  |

| MSB              | 最高有效位       |  |  |  |

| NACK             | 否认          |  |  |  |

| RoHS             | 有害物质限制      |  |  |  |

| R/W              | 读/写         |  |  |  |

| SCL              | 串行时钟线       |  |  |  |

| SDA              | 串行数据访问      |  |  |  |

| SOIC             | 小外型集成电路     |  |  |  |

| WP               | 写保护         |  |  |  |

# 文档规范

# 测量单位

| 符号  | 测量单位   |

|-----|--------|

| °C  | 摄氏度    |

| Hz  | 赫兹     |

| KB  | 1024 位 |

| kHz | 千赫兹    |

| kΩ  | 千欧     |

| MHz | 兆赫     |

| ΜΩ  | 兆欧     |

| μΑ  | 微安     |

| μS  | 微秒     |

| mA  | 毫安     |

| ms  | 毫秒     |

| ns  | 纳秒     |

| Ω   | 欧姆     |

| %   | 百分比    |

| pF  | 皮法     |

| V   | 伏特     |

| W   | 瓦特     |

# 文档修订记录页

| 文档标题: 文档编号: | 题:FM24V02A, 256 Kbit (32 K × 8)串行 (I <sup>2</sup> C) F-RAM<br>号:001-93810 |      |            |                                      |

|-------------|---------------------------------------------------------------------------|------|------------|--------------------------------------|

| 版本          | ECN 编号                                                                    | 变更者  | 提交日期       | 更改说明                                 |

| **          | 4478636                                                                   | YLIU | 09/08/2014 | 本文档版本号为 Rev**,译自英文版 001-90839 Rev*A。 |

| *A          | 5563061                                                                   | GVCH | 12/29/2016 | 更新第 14 页的 tPU,将 1ms 更新为 250μs。       |