# KTFRDMHB2001FEVMUG

# FRDM-HB2001FEVM evaluation board Rev. 1.0 — 25 May 2016

User guide

### FRDM-HB2001FEVM

#### 2 Important notice

NXP provides the enclosed product(s) under the following conditions:

This evaluation kit is intended for use of ENGINEERING DEVELOPMENT OR EVALUATION PURPOSES ONLY. It is provided as a sample IC pre-soldered to a printed circuit board to make it easier to access inputs, outputs, and supply terminals. This evaluation board may be used with any development system or other source of I/O signals by simply connecting it to the host MCU or computer board via off-the-shelf cables. This evaluation board is not a Reference Design and is not intended to represent a final design recommendation for any particular application. Final device in an application will be heavily dependent on proper printed circuit board layout and heat sinking design as well as attention to supply filtering, transient suppression, and I/O signal quality.

The goods provided may not be complete in terms of required design, marketing, and or manufacturing related protective considerations, including product safety measures typically found in the end product incorporating the goods. Due to the open construction of the product, it is the user's responsibility to take any and all appropriate precautions with regard to electrostatic discharge. In order to minimize risks associated with the customers applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards. For any safety concerns, contact NXP sales and technical support services.

Should this evaluation kit not meet the specifications indicated in the kit, it may be returned within 30 days from the date of delivery and will be replaced by a new kit.

NXP reserves the right to make changes without further notice to any products herein. NXP makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typical", must be validated for each customer application by customer's technical experts.

NXP does not convey any license under its patent rights nor the rights of others. NXP products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the NXP product could create a situation where personal injury or death may occur.

Should the Buyer purchase or use NXP products for any such unintended or unauthorized application, the Buyer shall indemnify and hold NXP and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges NXP was negligent regarding the design or manufacture of the part. NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. © 2016 NXP B.V.

#### 3 Getting started

#### 3.1 Kit contents/packing list

The FRDM-HB2001FEVM contents includes:

- · Assembled and tested evaluation board/module in anti-static bag

- FRDM-KL25Z

- · Quick start guide

#### 3.2 Jump start

NXP's analog product development boards provide an easy-to-use platform for evaluating NXP products. The boards support a range of analog, mixed-signal and power solutions. They incorporate monolithic ICs and system-in-package devices that use proven high-volume SMARTMOS technology. NXP products offer longer battery life, a smaller form factor, reduced component counts, lower cost and improved performance in powering state of the art systems.

- 1. Go to www.nxp.com/FRDM-HB2001FEVM.

- 2. Review your Tools Summary Page.

- 3. Locate and click:

# Jump Start Your Design

4. Download the documents, software and other information.

Once the files are downloaded, review the user guide in the bundle. The user guide includes setup instructions, BOM and schematics. Jump start bundles are available on each tool summary page with the most relevant and current information. The information includes everything needed for design.

#### 3.3 Required equipment

This kit requires the following items:

- 3/16" blade screwdriver for connecting the cables

- DC Power supply: 5.0 V to 40 V with up to 20 A current handling capability, depending on motor requirements

- USB Standard A (male) to mini-B (male) cable

- Typical loads (brushed DC motor, power resistors or inductive load with up to 5.0 A and 28 V operation)

- Function generator (optional)

- FRDM-KL25Z Freedom Development Platform for SPI communication (included in KIT)

- SPIGen software (for using FRDM-KL25Z based SPI Dongle)

#### 3.4 System requirements

The kit requires the following to function properly with the software:

USB enabled computer with Windows XP or newer

KTFRDMHB2001FEVMUG

All information provided in this document is subject to legal disclaimers.

## 4 Getting to know the hardware

#### 4.1 Board overview

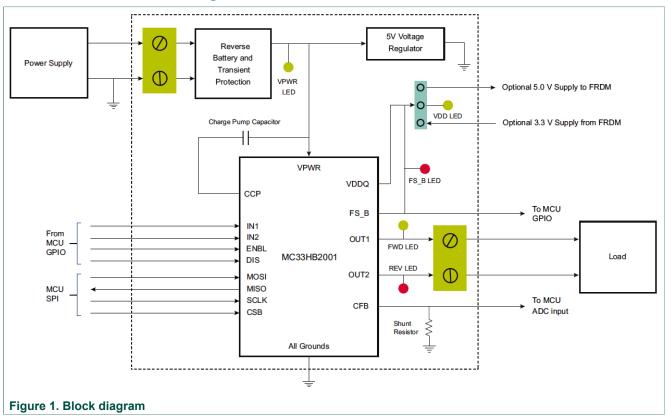

The FRDM-HB2001FEVM evaluation kit exercises all the functions of the MC33HB2001 H-Bridge device. The parallel input can be easily controlled by lab equipment or any MCU with GPIOs.

The board can be used in conjunction with a FRDM-KL25Z board connected to a PC's USB port. Configure, control and monitor the status of MC33HB2001 by using the board's SPI communication capabilities.

#### 4.2 Board features

The FRDM-HB2001FEVM board evaluates the NXP part MC33HB2001, including all functions. The board features the following:

- · Built-in reverse battery protection

- · Test points allows probing its signals

- · Built-in voltage regulator to supply logic level circuitry

- · LEDs to indicate the supply status and the direction of the motor

- Low Equivalent Series Resistance (ESR) capacitor to reduce ripple in the power supply

- Transient voltage suppressor to handle system level transients

#### 4.3 Block diagram

#### 4.3.1 Device features

This evaluation board features the following NXP product:

Table 1. Device features

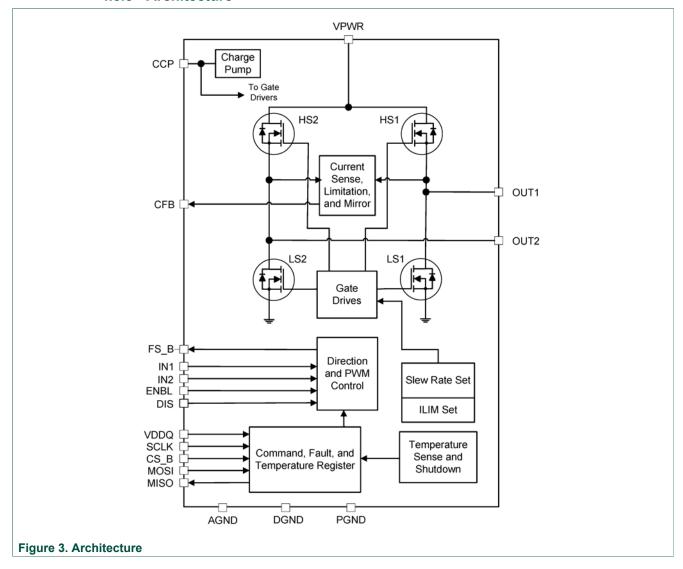

| Device     | Description                                                                                                    | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MC33HB2001 | The 33HB2001 is a monolithic H-Bridge Power IC, enhanced with SPI configurability and diagnostic capabilities. | <ul> <li>Advanced diagnostic reporting via a serial peripheral interface (SPI): charge pump undervoltage on VPWR, short to ground and short to VPWR for each output, open load, temperature warning and overtemperature shutdown</li> <li>Thermal management: excellent thermal resistance of &lt; 1.0 °C/W between junction and case (exposed pad)</li> <li>Eight selectable slew rates via the SPI: 0.25 V/μs to more than 16 V/μs for EMI and thermal performance optimization</li> <li>Four selectable current limits via the SPI: 5.4/7.0/8.8/10.7 A, covering a wide range of applications</li> <li>Can be operated without the SPI with a default slew rate of 2.0 V/μs and a 7.0 A current limit threshold</li> <li>Highly accurate real-time current feedback through a current mirror output signal with less than 5.0 % error</li> <li>Drives inductive loads in a full H-Bridge or Half-bridge configuration</li> <li>Overvoltage protection places the load in high-side recirculation (braking) mode with notification in H-Bridge mode</li> <li>Wide operating range: 5.0 V to 28 V operation</li> <li>Low R<sub>DS(on)</sub> integrated MOSFETs: Maximum of 125 mΩ (T<sub>J</sub> = 150 °C) for each MOSFET</li> <li>Internal protection for overtemperature, undervoltage</li> </ul> |

|            |                                                                                                                | and short-circuit by signaling the error condition and disabling the outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|            |                                                                                                                | <ul> <li>I/0 pins can withstand up to 36 V</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

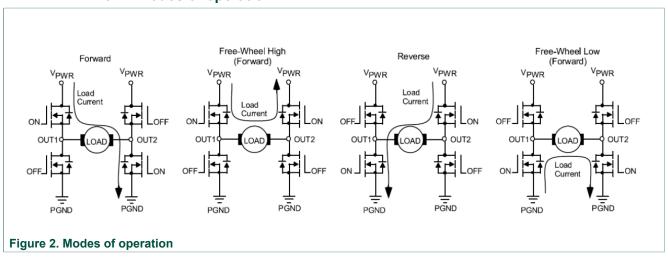

#### 4.3.2 Modes of operation

#### 4.3.3 Architecture

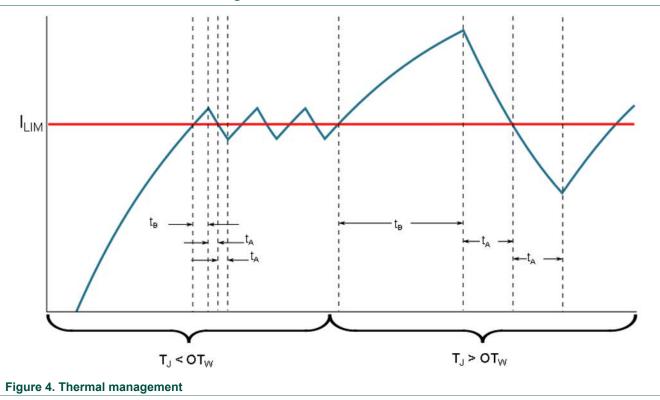

#### 4.3.4 Thermal management

#### 4.4 Board description

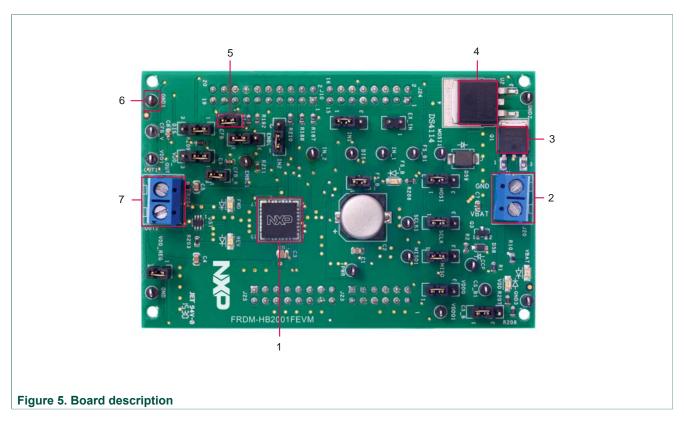

Figure 5 describes the main elements on the FRDM-HB2001FEVM.

**Table 2. Board description**

| Number | Name                       | Descrioption                                                                     |  |  |  |

|--------|----------------------------|----------------------------------------------------------------------------------|--|--|--|

| 1      | MC33HB2001                 | Monolithic H-Bridge Power IC in a robust thermally enhanced 32 lead PQFN package |  |  |  |

| 2      | Power and ground inputs    | Power supply terminal to connect the battery/power supply with the board         |  |  |  |

| 3      | Reverse battery protection | MOSFET for protecting MC33HB2001 in reverse battery condition                    |  |  |  |

| 4      | 5.0 V regulator            | 5.0 V regulator for VDD and supply                                               |  |  |  |

| 5      | Jumpers                    | Jumpers for configuring the board for different modes of operation               |  |  |  |

| 6      | Test points                | Test points to probe different signals                                           |  |  |  |

| 7      | Output terminal            | Output connector to connect a load to the MC33HB2001 output                      |  |  |  |

#### 4.4.1 LED display

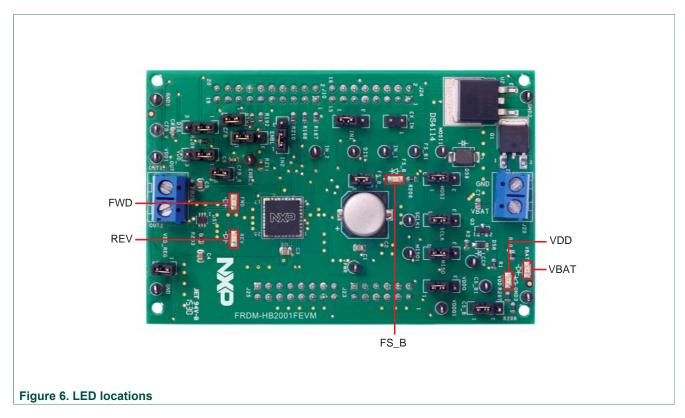

The following LEDs serve as visual output devices for the evaluation board:

**Table 3. LED locations**

| LED ID | Description                                                |

|--------|------------------------------------------------------------|

| VBAT   | Green LED, indicates when main/battery supply is connected |

| VDD    | Green LED, indicates when +5.0 V supply is connected       |

| FS_B   | Red LED, illuminates when the H-Bridge detects a fault     |

| FWD    | Green LED, indicates current flowing in forward direction  |

| REV    | Red LED, indicates current flowing in reverse direction    |

#### 4.4.2 Jumper definitions

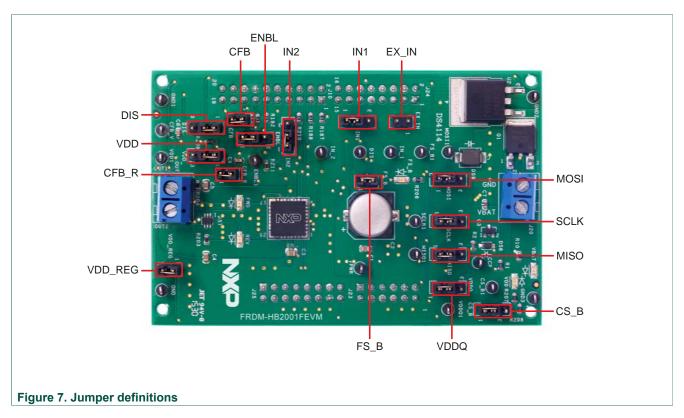

<u>Figure 7</u> illustrates the evaluation board jumper locations. <u>Table 4</u> explains the function of each position. Blue fonts in the jumper position column indicate the default settings for use with the FRDM-KL25Z.

Table 4. Jumper locations

| Name           | Signal  | Jumper position | Connection                                                    |  |  |

|----------------|---------|-----------------|---------------------------------------------------------------|--|--|

| J1             | .,      | 1-2             | IN1 control through MCU parallel output on J10 Pin 1 (DATA0)  |  |  |

| JI             | IN1     | 2-3             | IN1 control through MCU parallel output on J10 Pin 1 (DATA0)  |  |  |

| J2             | DIS     | 1-2             | DIS control through MCU parallel output on J10 Pin 13 (CTRL1) |  |  |

| JZ             | סוט     | 2-3             | DIS connected to GND to keep the outputs enabled              |  |  |

| 12             | INIO    | 1-2             | IN2 control through MCU parallel output on J10 Pin 3 (DATA1)  |  |  |

| JS             | J3 IN2  |                 | IN2 control through external input on J15 Pin 2               |  |  |

| J4             | 00 B    | 1-2             | CS_B control through MCU SPI output J10 Pin 6 (SPI_CS_B)      |  |  |

| J <del>4</del> | CS_B    | 2-3             | CS_B pulled up to VDD for operation without SPI               |  |  |

| J5             | ENDI    | 1-2             | ENBL control through MCU parallel output J10 Pin 11 (CTRL0)   |  |  |

| JO             | ENBL    | 2-3             | ENBL pulled up to VDD to keep the outputs enabled             |  |  |

| J6             | CCLK    | 1-2             | SPI clock SCLK from MCU J10 Pin 12 (SPI_SCLK)                 |  |  |

| Jo             | SCLK    | 2-3             | SCLK connected to GND for operation without SPI               |  |  |

| 17             | MOCI    | 1-2             | MOSI control through MCU SPI output J10 Pin 8 (SPI_MOSI)      |  |  |

| J/             | J7 MOSI | 2-3             | MOSI connected to GND for operation without SPI               |  |  |

| J8             | MISO    | 1-2             | MISO control through MCU SPI output J10 Pin 10 (SPI_MISO)     |  |  |

| JO             | MISO    | 2-3             | MISO not connected for operation without SPI                  |  |  |

| J11            | CFB     | 1-2             | CFB connected to 200 Ω resistor                               |  |  |

| Name | Signal                                               | Jumper position | Connection                                           |

|------|------------------------------------------------------|-----------------|------------------------------------------------------|

| J14  | VDDQ                                                 | 1-2             | VDD connected to VDDQ                                |

| 314  | VDDQ                                                 | 2-3             | VDDQ not connected                                   |

| 117  | J17 VDD                                              | 1-2             | V <sub>DD</sub> supply from regulator U2             |

| 317  |                                                      | 2-3             | V <sub>DD</sub> supply from FRDM board               |

| J18  | CFB_R <b>1-2</b>                                     |                 | CFB connected to MCU ADC input J10 Pin 17 (CFB_READ) |

| J19  | FS_B                                                 | 1-2             | FS_B connected to the pull-up resistor               |

| J26  | J26 VDD_REG <b>1-2</b> V <sub>DD</sub> to FRDM board |                 | V <sub>DD</sub> to FRDM board                        |

| J15  | EX_IN                                                | Open            | IN1 and IN2 external inputs                          |

The FRDM-HB2001FEVM, in conjunction with a FRDM-KL25Z board (shipped with the kit), can evaluate the design by means of a GUI, any MCU with GPIO or with simple lab equipment. A FRDM-KL25Z-compatible GUI and MCU program are available online at the following link: <a href="http://www.nxp.com/FRDM-HB2001FEVM">http://www.nxp.com/FRDM-HB2001FEVM</a>.

The FRDM-HB2001FEVM is compatible with any Arduino<sup>™</sup> platform board. However, if a board other than the FRDM-KL25Z is used, MCU code must be written to work with the board.

#### 4.4.3 Input signal definitions

The following input signals control the outputs or functions inside the circuit.

Table 5. Input signal definitions

| Input name | Description                                                           |  |  |

|------------|-----------------------------------------------------------------------|--|--|

| DIS        | Disable signal to tri-state the outputs                               |  |  |

| ENBL       | Disable signal to tri-state the output and put the part in Sleep mode |  |  |

| IN1        | Logic input to control OUT1                                           |  |  |

| IN2        | Logic input to control OUT2                                           |  |  |

| MOSI       | Master out slave input for the SPI                                    |  |  |

| CS_B       | Chip select bar input for the SPI                                     |  |  |

| SCLK       | Clock for the SPI                                                     |  |  |

#### 4.4.4 Output signal definitions

The FRDM-HB2001-FEVM uses the following output signals to drive a load such as a brushed DC motor. The board provides an analog output for real time load current monitoring. This signal allows closed loop control of the load.

Table 6. Output signal definitions

| Output name | Description                                                |  |

|-------------|------------------------------------------------------------|--|

| OUT1        | Output 1 of H-Bridge                                       |  |

| OUT2        | Output 2 of H-Bridge                                       |  |

| FS_B        | Open drain Active Low status flag output to indicate fault |  |

KTFRDMHB2001FEVMUG

All information provided in this document is subject to legal disclaimers.

| Output name | Description                                                 |  |

|-------------|-------------------------------------------------------------|--|

| CFB         | Current mirror output for real time load current monitoring |  |

| MISO        | Master input slave output for SPI                           |  |

#### 4.4.5 Test point definitions

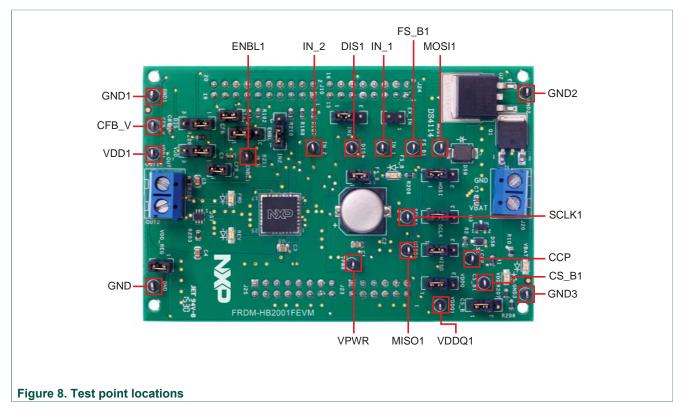

The following test points provide access to various signals to and from the board.

Table 7. Test point definitions

| Test point name | Signal name | Description                                                                             |

|-----------------|-------------|-----------------------------------------------------------------------------------------|

| CFB_V           | CFB_READ    | CFB pin voltage going to ADC                                                            |

| CCP             | CCP         | Charge pump voltage                                                                     |

| ENBL1           | ENBL        | Enable/disable signal to activate/tristate the outputs and put the device to Sleep mode |

| DIS1            | DIS         | Enable/disable signal to activate/tri-<br>state the outputs                             |

| IN_1            | IN1         | Direction control in H-Bridge mode and OUT1 control in Half-Bridge mode                 |

| IN_2            | IN2         | PWM control in H-Bridge mode and OUT2 control in Half-Bridge mode                       |

| VPWR            | VPWR        | System voltage                                                                          |

| VDDQ1           | VDDQ        | VDDQ digital output supply voltage                                                      |

KTFRDMHB2001FEVMUG

All information provided in this document is subject to legal disclaimers.

| Test point name | Signal name | Description                         |

|-----------------|-------------|-------------------------------------|

| FSB1            | FSB         | Fault status monitoring pin         |

| VDD1            | VDD         | V <sub>DD</sub> supply for the part |

| CS_B1           | CS_B        | Chip select bar                     |

| SCLK1           | SCLK        | Clock for SPI                       |

| MOSI1           | MOSI        | Master output slave input signal    |

| MISO1           | MISO        | Master input slave output signal    |

| GND             | GND         | Ground signal                       |

| GND1            | GND         | Ground signal                       |

| GND2            | GND         | Ground signal                       |

| GND3            | GND         | Ground signal                       |

#### 4.4.6 Screw terminal connections

The board has the following screw terminal connections to connect the power supply and the load.

**Table 8. Screw terminal connections**

| Screw terminal name | Description                               |  |

|---------------------|-------------------------------------------|--|

| J20                 | Power supply connector for the MC33HB2001 |  |

| J21                 | Output connector to connect load          |  |

KTFRDMHB2001FEVMUG

All information provided in this document is subject to legal disclaimers.

## 5 FRDM-KL25Z Freedom SPI dongle

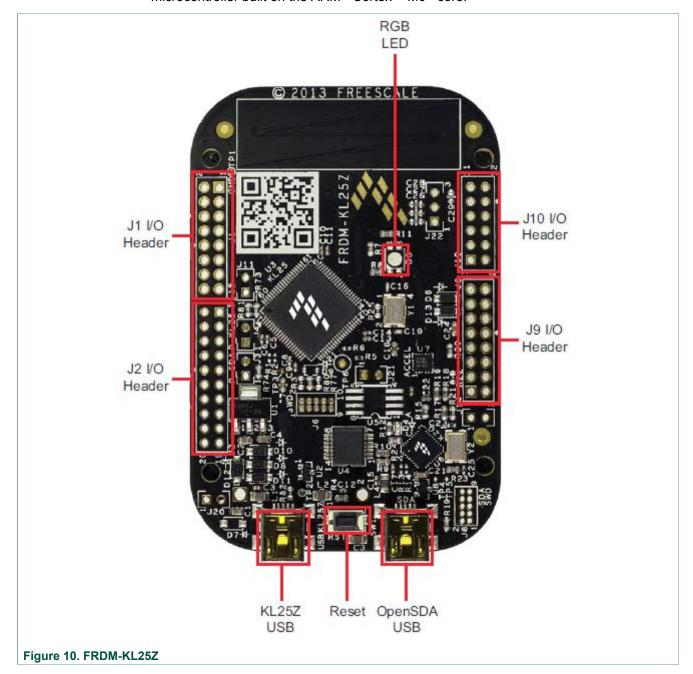

The NXP Freedom development platform is a set of software and hardware tools supporting evaluation and development. It is ideal for rapid prototyping of microcontroller-based applications. The NXP Freedom KL25Z hardware, FRDM-KL25Z, is a simple, yet sophisticated design featuring a Kinetis L Series microcontroller, the industry's first microcontroller built on the ARM<sup>®</sup> Cortex<sup>™</sup>-M0+ core.

#### 5.1 Connecting the FRDM-KL25Z to the board

The FRDM-KL25Z evaluation board was chosen specifically to work with the FRDM-HB2001FEVM kit because of its low cost and features. The FRDM-KL25Z board makes use of the USB, built in LEDs and I/O ports available with NXP's Kinetis KL2x family of microcontrollers.

The FRDM-KL25Z connects to a PC through a USB port, which permits the user to control a DC brushed motor and to drive the evaluation board inputs in order to operate the motor via the GPIOs and SPI pins. The FRDM-KL25Z also monitors the SPI registers, thereby facilitating the use of safety and advanced diagnostic functions.

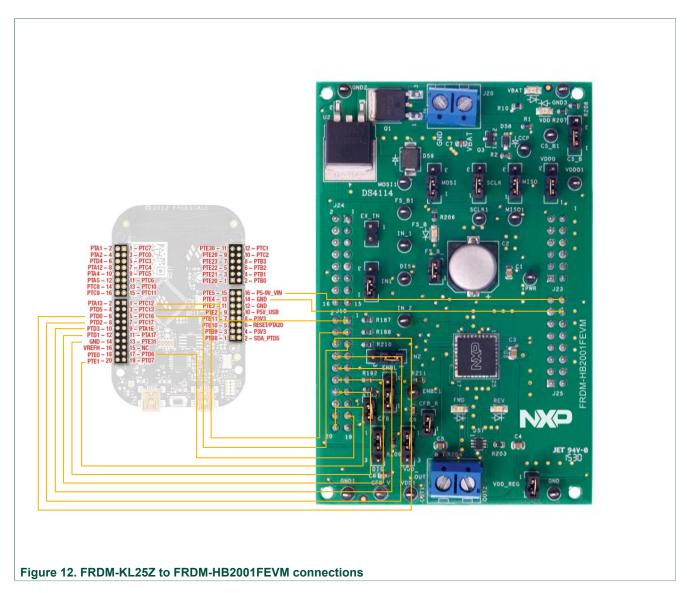

The FRDM-HB2001FEVM connects to the FRDM-KL25Z using the four dual row Arduino<sup>™</sup> R3 connectors on the bottom of the board (see <u>Table 9</u>, <u>Figure 11</u> and <u>Figure 12</u>).

Figure 11. Connecting the FRDM-HB2001FEVM to the FRDM-KL25Z

Table 9. FRDM-HB2001FEVM to FRDM-KL25Z connections

| FRDM-HB2001FEVM |     | FRDM-KL25Z |     | Pin hardware name |            | Description   |

|-----------------|-----|------------|-----|-------------------|------------|---------------|

| Header          | Pin | Header     | Pin | FRDM-HB2001FEVM   | FRDM-KL25Z | Description   |

| J24             | 1   | J1         | 1   | N/C               | PTC7       | No Connection |

| J24             | 2   | J1         | 2   | N/C               | PTA1       | No Connection |

| J24             | 3   | J1         | 3   | N/C               | PTC0       | No Connection |

| J24             | 4   | J1         | 4   | N/C               | PTA2       | No Connection |

| J24             | 5   | J1         | 5   | N/C               | PTC3       | No Connection |

| J24             | 6   | J1         | 6   | N/C               | PTD4       | No Connection |

| J24             | 7   | J1         | 7   | N/C               | PTC4       | No Connection |

| J24             | 8   | J1         | 8   | N/C               | PTA12      | No Connection |

| J24             | 9   | J1         | 9   | N/C               | PTC5       | No Connection |

| J24             | 10  | J1         | 10  | N/C               | PTA4       | No Connection |

| J24             | 11  | J1         | 11  | N/C               | PTC6       | No Connection |

| J24             | 12  | J1         | 12  | N/C               | PTA5       | No Connection |

KTFRDMHB2001FEVMUG

All information provided in this document is subject to legal disclaimers.

# KTFRDMHB2001FEVMUG

#### FRDM-HB2001FEVM evaluation board

| FRDM-HB: | 2001FEVM | FRDM-  | KL25Z | Pin hardwar     | re name    | Description                                                                              |

|----------|----------|--------|-------|-----------------|------------|------------------------------------------------------------------------------------------|

| Header   | Pin      | Header | Pin   | FRDM-HB2001FEVM | FRDM-KL25Z | Description                                                                              |

| J24      | 13       | J1     | 13    | N/C             | PTC10      | Not Connected                                                                            |

| J24      | 14       | J1     | 14    | N/C             | PTC8       | No Connection                                                                            |

| J24      | 15       | J1     | 15    | N/C             | PTC11      | Not Connected                                                                            |

| J24      | 16       | J1     | 16    | N/C             | PTC9       | No Connection                                                                            |

| J10      | 1        | J2     | 1     | DATA0/IN1       | PTC12      | IN1 signal for the H<br>Bridge                                                           |

| J10      | 2        | J2     | 2     | N/C             | PTA13      | No Connection                                                                            |

| J10      | 3        | J2     | 3     | DATA1/IN2       | PTC13      | IN2 signal for the H<br>Bridge                                                           |

| J10      | 4        | J2     | 4     | N/C             | PTD5       | No Connection                                                                            |

| J10      | 5        | J2     | 5     | FS_B            | PTC16      | Fault status pin to report fault                                                         |

| J10      | 6        | J2     | 6     | CS_B            | PTD0       | Chip select bar pin                                                                      |

| J10      | 7        | J2     | 7     | N/C             | PTC17      | No Connection                                                                            |

| J10      | 8        | J2     | 8     | MOSI            | PTD2       | Master output seria                                                                      |

| J10      | 9        | J2     | 9     | N/C             | PTA16      | No Connection                                                                            |

| J10      | 10       | J2     | 10    | MISO            | PTD3       | Master input serial output                                                               |

| J10      | 11       | J2     | 11    | N/C             | PTA17      | No Connection                                                                            |

| J10      | 12       | J2     | 12    | SCLK            | PTD1       | Clock for SPI                                                                            |

| J10      | 13       | J2     | 13    | N/C             | PTE31      | No Connection                                                                            |

| J10      | 14       | J2     | 14    | GND             | GND        | No Connection                                                                            |

| J10      | 15       | J2     | 15    | N/C             | N/C        | No Connection                                                                            |

| J10      | 16       | J2     | 16    | N/C             | VREFH      | No Connection                                                                            |

| J10      | 17       | J2     | 17    | CFB_READ        | PTD6       | ADC input for monitoring the CFE pin                                                     |

| J10      | 18       | J2     | 18    | N/C             | PTE0       | Disable signal to tr<br>state the output an<br>put the part in Slee<br>mode (Active Low) |

| J10      | 19       | J2     | 19    | N/C             | PTD7       | No Connection                                                                            |

| J10      | 20       | J2     | 20    | FRDM_VDD        | PTE1       | No Connection                                                                            |

| J23      | 1        | J10    | 1     | N/C             | PTE20      | No Connection                                                                            |

| J23      | 2        | J10    | 2     | N/C             | PTB0       | No Connection                                                                            |

| J23      | 3        | J10    | 3     | N/C             | PTE21      | No Connection                                                                            |

| J23      | 4        | J10    | 4     | N/C             | PTB1       | No Connection                                                                            |

| J23      | 5        | J10    | 5     | N/C             | PTE22      | No Connection                                                                            |

| J23      | 6        | J10    | 6     | N/C             | PTB2       | No Connection                                                                            |

| J23      | 7        | J10    | 7     | N/C             | PTE23      | No Connection                                                                            |

| J23      | 8        | J10    | 8     | N/C             | PTB3       | No Connection                                                                            |

| J23      | 9        | J10    | 9     | N/C             | PTE29      | No Connection                                                                            |

| J23      | 10       | J10    | 10    | N/C             | PTC2       | No Connection                                                                            |

| J23      | 11       | J10    | 11    | N/C             | PTE30      | No Connection                                                                            |

| J23      | 12       | J10    | 12    | N/C             | PTC1       | No Connection                                                                            |

| J25      | 1        | J9     | 1     | N/C             | PTB8       | No Connection                                                                            |

| J25      | 2        | J9     | 2     | N/C             | SDA_PTD5   | No Connection                                                                            |

|          |          | -      | 3     | N/C             | PTB9       |                                                                                          |

KTFRDMHB2001FEVMUG

All information provided in this document is subject to legal disclaimers.

| FRDM-HB2 | 2001FEVM | FRDM-  | KL25Z | Pin hardwa      | re name     | Decemention                                                         |

|----------|----------|--------|-------|-----------------|-------------|---------------------------------------------------------------------|

| Header   | Pin      | Header | Pin   | FRDM-HB2001FEVM | FRDM-KL25Z  | Description                                                         |

| J25      | 4        | J9     | 4     | N/C             | P3V3        | No Connection                                                       |

| J25      | 5        | J9     | 5     | N/C             | PTB10       | No Connection                                                       |

| J25      | 6        | J9     | 6     | N/C             | RESET/PTA20 | No Connection                                                       |

| J25      | 7        | J9     | 7     | N/C             | PTB11       | No Connection                                                       |

| J25      | 8        | J9     | 8     | N/C             | P3V3        | No Connection                                                       |

| J25      | 9        | J9     | 9     | N/C             | PTE2        | No Connection                                                       |

| J25      | 10       | J9     | 10    | N/C             | P5V_USB     | No Connection                                                       |

| J25      | 11       | J9     | 11    | N/C             | PTE3        | No Connection                                                       |

| J25      | 12       | J9     | 12    | GND             | GND         | Ground                                                              |

| J25      | 13       | J9     | 13    | N/C             | PTE4        | No Connection                                                       |

| J25      | 14       | J9     | 14    | GND             | GND         | No Connection                                                       |

| J25      | 15       | J9     | 15    | N/C             | PTE5        | No Connection                                                       |

| J25      | 16       | J9     | 16    | VDD_REG         | P5-9V_VIN   | 5.0 V logic input<br>to FRDM-KL25Z<br>board from FRDM<br>HB2001FEVM |

#### 6 Installing the software and setting up the hardware

#### 6.1 Configuring the hardware

The FRDM-HB2001FEVM consists of an H-Bridge, a parallel and SPI interface, power conditioning circuitry and an FRDM-KL25Z board. The board can be configured for use in conjunction with a FRDM-KL25Z board or a function generator.

#### Caution

When using the FRDM-HB2001FEVM, make sure that the maximum motor supply voltage (VPWR) stays within the 5.0 V to 40 V range. Operating outside this range may cause damage to the board.

# 6.1.1 Step-by-step instructions for setting up the hardware for use with a FRDM-KI 257

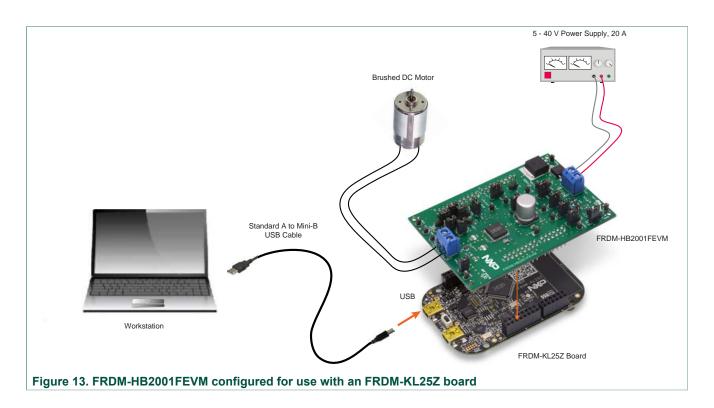

To configure the FRDM-HB2001FEVM for use with the FRDM-KL25Z do the following:

- Connect the FRDM-HB2001FEVM to the FRDM-KL25Z using the Arduino<sup>™</sup> connectors on each board.

- 2. Connect the USB cable (not supplied with the kit) between the PC and the KL25Z USB port on the FRDM-KL25Z board.

- 3. With the power switched off, attach the DC power supply to the VBAT and GND screw connector terminal (J20) on the evaluation board.

- 4. Connect the load to the screw terminal (J21).

Figure 13 illustrates the hardware configuration using a FRDM-KL25Z.

KTFRDMHB2001FEVMUG

All information provided in this document is subject to legal disclaimers.

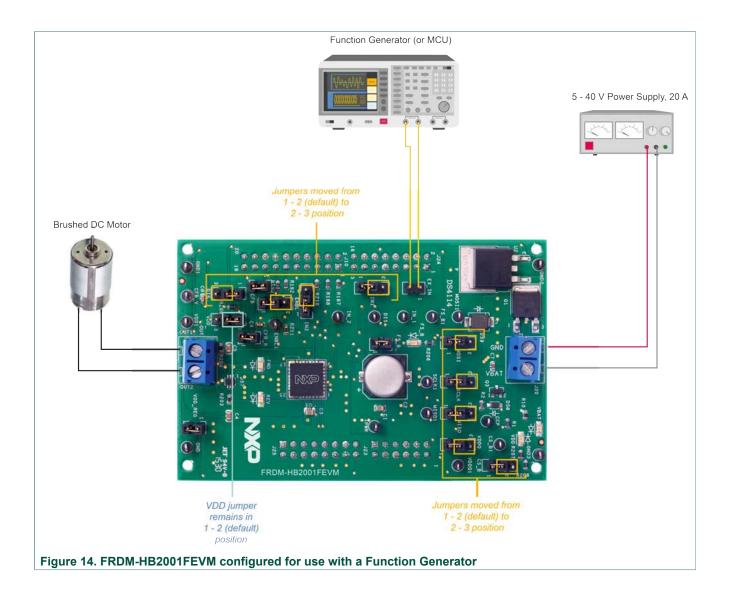

# 6.1.2 Step-by-step instructions for setting up the hardware for use with a function generator

This section describes how to configure the FRDM-HB2001FEVM for use with a function generator. The same connections apply if the board is connected to a microcontroller instead of a function generator. See the board description (Section 4.4 "Board description"), the schematic (Section 7 "Schematic") and the MC33HB2001 datasheet, to configure the board for use in a specific environment.

- 1. Connect the function generator to the EX\_IN jumper, with one channel attached to each pin.

- 2. Change the board jumper connections, as shown in Figure 14.

- 3. With the power switched off, attach the DC power supply to the VBAT and GND screw connector terminal (J20) on the evaluation board.

- 4. Connect the load to the screw terminal (J21).

Figure 14 illustrates the hardware configuration.

#### 6.2 Installing and using SPIGen

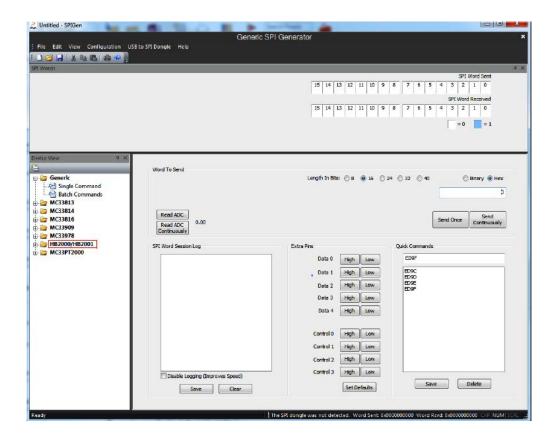

The latest version of SPIGen supports the MC33HB2001 and is designed to run on any Windows 8, Windows 7, Vista, or XP-based operating system. To install the software, do the following:

- 1. Go to <a href="www.nxp.com/SPIGen">www.nxp.com/SPIGen</a> and click **Download**.

- 2. When the SPIGEN: SPI Generator (SPIGen) Software page appears, go to the **Device Drivers** section and click **Download** associated with the description of the selected environment. A wizard guides the user through the process.

- 3. If instructed for the SPIGen wizard to create a shortcut, a SPIGen icon appears on the desktop. By default, the SPIGen executable file is installed at **C:Program Files \SPIGen**.

- Installing the device drivers overwrites any previous SPIGen installation and replaces it with a current version containing the MC33HB2001 drivers. However, configuration files (.spi) from the previous version remain intact.

- 4. Launch SPIGen. The HB2000/HB2001 device appears in the **Device View** panel.

KTFRDMHB2001FEVMUG

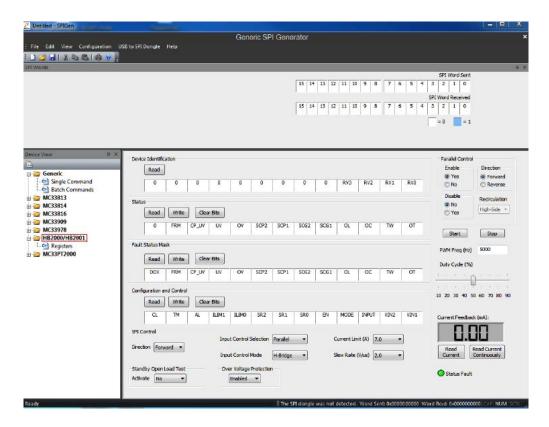

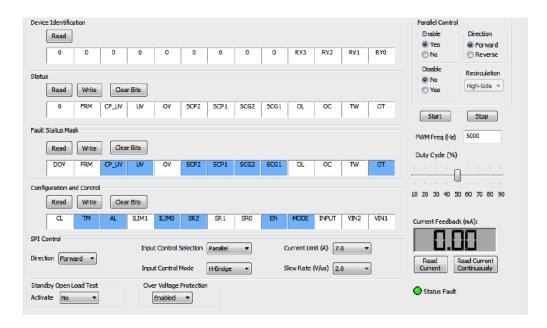

5. To access the HB2000/HB2001 tab in the SPIGen window, expand the HB2000/ HB2001 folder in the Device View. Then click **Registers** icon.

If the pre-programmed code on FRDM-KL25Z is accidentally erased, download "UsbSpiDongleKL25Z\_SPIDrive\_v512.srec" from the following link: <a href="www.nxp.com/usb-Spi-Dongle-firmware-KL25Z-HB2000-1">www.nxp.com/usb-Spi-Dongle-firmware-KL25Z-HB2000-1</a>.

6. Reading all the SPI Registers displays the following default status.

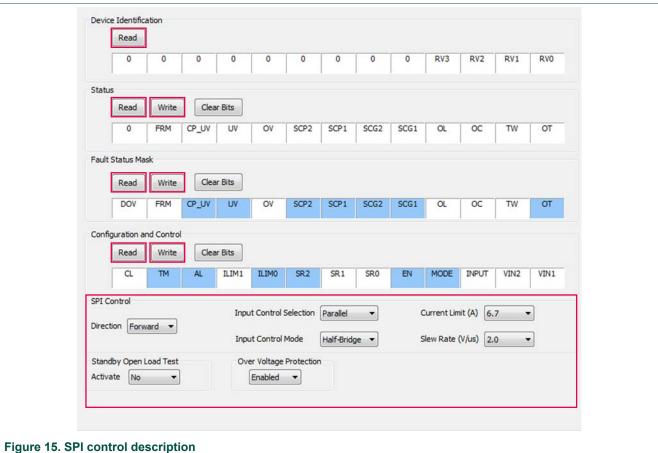

#### 6.2.1 SPI control

Table 10. SPI control description

| Name        | Description                                                                                                                                                                                                                                                                |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read        | Click the read button on top of each register to read the content of each register.                                                                                                                                                                                        |

| Write       | Click individual bits of any register and then press the corresponding write button to write into the register.                                                                                                                                                            |

| SPI Control | This section is designed for ease of use. Each dropdown menu sets or resets appropriate bits in the registers for a selected configuration. However, after configuration selection, press the write button of the corresponding register to be able to configure the part. |

#### 6.2.2 Parallel control

#### Direction:

- Forward: Current flowing through OUT1 to OUT2

- Reverse: Current flowing through OUT2 to OUT1

#### Recirculation:

- High-side: Freewheel-High (both high-side FETs turned on) during PWMing

- **Low-side**: Freewheel-Low (both low-side FETs turned on) during PWMing (only valid for Half-Bridge mode)

#### ENBL:

- Yes: ENBL is logic HIGH, the H-Bridge is operational

- No: ENBL is logic LOW, the H-Bridge outputs are tri-stated and placed in Sleep mode

#### DIS:

- DIS is logic HIGH, both OUT1 and OUT2 are tri-stated

- DIS is logic LOW, both OUT1 and OUT2 are enabled

#### **PWM Freq:**

• Enter PWM frequency up to 20000 Hz

#### **Duty Cycle:**

$\bullet$  Select PWM duty cycle from 10 to 90 %

#### Start

• After selection of parallel control configuration, press Start to activate the outputs

KTFRDMHB2001FEVMUG

All information provided in this document is subject to legal disclaimers.

#### Stop:

• Press **Stop** to deactivate the outputs

#### **Current Feedback:**

• Shows current through the high-side FET using the current recopy feature

#### Status Fault:

· Shows any fault condition in Sleep mode

Table 11. Logic behind direction control with High-side versus Low-side recirculation

| Half-Bridge Mode |                                                                 |

|------------------|-----------------------------------------------------------------|

|                  | Forward - High-side Recirculation                               |

| 1                | IN1 = 1                                                         |

|                  | IN2 = PWM signal with selected duty cycle and frequency         |

|                  | Reverse - High-side Recirculation                               |

| 2                | IN1 = PWM signal with selected duty cycle and frequency IN2 = 1 |

|                  | Forward - Low-side Recirculation                                |

| 3                | IN1 = PWM signal with selected duty cycle and frequency IN2 = 0 |

| 4                | Reverse - Low-side Recirculation                                |

|                  | IN1 = 0 IN2 = PWM signal with selected duty cycle and frequency |

| H-Bridge Mode |                                                                 |  |

|---------------|-----------------------------------------------------------------|--|

|               | Forward - High-side Recirculation                               |  |

| 1             | IN1 = 1 IN2 = PWM signal with selected duty cycle and frequency |  |

|               | Reverse - High-side Recirculation                               |  |

| 2             | IN1 = 0 IN2 = PWM signal with selected duty cycle and frequency |  |

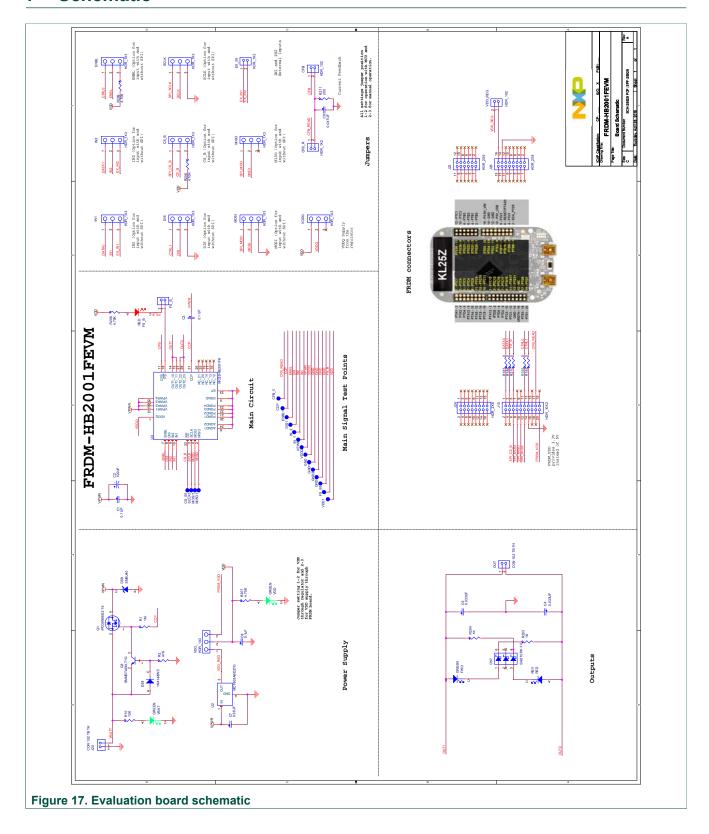

#### 7 Schematic

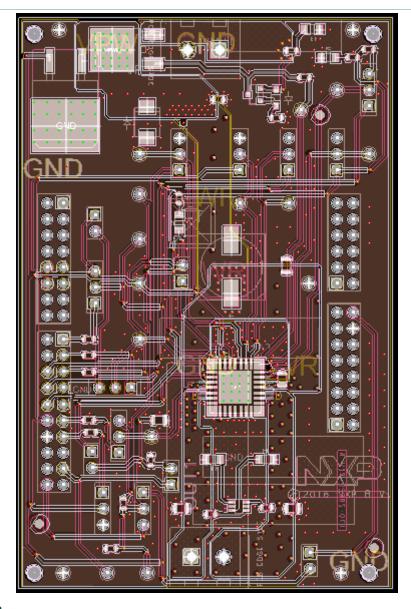

# 8 Board layout

Figure 18. Silkscreen

#### 9 Bill of materials

#### Table 12. Bill of materials

| Item                  | Qty               | Schematic label           | Value       | Description                                              | Part number         | Assy op |

|-----------------------|-------------------|---------------------------|-------------|----------------------------------------------------------|---------------------|---------|

| Active co             | mponer            | nts <sup>[1]</sup>        | -           |                                                          |                     |         |

| 1                     | 1                 | U1                        |             | IC DRV H-BRIDGE MOTOR 3.0 A 5.0 to 28 V SOIC32 – NXP     | MC33HB2001FK        | [2]     |

| 2                     | 1                 | U2                        |             | IC VREG 5.0 V 1.0 A 5.0 to 18 V D2PAK – ON Semiconductor | MC7805ABD2TG        | [2]     |

| Diodes <sup>[1]</sup> |                   |                           |             |                                                          |                     |         |

| 3                     | 1                 | D2                        | 24 V        | DIODE TVS UNIDIR 600 W 24 V AEC-Q101<br>SMB              | SMBJ24AHE3/52       |         |

| 4                     | 1                 | D57                       | 70 V        | DIODE SCH TRIPLE 70 mA 70 V / 200 MW<br>SOT363           | BAS70TW-7-F         |         |

| 5                     | 1                 | D58                       | 75 V        | DIODE SW 150 mA 75 V SOD-323                             | 1N4148WS-7-F        |         |

| 6                     | 2                 | D59, D64                  | 150 mA      | LED RED SGL 25 mA 0805                                   | 598-8110-107F       |         |

| 7                     | 3                 | D60, D61,<br>D63          | 25 mA       | LED RED SGL 25 mA 0805                                   | 598-8110-107F       |         |

| Capacito              | rs <sup>[1]</sup> |                           |             |                                                          |                     | '       |

| 8                     | 2                 | C1, C13                   | 0.1 μF      | CAP CER 0.1 µF 50 V 10 % X7R 0805                        | C0805C104K5RAC      |         |

| 9                     | 1                 | C2                        | 100 μF      | CAP ALEL 100 µF 50 V 20 % AEC-Q200<br>RADIAL SMT         | MAL214699104E3      |         |

| 10                    | 2                 | C4, C5                    | 0.033<br>μF | CAP CER 0.033 µF 50 V 10 % X7R 0805                      | 08055C333KAT2A      |         |

| 11                    | 1                 | C7                        | 0.33 μF     | CAP CER 0.33 µF 50 V 10 % X7R 0603                       | C1608X7R1H334K080AC |         |

| 12                    | 1                 | C8                        | 0.1 μF      | CAP CER 0.1 μF 16 V 10 % X7R AEC-Q200<br>0603            | GCM188R71C104KA37D  |         |

| 13                    | 1                 | C9                        | 0.047<br>μF | CAP CER 0.047 µF 25 V 10 % X7R 0603                      | C0603X7R250-473KNE  |         |

| Resistors             | s <sup>[1]</sup>  |                           |             | 1                                                        |                     |         |

| 14                    | 1                 | R1                        | 1.0 ΜΩ      | RES 1 MΩ 1/4 W 1 % AEC-Q200 0603                         | CRCW06031M00FKEAHP  |         |

| 15                    | 1                 | R2                        | 47 kΩ       | RES MF 47 kΩ 1/10 W 1.0 % AEC-Q200 0603                  | CRCW060347K0FKEA    |         |

| 16                    | 1                 | R10                       | 10 kΩ       | RES MF 10 kΩ 1/10 W 5 % AEC-Q200 0603                    | ERJ-3GEYJ103V       |         |

| 17                    | 4                 | R18, R188,<br>R192, R193  | 0 Ω         | RES MF 0 Ω 1/10 W – 0603                                 | CRCW06030000Z0EA    |         |

| 18                    | 1                 | R211                      | 200 Ω       | RES MF 200 Ω 1/10 W 1 % 0603                             | RK73H1JTTD2000F     |         |

| 19                    | 2                 | R203, R204                | 1.0 kΩ      | RES MF 1.0 KΩ 1/10 W 1 % 0603                            | AR03FTNX1001        |         |

| 20                    | 4                 | R206, R207,<br>R208, R209 | 4.70 kΩ     | RES MF 4.70 KΩ 1/10 W 1 % 0603                           | RK73H1JTTD4701F     |         |

| Switches              | , connec          | ctors, jumpers a          | and test po | oints <sup>[1]</sup>                                     |                     |         |

| Item | Qty | Schematic<br>label                                                                                               | Value | Description                                      | Part number        | Assy opt |

|------|-----|------------------------------------------------------------------------------------------------------------------|-------|--------------------------------------------------|--------------------|----------|

| 21   | 16  | IN1,<br>GND1,IN2,<br>GND2, GND3,<br>VPWR,<br>VDDQ, VDD,<br>SCLK, MOSI,<br>MISO, GND,<br>FS_B, ENBL,<br>DIS, CS_B |       | TEST POINT BLACK 40 MIL DRILL 180 MIL<br>TH 109L | 5001               |          |

| 22   | 11  | J1, J2, J3, J4,<br>J5, J6, J7, J8,<br>J14, J17                                                                   |       | HDR 1X3 TH 100 MIL SP 374H AU                    | 826629-3           |          |

| 23   | 1   | J10                                                                                                              |       | HDR 2X10 TH 100 MIL CTR 330H AU 100L             | TSW-110-07-S-D     |          |

| 24   | 4   | J11, J15, J18,<br>J19, J26                                                                                       |       | HDR 1X2 TH 100 MIL SP 378H AU 130L               | 826629-2           |          |

| 25   | 2   | J20, J21                                                                                                         |       | CON 1X2 TB TH 5.08 MM 543H SN 138L               | 20020316-H021B01LF |          |

| 26   | 1   | J23                                                                                                              |       | HDR 2X6 TH 100 MIL CTR 330H AU                   | TSW-106-07-S-D     |          |

| 27   | 2   | J24, J25                                                                                                         |       | HDR 2X8 TH 100 MIL CTR 330H AU                   | TSW-108-07-G-D     |          |

| 28   | 1   | Q1                                                                                                               |       | TRAN NMOS PWR 30 A 55 V AEC-Q101<br>TO252        | IPD30N06S2-15      |          |

| 29   | 1   | Q3                                                                                                               |       | TRAN NPN DRIVER 500 mA 80 V AEC-Q101 SOT23       | SMMBTA06LT1G       |          |

<sup>[1]</sup> NXP does not assume liability, endorse, or warrant components from external manufacturers are referenced in circuit drawings or tables. While NXP offers component recommendations in this configuration, it is the customer's responsibility to validate their application.

# 10 Accessory item bill of materials

Table 13. Accessory item bill of materials

| Item | Qty | Part Number               | Description                                                           |

|------|-----|---------------------------|-----------------------------------------------------------------------|

| 1    | 1   | FRDM-KL25Z <sup>[1]</sup> | NXP Freedom Development<br>Platform for Kinetis<br>KL14/15/24/25 MCUs |

NXP does not assume liability, endorse, or warrant components from external manufacturers are referenced in circuit drawings or tables. While NXP offers component recommendations in this configuration, it is the customer's responsibility to validate their application.

#### 11 References

Following are URLs where you can obtain information on related NXP products and application solutions:

| NXP.com support pages | Description            | URL                                    |

|-----------------------|------------------------|----------------------------------------|

| FRDM-HB2001FEVM       | Tool summary page      | http://www.nxp.com/FRDM-<br>HB2001FEVM |

| MC33HB2001            | Product summary page   | http://www.nxp.com/MC33HB2001          |

| FRDM-KL25Z            | Tool summary page      | http://www.nxp.com/FRDM-KL25Z          |

| SPIGen                | SPI generator software | http://www.nxp.com/SPIGEN              |

KTFRDMHB2001FEVMUG

All information provided in this document is subject to legal disclaimers.

<sup>[2]</sup> Critical components. For critical components, it is vital to use the manufacturer listed.

# 12 Revision history

| Revision | Date   | Description of changes |

|----------|--------|------------------------|

| 1.0      | 5/2016 | Initial release        |

#### 13 Contact information

Visit <a href="http://www.nxp.com/support">http://www.nxp.com/support</a> for a list of phone numbers within your region.

Visit <a href="http://www.nxp.com/warranty">http://www.nxp.com/warranty</a> to submit a request for tool warranty.

### 14 Legal information

#### 14.1 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

#### 14.2 Disclaimers

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit,

and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/ or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/salestermsandconditions.

#### 14.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

NXP — is a trademark of NXP B.V.

the NXP logo — is a trademark of NXP B.V.

Freescale — is a trademark of NXP B.V.

the Freescale logo — is a trademark of NXP B.V.

**SMARTMOS** — is a trademark of NXP B.V.

# KTFRDMHB2001FEVMUG

#### FRDM-HB2001FEVM evaluation board

#### **Tables**

| Tab. 1. | Device features            | 6  | Tab. 9.  | FRDM-HB2001FEVM to FRDM-KL252                 | 7            |

|---------|----------------------------|----|----------|-----------------------------------------------|--------------|

| Tab. 2. | Board description          | 9  |          | connections                                   | 17           |

|         |                            |    |          | SPI control description                       |              |

| Tab. 4. | Jumper locations           | 11 | Tab. 11. | Logic behind direction control with High-side | <del>)</del> |

| Tab. 5. | Input signal definitions   | 12 |          | versus Low-side recirculation                 | 26           |

| Tab. 6. | Output signal definitions  | 12 | Tab. 12. | Bill of materials                             | 29           |

| Tab. 7. | Test point definitions     | 13 | Tab. 13. | Accessory item bill of materials              | 30           |

| Tab. 8. | Screw terminal connections | 14 |          | •                                             |              |

# KTFRDMHB2001FEVMUG

#### FRDM-HB2001FEVM evaluation board

# **Figures**

| Fig. 1.  | Block diagram                         | 5  | Fig. 12. | FRDM-KL25Z to FRDM-HB2001FEVM      |    |

|----------|---------------------------------------|----|----------|------------------------------------|----|

| Fig. 2.  | Modes of operation                    | 6  |          | connections                        | 17 |

| Fig. 3.  | Architecture                          | 7  | Fig. 13. | FRDM-HB2001FEVM configured for use |    |

| Fig. 4.  | Thermal management                    | 8  |          | with an FRDM-KL25Z board           | 20 |

| Fig. 5.  | Board description                     | 9  | Fig. 14. | FRDM-HB2001FEVM configured for use |    |

| Fig. 6.  | LED locations                         | 10 |          | with a Function Generator          | 21 |

| Fig. 7.  | Jumper definitions                    | 11 | Fig. 15. | SPI control description            | 24 |

| Fig. 8.  | Test point locations                  | 13 | Fig. 16. | Parallel control description       | 25 |

| Fig. 9.  | Screw terminal locations              | 14 | Fig. 17. | Evaluation board schematic         | 27 |

| Fig. 10. | FRDM-KL25Z                            | 15 | Fig. 18. | Silkscreen                         | 28 |

| Fig. 11. | Connecting the FRDM-HB2001FEVM to the |    |          |                                    |    |

|          | FRDM-KL25Z                            | 16 |          |                                    |    |