# 12G UHD-SDI Re-timing **Adaptive Cable Equalizer**

## **Key Features**

- $75\Omega$  cable input interface with on-chip termination

- SMPTE ST 2082-1, ST 2081-1, ST 424, ST 292-1 and ST 259 compliant input/output

- Multi-standard operation from 1Mb/s to 11.88Gb/s

- In addition to standard SMPTE rates, the device also supports re-timing of DVB-ASI at 270Mb/s, and MADI at 125Mb/s

- 3D Input Signal Eye Monitor

- PRBS generator and checker

- Automatic cable equalization—typical equalized cable lengths of Belden 1694A cable:

- 80m at 11.88Gb/s

- 100m at 5.94Gb/s

- 190m at 2.97Gb/s

- 260m at 1.485Gb/s

- 450m at 270Mb/s and 125Mb/s

- Cable equalizer mode features:

- Automatic power down on loss of signal

- Programmable carrier detect with squelch threshold adjustment

- Programmable launch swing compensation for non-compliant source

- Manual and automatic cable equalizer bypass

- Trace driver features:

- Integrated 100Ω, differential output termination

- Extends output DC-coupling support with 1.2V to 2.5V output supply range

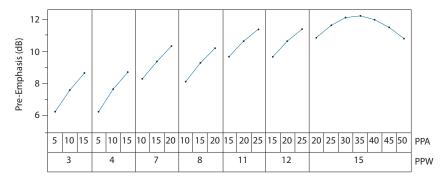

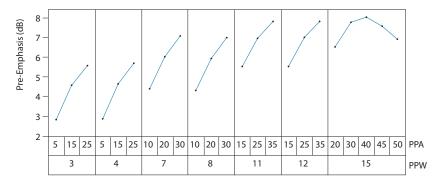

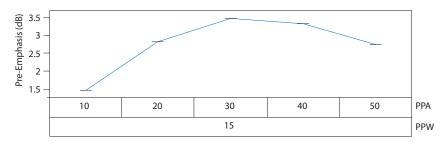

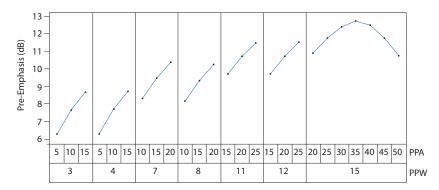

- Trace driver data output pre-emphasis to compensate for up to 20" FR4 at 11.88Gb/s

- Manual or automatic re-timer bypass

- Manual or automatic mute or disable on LOS

- CDR features:

- Manual or automatic rate modes

- Wide Loop bandwidth control

- Re-timing at the following data rates: 125Mb/s, 270Mb/s, 1.485Gb/s, 2.97Gb/s, 5.94Gb/s, and 11.88Gb/s—this includes the f/1.001 rates

### **Additional Features**

- Single 1.8V power supply for analog and digital core

- GSPI serial control and monitoring interface

- Four configurable GPIO pins for control or status monitoring

- Wide operating temperature range: -40°C to +85°C

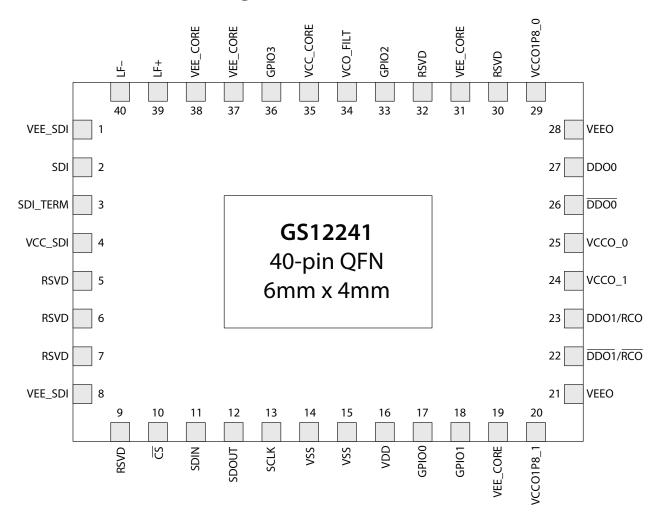

- Small 6mm x 4mm 40-pin QFN

- Pin compatible with the GS12141, GS12142, and GS3241

- Pb-free/Halogen-free/RoHS and WEEE compliant package

### **Applications**

Next Generation 12G UHD-SDI infrastructures designed to support UHDTV1, UHDTV2, 4K D-Cinema and 3D HFR and HDR production image formats. Typical applications: Monitors, Switchers, Distribution Amplifiers and Routers.

### Description

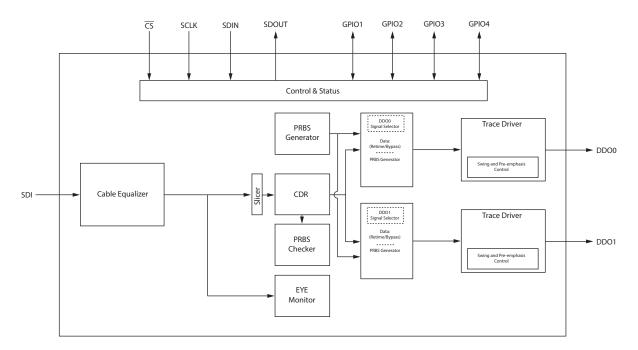

The GS12241 is a low-power, multi-rate re-timing Cable Equalizer supporting rates up to 12G UHD-SDI. It is designed to equalize and restore signals received over 80m coaxial cable at 12G, compensate for DC content of SMPTE pathological signals, and re-time the incoming data.

The integrated eye monitor provides non-disruptive mission mode analysis of the post equalized input signal. The 256x128 resolution scan matrix allows accurate signal analysis to speed up prototyping and enable field analysis.

Built in macros enable customizable cross section analysis and quick horizontal and vertical eye opening measurements.

With high phase consistency between scans and configurable space and time thresholds, algorithms can be deployed in the field to analyse long term signal quality variation (Bathtub Plot) to reduce costly system installation debug time for intermittent errors

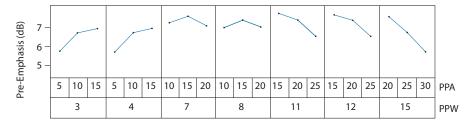

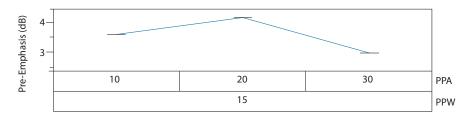

The two independently controlled trace drivers feature highly configurable pre-emphasis and swing controls to compensate for long trace and connector losses. The pre-emphasis pulse width can be optimized to compensate for perturbations to frequency response of transmission lines due to vias connectors and stubs. The GS12241 is pin compatible with the GS12141 single input and the GS12142 dual input 12G UHD-SDI Multi-rate Re-timing Cable Equalizers, as well as the GS3241 3G SDI Multi-rate Re-timing Cable Equalizer.

Note: For the GS12241 to be pin compatible with the GS12142, careful design considerations are required. Contact for your local Semtech FAE for details.

**GS12241 Functional Block Diagram**

# **Revision History**

| Version | ECO    | PCN | Date         | Changes and/or Modifications                                                                                                                                                 |

|---------|--------|-----|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5       | 041065 | _   | July 2018    | Updated Table 2-2, Section 4.2.3.1, Section 4.9.5.6, Section 4.7.6.2 and Section 5.                                                                                          |

| 4       | 040344 | _   | January 2018 | Updated Figure 1-1, Table 1-1, Table 2-2, Figure 6-1, Section 4.2.1 and Section 3.                                                                                           |

| 3       | 037798 | _   | August 2017  | Added Section 4.7.3, updated Table 2-2 and Table 2-3.                                                                                                                        |

| 2       | 037112 | _   | June 2017    | Updated Section 4.5, Table 5-3, Section 4.9.13 and added Section 4.9.12.                                                                                                     |

| 1       | 033958 | _   | May 2017     | Updates as described in the GS12241 Errata (PDS-061436, ECO-034464). Rewrite of Section 4.4, Section 4.5, Section 4.6 Updated Table 2-2, Table 2-3, Table 5-1 and Table 5-2. |

| 0       | 033177 | _   | October 2016 | New Document.                                                                                                                                                                |

## **Contents**

| 1. Pin Out                                                | 5  |

|-----------------------------------------------------------|----|

| 1.1 GS12241 Pin Assignment                                | 5  |

| 1.2 GS12241 Pin Descriptions                              | 6  |

| 2. Electrical Characteristics                             | 9  |

| 2.1 Absolute Maximum Ratings                              | 9  |

| 2.2 DC Electrical Characteristics                         | 10 |

| 2.3 AC Electrical Characteristics                         | 12 |

| 3. Input/Output Circuits                                  | 14 |

| 4. Detailed Description                                   | 15 |

| 4.1 Device Description                                    | 15 |

| 4.1.1 Sleep Mode                                          | 15 |

| 4.2 Cable Equalizer                                       | 16 |

| 4.2.1 Cable Equalizer Bypass                              | 16 |

| 4.2.2 Upstream Launch Swing Compensation                  | 16 |

| 4.2.3 Carrier Detect, Squelch Control, and Loss of Signal | 17 |

| 4.3 Serial Digital Re-timer (CDR)                         | 19 |

| 4.3.1 PLL Loop Bandwidth Control                          | 20 |

| 4.3.2 Automatic and Manual Rate Detection                 | 20 |

| 4.3.3 Lock Time                                           | 21 |

| 4.4 PRBS Checker                                          | 23 |

| 4.4.1 Timed PRBS Check Measurement Procedure              | 23 |

| 4.4.2 Continuous PRBS Check Measurement Procedure         | 24 |

| 4.5 EYE Monitor                                           | 27 |

|                                                           |    |

| 4.5.1 Shape Scan and Measurement Time                 | 28  |

|-------------------------------------------------------|-----|

| 4.5.2 Matrix-Scan and Shape-Scan Operation            | 30  |

| 4.6 PRBS Generator                                    | 36  |

| 4.7 Output Drivers                                    | 38  |

| 4.7.1 Bypassed Re-timer Signal Output Control         | 38  |

| 4.7.2 Output Driver Polarity Inversion                | 39  |

| 4.7.3 Output Driver Data Rate Selection               | 39  |

| 4.7.4 Amplitude and Pre-Emphasis Control              | 39  |

| 4.7.5 Trace Driver DC coupling requirements           | 47  |

| 4.7.6 Output State Control Modes                      | 48  |

| 4.8 GPIO Controls                                     | 50  |

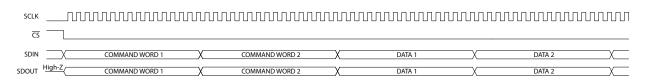

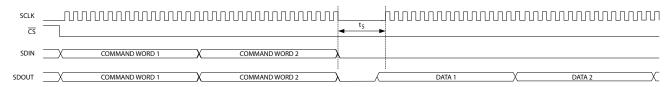

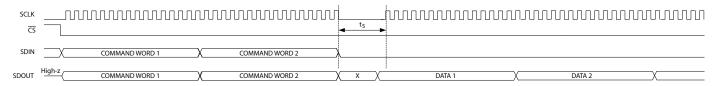

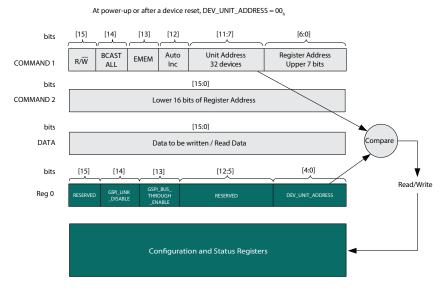

| 4.9 GSPI Host Interface                               | 50  |

| 4.9.1 CS Pin                                          | 50  |

| 4.9.2 SDIN Pin                                        | 50  |

| 4.9.3 SDOUT Pin                                       | 51  |

| 4.9.4 SCLK Pin                                        | 52  |

| 4.9.5 Command Word 1 Description                      | 52  |

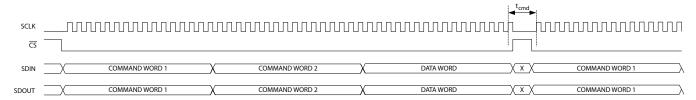

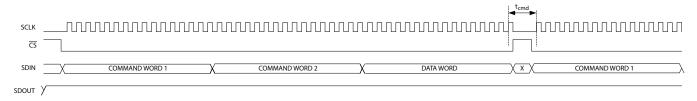

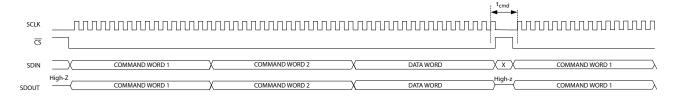

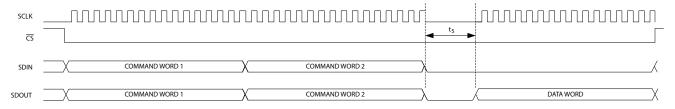

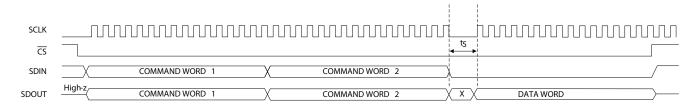

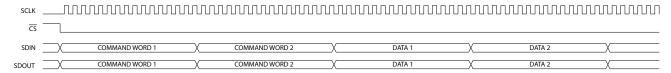

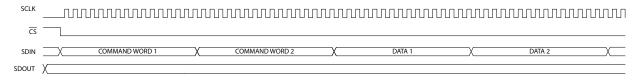

| 4.9.6 GSPI Transaction Timing                         | 55  |

| 4.9.7 Single Read/Write Access                        | 56  |

| 4.9.8 Auto-increment Read/Write Access                | 58  |

| 4.9.9 Setting a Device Unit Address                   | 59  |

| 4.9.10 Default GSPI Operation                         | 60  |

| 4.9.11 Clear Sticky Counts Through Four Way Handshake | 61  |

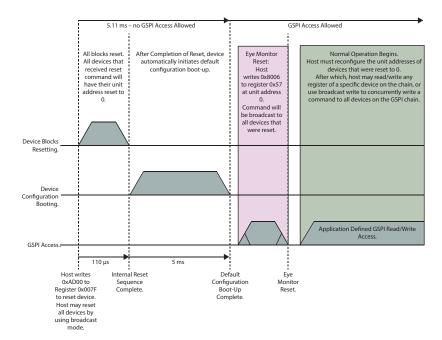

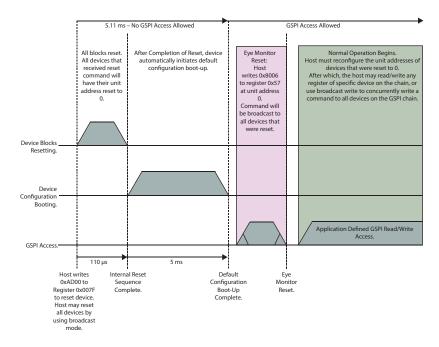

| 4.9.12 Device Power-up Sequence                       | 61  |

| 4.9.13 Host Initiated Device Reset                    | 62  |

| 5. Register Map                                       | 64  |

| 5.1 Control Registers                                 | 64  |

| 5.2 Status Registers                                  | 67  |

| 5.3 Register Descriptions                             | 68  |

| 6. Application Information                            | 104 |

| 6.1 Typical Application Circuit                       | 104 |

| 7. Package & Ordering Information                     | 105 |

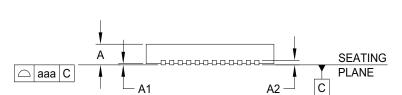

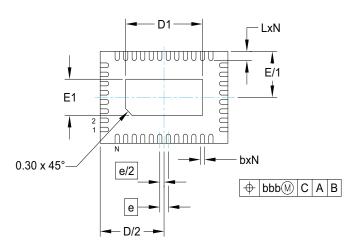

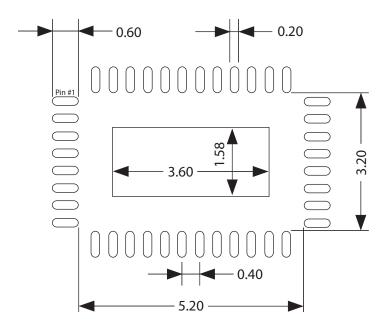

| 7.1 Package Dimensions                                | 105 |

| 7.2 Recommended PCB Footprint                         |     |

| 7.3 Packaging Data                                    |     |

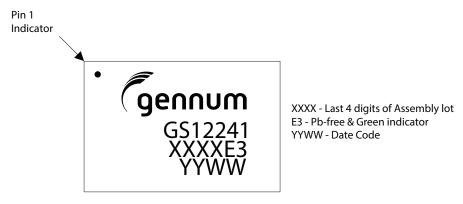

| 7.4 Marking Diagram                                   | 107 |

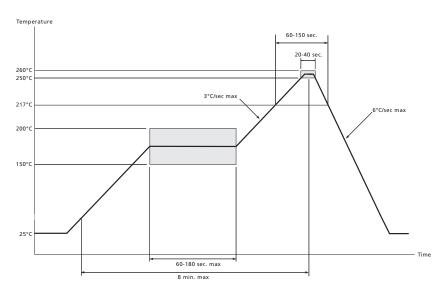

| 7.5 Solder Reflow Profiles                            |     |

| 7.6 Ordering Information                              |     |

|                                                       |     |

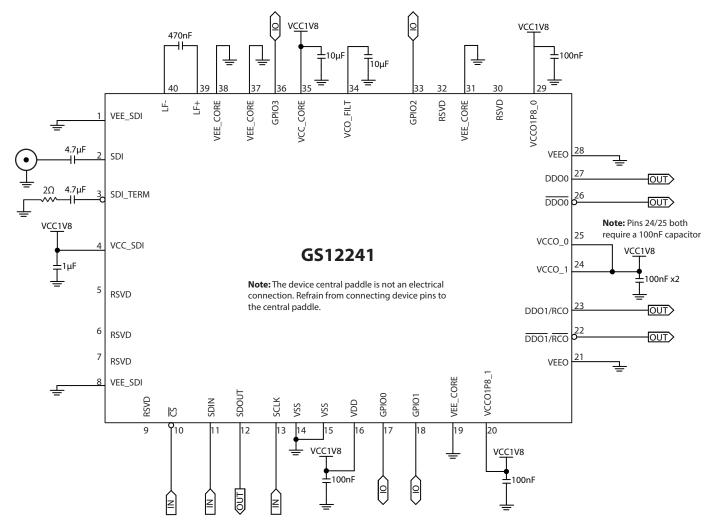

# 1. Pin Out

## 1.1 GS12241 Pin Assignment

Figure 1-1: GS12241 Pin Assignment

# 1.2 GS12241 Pin Descriptions

Table 1-1: GS12241 Pin Descriptions

| Pin Number         | Name      | Туре                    | Description                                                                                                                                                                                                                                                    |

|--------------------|-----------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1,8                | VEE_SDI   | Power                   | Most negative power supply connection for the Cable Equalizer. Connect to ground.                                                                                                                                                                              |

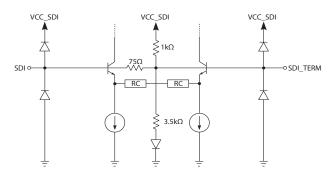

| 2                  | SDI       | Input                   | Single-ended CML input with internal $75\Omega$ termination.                                                                                                                                                                                                   |

| 3                  | SDI_TERM  | _                       | Input Common Mode termination. Decouple to ground through resistor and capacitor. See Section 6.1 for recommended values.                                                                                                                                      |

| 4                  | VCC_SDI   | Power                   | Most positive power supply connection for the Cable Equalizer.  Connect to 1.8V and decouple to ground. See Section 6.1 for recommended values.                                                                                                                |

| 5, 6, 7, 9, 30, 32 | RSVD      | _                       | These pins may be left floating. Please contact your Semtech FAE for additional information on circuit compatibility with the GS12281.                                                                                                                         |

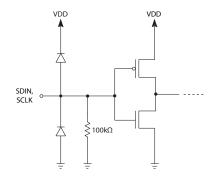

| 10                 | <u>cs</u> | Digital Input           | Chip Select input for the Gennum Serial Peripheral Interface (GSPI) host control/status port. $1.8V\ CMOS\ input\ with\ 100k\Omega\ pull-up.$ Active-LOW input. $Refer\ to\ Section\ 4.9.1\ for\ more\ details.$                                               |

| 11                 | SDIN      | Digital Input           | Serial digital data input for the Gennum Serial Peripheral Interface (GSPI) host control/status port.<br>1.8V CMOS input with $100k\Omega$ pull-down.<br>Refer to Section 4.9.2 for more details.                                                              |

| 12                 | SDOUT     | Digital Output          | Serial digital data output for the Gennum Serial Peripheral Interface (GSPI) host control/status port.  1.8V CMOS output.  Refer to Section 4.9.3 for more details.                                                                                            |

| 13                 | SCLK      | Digital Input           | Burst-mode clock input for the Gennum Serial Peripheral Interface (GSPI) host control/status port.<br>1.8V CMOS input with $100k\Omega$ pull-down.<br>Refer to Section 4.9.4 for more details.                                                                 |

| 14, 15             | VSS       | Power                   | Most negative power supply for digital core logic. Connect to ground.                                                                                                                                                                                          |

| 16                 | VDD       | Power                   | Most positive power supply connection for digital core logic.  Connect to 1.8V and decouple to ground. See Section 6.1 for recommended values.                                                                                                                 |

| 17                 | GPIO0     | Digital<br>Input/Output | Multi-function Control/Status Input/Output 0.  Default function:  Direction = Output  Signal = High indicates LOS (Loss of Signal, inverse of Carrier Detect)  Pin is 1.8V CMOS I/O, please refer to GPIOO_CFG for more information on how to configure GPIOO. |

Table 1-1: GS12241 Pin Descriptions (Continued)

| Pin Number     | Name                  | Туре                    | Description                                                                                                                                                                                                                  |

|----------------|-----------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18             | GPIO1                 | Digital<br>Input/Output | Multi-function Control/Status Input/Output 1.  Default function:  Direction = Output  Signal = High indicates PLL is locked  Pin is 1.8V CMOS I/O, please refer to GPIO1_CFG for more information on how to configure GPIO1. |

| 19, 31, 37, 38 | VEE_CORE              | Power                   | Most negative power supply connection for the analog core. Connect to ground.                                                                                                                                                |

| 20             | VCCO1P8_1             | Power                   | Most positive power supply connection for trace driver pre driver. Connect to 1.8V and decouple to ground. See Section 6.1 for recommended values.                                                                           |

| 21, 28         | VEEO                  | Power                   | Most negative power supply connection for the output drivers.  Connect to ground.                                                                                                                                            |

| 22, 23         | DDO1/RCO,<br>DDO1/RCO | Output                  | Differential CML output with two internal $50\Omega$ pull-ups. The data signal or PRBS generator can be selected for this output. The PRBS generator can be configured to generate a PRBS7 or a clock pattern.               |

| 24             | VCCO_1                | Power                   | Most positive power supply connection for the DDO1/ $\overline{DDO1}$ output driver.  Connect to 1.2V – 2.5V and decouple to ground. See Section 6.1 for recommended values.                                                 |

| 25             | VCCO_0                | Power                   | Most positive power supply connection for the DDO0/ $\overline{DDO0}$ output driver.  Connect to 1.2V – 2.5V and decouple to ground. See Section 6.1 for recommended values.                                                 |

| 26, 27         | DDO0/DDO0             | Output                  | Differential CML output with two internal $50\Omega$ pull-ups. The data signal or PRBS generator can be selected for this output. The PRBS generator can be configured to generate a PRBS7 or a clock pattern.               |

| 29             | VCCO1P8_0             | Power                   | Most positive power supply connection for trace driver pre driver. Connect to 1.8V and decouple to ground. See Section 6.1 for recommended values.                                                                           |

| 33             | GPIO2                 | Digital<br>Input/Output | Multi-function Control/Status Input/Output 2.  Default function:  Direction = Input Signal = Set HIGH to put device in sleep Pin is 1.8V CMOS I/O, please refer to GPIO2_CFG for more information on how to configure GPIO2. |

| 34             | VCO_FILT              | Passive                 | VCO filter capacitor connection. Decouple to ground. See Section 6.1 for recommended values.                                                                                                                                 |

| 35             | VCC_CORE              | Power                   | Most positive power supply connection for the analog core.  Connect to 1.8V and decouple to ground. See Section 6.1 for recommended values.                                                                                  |

Table 1-1: GS12241 Pin Descriptions (Continued)

| Pin Number | Name     | Туре                    | Description                                                                                                                                                                                                                                     |

|------------|----------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |          |                         | Multi-function Control/Status Input/Output 3.                                                                                                                                                                                                   |

|            |          |                         | Default function:                                                                                                                                                                                                                               |

| 36         | 36 GPIO3 | Digital<br>Input/Output | Direction = Input<br>Signal = Set HIGH to disable DDO1                                                                                                                                                                                          |

| _          |          |                         | Pin is 1.8V CMOS I/O, please refer to GPIO3_CFG for more information on how to configure GPIO3.                                                                                                                                                 |

| 39         | LF+      | Passive                 | Loop filter capacitor connection. Connect to pin 40 through capacitor. See Section 6.1 for recommended values.                                                                                                                                  |

| 40         | LF-      | Passive                 | Loop filter capacitor connection. Connect to pin 39 through capacitor. See Section 6.1 for recommended values.                                                                                                                                  |

| Tab        | _        | <del>-</del>            | Central paddle can be connected to ground or left unconnected. Its purpose is to provide increased mechanical stability. It is not required for thermal dissipation. It is not recommended to connect device ground pins to the central paddle. |

# 2. Electrical Characteristics

# 2.1 Absolute Maximum Ratings

**Table 2-1: Absolute Maximum Ratings**

| Parameter                                                    | Value                    |

|--------------------------------------------------------------|--------------------------|

| Supply Voltage—Core<br>(VCC_SDI, VCC_CORE, VDD)              | -0.5V to +2.2V           |

| Supply Voltage—Output Driver (VCCO_0, VCCO_1)                | -0.5V to +2.8V           |

| Input ESD Voltage (any pin)                                  | 2kV HBM                  |

| Storage Temperature Range (T <sub>S</sub> )                  | -50°C to +125°C          |

| Input Voltage Range (SDI, SDI)                               | -0.3 to (VCC_SDI +0.3)V  |

| Input Voltage Range (GPIO2, GPIO3)                           | -0.3 to (VCC_CORE +0.3)V |

| Input Voltage Range (CS, SDIN, SCLK, VSS, VDD, GPIO0, GPIO1) | -0.3 to (VDD +0.3)V      |

| Solder Reflow Temperature                                    | 260°C                    |

**Note:** Absolute Maximum Ratings are those values beyond which damage may occur. Functional operation outside of the ranges shown in the AC/DC electrical characteristics tables is not guaranteed.

# 2.2 DC Electrical Characteristics

**Table 2-2: DC Electrical Characteristics**

$T_A = -40$ °C to +85°C, unless otherwise shown.

| Parameter                                  | Symbol                                           | Conditions                                             | Min  | Тур | Max  | Units | Notes |

|--------------------------------------------|--------------------------------------------------|--------------------------------------------------------|------|-----|------|-------|-------|

| Supply Voltage                             | VCC_SDI,<br>VCC_CORE,<br>VDD                     |                                                        | 1.71 | 1.8 | 1.89 | V     | _     |

|                                            |                                                  |                                                        | 1.14 | 1.2 | 1.26 | V     | _     |

| Supply Voltage - Output<br>Driver          | VCCO_0,<br>VCCO_1                                |                                                        | 1.71 | 1.8 | 1.89 | V     | _     |

|                                            |                                                  |                                                        | 2.38 | 2.5 | 2.63 | V     | _     |

|                                            |                                                  | VCCO_0 = 1.2V,<br>Output Swing = $400 \text{mV}_{ppd}$ | _    | 405 | _    | mW    | 1     |

| Power—Mission Mode                         |                                                  | VCCO_0 = 1.8V,<br>Output Swing = 400mV <sub>ppd</sub>  | _    | 410 | _    | mW    | 1     |

| (DD00/DD00 enabled,<br>DD01/DD01 disabled) | P <sub>D</sub>                                   | VCCO_0 = 1.8V,<br>Output Swing = 800mV <sub>ppd</sub>  | _    | 430 | _    | mW    | 1     |

|                                            |                                                  | VCCO_0 = 2.5V,<br>Output Swing = 400mV <sub>ppd</sub>  | _    | 420 | _    | mW    | 1     |

|                                            |                                                  | VCCO_0 = 2.5V,<br>Output Swing = 800mV <sub>ppd</sub>  | _    | 440 | _    | mW    | 1     |

| Power—Sleep Mode                           | $P_{D}$                                          | Sleep                                                  | _    | 35  | 50   | mW    | _     |

|                                            | l <sub>cco_0</sub> , l <sub>cco_1</sub>          | VCCO = 1.2V,<br>Output Swing = 400mV <sub>ppd</sub>    | _    | 9   | 16   | mA    | 1,3   |

|                                            |                                                  | VCCO = 1.8V,<br>Output Swing = 400mV <sub>ppd</sub>    | _    | 9   | 16   | mA    | 1,3   |

| Supply Current—Trace Driver                |                                                  | VCCO = 1.8V,<br>Output Swing = 800mV <sub>ppd</sub>    | _    | 18  | 27   | mA    | 1,3   |

|                                            |                                                  | VCCO = 2.5V,<br>Output Swing = 400mV <sub>ppd</sub>    | _    | 9   | 16   | mA    | 1,3   |

|                                            |                                                  | VCCO = 2.5V,<br>Output Swing = 800mV <sub>ppd</sub>    | _    | 18  | 27   | mA    | 1,3   |

| Supply Current—Trace Driver<br>Pre-driver  | I <sub>CCO1P8_0</sub> ,<br>I <sub>CCO1P8_1</sub> | VCCO1P8_0<br>Output Swing = 800mV <sub>ppd</sub>       | _    | 25  | 32   | mA    | 1,3   |

|                                            |                                                  | VCCO1P8_1<br>Output Swing = 800mV <sub>ppd</sub>       | _    | 25  | 32   | mA    | 1,3   |

## **Table 2-2: DC Electrical Characteristics (Continued)**

$T_A = -40$ °C to +85°C, unless otherwise shown.

| Parameter                         | Symbol               | Conditions                         | Min                | Тур                                        | Max               | Units | Notes |

|-----------------------------------|----------------------|------------------------------------|--------------------|--------------------------------------------|-------------------|-------|-------|

|                                   |                      | CDR Locked to Rate                 | _                  | 124                                        | 142               | mA    | _     |

| Supply Current—Analog             |                      | CDR Unlocked During<br>Rate Search | _                  | 182                                        | 208               | mA    | _     |

| Core                              | I <sub>CC_CORE</sub> | PRBS Generator Enabled             | _                  | 119                                        | 140               | mA    | 4,5   |

|                                   |                      | PRBS Checker Enabled               | _                  | 55                                         | 94                | mA    | 4     |

|                                   |                      | Eye Monitor Enabled                | _                  | 50                                         | 92                | mA    | 4     |

| Supply Current—Cable<br>Equalizer | I <sub>CC_SDI</sub>  | _                                  | _                  | 55                                         | 75                | mA    | _     |

| Supply Current—Digital<br>Logic   | I <sub>DD</sub>      | _                                  | _                  | 15                                         | 18                | mA    | _     |

| DDO Output Common<br>Mode Voltage | V <sub>CMOUT</sub>   | _                                  | _                  | V <sub>CCO</sub> -<br>ΔV <sub>DDO</sub> /2 | _                 |       | 2     |

| DDO<br>Output Termination         |                      | Differential                       | _                  | 100                                        | _                 | Ω     | 2     |

| SDI Input Termination             |                      | Between SDI and GND                | _                  | 75                                         | _                 | Ω     | _     |

| Input Voltage—Digital Pins        | V <sub>IH</sub>      |                                    | 0.65*<br>VDD       | _                                          | VDD               | V     | _     |

| (CS, SDIN, SCLK, GPIO[0:1])       | $V_{IL}$             |                                    | 0                  | _                                          | 0.35*<br>VDD      | V     | _     |

| Input Voltage—Digital Pins        | V <sub>IH</sub>      |                                    | 0.65*<br>VCC_CORE  | _                                          | VCC_CORE          | V     | _     |

| (GPIO[2:3])                       | V <sub>IL</sub>      |                                    | 0                  | _                                          | 0.35*<br>VCC_CORE | V     | _     |

| Output Voltage—Digital Pins       | V <sub>OH</sub>      | I <sub>OH</sub> = -5mA             | VDD -<br>0.45      | _                                          | _                 | V     | _     |

| (SDOUT, GPIO[0:1]) —              | V <sub>OL</sub>      | $I_{OL} = +5mA$                    | _                  | _                                          | 0.45              | V     | _     |

| Output Voltage—Digital Pins       | V <sub>OH</sub>      | I <sub>OH</sub> = -5mA             | VCC_CORE<br>- 0.45 | _                                          | _                 | V     | _     |

| (GPIO[2:3]) —                     | V <sub>OL</sub>      | $I_{OL} = +5mA$                    | _                  | _                                          | 0.45              | V     |       |

#### Notes:

- 1. Pre-emphasis is disabled.

- 2. This applies for DDO0 and DDO1.

- 3. The specifications provided are per symbol, not a combined value.

- 4. Current listed is an increase to ICC\_CORE when stated condition is true.

- 5. Selected clock source = VCO free running.

# 2.3 AC Electrical Characteristics

**Table 2-3: AC Electrical Characteristics**

$VCC\_SDI, VCC\_CORE, VDD = 1.8V \pm 5\% \ and \ VCCO\_0, VCCO\_1 = +1.2/1.8/2.5V \pm 5\%, T_A = -40^{\circ}C \ to \ +85^{\circ}C, \ unless \ otherwise \ shown.$

| Parameter                         | Symbol                                         | Conditions          | Min   | Тур  | Max   | Units             | Notes |

|-----------------------------------|------------------------------------------------|---------------------|-------|------|-------|-------------------|-------|

| Serial Input Data Rate            | DR <sub>SDI</sub>                              | _                   | 0.001 | _    | 11.88 | Gb/s              | 12    |

| Upstream Launch Swing             | $V_{SDI}$                                      | _                   | 720   | 800  | 880   | mV <sub>pp</sub>  | 3     |

| Differential Output               | A\/                                            | 200mV               | 150   | 200  | 250   | mV <sub>ppd</sub> | 8     |

| oltage Swing                      | $\Delta V_{ m DDO}$                            | 800mV               | 600   | 800  | 1000  | mV <sub>ppd</sub> | 9     |

| Intrinsic Input Jitter Tolerance  | TUI                                            | 12G                 | 0.7   | 0.85 | _     | UI                | _     |

| intrinsic input sitter folerance  | 1131                                           | MADI/SD/HD/3G/6G    | 0.8   | 0.95 | _     | UI                | _     |

| PLL Lock Time—<br>Asynchronous    | t <sub>ALOCK</sub>                             | _                   | _     | 75   | _     | ms                | 5     |

| PLL Lock Time—Synchronous         | t <sub>SLOCK</sub>                             | SD                  | _     | _    | 10    | μs                | 5     |

| FEE LOCK TIME—Synchronous         | SLOCK                                          | HD/3G/6G/12G        | _     | _    | 2     | μs                | 5     |

| DDO, DDO, Rise/Fall Time          | t <sub>riseDDO</sub> ,<br>t <sub>fallDDO</sub> | All rates           | _     | _    | 40    | ps                | 6,11  |

| DDO Mismatch in<br>Rise/Fall Time | _                                              | _                   | _     |      | 8     | ps                | 6     |

| DDO Duty Cycle Distortion         | _                                              | _                   | _     | _    | 10    | ps                | 6,11  |

|                                   |                                                | 5MHz to 1.485GHz    | _     | _    | -17   | dB                | 1     |

| Input Return Loss                 | _                                              | 1.485GHz to 2.97GHz | _     | _    | -12   | dB                | 1     |

| input neturi 2033                 |                                                | 2.97GHz to 5.94GHz  | _     | _    | -8    | dB                | 1     |

|                                   |                                                | 5.94GHz to 11.88GHz | _     | _    | -5    | dB                | 1     |

|                                   | t <sub>OJ(125Mb/s)</sub>                       | 450m                | _     | 0.01 | 0.05  | Ul <sub>pp</sub>  | 2,10  |

| _                                 | t <sub>OJ(270Mb/s)</sub>                       | 450m                | _     | 0.05 | 0.20  | Ul <sub>pp</sub>  | 2,10  |

| Serial Data Output Jitter         | t <sub>OJ(270Mb/s)</sub>                       | 400m                | _     | 0.05 | 0.10  | Ul <sub>pp</sub>  | 2,10  |

| DD00, DD00                        | t <sub>OJ(1.485Gb/s)</sub>                     | 260m                | _     | 0.03 | 0.10  | Ul <sub>pp</sub>  | 2,10  |

| DD01, DD01                        | t <sub>OJ(2.97Gb/s)</sub>                      | 190m                | _     | 0.05 | 0.10  | Ul <sub>pp</sub>  | 2,10  |

| <del>-</del>                      | t <sub>OJ(5.94Gb/s)</sub>                      | 100m                | _     | 0.07 | 0.15  | Ul <sub>pp</sub>  | 2,10  |

| _                                 | t <sub>OJ(11.88Gb/s)</sub>                     | 80m                 | _     | 0.07 | 0.15  | Ul <sub>pp</sub>  | 2,10  |

### **Table 2-3: AC Electrical Characteristics (Continued)**

$VCC\_SDI, VCC\_CORE, VDD = 1.8V \pm 5\% \ and \ VCCO\_0, VCCO\_1 = +1.2/1.8/2.5V \pm 5\%, T_A = -40 ^{\circ}C \ to \ +85 ^{\circ}C, \ unless \ otherwise \ shown.$

| Parameter            | Symbol                        | Conditions             | Min | Тур  | Max | Units | Notes |

|----------------------|-------------------------------|------------------------|-----|------|-----|-------|-------|

|                      |                               | Setting 0.0625x        | _   | 10   | _   | kHz   | 7     |

|                      |                               | Setting 0.125x         | _   | 20   | _   | kHz   | 7     |

|                      | BW <sub>LOOP(125Mb/s)</sub>   | Setting 0.25x          | _   | 38   | _   | kHz   | 7     |

|                      |                               | Setting 0.5x (Default) | _   | 76   | _   | kHz   | 7     |

|                      |                               | Setting 1.0x           | _   | 150  | _   | kHz   | 7     |

|                      |                               | Setting 0.0625x        | _   | 20   | _   | kHz   | 7     |

|                      |                               | Setting 0.125x         | _   | 40   | _   | kHz   | 7     |

|                      | BW <sub>LOOP(270Mb/s)</sub>   | Setting 0.25x          | _   | 80   | _   | kHz   | 7     |

|                      |                               | Setting 0.5x           | _   | 160  | _   | kHz   | 7     |

|                      |                               | Setting 1.0x (Default) | _   | 316  | _   | kHz   | 7     |

|                      |                               | Setting 0.0625x        | _   | 110  | _   | kHz   | 7     |

|                      | BW <sub>LOOP(1.485Gb/s)</sub> | Setting 0.125x         | _   | 220  | _   | kHz   | 7     |

|                      |                               | Setting 0.25x          | _   | 440  | _   | kHz   | 7     |

|                      |                               | Setting 0.5x (Default) | _   | 876  | _   | kHz   | 7     |

| PLL Loop Bandwidth   |                               | Setting 1.0x           | _   | 1750 | _   | kHz   | 7     |

| PLL LOOP Ballawiatti | BW <sub>LOOP(2.97Gb/s)</sub>  | Setting 0.0625x        | _   | 220  | _   | kHz   | 7     |

|                      |                               | Setting 0.125x         | _   | 440  | _   | kHz   | 7     |

|                      |                               | Setting 0.25x          | _   | 880  | _   | kHz   | 7     |

|                      |                               | Setting 0.5x (Default) | _   | 1.76 | _   | MHz   | 7     |

|                      |                               | Setting 1.0x           | _   | 3.5  | _   | MHz   | 7     |

|                      |                               | Setting 0.0625x        | _   | 440  | _   | kHz   | 7     |

|                      |                               | Setting 0.125x         | _   | 880  | _   | kHz   | 7     |

|                      | BW <sub>LOOP(5.94Gb/s)</sub>  | Setting 0.25x          | _   | 1.76 | _   | MHz   | 7     |

|                      |                               | Setting 0.5x (Default) | _   | 3.5  | _   | MHz   | 7     |

|                      |                               | Setting 1.0x           | _   | 7    | _   | MHz   | 7     |

|                      |                               | Setting 0.0625x        | _   | 880  | _   | kHz   | 7     |

|                      |                               | Setting 0.125x         | _   | 1.76 | _   | MHz   | 7     |

|                      | BW <sub>LOOP(11.88Gb/s)</sub> | Setting 0.25x          | _   | 3.5  | _   | MHz   | 7     |

|                      |                               | Setting 0.5x (Default) | _   | 7    | _   | MHz   | 7     |

|                      |                               | Setting 1.0x           | _   | 14   | _   | MHz   | 7     |

#### **Table Notes:**

- 1. Values achieved with Semtech evaluation board and connector.

- 2. Measured using a clean input source.

- 3. Default value for CFG\_EQ\_INPUT\_LAUNCH\_SWING\_COMP parameter in control register 0x18. The default parameter value is  $80_d$  ( $50_h$ ).

- 4. Default trace driver swing Setting.

- 5. Please see 4.3.3.1 for the further definition on Synchronous and Asynchronous Lock Time.

- 6. This specification applies to and DDO1/DDO1 and DDO0/DDO0.

- 7. Please see PLL\_LOOP\_BANDWIDTH\_0 for the full range of loop bandwidth settings.

- 8. Output Driver Setting of 8.

- 9. Output Driver Setting of 36.

- 10. Max jitter occurs at the maximum cable length.

- 11. Rise/fall time was measured between 80% and 20%.

- 12. The rise/fall time of signals at source should not be more than 62ns.

# 3. Input/Output Circuits

Figure 3-1: SDI, SDI\_TERM

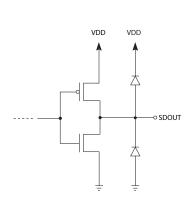

Figure 3-3: SDIN, SCLK

Figure 3-5: SDOUT

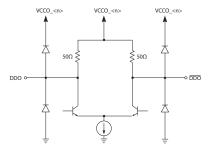

$\label{eq:Note:The} \textbf{Note:} The <n> in VCCO\_<n> refers to the ouput power supply number. VCCO\_1 is the power supply connection for DDO1/$\overline{DDO1}$, and VCCO\_0 is the power supply connection for DDO0/$\overline{DDO0}$.$

Figure 3-2: DDO1/DDO1, DDO0/DDO0

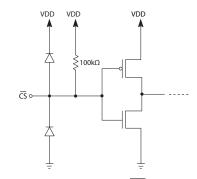

Figure 3-4: CS

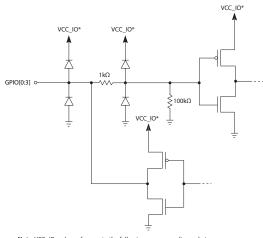

Note: VCC\_IO makes reference to the following power supplies and pins: VCC\_IO = VDD for GPIO[0:1] VCC\_IO = VCC\_CORE for GPIO[2:3]

Figure 3-6: GPIO[0:3]

# 4. Detailed Description

## **4.1 Device Description**

The GS12241 features a  $75\Omega$  internally terminated Cable Equalizer, which can equalize up to 80m of Belden1694A cable at 12G. The device includes a CDR which will lock to and retime valid SMPTE, MADI, and DVB-ASI signals to produce extremely low output jitter, even at extended cable lengths. The CDR has extensive loop bandwidth control to enable jitter transfer optimization. To facilitate system testing, the device also includes 3D eye monitor, PRBS7 checker and generator. The two trace drivers have independent amplitude and pre-emphasis control which can compensate for 14dB of insertion loss at 5.94GHz. The pre-emphasis control is two dimensional in both drivers, where both pre-emphasis pulse amplitude and width adjustments can be made to help optimize for interconnect mismatches such as vias and connectors.

### 4.1.1 Sleep Mode

To enable low power operation, the GS12241 has manual and automatic sleep mode control.

The default mode is automatic sleep mode on LOS (Loss Of Signal). The device can also be manually put into sleep mode. When the device is in sleep mode, all the core blocks are powered down, except the host interface and carrier detect circuits. The trace driver can be configured to be disabled or muted during sleep.

The CTRL\_AUTO\_SLEEP and CTRL\_MANUAL\_SLEEP parameters in register 0x3, control the sleep mode of the device. The default value of the CTRL\_AUTO\_SLEEP parameter is  $1_b$  (auto sleep). While in auto sleep mode, the CTRL\_MANUAL\_SLEEP parameter has no effect. To enable host control of the sleep mode, set the CTRL\_AUTO\_SLEEP parameter to  $0_b$  manual sleep control. To prevent the device from entering sleep, set the CTRL\_MANUAL\_SLEEP parameter to  $0_b$  (not sleep). To manually configure the device to sleep, set the CTRL\_MANUAL\_SLEEP parameter to  $0_b$  (sleep).

The device can also be manually made to sleep through the *GPIO* pins. The default GPIO pin to control sleep is *GPIO2* (pin 33). Drive this pin HIGH to make the device sleep.

Section 4.6 describes the PRBS generator function. If the device's PRBS generator is intended to be used without a valid input signal, the device should be manually set to not sleep as described above. Without a valid input signal, an LOS status will be generated and the device will enter sleep mode and the PRBS block will be disabled. For a description of LOS thresholds and settings, see Section 4.2.3.

## 4.2 Cable Equalizer

The GS12241 can automatically adjust its gain to equalize and restore SMPTE compliant signals received over different lengths of coaxial cable having loss characteristics similar to Belden 8281 or 1694A. With the default settings, the device will automatically equalize MADI at 125Mb/s and most common SMPTE compliant signal between SD at 270Mb/s and UHD-SDI at 11.88Gb/s and bypass signals below 125Mb/s.

The GS12241 features programmable Launch Swing Compensation, squelch threshold adjust, and bypass, all of which can be set through the device's host interface. The equalized or bypassed signal is then routed to the eye monitor and serial digital re-timer (CDR) block.

### 4.2.1 Cable Equalizer Bypass

With the default settings, the device will automatically bypass signals below 125Mb/s. During cable equalizer-bypass mode, the device supports low data rate and slow edge signals such as SMPTE310 and AES3id. The rise/fall times must not exceed 62ns. While in cable equalizer bypass mode, signal will not be re-timed by the CDR block.

To force the device to bypass the cable equalizer, DC restoration stage, and CDR, the following two methods can be used:

#### **Host Interface Control:**

Set the following parameters in register 17<sub>h</sub>:

- CTRL\_CEQ\_AUTO\_BYPASS = 0

- CTRL\_CEQ\_MANUAL\_BYPASS = 1

#### **GPIO Control:**

- Configure a GPIO as an input by writing 0<sub>h</sub> to the CFG\_GPIO<n>\_OUTPUT\_ENA.

- Configure the GPIO function as "cable equalizer bypass enable," by writing 84h to CFG GPIO<n> FUNCTION.

- 3. Drive the selected GPIO pin HIGH.

**Note**: The <n> in the control parameter names refers to the GPIO pin number.

## 4.2.2 Upstream Launch Swing Compensation

The GS12241 cable equalizer has an automatic gain control circuit, that is optimized on the assumption that the trace driver in the upstream device is SMPTE compliant and has a launch swing of  $800 \text{mV}_{pp} \pm 10\%$ . When the source amplitude is known to be non-SMPTE compliant, a compensation adjustment can be made in the GS12241. The GS12241 can adjust for launch swings in the range of 250mV to 1V in approximately  $50 \text{mV}_{ppd}$  increments. Upstream launch swing compensation can be adjusted through the **CFG\_EQ\_INPUT\_LAUNCH\_SWING\_COMP** parameter in control register 0x18. The default parameter value is  $80_{d}$  ( $50_{h}$ ), which corresponds to a nominal launch swing of  $800 \text{mV}_{ppd}$ .

## 4.2.3 Carrier Detect, Squelch Control, and Loss of Signal

The GS12241 cable equalizer has highly configurable carrier detection and squelching capability. The carrier detection can be made more robust against spurious signals and noise at the inputs and the squelch control can be configured and enabled to reduce false outputs to low level signals such as crosstalk.

The GS12241 reports two separate carrier detect parameters—**STAT\_PRI\_CD** and **STAT\_SEC\_CD**. They are described in Section 4.2.3.1 and Section 4.2.3.2 respectively.

**Note:** The parameters referred to within Section 4.2.3 to Section 4.2.3.2 are linked to their respective registers in Table 4-1.

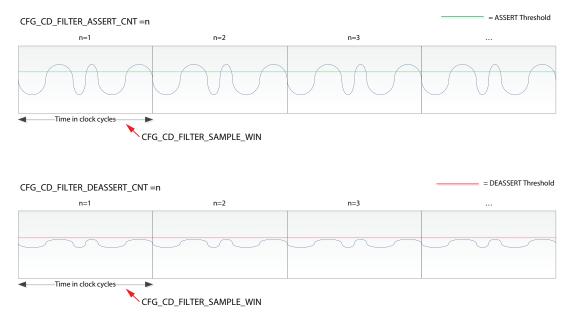

### 4.2.3.1 Primary Carrier Detection (STAT\_PRI\_CD) Configuration

Primary carrier detection (**STAT\_PRI\_CD**) can be configured for higher stability by filtering out longer transients or glitches. This can be achieved by increasing the sampling window over which the signal is sampled and the number of samples required to assert or de-assert it.

There are three configuration parameters that control assertion or de-assertion of **STAT PRI CD**:

- CFG\_CD\_FILTER\_SAMPLE\_WIN

- CFG\_FILTER\_DEASSERT\_CNT

- CFG CD FILTER ASSERT CNT

See Figure 4-1 for a visual representation of the **STAT\_PRI\_CD** configuration parameters.

With the default values in place:

- An assertion (setting HIGH) of STAT\_PRI\_CD will take place after a valid signal is present for ~6.5ms

- A de-assertion (setting LOW) of STAT\_PRI\_CD will take place after loss of a valid signal for ~96μs

If the application requires any adjustment of the sampling window, assertion count, or de-assertion count, please consult the following equations to calculate the associated time to assert or de-assert STAT\_PRI\_CD.

#### STAT\_PRI\_CD de-assert time:

(1.6µs) \* (CFG\_CD\_FILTER\_SAMPLE\_WIN + 1) \* CFG\_CD\_FILTER\_ DEASSERT\_CNT

#### **STAT\_PRI\_CD** assert time:

(1.6µs) \* (CFG\_CD\_FILTER\_SAMPLE\_WIN + 1) \* CFG\_CD\_FILTER\_ASSERT\_CNT

Figure 4-1: STAT\_PRI\_CD Configuration Parameters

### 4.2.3.2 Secondary Carrier Detection (STAT\_SEC\_CD) Configuration

The secondary carrier detection signal acts as an additional carrier detection which can be further filtered through squelch controls. It also serves as the control signal for Mute on LOS (Loss Of Signal) and Disable on LOS. Please refer to Section 4.7.6 to Section 4.7.6.2 for further information on this.

If the application requires the use of squelch settings, start by setting the following:

• CFG SEC CD INCL CLI SQUELCH = 1

Once this parameter is set, the device will apply squelch based off of the settings found within the following parameters:

- CFG\_CLI\_SQUELCH\_THRESHOLD

- CFG\_CLI\_SQUELCH\_HYSTERESIS

The device will use these parameters to determine squelch status and set that within **STAT CLI SQUELCH**. Based off of this, secondary carrier detection can be described as:

STAT\_SEC\_CD = inverse of (STAT\_CLI\_SQUELCH & STAT\_PRI\_CD).

To help detail how the device determines the state of Squelch, we define the following variables:

- CLI = STAT\_CABLE\_LEN\_INDICATION

- THR = CFG\_CLI\_SQUELCH\_THRESHOLD

- HYS = CFG CLI SQUELCH HYSTERESIS

- SQL = STAT\_CLI\_SQUELCH

The following rules define the state of SQL. **Note:** If the cable equalizer is in bypass (**STAT\_CEQ\_BYPASS** = 1), the device will set SQL to 0.

• If CLI > (THR + HYS), the device will set SQL to 1, otherwise:

- If CLI < (THR HYS), the device will set SQL to 0, otherwise:

- If CLI ≥ (THR HYS) and CLI ≤ (THR + HYS), SQL remains unchanged

- If SQL = 1, the device will not indicate lock and the trace driver state will be defined by output state control parameters settings, see Section 4.7.6 for more details

**Table 4-1: Cable Equalizer Status and Configuration Parameters**

| Register Address <sub>h</sub> and Name | Parameter Name              | Parameter Description                                                                       |

|----------------------------------------|-----------------------------|---------------------------------------------------------------------------------------------|

| 15,<br>CARR_ DET_CFG                   | CFG_SEC_CD_INCL_CLI_SQUELCH | Enables or disables squelch control.                                                        |

| 16,                                    | CFG_CLI_SQUELCH_THRESHOLD   | Used to tune the squelch threshold based on the tolerance requirements of the application.  |

| SQUELCH_ PARAMETERS                    | CFG_CLI_SQUELCH_HYSTERESIS  | Used to tune the squelch hysteresis based on the tolerance requirements of the application. |

| 20,<br>CD_FILTER_ DELAYS_0             | CFG_CD_FILTER_SAMPLE_WIN    | Primary carrier detect sampling window size.                                                |

| 21,<br>CD_FILTER_ DELAYS_1             | CFG_CD_FILTER_DEASSERT_CNT  | Primary carrier detect de-assertion count.                                                  |

| 22,<br>CD_FILTER_ DELAYS_2             | CFG_CD_FILTER_ASSERT_CNT    | Primary carrier detect assertion count.                                                     |

| 84,                                    | STAT_CNT_PRI_CD_CHANGES     | A counter showing the number of times the primary Carrier Detect signal changed.            |

| STICKY_COUNTS_0                        | STAT_CNT_SEC_CD_CHANGES     | A counter showing the number of times the secondary Carrier Detect signal changed.          |

| 86,<br>CURRENT_ STATUS_0               | STAT_CLI_SQUELCH            | Cable equalizer Squelch status.                                                             |

| 87,                                    | STAT_PRI_CD                 | Primary filtered carrier detect of the analog carrier detect signal.                        |

| CURRENT_STATUS_1                       | STAT_SEC_CD                 | Secondary filtered carrier detect of the analog carrier detect signal.                      |

| 88,<br>EQ_GAIN_IND                     | STAT_CABLE_LEN_INDICATION   | SDI cable length indicator.                                                                 |

## 4.3 Serial Digital Re-timer (CDR)

The GS12241 includes an integrated CDR, whose purpose is to lock to a valid incoming signal from the cable equalizer stage and produce a lower jitter signal at the cable or trace driver outputs. The CDR will attempt to lock to any of the following data rates: MADI (125Mb/s), SD-SDI (270Mb/s), HD-SDI (1.485Gb/s), 3G-SDI (2.97Gb/s), 6G-SDI (5.94Gb/s) and 12G-SDI (11.88Gb/s). This includes the f/1.001 rates. The default settings of the re-timer block are optimal for most applications. However, the following controls allow the user to customize the behaviour of the re-timer: loop bandwidth control, Automatic and Manual Rate Detection. Please see Section 4.3.1 to Section 4.3.2 for a description of these functionalities.

**Note:** The parameters referred to within Section 4.3.1 to Section 4.3.2 are linked to their respective registers in Table 4-3. For a complete list of registers and functions, please see Section 5.

## 4.3.1 PLL Loop Bandwidth Control

The ratio of output peak-to-peak jitter to input peak-to-peak jitter of the CDR can be represented by a low-pass jitter transfer function, with a bandwidth equal to the PLL loop bandwidth. Although the default loop bandwidth settings for the GS12241 CDR are ideal for most SDI signals, the GS12241 allows the user to adjust the loop bandwidth for each supported rate.

Registers 0x0A through 0x0C contain the following parameters which allow the user to configure rate dependent loop bandwidth: CFG\_PLL\_LBW\_12G, CFG\_PLL\_LBW\_6G, CFG\_PLL\_LBW\_3G, CFG\_PLL\_LBW\_HD, CFG\_PLL\_LBW\_SD, and CFG\_PLL\_LBW\_MADI. The loop bandwidth settings are defined in terms of ratios of the nominal loop bandwidth. For each rate, where '1.0x' is the nominal loop bandwidth, the following ratios are available: 0.0625x, 0.125x, 0.25x, 0.5x, and 1.0x. Table 2-3 provides the specific loop bandwidths for each data rate and loop bandwidth setting. Lowering the loop bandwidth will lower the jitter amplitude above the loop bandwidth frequency. Although lower output jitter is desirable, the lower loop bandwidth may reduce the device's IJT to very high jitter that may be present outside the loop bandwidth.

### 4.3.2 Automatic and Manual Rate Detection

With the default rate detect setting, the CDR will automatically attempt to lock to any of following data rates: MADI (125Mb/s), SD-SDI (270Mb/s), HD-SDI (1.485Gb/s), 3G-SDI (2.97Gb/s), 6G-SDI (5.94Gb/s) and 12G-SDI (11.88Gb/s). This includes the f/1.001 rates. However, the CDR can be configured to only lock to a single rate, by setting the CFG\_AUTO\_RATE\_DETECT\_ENA and CFG\_MANUAL\_RATE parameters in register 0x06.

The **STAT\_LOCK** parameter in register 0x86 will indicate that the CDR is locked when its value is  $1_b$  and unlocked when its value is  $0_b$ . The lock status can also be monitored externally on any *GPIO* pin, however it is the default mode for *GPIO1*, pin 18. The **STAT\_DETECTED\_RATE** parameter in register 0x87 will indicate the data rate at which the CDR is locked to. A value of  $0_d$  in the **STAT\_DETECTED\_RATE** parameter indicates that the device is not locked, while values between  $1_d$  and  $6_d$  will indicate that the device is locked to one of the six available rates between MADI at 125Mb/s and UHD-SDI at 11.88Gb/s.

**Table 4-2: Detected Data Rates**

| STAT_DETECTED_<br>RATE [2:0] | Detected Data Rate |

|------------------------------|--------------------|

| 0                            | Unlocked           |

| 1                            | MADI (125Mb/s)     |

| 2                            | SD (270Mb/s)       |

| 3                            | HD (1.485Gb/s)     |

| 4                            | 3G (2.97Gb/s)      |

| 5                            | 6G (5.94Gb/s)      |

| 6                            | 12G (11.88Gb/s)    |

| 7                            | Reserved           |

If the CDR cannot lock to any of the valid rates in automatic mode or the selected rate in manual mode, the signal can automatically be bypassed to the output. If the CDR does lock to the incoming signal, the re-timed and bypassed (if manual bypass control enabled) signals are available at the appropriate output. See the Section 4.7 for more details.

### 4.3.3 Lock Time

### 4.3.3.1 Synchronous and Asynchronous Lock Time

Synchronous lock time is defined as the time it takes the device to re-lock to an existing signal that has been momentarily interrupted or to a new signal of the same data rate as the previous signal which has been quickly switched in.

Asynchronous lock time is defined as the time it takes the device to lock when a signal is first applied to the serial digital inputs, or when the signal rate changes. The asynchronous and synchronous lock times are defined in Table 2-3.

**Note:** To ensure synchronous lock times are met, the maximum interruption time of the signal is  $10\mu$ s for an SD-SDI signal. HD, 3G, 6G, or 12G signals must have a maximum interruption time of  $6\mu$ s. The new signal, after interruption, must have the same frequency as the original signal but may have an arbitrary phase.

**Table 4-3: CDR Control and Status Parameters**

| Register Address <sub>h</sub><br>and Name | Parameter Name            | Description                                                                                   |

|-------------------------------------------|---------------------------|-----------------------------------------------------------------------------------------------|

| 06,<br>RATE_ DETECT_ MODE                 | CFG_AUTO_RATE_DETECT_ENA  | Enables or disables the automatic rate detection mode of the CDR.                             |

|                                           | CFG_MANUAL_RATE           | Select a single rate for CDR rate detection when CFG_AUTO_RATE_DETECT_ENA is 0 <sub>b</sub> . |

| 0A,                                       | CFG_PLL_LBW_12G           | Configures the Loop Bandwidth for 12G signals.                                                |

| PLL_LOOP_<br>BANDWIDTH_ 0                 | CFG_PLL_LBW_6G            | Configures the Loop Bandwidth for 6G signals.                                                 |

| 0B,<br>PLL_LOOP_<br>BANDWIDTH_ 1          | CFG_PLL_LBW_3G            | Configures the Loop Bandwidth for 3G signals.                                                 |

|                                           | CFG_PLL_LBW_HD            | Configures the Loop Bandwidth for HD signals.                                                 |

| OC,<br>PLL_LOOP_<br>BANDWIDTH_ 2          | CFG_PLL_LBW_SD            | Configures the Loop Bandwidth for SD signals.                                                 |

|                                           | CFG_PLL_LBW_MADI          | Configures the Loop Bandwidth for MADI signals.                                               |

| 11,<br>GPIO1_CFG                          | CFG_GPIO1_FUNCTION        | Sets the function of GPIO1.                                                                   |

|                                           | CFG_GPIO1_OUTPUT_ENA      | Sets the GPIO pin as either an output or an input.                                            |

| 85,<br>STICKY_COUNTS_1                    | STAT_CNT_PLL_LOCK_CHANGES | Counter showing the number of times the PLL lock status changed.                              |

|                                           | STAT_CNT_RATE_CHANGES     | Counter showing the number of times the PLL lock rate changed.                                |

| 86,<br>CURRENT_ STATUS_0                  | STAT_LOCK                 | The status of the PLL. Locked, or unlocked.                                                   |

| 87,<br>CURRENT_STATUS_1                   | STAT_DETECTED_RATE        | The rate at which the PLL is locked to.                                                       |

## 4.4 PRBS Checker

The GS12241 includes an integrated PRBS checker, which can error check a PRBS7 signal out of the cable equalizer input block.

There are two modes of operation for the PRBS checker:

- Timed Mode: Used for precise measurements of up to ~3.334s.

- In timed mode, the host sets the measurement time and executes the checker operation. The device ends the PRBS error check measurement when the timer expires, and the host reads back the measurement status and error count.

- Continuous Mode: Can be used for longer measurements but with less precision in the time interval.

- In continuous mode, the host controls the starts and stops of the PRBS error checking operation then reads back the measurement status and error count.

**Note:** When working with the PRBS Checker, please note the following:

- The parameters referred to in this Section 4.4.1 to Section 4.4.2 are briefly described and linked to their respective registers in Table 4-4. For a complete list of registers and functions, please see Section 5.

- The PRBS generator and checker can be active at the same time, however, the generator can not be looped back on itself for error checking.

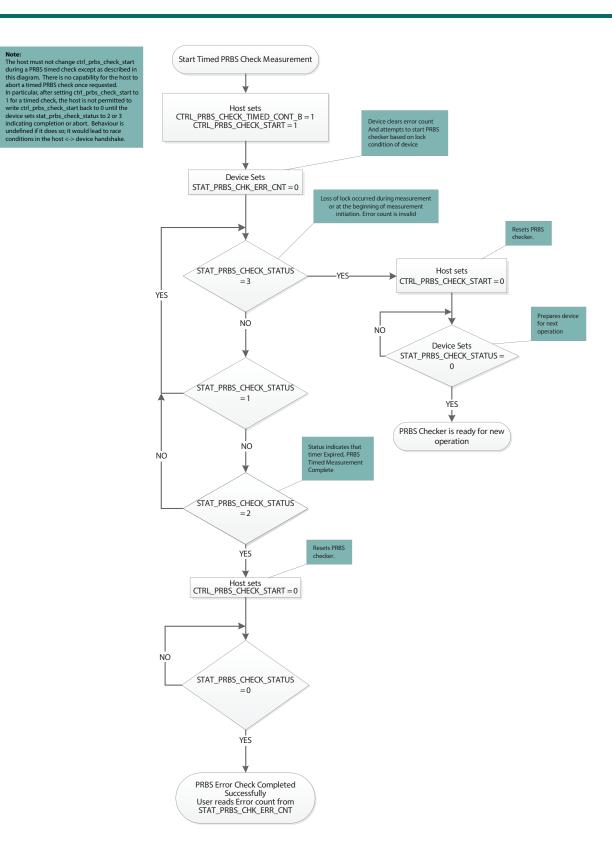

#### 4.4.1 Timed PRBS Check Measurement Procedure

For applications where measurement times are ~3.34s or less, the timed PRBS check mode is the most suitable. Alternatively, to achieve precise timing for lower BER signals, the timed PRBS check measurement can be repeated by the host and the total measurement time and error count is determined by summing the individual measurements.

In timed mode, the host sets the total measurement time by setting the CFG\_PRBS\_CHECK\_PREDIVIDER and the CFG\_PRBS\_CHECK\_MEAS\_TIME parameters to the required values to achieve the total measurement time required by the application.

To perform a timed PRBS measurement, please complete the following steps:

Set the appropriate settings within CFG\_PRBS\_CHECK\_PREDIVIDER and CFG\_PRBS\_CHECK\_MEAS\_TIME to achieve the total measurement time required by the application. The TMT (Total Measurement Time) is determined by the following equation:

TMT = CFG\_PRBS\_CHECK\_PREDIVIDER \* (CFG\_PRBS\_CHECK\_MEAS\_TIME \*256+1) \* (1/40MHz)

**Note:** Using the default **CFG\_PRBS\_CHECK\_PREDIVIDER** setting of 0 (pre-divider = 4) and **CFG\_PRBS\_CHECK\_MEAS\_TIME** setting of 3 (MEAS\_TIME = 3), the TMT (total measurement time) is  $\sim$ 77 $\mu$ s per measurement.

2. Follow the steps outlined in Figure 4-2: Timed PRBS Check Flow.

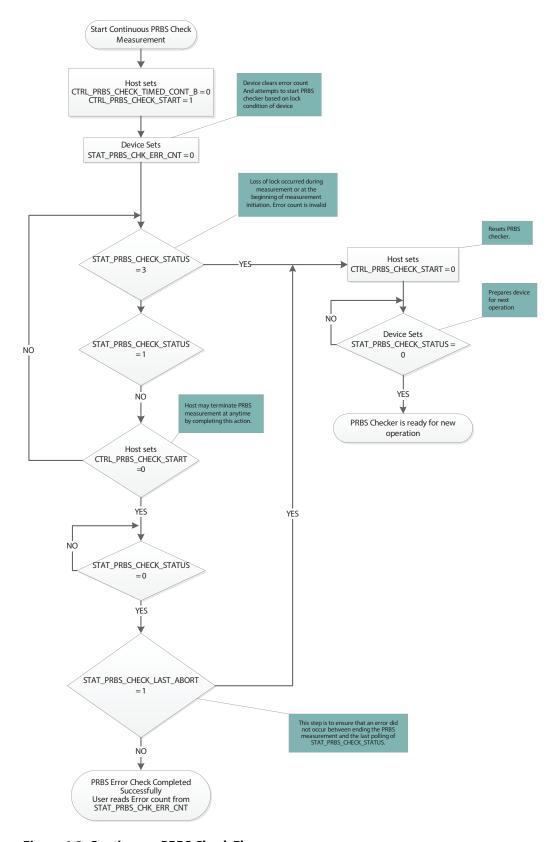

## 4.4.2 Continuous PRBS Check Measurement Procedure

As previously mentioned, the maximum measurement time for a timed PRBS error measurement is  $\sim$ 3.35 seconds. For links with very low error rates, this time is insufficient to capture an adequate number of errors. For these situations, the continuous PRBS check measurement is more appropriate.

In continuous PRBS measurement mode, the measurement can run as long as required (assuming the device remains locked) to ensure the BER test level is met.

To perform a continuous PRBS measurement, please follow the steps outlined in the flowchart found within Figure 4-3: Continuous PRBS Check Flow.

**Table 4-4: PRBS Checker Parameter Description**

| Register Address <sub>h</sub><br>and Name | Parameter Name               | Description                                                     |

|-------------------------------------------|------------------------------|-----------------------------------------------------------------|

| 50,<br>PRBS_ CHK_CFG                      | CFG_PRBS_CHECK_PREDIVIDER    | Selects pre-divider for PRBS check measurement timer.           |

|                                           | CFG_PRBS_CHECK_MEAS_TIME     | Selects PRBS check measurement interval for timed measurements. |

| 51,<br>PRBS_CHK_ CTRL                     | CTRL_PRBS_CHECK_TIMED_CONT_B | Selects between timed and continuous type PRBS measurement.     |

|                                           | TRL_PRBS_CHECK_START         | Used to start and stop PRBS measurements.                       |

| 89,<br>PRBS_ CHK_ERR_CNT                  | STAT_PRBS_CHK_ERR_CNT        | PRBS error count storage location.                              |

| <b>8A,</b><br>PRBS_ CHK_STATUS            | STAT_PRBS_CHECK_STATUS       | Status indication of PRBS checker.                              |

|                                           | STAT_PRBS_CHECK_LAST_ABORT   | Indication bit for PRBS successful completion or abort.         |

Figure 4-2: Timed PRBS Check Flow

Figure 4-3: Continuous PRBS Check Flow

## **4.5 EYE Monitor**

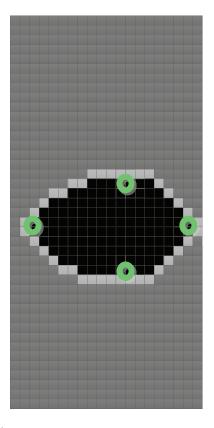

The GS12241 includes an integrated eye monitor, which can scan the equalized signal from the cable equalizer block. The eye monitor is capable of performing a full 128h x 256v matrix-scan or simply a 4 coordinate shape-scan of the equalized signal (See Figure 4-4).

**Note:** If the eye monitor will be used during normal operation of the device (cable equalizer mission mode), the user must ensure that the Device Power-up Sequence in Section 4.9.12 is completed to prevent temporary signal disturbance when enabling the eye monitor.

Figure 4-4: Full Matrix Scan (left) and 4-Point Shape Scan (right)

The eye monitor is highly configurable, and the host can configure the offset, resolution, sample time, and error threshold parameters to control the depth and execution time of the scan. The EYE Monitor scans the signal from the cable equalizer block. Similar to the PRBS Checker, the eye monitor is controlled through a 4-way handshake mechanism. The following sections outline the scan parameters and procedure to configure the eye scan area, error threshold, and run a shape or full scan.

## 4.5.1 Shape Scan and Measurement Time

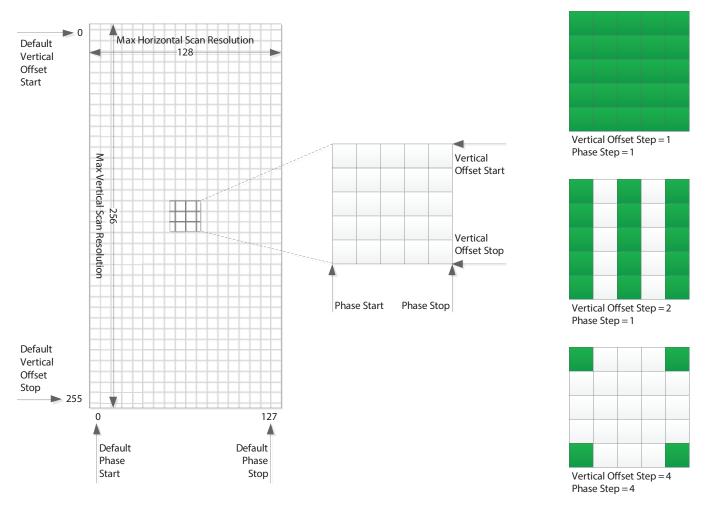

Figure 4-5: Eye Scan Matrix Parameters

Figure 4-5 shows a visual representation of the scan matrix and indicates the spatial parameters that determine the scan area and resolution. Running a scan using the default offset and step parameters, results in 32768 (128x256) samples. The number of samples and thus, the total scan time can be reduced to meet the needs of the application. The scan area can be reduced by reducing the span determined by the vertical and phase start and stop offsets, or the resolution can be reduced by increasing the step size between adjacent samples. On the right in Figure 4-5, there are three step settings used as examples, however there are a total of nine combinations possible. See Table 4-6 for the register addresses and parameter names of the spatial eye scan parameters.

For example, by increasing the vertical and phase step size to 4, the resolution is reduced to  $(1/4)^2$ , thus reducing the number of samples down to 2048 (32768x1/16).

The vertical and horizontal scan information is useful when adjusting pre-emphasis and equalization of a link. However, once this is accomplished, it may be sufficient to use the eye scanner to only monitor jitter by setting the offsets to simply slice the eye at the centre offset position, thus obtaining a simple 128 sample horizontal scan. A horizontal eye can be configured to run in just over a millisecond.

In addition to the spatial parameters, the sample time, and thus the bit error rate resolution for the eye scan can be adjusted; longer scans can detect finer bit error rates. However, this proportionally increases the total scan time. The sample time in microseconds is determined by a 32-bit time-out value split across two 16 bit registers. See Table 4-6 for the register addresses and parameter names of the time-out eye scan parameters.

For example, using the default spatial and temporal measurement scan parameters, the scan time is approximately 6.6 seconds (32768 x 2 x 100 $\mu$ s). However, by changing the vertical and horizontal step size to 4, the scan time can be reduced to 400ms (2048x2x100 $\mu$ s).

The error count information can be used as is to determine the minimum inner contour based on the measurement time. However, the basic data can be post processed to determine things like error rate, and error threshold.

The following equations provide guidance for user post-processing:

Equation 4-1

```

error rate = \frac{sample \ error \ count}{sample \ time}

```

Contour maps can be created by defining error rate thresholds, and grouping sampled points that fall between thresholds.

For example:

Equation 4-2

```

\frac{\textit{sample time}}{\textit{error rate threshold}} < \textit{sample error threshold} < \frac{\textit{sample time}}{\textit{error rate threshold}} \ge \frac{1}{2}

```

Some sampling scopes provide eye maps with BER contours; similar limited BER contour approximations can be obtained from the eye scan by using BER threshold groups.

For example:

Equation 4-3

```

\frac{\textbf{sample time x data rate}}{\textbf{error rate threshold}} < \textbf{sample error threshold} < \frac{\textbf{sample time x data rate}}{\textbf{error rate threshold}} < \frac{\textbf{sample time x data rate}}{\textbf{error rate threshold}}

```

**Table 4-5: Spatial Scan Configuration Parameters**

| Register Address <sub>h</sub> and Name | Parameter Name             | Description                  |

|----------------------------------------|----------------------------|------------------------------|

| <b>5A</b> , EYE_MON_ SCAN_CTRL_0       | CTRL_EYE_PHASE_START       | Horizontal phase start index |

|                                        | CTRL_EYE_PHASE_STOP        | Horizontal phase stop index  |

| 5B, EYE_MON_ SCAN_CTRL_1               | CTRL_EYE_PHASE_STEP        | Horizontal phase step size   |

|                                        | CTRL_EYE_VERT_OFFSET_START | Vertical offset start index  |

| 5C, EYE_MON_ SCAN_CTRL_2               | CTRL_EYE_VERT_OFFSET_STOP  | Vertical offset stop index   |

|                                        | CTRL_EYE_VERT_OFFSET_STEP  | Vertical offset step size    |

The next section describes the implementation of the matrix-scan and shape-scan.

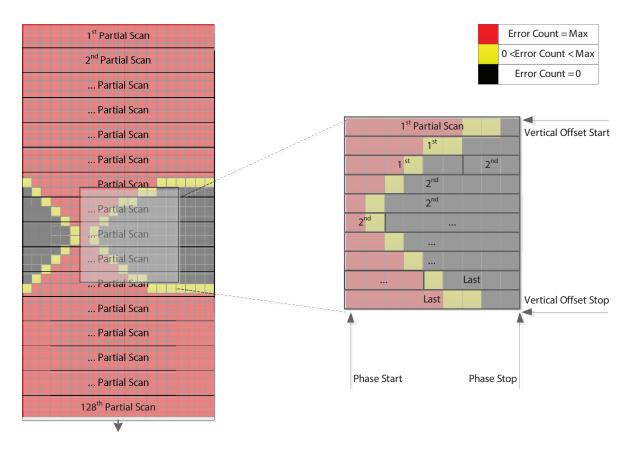

### 4.5.2 Matrix-Scan and Shape-Scan Operation

The previous section described the parameters used to adjust the spatial and temporal eye scan settings. Each sample of the eye scan can record up to 65536 errors. A full eye scan would require 64KB (256 x 128 x 2 Bytes) of memory to store the data of a full scan. The eye monitor was implemented to use device resources more efficiently by segmenting a full scan into several partial scan segments. Each partial scans segment can contain up to 512B of scan data.

In the case of a full matrix-scan, there are 128 partial scan segments and each partial scan segment contains two complete scan lines ( $2 \times 128 \times 2B = 512B$ ). In the case of a partial matrix-scan, each scan segment contains multiple partial scan lines including partial lines (see Figure 4-6).

Figure 4-6: Full Matrix Scan (left) and Partial Matrix Scan (right)

Figure 4-6 illustrates an example of an eye scan, where the sampled eye data is not centred within the scan matrix. The eye scan data has an arbitrary centre phase relative to the centre of the matrix which is determined when the eye monitor is powered up. While the eye monitor remains powered, subsequent scans will maintain the same relative phase allowing for consecutive scans to be compared for changes.

Although the scan data is not centred, a simple algorithm can be applied to the data to shift the eye data and extract the relevant information.

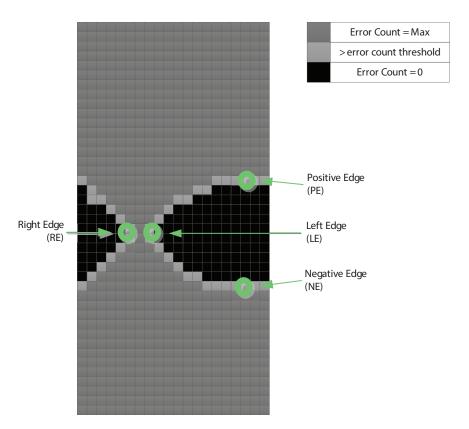

In addition to the matrix-scan, the eye monitor includes a built-in function called a shape-scan. The shape-scan returns four coordinates corresponding to the horizontal and vertical extremes of the inner eye (Figure 4-7).

Figure 4-7: 4-Point Scan Coordinates Relative to the Eye

The four points obtained from the shape-scan can be used to quickly and easily calculate the eye height and width of the signal eye. The shape-scan alone will most likely meet the signal analysis requirements of most applications. Alternatively, the coordinates obtained from the shape-scan can be used to optimize the bounds of a partial matrix-scan. The four points returned from the shape-scan are determined by the error rate threshold set by the error threshold parameter and the time-out parameters previously discussed.

**Table 4-6: Time-out Eye Scan Parameters**

| Register Address <sub>h</sub> and Name | Parameter Name         | Description                               |

|----------------------------------------|------------------------|-------------------------------------------|

| 56, EYE_MON_INT_CFG_2                  | CFG_EYE_BER_THRESHOLD  | Number of sample errors to determine fail |

| 54, EYE_MON_INT_CFG_0                  | CFG_EYE_MON_TIMEOUT_MS | MSB of measurement time in microseconds   |

| 55, EYE_MON_INT_CFG_1                  | CFG_EYE_MON_TIMEOUT_LS | LSB of measurement time in microseconds   |

This section provides a step-by-step procedure to run a matrix and shape-scan. The shape-scan procedure is described first.

#### **Shape-Scan Procedure:**

- 1. Ensure the offset and step parameters described in Table 4-5 are set to their default values

- 2. Configure the 4-point error rate threshold by setting each of the parameters listed in Table 4-6.

- 3. Configure the eye monitor to run a shape-scan by setting CTRL EYE SHAPE SCAN B to 1.

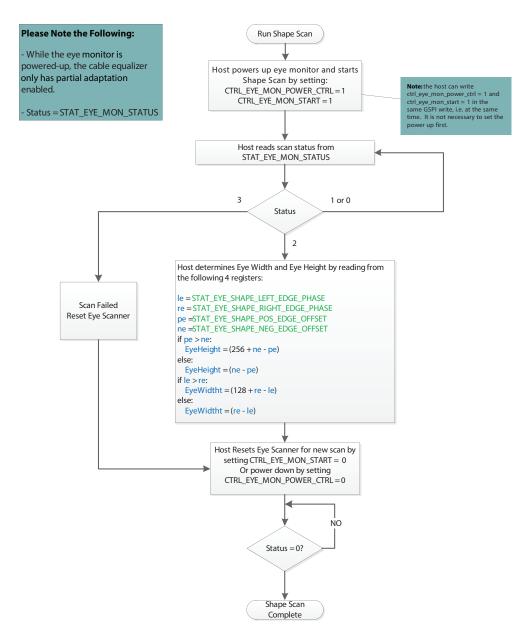

Start the scan and poll the scanner status register until the scan is complete. Please refer to the flow diagram in Figure 4-8.

Figure 4-8: Shape-Scan Flow Diagram

#### **Matrix-Scan Procedure:**

- 1. Set the bounds of the matrix-scan with the offset and step parameters described in Table 4-5. The default value results in a full matrix-scan. Alternatively, the shape-scan can be executed and the coordinates returned can be used to minimize the scan time and data size of the scan.

- 2. Configure the 4-point error rate threshold by setting each of the parameters listed in Table 4-6.

- 3. Configure the eye monitor to run a matrix-scan by setting CTRL EYE SHAPE SCAN B to 0.

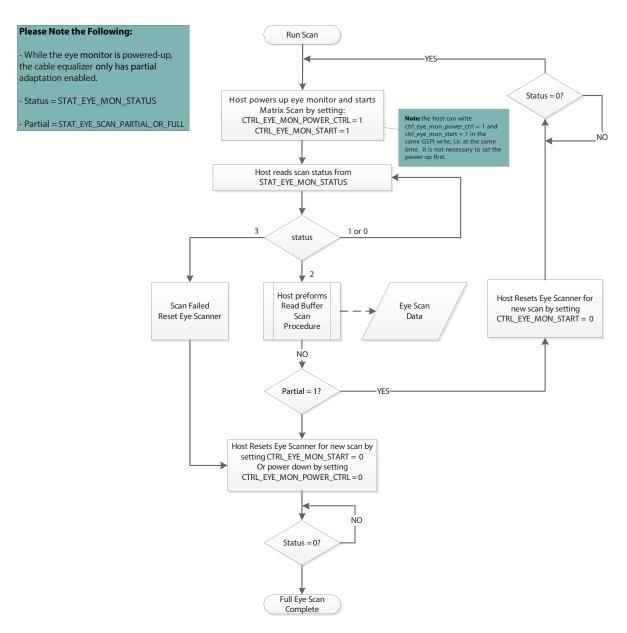

- 4. Start the scan and poll the scanner status register until the scan is complete. Please refer to the flow diagram in Figure 4-9.

#### **Read Eye Scan Buffer Procedure:**

- Host reads image size from STAT\_EYE\_IMAGE\_SIZE.

Note: The matrix-scan is composed of multiple partial scan segments. The size (in Bytes) of the last partial scan segment is stored in STAT\_EYE\_IMAGE\_SIZE.

- 2. Host reads scan buffer data from register 0x6CC1 to (0x6CC1 + (size read from **STAT\_EYE\_IMAGE\_SIZE**)/2).

- Address 0x6CC1 is the first header word corresponding to the last vertical offset position in the matrix that was read

- Address 0x6CC2 is the second header word corresponding to the image size.

This value is a copy of the image size that was read from

STAT\_EYE\_IMAGE\_SIZE.

- Address 0x6CC3 to (0x6CC1 + (size read from **STAT\_EYE\_IMAGE\_SIZE**)/2) is the eye scan data.

- The image data is 2 bytes per sample point

- Making reference to the Matrix shown in Figure 4-5, the eye scan data starting at 0x6CC3 is stored in order from left to right, top to bottom, from the last stored vertical/horizontal position in the matrix

The number of samples contained in the scan buffer is equal to (size read from **STAT\_EYE\_IMAGE\_SIZE** - 4)/2.

Figure 4-9: Matrix-Scan Flow Diagram

## 4.6 PRBS Generator

The GS12241 includes an integrated PRBS generator which can produce a differential PRBS7 or a divided clock signal on either output for system testing.

**Note:** When working with the PRBS Generator, please note the following.

- The PRBS generator and checker can be active at the same time, however, the generator can not be looped back on itself for error checking.

- If the application requires adjustments to the default output swing, please see Section 4.7.4.

- The parameters referred to within this section are linked to their respective registers in Table 4-7. For a complete list of registers and functions, please see Section 5.

- 1. Select the PRBS generator as the source on the appropriate output:

- To switch DDO0/DDO0 from data mode to PRBS generator mode, set

CTRL OUTPUTO SIGNAL SEL = 1

- To switch DDO1/DDO1 from data mode to PRBS generator mode, set

CTRL\_OUTPUT1\_SIGNAL\_SEL = 1

- 2. The default device settings are configured to power down the device on loss of input signal. If the PRBS generator is to be used without a valid input signal, then the following automatic setting parameters must be disabled. This must be done to ensure device is powered up and the outputs are active for the PRBS generator.

The following settings are required for PRBS generator on either output:

- CTRL AUTO SLEEP = 0

- CTRL MANUAL SLEEP = 0

The following settings are required when DDO1/DDO1 is selected as PRBS output:

- CTRL\_OUTPUT1\_AUTO\_MUTE = 0

- CTRL\_OUTPUT1\_MANUAL\_MUTE = 0

- CTRL\_OUTPUT1\_AUTO\_DISABLE = 0

- CTRL OUTPUT1 MANUAL DISABLE = 0

The following settings are required when DDO0/DDO0 is selected as PRBS output:

- CTRL OUTPUTO AUTO MUTE = 0

- CTRL\_OUTPUT0\_MANUAL\_MUTE = 0

- CTRL\_OUTPUTO\_AUTO\_DISABLE = 0

- CTRL\_OUTPUTO\_MANUAL\_DISABLE = 0

- 3. Set the values within the following parameters which meet the needs of the application:

- CTRL\_PRBS\_GEN\_SIGNAL\_SELECT

- CTRL PRBS GEN CLK SRC

- CTRL PRBS GEN DATA RATE

- Note: If CTRL\_PRBS\_GEN\_CLK\_SRC was set to CDR recovered clock a valid signal that the CDR has locked to must be present for proper operation, and the PRBS generator will match this data rate regardless of what rate CTRL\_PRBS\_GEN\_DATA\_RATE is set to.

- CTRL\_PRBS\_GEN\_CLK\_DIVIDER

- CTRL\_PRBS\_GEN\_INVERT

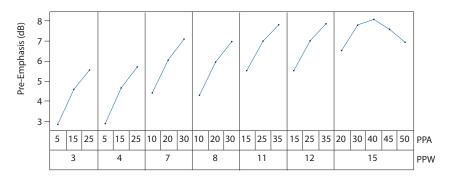

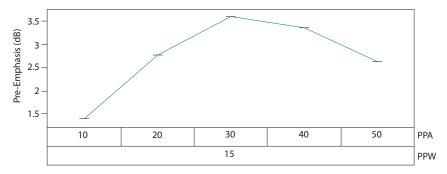

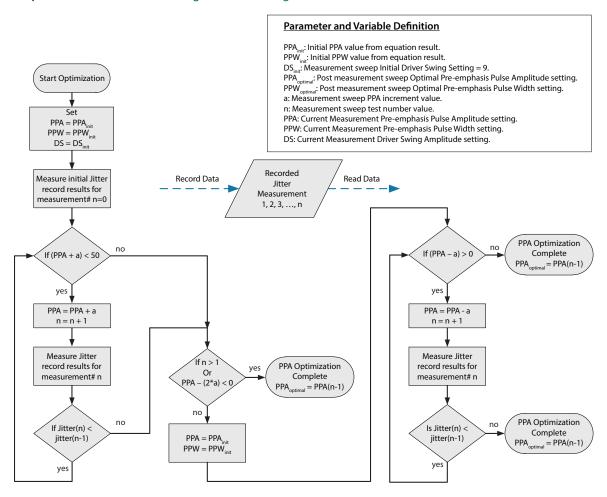

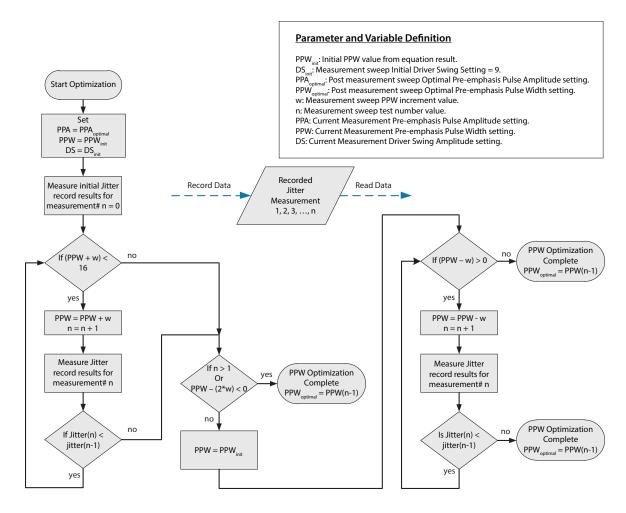

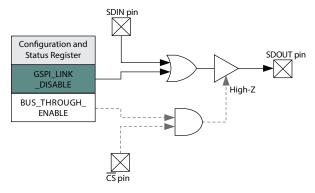

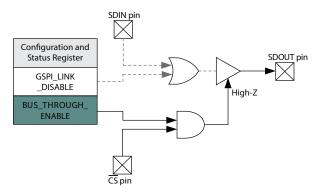

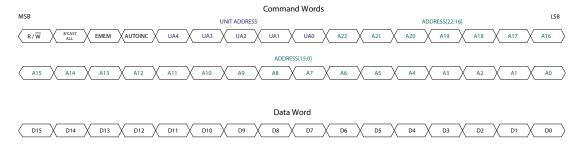

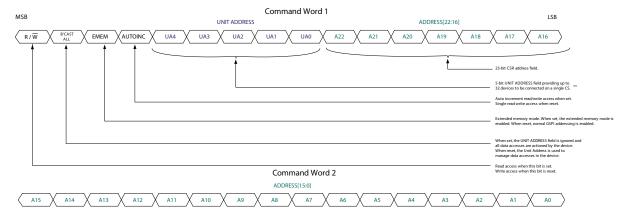

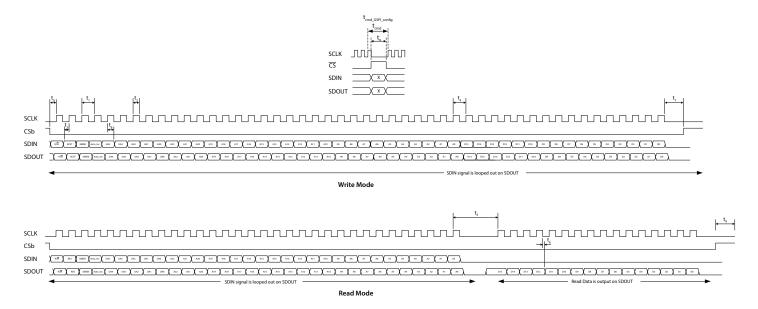

- 4. Start the generator by setting **CTRL\_PRBS\_GEN\_ENABLE** = 1.