# High Power IMS Evaluation Platform

Technical Manual

Visit <u>www.gansystems.com</u> for the latest version of this technical manual.

GSP65RXXHB-EVB UG rev. 210914

# DANGER DO NOT TOUCH THE BOARD WHEN IT IS ENERGIZED AND ALLOW ALL COMPONENTS TO DISCHARGE COMPLETELY PRIOR HANDLING THE BOARD. HIGH VOLTAGE CAN BE EXPOSED ON THE BOARD WHEN IT IS CONNECTED TO POWER SOURCE. EVEN BRIEF CONTACT DURING **OPERATION MAY RESULT IN SEVERSE INJURY OR DEATH.** Please sure that appropriate safety procedures are followed. This evaluation kit is designed for engineering evaluation in a controlled lab environment and should be handled by qualified personnel ONLY. Never leave the board operating unattended. WARNING Some components can be hot during and after operation. There are NO built-in electrical or thermal protection on this evaluation kit. The operating voltage, current and component temperature should be monitored closely during operation to prevent device damage. CAUTION This product contains parts that are susceptible to damage by electrostatic discharge (ESD). Always follow ESD prevention procedures when handling the product.

# Contents

| 1 | Over  | view                                                                   | 6  |

|---|-------|------------------------------------------------------------------------|----|

|   | 1.1   | Introduction                                                           | 6  |

|   | 1.2   | IMS Evaluation Module - Technical Description                          | 7  |

|   | 1.3   | IMS-based Power Stage Design                                           | 8  |

|   | 1.3.1 | IMS Board thermal design                                               | 8  |

|   | 1.3.2 | Control and power I/O                                                  | 10 |

|   | 1.3.3 | IMS Board Design                                                       | 11 |

|   | 1.3.4 | Gate driver board                                                      | 13 |

|   | 1.3.5 | Evaluation module assembly                                             | 15 |

| 2 | Usin  | g the IMS evaluation module with the mother board GSP65MB-EVB          | 17 |

|   | 2.1   | VDC Input Fusing                                                       | 18 |

|   | 2.2   | Optional Over Current / Current Sense Protection Circuit               | 18 |

|   | 2.3   | 12V input                                                              | 19 |

|   | 2.4   | PWM control circuit                                                    | 19 |

|   | 2.5   | Installation of IMS evaluation module                                  | 21 |

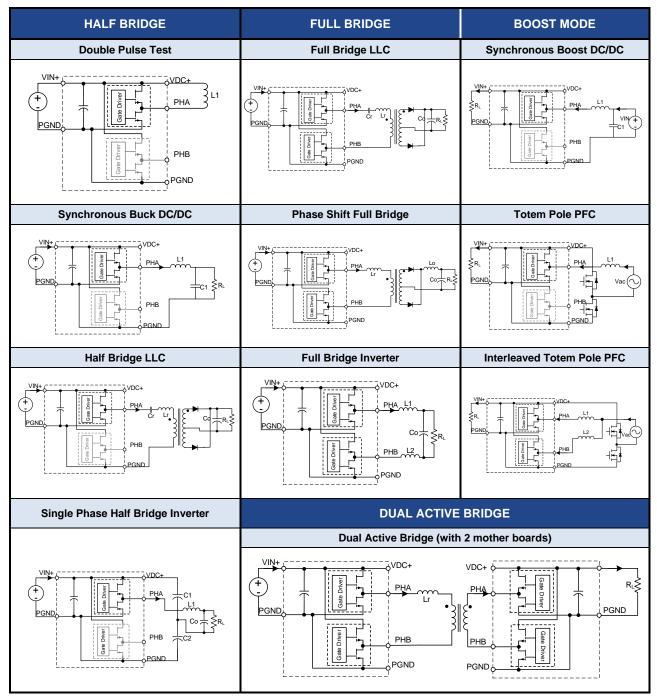

|   | 2.6   | Operation modes                                                        | 22 |

| 3 | Test  | Results                                                                | 24 |

|   | 3.1   | Double pulse test (GSP65R13HB-EVB, 650V/13mΩ)                          | 24 |

|   | 3.2   | Open-loop Synchronous Buck DC/DC operation (GSP65R25HB-EVB, 650V/25mΩ) | 24 |

| 4 | App   | endix                                                                  | 26 |

|   | 4.1   | IMS Power Board                                                        | 26 |

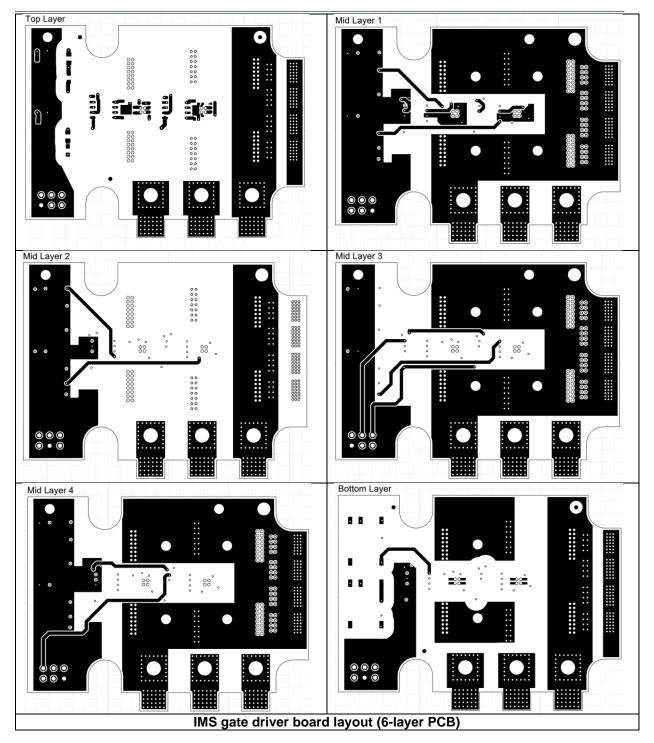

|   | 4.2   | IMS Gate driver board                                                  | 28 |

|   | 4.3   | Full bridge Mother Board GSP65MB-EVB)                                  | 33 |

# List of Figures

| Figure 1 GS66516B GaNPx SMD Package                                                                     | .7 |

|---------------------------------------------------------------------------------------------------------|----|

| Figure 2 Cross-section view of a single layer IMS board                                                 | .8 |

| Figure 3 Comparison of Junction to Heatsink thermal resistance (RthJ-HS) (Estimated based on GS66516B). | .9 |

| Figure 4 GSP65RxxHB-EVB Functional Block Diagram1                                                       | 10 |

| Figure 5 IMS Boards1                                                                                    | 11 |

| Figure 6 J2/J5 header connection for gate drive1                                                        | 12 |

| Figure 7 IMS gate driver board1                                                                         | 13 |

| Figure 8 Gate driver circuit1                                                                           | 13 |

| Figure 9 Cross section view of IMS assembly showing the power Loop path1                                | 14 |

| Figure 10 IMS evaluation module assembly1                                                               | 15 |

| Figure 11 Recommended footprint for GSP65RxxHB-EVB (unit: mm)1                                          | 16 |

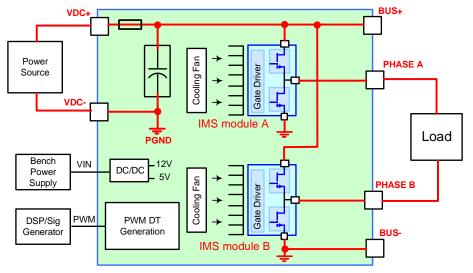

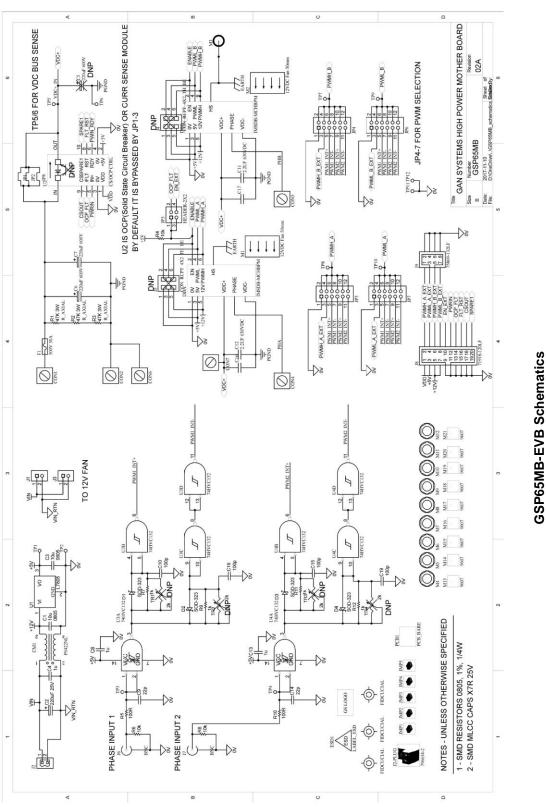

| Figure 12 Circuit block diagram of full bridge mother board1                                            | 17 |

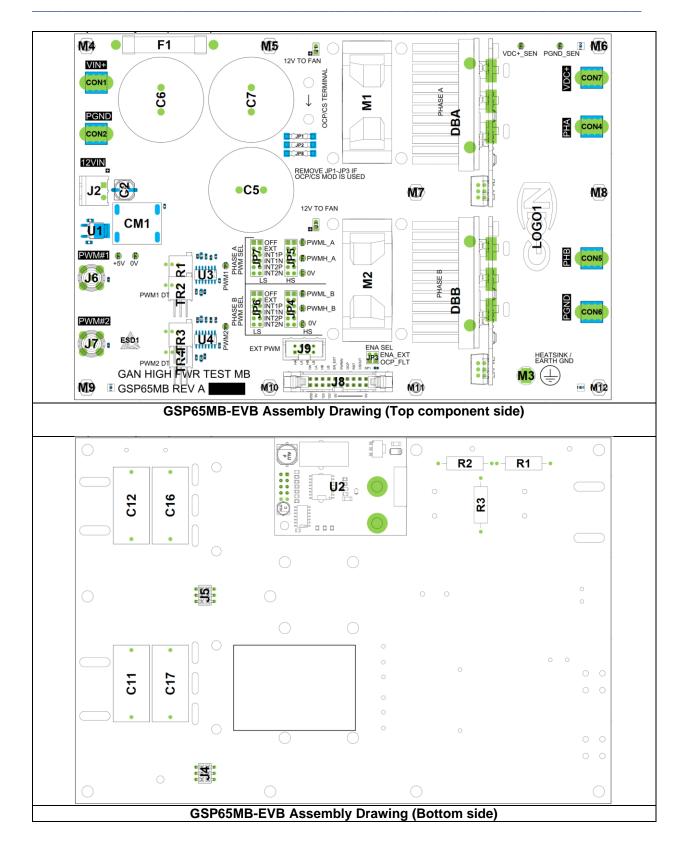

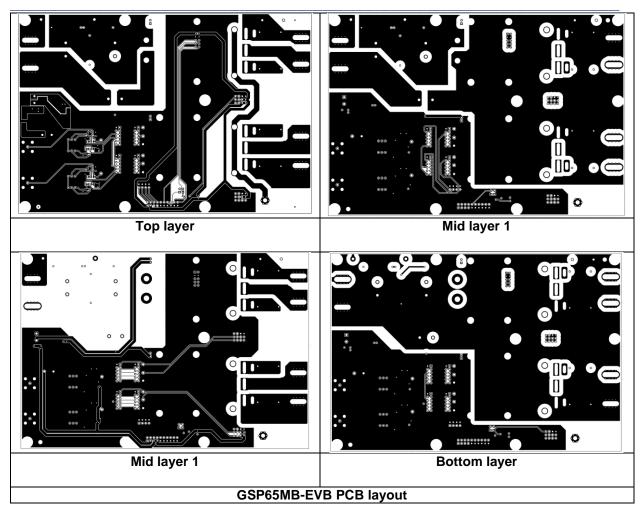

| Figure 13 GSP65MB-EVB1                                                                                  | 17 |

| Figure 14 DC Bus input and protection circuit1                                                          | 18 |

| Figure 15 PWM control input and dead time circuit1                                                      | 19 |

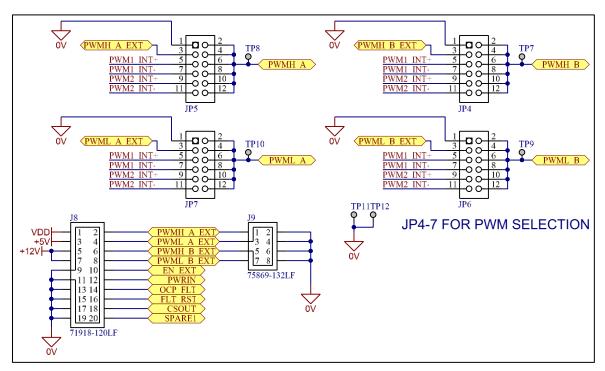

| Figure 16 External PWM input and selection circuits2                                                    | 20 |

| Figure 17 Double pulse test setup2                                                                      | 24 |

| Figure 18 Double pulse test waveforms (400V/120A)2                                                      | 24 |

| Figure 19 Open Loop Buck DC/DC Test Setup2                                                              | 24 |

| Figure 20 Buck DC/DC Efficiency and thermal measurement (400-200V, 80kHz, 0-2.4kW)2                     | 25 |

| Figure 21 Test waveforms (400Vin, 200Vo, 80kHz, Po=2.4kW)2                                              | 25 |

# **List of Tables**

| Table 1 Ordering configuration and part numbers                                  | 7  |

|----------------------------------------------------------------------------------|----|

| Table 2 Part numbers and Description                                             | 7  |

| Table 3 Performance comparison of 3 thermal design options for SMT power devices | 9  |

| Table 4 Description of J1 control pins                                           | 11 |

| Table 5 IMS board identification markings                                        | 12 |

| Table 6 List of PWM selection jumpers                                            | 20 |

| Table 7 Jumper settings for JP4-JP7                                              | 21 |

| Table 8 Evaluation Platform Configurations                                       | 22 |

# 1 Overview

#### 1.1 Introduction

A frequent challenge for power designers is to engineer a product that has excellent power density while simultaneously reducing the cost of the system.

This IMS evaluation platform demonstrates an inexpensive way to improve heat transfer, to increase power density and reduce system cost. An Insulated Metal Substrate PCB (IMS PCB) is used to cool GaN Systems' bottom-side cooled power transistors. An IMS PCB is also known as Metal Core/Aluminum PCB.

Examples of applications that have successfully used this approach include:

- Automotive: 3.3kW-22kW on board charger, DC/DC, 3- $\Phi$  inverter, high power wireless charger

- Industrial: 3-7kW Photovoltaic Inverter and Energy Storage System (ESS), Motor Drive / VFD

- Server/Datacenter: 3kW Server ACDC power supply.

- Consumer: Residential Energy Storage System (ESS)

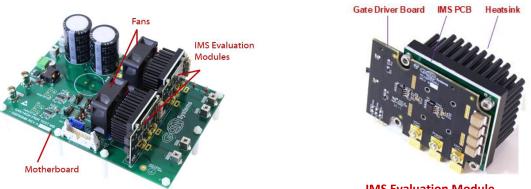

This evaluation platform consists up of a motherboard and IMS evaluation modules The IMS evaluation modules are configured as a half bridge and are available in 2 power levels; 2-4kW and 4-7kW.

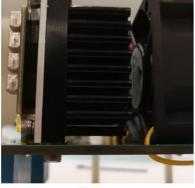

A suitable heatsink is included for lower power applications. For higher power applications additional heatsinking may be required. To prevent device damage, ensure adequate heatsinking through design and by monitoring the component temperatures during operation.

To assemble a heatsink, apply thermal grease to the heatsink / IMS board interface before screwing the units together. Enough thermal grease should be applied so that a small amount extrudes on all four sizes as the screws are tightened. Wipe the assembly clean.

**IMS Evaluation Module**

With these building blocks, the evaluation platform can be purchased in 4 different configurations: low power and high power, half bridge and full bridge. The IMS Evaluation modules can also be purchased independently to be used with the users' own board for in-system prototyping. Table 1 lists the ordering options.

GSP65RXXHB-EVB UG rev. 210914

| CONFIGURATION    | IMS HALF BRIDGE MODULE | MOTHERBOARD        |

|------------------|------------------------|--------------------|

| 3 kW Half Bridge | QTY 1 - GSP65R25HB-EVB |                    |

| 6 kW Half Bridge | QTY 1 - GSP65R13HB-EVB | QTY 1: GSP65MB-EVB |

| 3 kW Full Bridge | QTY 2 - GSP65R25HB-EVB |                    |

| 6 kW Full Bridge | QTY 2 - GSP65R13HB-EVB |                    |

#### Table 1 Ordering configuration and part numbers

#### Table 2 Part numbers and Description

| PART NUMBER                         | IBER DESCRIPTION                                          |              |  |

|-------------------------------------|-----------------------------------------------------------|--------------|--|

| GSP65MB-EVB High Power Mother Board |                                                           | N/A          |  |

| GSP65R25HB-EVB                      | GaN E-HEMT Half Bridge Evaluation Module $650V/25m\Omega$ | GS66516B     |  |

| GSP65R13HB-EVB                      | GaN E-HEMT Half Bridge Evaluation Module $650V/13m\Omega$ | 2 x GS66516B |  |

#### 1.2 IMS Evaluation Module - Technical Description

Using this platform, power designers can evaluate the performance of GaN Systems' E-HEMT (Enhancement mode High Electron Mobility Transistor) in high power and high efficiency applications.

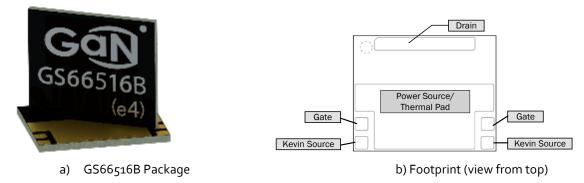

The IMS evaluation module is populated with GaN Systems' GS66516B, a bottom-side cooled E-HEMT, rated at  $650V/25m\Omega$ . The embedded GaN*PX*® SMD package has the following features:

- Dual symmetrical gate and source sense (kelvin source) for flexible PCB layout and paralleling.

- Large power source/thermal pad for improved thermal dissipation.

- Bottom-side cooled packaging for conventional PCB or advanced IMS/Cu inlay thermal design.

- Ultra-low inductance for high frequency switching.

Figure 1 - GS66516B GaNPX<sup>®</sup> SMD Package

The IMS evaluation module is a two-board assembly that includes GaN E-HEMTs, gate drivers, isolated DC/DC supply, DC bus decoupling capacitors and a heatsink to form a fully functional half bridge power stage. It was designed for users to gain hands-on experience in the following ways:

GSP65RXXHB-EVB UG rev. 210914

- Evaluate the GaN E-HEMT performance in any half bridge based topology, over a range of operating conditions. This can be done using either the accompanying power motherboard (P/N: GSP65MB-EVB) or with the users' own board for in-system prototyping.

- Use as a thermal and electrical design reference of the GS66516B GaNPX® SMD package in demanding high-power applications.

- Design concept for compact GaN smart power modules (or IPMs).

- Evaluate the performance of GaN E-HEMTs in parallel, for high power applications.

- Achieve high power density with its vertical design concept.

#### 1.3 IMS-based Power Stage Design

#### 1.3.1 IMS Board thermal design

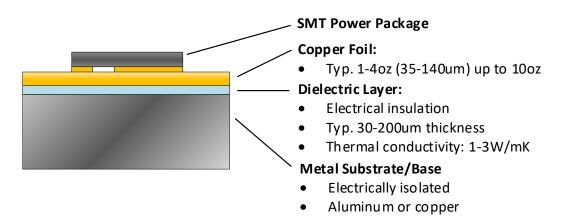

An IMS board assembly uses metal as the PCB core, to which a dielectric layer and copper foil layers are bonded. The metal PCB core is often aluminum. The copper foil layers can be single or double-sided. An IMS board offers superior thermal conductivity to standard FR4 PCB. It's commonly used in high power, high current applications where most of heat is concentrated in a small footprint SMT device.

#### Figure 2 Cross-section view of a single layer IMS board

As high-speed Gallium Nitride power devices are adopted widely, the industry is trending away from through-hole packaging (TH), towards surface mount packaging (SMT). Traditional TH devices, such as the TO-220, are no longer the appropriate choice because their high parasitic inductance and capacitance negate the performance benefits offered by GaN E-HEMTs. SMT packaging, such as PQFN, D2PAK and GaN Systems' GaN*PX*®, by comparison, offer low inductance and low thermal impedance, enabling efficient designs at high power and high switching frequency.

Thermal management of SMT power transistors must be approached differently than TH devices. TO packages are cooled by attaching them to a heatsink, with an intermediary Thermal Interface material (TIM) sheet for electrical high voltage insulation. The traditional cooling method for SMT power devices is to use thermal vias tied to multiple copper layers in a PCB. The IMS board presents designers with another option which is especially useful for high power applications. The IMS board has a much lower junction to heatsink thermal resistance ( $R_{thJ-HS}$ ) than FR4 PCBs, for efficient heat transfer out of the transistor. As well, assembly on an IMS board has lower assembly cost and risk than the TH alternative. The manual assembly process of a TO package onto a heatsink is costly and prone to human error.

GSP65RXXHB-EVB UG rev. 210914

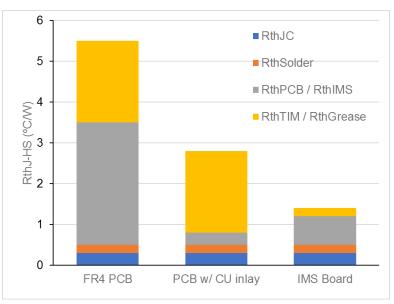

Table 3 compares 3 different design approaches for cooling discrete SMT power devices. While the cost is lower for a FR4 PCB cooling with thermal vias, the IMS board offers the best performance for thermal management Figure 3 provides a quantitative comparison of the thermal resistance for the 3 design options. The IMS board clearly comes out ahead.

|                       | FR4 PCB Cooling with Vias                                                             | FR4 PCB with Cu inlay                                                                         | IMS PCB<br>IMS Board<br>Thermal<br>grease                                                                                         |

|-----------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Thermal resistance    | Good                                                                                  | Cu-inlay<br>Better                                                                            | Best                                                                                                                              |

| Electrical Insulation | No, additional TIM needed                                                             | No, additional TIM needed                                                                     | Yes                                                                                                                               |

| Cost                  | Lowest                                                                                | High Low                                                                                      |                                                                                                                                   |

| Advantages            | <ul> <li>Standard process</li> <li>Lowest cost</li> <li>Layout flexibility</li> </ul> | <ul> <li>Layout flexibility</li> <li>Improved thermal<br/>compared to thermal vias</li> </ul> | <ul><li>Lowest thermal resistance</li><li>Electrically isolated</li></ul>                                                         |

| Design challenges     | • High PCB thermal resistance                                                         | • Cu-inlay surface coplanarity<br>• High TIM thermal resistance                               | <ul> <li>Layout limited to 1 layer</li> <li>Parasitic inductance</li> <li>Coupling capacitances to the metal substrate</li> </ul> |

Table 3 Performance comparison of 3 thermal design options for SMT power devices

The following additional measures are taken to optimize the design further.

- The half bridge design is implemented as a two-board asssembly. The gate drive circuitry is assembled on a multi-layer FR4. This includes the gate driver ICs, an isolated DC/DC converter to power the driver IC, and DC decoupling capacitors. The GaN E-HEMTs are mounted to the IMS board. This approach addresses the shortcomings of implementing the design on a single layer IMS board.

- To mate the IMS board to the FR4 driver board, small pitch low profile SMT headers are used. The short loop lengths optimize parasitic gate inductance.

- While a large copper area is preferred to maximize heat spreading and handle high current, the area of copper at the switching node (high dv/dt) needs to be minimized to reduce the parasitic coupling capacitance to the metal substrate. An IMS board with thicker dielectric layer (100um) is chosen on this design to further reduce this effect. Refer to Figure 9 for more detail.

#### 1.3.2 Control and power I/O

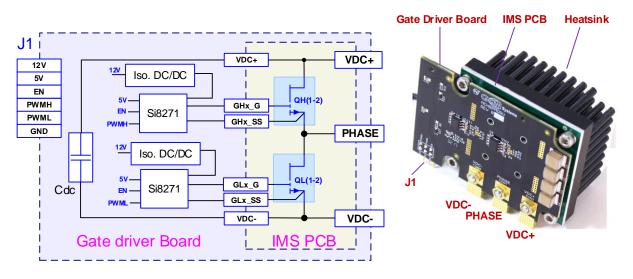

The functional block diagram of the IMS evaluation module assembly is shown in figure 4.

Figure 4 GSP65RxxHB-EVB Functional Block Diagram

The three power pins are

- CON1: VDC+, Input DC Bus voltage

- CON2: Phase, Switching node / phase output

- CON3: VDC- Input DC bus voltage ground return.

- Note that control ground GND on J1 is isolated from VDC- on CON3.

The control pins on connector J1 are described in table 4.

Table 4 Description of J1 control pins

| PIN                                                                                 | DESCRIPTION                                                                                                                                                                   |  |

|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 12V                                                                                 | +12V bias supply for gate drive. This feeds to the input of two isolated DC/DC (12V-9V) to generate isolated +6/-3V gate drive bias.                                          |  |

| 5V                                                                                  | +5V bias supply for gate driver IC.                                                                                                                                           |  |

| EN                                                                                  | Enable input. Logic low disables all the gate drive outputs. If not used the pin can be pulled up to 5V and it is recommended to add a small 0.1uF capacitor to filter noise. |  |

| PWMH High side PWM logic input for top switch Q1. It is compatible with 3.3V and 5V |                                                                                                                                                                               |  |

| PWML                                                                                | Low side PWM logic input for bottom switch Q2. It is compatible with 3.3V and 5V                                                                                              |  |

| GND/0V                                                                              | Logic inputs and gate drive power supply common ground return.                                                                                                                |  |

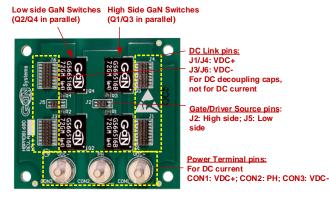

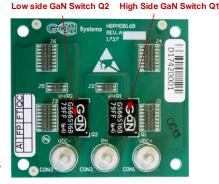

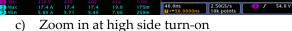

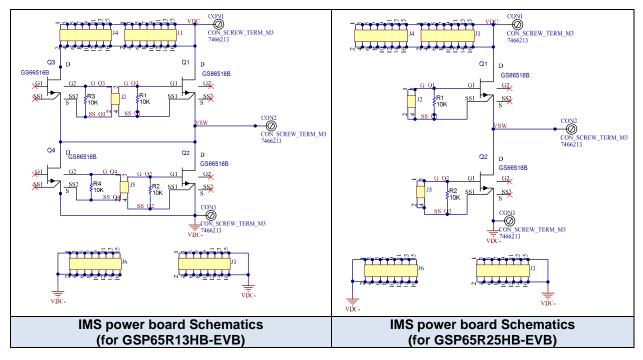

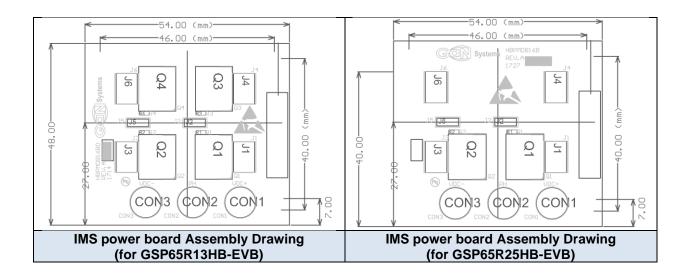

#### 1.3.3 IMS Board Design

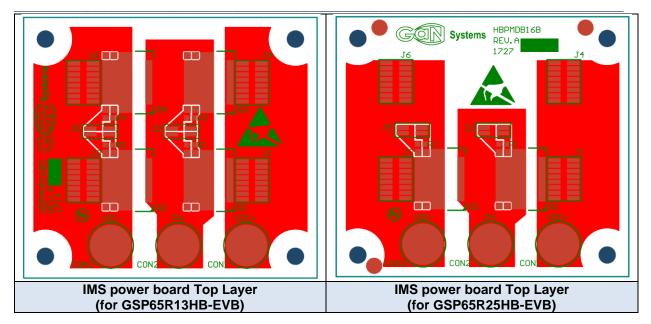

IMS BOARD FOR GSP65R13HB-EVB

IMS BOARD FOR GSP65R25HB-EVB

Figure 5 IMS Boards

The IMS board is populated with the following components:

- **Q1-Q4:** GS66516B E-HEMTs in a half bridge configuration.

- o 6kW GSP25R13HB-EVB: Q1/Q3 (high side) and Q2/Q4 (low side). Devices are paralleled.

- o 3kW GSP25R25HB-EVB: Only Q1 and Q2 are populated.

- CON1, CON2, CON3:

- SMT M3 stud power terminals (Wurth Electronics, P/N: 7466213).

- These terminals are designed to carry the main current.

- J2-J5: SMT 2x2 header (Samtec P/N: FTM-102-02-L-DV) for gate driver connections.

- For optimum parallel operation of the GaN E-HEMTs, individual Gate (G) and Source Sense (SS) resistors should be used to ensure a symmetric gate loop layout. G and SS on each device are brought to the driver board separately by J2/J5 as shown in figure 6. By utilizing the dual gate feature on GS66516B package, an optimum symmetric gate loop

layout is easily achieved. For additional detail, refer to GaN Systems' <u>application note</u> <u>GN004</u>,

Figure 6 - J2/J5 header connection for gate drive

- **R1-R4**: 10K pull-down resistors.

- These resistors prevent accidental gate turn-on or overvoltage induced by static or miller capacitor feedback when the gate driver circuit is not active (during start-up) or malfunctional.

- J1, J3, J4 and J6: 2x8 SMT headers (Samtec P/N: FTM-108-02-L-DV-P-TR) for DC coupling capacitors.

- Note: These pins are NOT designed to carry DC main current.

- Together with the DC coupling capacitors on the driver board, they are designed to create a balanced and low inductance power loop path for high-frequency current across the half bridge.

The two versions of the IMS board can be identified by the markings described in table 5.

| Table 5 IMS board identification markir | igs |  |

|-----------------------------------------|-----|--|

|-----------------------------------------|-----|--|

| EVB PART NUMBER | GaN E-HEMT                       | IMS BOARD MARKINGS |  |

|-----------------|----------------------------------|--------------------|--|

| GSP65R13HB-EVB  | GS66516B x 2 in parallel (Q1-Q4) | HBPMDB16BD         |  |

| GSP65R25HB-EVB  | GS66516B x 1 (Q1, Q2)            | HBPMDB16B          |  |

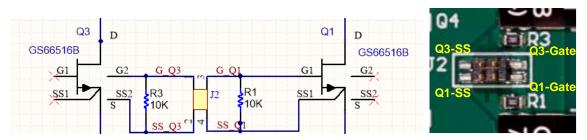

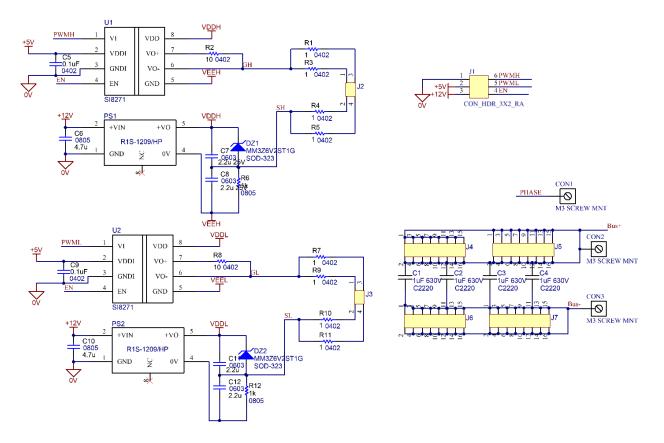

#### 1.3.4 Gate driver board

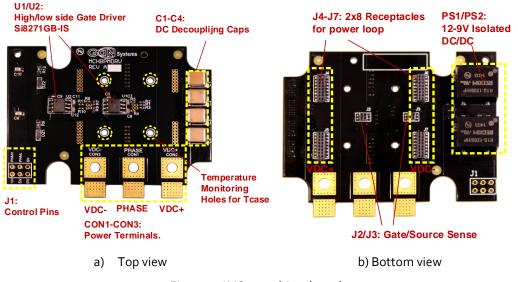

Figure 7 - IMS gate driver board

A gate driver board is designed to mate closely with the IMS board. It provides the half bridge gate drivers for the half bridge GaN E-HEMTs and DC link decoupling capacitors. It also enables the IMS board to be mounted vertically for high power density design.

- Half bridge gate drivers: high and low side gate drivers, fully isolated.

- U1 and U2 are the isolated gate drivers (Silicon Labs P/N: Si8271)

- PS1/PS2 are 12-9V isolated power supplies (RECOM P/N: R1S-1209/HP) which are then divided to +6/-3V to power the gate drivers.

- R7, R9, R10 and R11 are small distributed gate and source resistors, used on each paralleled device to reduce gate ringing or oscillation.

- R8 provides additional gate resistance to control the turn-on slew rate.

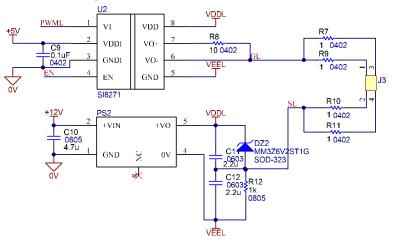

Figure 8 Gate driver circuit

• **DC link decoupling capacitors:** As it is challenging to create low inductance power loop on singlelayer IMS board, DC decoupling capacitors are placed on multi-layer gate driver PCB. The power loop path is highlighted as below.

GSP65RXXHB-EVB UG rev. 210914

Figure 9 - Cross section view of IMS assembly showing the power Loop path

- **Power terminals and control I/O:** CON1-CON3 are designed so that the IMS evaluation module can be mounted vertically. The PCB tabs are edge-plated and can be wave-soldered to the main board. Alternatively, the power cables can be directly screwed onto the M3 screw post for power connections. J1 is populated with a 2x3 standard 0.1" pitch right angle header which be either soldered or attach to the socket on the main board.

- **Temperature monitoring holes:** 4 holes are located on the center of 4 GaN E-HEMTs to assist with the temperature monitoring during operation. An IR camera can be used to monitor the case temperature through these holes. The temperature measured at the center of GaN*PX*® package will be close to the T<sub>J</sub>.

NOTE: Thermal performance of the transistors is dependent on a number of factors including circuit configuration, ambient temperature, airflow, and heatsinking. The user is responsible for monitoring the temperature of the devices to ensure operation remains within specification.

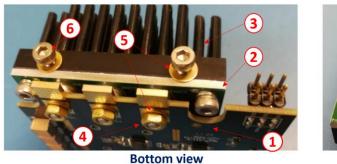

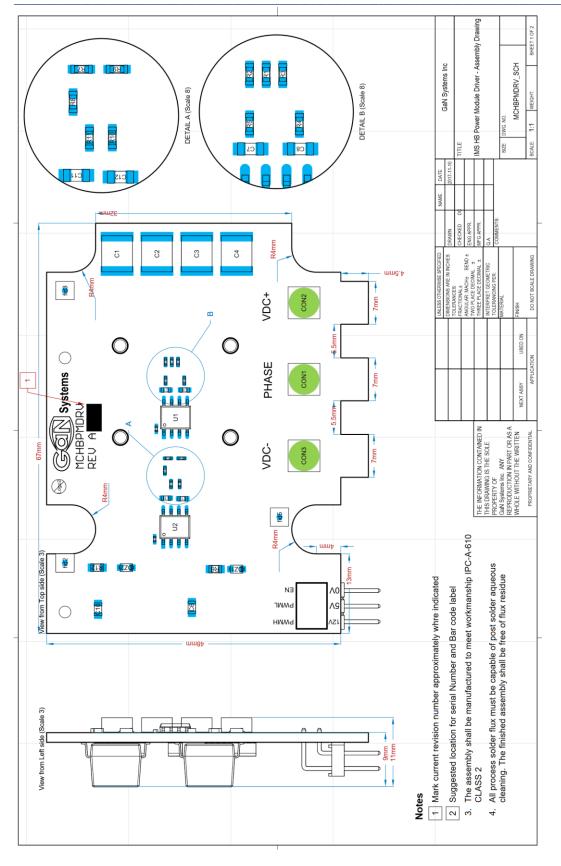

#### 1.3.5 Evaluation module assembly

Top View with driver board removed

| ltem | QTY | Description                                     | Manufacturer       | Part Number                |

|------|-----|-------------------------------------------------|--------------------|----------------------------|

| 1    | 1   | PCBA H/B DRIVER<br>BOARD                        | GAN SYSTEMS        | MCHBPMDRV                  |

| 2    | 1   | PCBA GS66516B HALF<br>BRIDGE IMS POWER<br>BOARD | GAN SYSTEMS        | MCHBPM16BD or<br>MCHBPM16B |

| 3    | 1   | ,                                               | COOL<br>INNOVATION | 3-211910RS74844            |

| 4    | 3   | BRASS M3 NUT 0.5MM                              | McMaster-Carr      | 90690A037                  |

| 5    | 8   | Brass Washer 0.5mm<br>Thickness M3              | McMaster-Carr      | 91635A190                  |

| 6    | 6   | M3 18-8 Stainless<br>Steel Socket Head<br>Screw | McMaster-Carr      | 91292A111                  |

| 7    | 4   | 316 Stainless Steel<br>Split Lock Washer        | McMaster-Carr      | 94241A510                  |

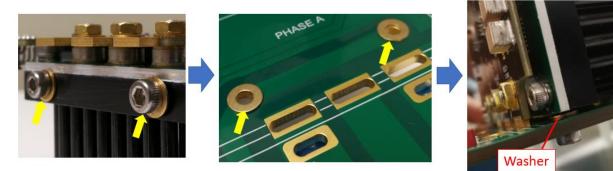

Figure 10 - IMS evaluation module assembly

The photos in Figure 10 shows show how the IMS evaluation module is assembled. The bill of materials is provided for reference.

If repair or customization is required, please note the following:

- Brass washers (#5) are required on 3 screw terminals to level off the terminals and connectors.

- When dismounting the driver board (#1):

- Remove 3 nuts and washers.

- To avoid damaging the SMT header pins, **<u>gently</u>** wiggle the driver board until the connectors are loose and pull it up straight.

- Two M3 hex screws provided on the bottom side of the heatsink are used.

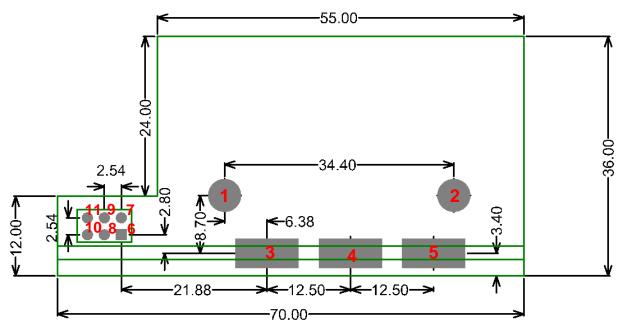

The IMS evaluation module allows users to easily evaluate the GaN performance in their own systems. Refer to the recommended footprint drawing of GSP65RxxHB-EVB as shown below:

#### All units are in mm

| Pin  | Description | Hole Size | Plated | Hole type | Length |

|------|-------------|-----------|--------|-----------|--------|

| 1-2  | M3 Mounting | 4mm       | Y      | Round     |        |

|      | Power       |           |        |           |        |

| 3-5  | terminal    | 2.5mm     | Y      | Slot      | 9mm    |

| 6-11 | Signal pins | 1.2mm     | Y      | Round     |        |

Figure 11 Recommended footprint for GSP65RxxHB-EVB (unit: mm)

### 2 Using the IMS evaluation module with the mother board GSP65MB-EVB

Figure 12 Circuit block diagram of IMS mother board

#### Figure 13 GSP65MB-EVB

GaN Systems offers a high-power mother board that can be purchased separately. The ordering part number is GSP65MB-EVB. It can be used as a platform for evaluating the IMS evaluation module in any half or full bridge topology.

GSP65RXXHB-EVB UG rev. 210914

#### 2.1 VDC Input Fusing

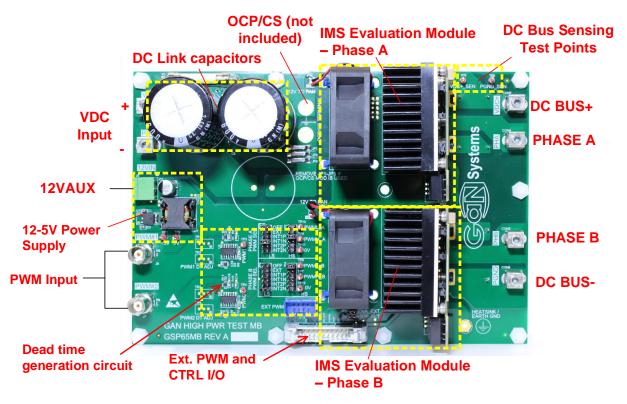

Figure 14 DC Bus input and protection circuit

The DC bus input on the motherboard are through connectors CON1 (VIN+) and CON2 (PGND). F1 is a 500V/30A-rated fuse for system protection. In case a lower DC bus voltage and higher than 30A current are required, bypass F1 and use external circuit breaker or fuse for protection.

#### 2.2 Optional Over Current / Current Sense Protection Circuit

Note: The mother board does not ship with Over Current Protection (OCP) or Current Sense (CS) circuitry. By default, U2 is bypassed by JP1-JP3.

However, the motherboard design is provisioned for adding an externally designed fast Over Current Protection (OCP) or current sensing (CS) circuit.

A non-populated footprint is available to the user. It consists of two screw terminals and a 2x5 header as shown in figure 14. If needed, users can design their own OCP or CS circuit and connected it to the mother board using these connections.

A few examples of how this can be used are

- Use an IGBT driver with de-sat protection as a solid-state circuit breaker for input power control and OCP.

- For current sensing, a hall effect sensor can be added to the circuit to feed the CSOUT output to a DSP controller board.

• For current monitoring with a scope probe, a simple wire loop can be soldered across the two terminals.

#### 2.3 12V input

The motherboard is powered from a 12V source, through connector J2. An on-board voltage regulator provides 5V for the IMS evaluation modules and control logic circuits. J1 and J3 provide 12V to power the cooling fans.

#### 2.4 PWM control circuit

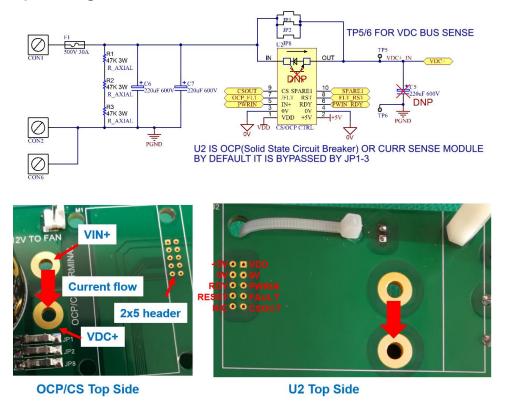

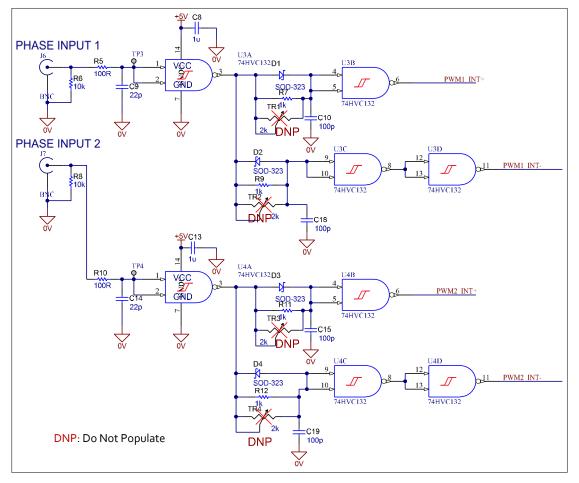

Figure 15 PWM control input and dead time circuit

Figure 16 External PWM input and selection circuits

The PWM signals of top and bottom switches on both phase legs can be individually selected by the jumpers JP4-JP7. Users can choose between 2 pairs of independent complementary on-board internal PWM signals (non-inverted and inverted) with dead time or external high/low side drive signals from J8 or J9.

Two channels of independent on-board dead time generation circuits are included on the mother board. Dead time is controlled by RC delay circuits. The default dead time is set to approximately 100ns. Potentiometers locations are provided (TR1-TR4, not populated) to allow fine adjustment of the dead time if needed.

#### WARNING!

ALWAYS double check the jumper setting and probe PWM signals before applying power. Incorrect PWM inputs or jumper settings may cause device failures.

| Phase Leg | Switch position | Jumper | Name   | Probe test points |

|-----------|-----------------|--------|--------|-------------------|

| Dhasa A   | High side       | JP5    | PWMH_A | TP8               |

| Phase A   | Low side        | JP7    | PWML_A | TP10              |

| Dhace P   | High side       | JP4    | PWMH_B | TP7               |

| Phase B   | Low side        | JP6    | PWML_B | TP9               |

| Table 6 List of PWM | selection | jumpers |

|---------------------|-----------|---------|

|---------------------|-----------|---------|

#### Table 7 Jumper settings for JP4-JP7

| Position | Jumper Setting | Description                    | Source            |

|----------|----------------|--------------------------------|-------------------|

| 1        | OFF            | Disabled                       |                   |

| 2        | EXT            | External PWM Signal            | J8/J9             |

| 3        | INT1P          | Internal Phase #1 non-inverted | J6: Phase Input 1 |

| 4        | INT1N          | Internal Phase #1 inverted     | J6: Phase Input 1 |

| 5        | INT1P          | Internal Phase #2 non-inverted | J7: Phase Input 2 |

| 6        | INT1N          | Internal Phase # 2 inverted    | J7: Phase Input 2 |

#### 2.5 Installation of IMS evaluation module

Follow the steps below to install the IMS evaluation module onto the motherboard:

- 1. Remove M3 hex screws and washers on the bottom side of module.

- 2. Place the brass washer onto the 2 matching mounting holes on mother board and then insert the IMS evaluation module.

- 3. Install the M3 screws from the bottom side. <u>Ensure that 2 washers are in place between the heatsink</u> <u>and mother board as they are needed to level off J1 and 3 power terminal tabs.</u>

4. Tighten the screws, and solder J1 and 3 power terminals from the bottom side.

Top view

#### 2.6 Operation modes

The Evaluation Platform can be configured into different topologies and operation modes as shown below

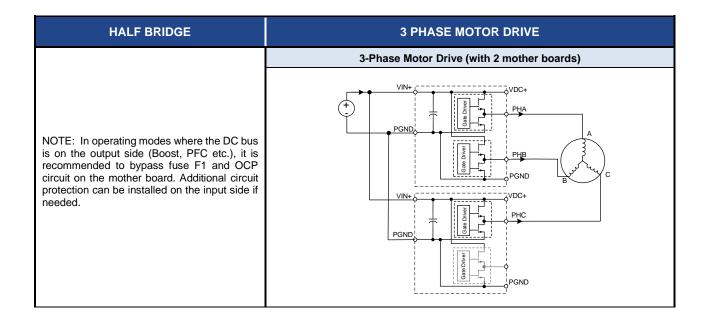

Table 8 Evaluation Platform Configurations

## 3 Test Results

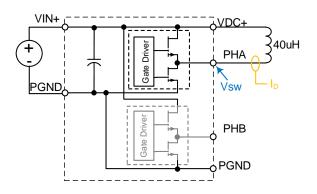

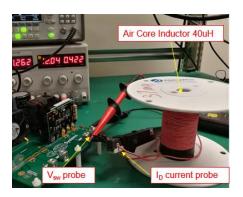

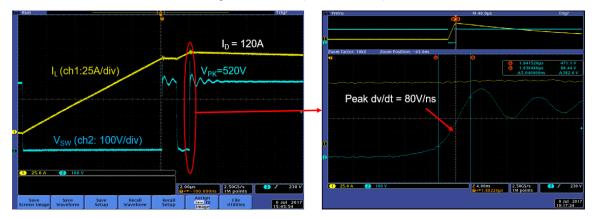

#### 3.1 Double pulse test (GSP65R13HB-EVB, 650V/13mΩ)

- Test condition:  $V_{DS} = 400V$ ,  $I_D = 120A$ ,  $V_{GS} = +6V/-3V$ , L = 40uH, No RC Snubber,  $T_J = 25^{\circ}C$

- Measured peak V<sub>DS</sub> = 520V and 80V/ns dv/dt

- Reliable hard switching with 2 x GS66516B in parallel is achieved at full rated current

Figure 17 Double pulse test setup

Figure 18 Double pulse test waveforms (400V/120A)

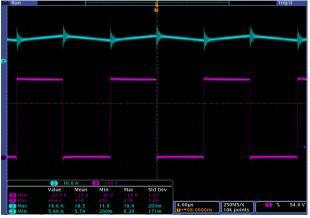

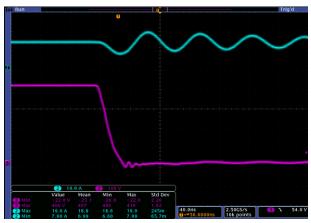

#### 3.2 Open-loop Synchronous Buck DC/DC operation (GSP65R25HB-EVB, 650V/25mΩ)

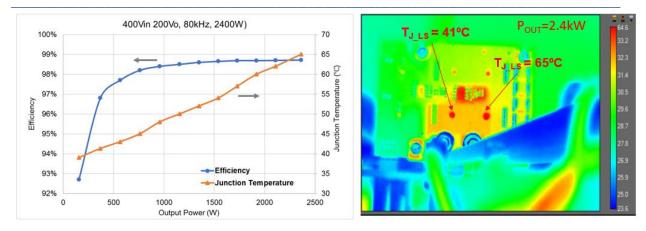

- Test condition: VIN = 400V, VOUT = 200V, fsw=80kHz, Po=2.4kW, TAMB = 25°C.

- Peak efficiency 98.8%; Device case temperature 65°C @ full load

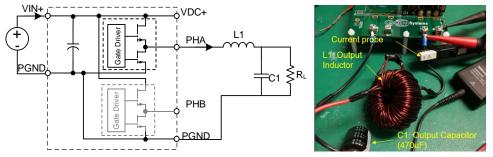

Figure 19 Open Loop Buck DC/DC Test Setup

Figure 20 Buck DC/DC Efficiency and thermal measurement (400-200V, 80kHz, 0-2.4kW)

a) 400-200V, 2.4kW output

b) Zoom in at high side turn-off

Figure 21 Test waveforms (400Vin, 200Vo, 80kHz, Po=2.4kW)

### 4 Appendix

#### 4.1 IMS Power Board

#### IMS Power board bill of materials

| Description       | Manufacturer Manufacturer P/N             | GSP65R13HB-EVB       |                  | GSP65R25HB-EVB |                  |     |

|-------------------|-------------------------------------------|----------------------|------------------|----------------|------------------|-----|

| Description       | Description Manufacturer Manufacturer P/N |                      | Designator QT    |                | Designator       | QTY |

| SMT POWER TERM    |                                           |                      |                  |                |                  |     |

| M3                | Wurth Electronics                         | 7466213              | CON1, CON2, CON3 | 3              | CON1, CON2, CON3 | 3   |

| Connector header  |                                           |                      |                  |                |                  |     |

| 1mm pitch SMT 2x8 | SAMTEC                                    | FTM-108-02-L-DV-P-TR | J1, J3, J4, J6   | 4              | J1, J3, J4, J6   | 4   |

| Connector header  |                                           |                      |                  |                |                  |     |

| 1mm pitch SMT 2x2 | SAMTEC                                    | FTM-102-02-L-DV      | J2, J5           | 2              | J2, J5           | 2   |

| GAN TRANS E-      |                                           |                      |                  |                |                  |     |

| MODE 650V 60A BOT |                                           |                      |                  |                |                  |     |

| SIDE COOL         | gan systems                               | GS66516B             | Q1, Q2, Q3, Q4   | 4              | Q1, Q2           | 2   |

| RES, 1%, 0603     | generic                                   | generic 0603 1%      | R1, R2, R3, R4   | 4              | R1, R2           | 2   |

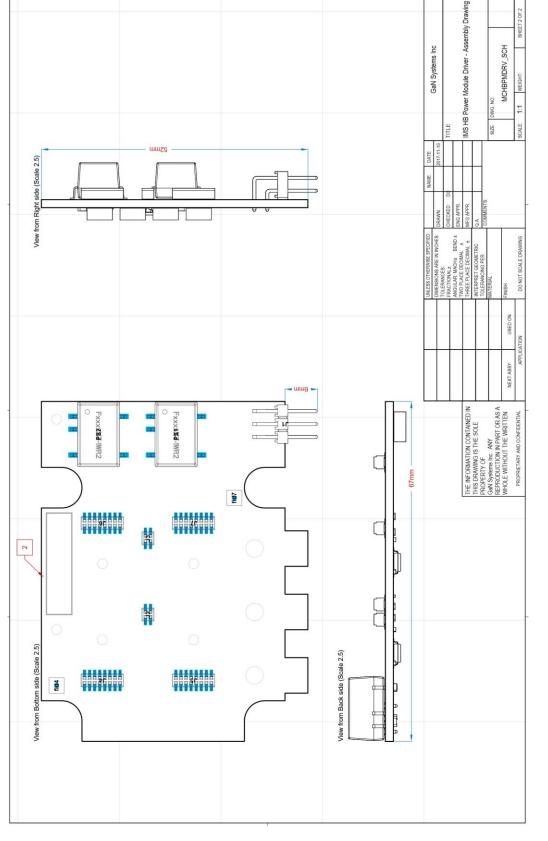

#### 4.2 IMS Gate driver board

IMS gate driver board schematics

Top assembly drawing

Bottom assembly drawing

| IMS gate driver board bill of materials                   |                                        |     |                        |                     |  |

|-----------------------------------------------------------|----------------------------------------|-----|------------------------|---------------------|--|

| DESCRIPTION                                               | DESIGNATOR                             | QTY | MANUFACTURER           | PARTNUMBER          |  |

| 1µF ±10% 630V Ceramic<br>Capacitor X7R 2220 (5750 Metric) | C1,C2, C3, C4                          | 4   | Knowles Syfer          | 2220Y6300105KXTWS2  |  |

| CAP, CERM, 0.1uF,10V +/-10%,<br>X7R, 0402                 | C5, C9                                 | 2   | AVX Corporation        | 0402ZD104KAT2A      |  |

| CAP, CERM, 0.1uF,16V +/-10%,<br>X7R, 0805                 | C6, C10                                | 2   | Samsung                | CL21B104KOANNNC     |  |

| CAP CER 2.2UF 16V X5R 0603                                | C7, C8,C11,<br>C12                     | 4   | Murata                 | GRM188R61C225KE15D  |  |

| DIODE ZENER 6.2V                                          | DZ1, DZ2                               | 2   | ON Semiconductor       | MM3Z6V2ST1G         |  |

| HEADER PIN 2X3 R/A                                        | J1                                     | 1   | Samtec                 | TSW-103-08-L-D-RA   |  |

| 2x2 Sucket                                                | J2, J3                                 | 2   | Samtec                 | CLM-102-02-F-D-TR   |  |

| 2x8 Sucket                                                | J4, J5, J6, J7                         | 4   | Samtec                 | CLM-108-02-F-D-P-TR |  |

| DC/DC CONV SMD 1W                                         | PS1, PS2                               | 2   | CUI                    | PDS1-S12-S9-M-TR    |  |

| RES SMD 1 OHM 1% 1/16W<br>0402                            | R1, R3, R4, R5,<br>R7, R9, R10,<br>R11 | 8   | Yageo                  | RC0402FR-071RL      |  |

| RES SMD 10 OHM 1% 1/16W<br>0402                           | R2, R8                                 | 2   | Yageo                  | RC0402FR-0710RL     |  |

| RES SMD 1K OHM 1% 1/8W<br>0805                            | R6, R12                                | 2   | Yageo                  | RC0805FR-071KL      |  |

| IC ISOL GATE DRIVER SINGLE                                | U1, U2                                 | 2   | Silicon Labs           | SI8271AB-ISR        |  |

| PCB for MCHPMDRV                                          | PCB                                    | 1   | Shenzhen Sprint<br>PCB |                     |  |

## 4.3 Full bridge Mother Board GSP65MB-EVB)

GSP65RXXHB-EVB UG rev. 210914

#### **GSP65MB-EVB Bill of Materials**

| ntity Reference                                                            | Description                            | Manufacturer            | Part number        | Assembly Note                    |

|----------------------------------------------------------------------------|----------------------------------------|-------------------------|--------------------|----------------------------------|

| 1 PCB1                                                                     | PCB BARE                               | Shenzhen Sprint PCB     |                    |                                  |

|                                                                            |                                        | Samsung Electro-        |                    |                                  |

| 2 C1, C3                                                                   | CAP, CERM, 10 uF, +/-10%, X7R, 0805    | Mechanics America, Inc. | CL21A106KAYNNNE    |                                  |

| 1 C2                                                                       | CAP ALUM 220UF 20% 25V SMD             | Panasonic ECG           | EEE-FK1E221P       |                                  |

|                                                                            |                                        | Samsung Electro-        |                    |                                  |

| 3 C4, C8, C13                                                              | CAP, CERM, 1uF, +/-10%, X7R, 0603      | Mechanics America, Inc. | CL10B105KA8NNNC    |                                  |

| 2 <mark>65</mark> , C6, C7                                                 | GENERIC CAPACITOR POLARISED            | Nichicon                | LGN2X221MELC50     | DO NOT INSTALL C5                |

| 2 C9, C14                                                                  | CAP, CERM, 0.022uF, +/-10%, X7R, 0603  | Kyocera AVX             | 06035C220JAT2A     |                                  |

| 4 C10, C15, C18, C19                                                       | CAP, CERM, 100pF,25V +/-10%, X7R, 0603 | KEMET                   | C0603C101J3GACTU   |                                  |

| 4 C11, C12, C16, C17                                                       | CAP, FILM, 2.2uF, +/-10%, LS=27.5mm    | KEMET                   | F862FN225K310ZV054 |                                  |

| 1 CM1                                                                      | COMMON MODE CHOKE 4.7A 2LN SMD         | Pulse Electronics       | P0422NLT           |                                  |

| CON1, CON2, CON4, CON5, CON6,                                              |                                        |                         |                    |                                  |

| 6 CON7                                                                     | PCB WIRE LUG HIGH CURRENT 6-16AWG      | Lugs Direct             | B6A-PCB-HEX        |                                  |

| 4 D1, D2, D3, D4                                                           | DIODE SCHOTTKY 30V 200MA SOD323        | Diodes                  | BAT54WS-E3-08      |                                  |

| 2 DBA, DBB                                                                 | 650V GAN HIGH BRIDGE IMS DEMO KIT      | GaN Systems             |                    | DO NOT INSTALL                   |

| 1 F1                                                                       | FUSE 3AB 1/4 DIA                       | Littelfuse              | 0505030.MXEP       |                                  |

| 2 J1, J3                                                                   | CONN HEADER VERT 2POS .100 TIN         | TE Connectivity         | 640456-2           |                                  |

| 1 J2                                                                       | TERM BLK HDR 2POS R/A 5.08MM           | TE Connectivity         | 796638-2           |                                  |

| 2 J4, J5                                                                   | 03+03 DIL BTM ENTRY SKT                | Harwin                  | M20-7850342        | DO NOT INSTALL                   |

| 2 J6, J7                                                                   | BNC JACK STR 500HM PCB NMT             | Amphenol Connex         | 112538             |                                  |

| 1 J8                                                                       | CONN HEADER 20POS DUAL VERT PCB        | Amphenol FCI            | 71918-120LF        |                                  |

| 1 J9                                                                       | CON HDR 8POS DUAL VERT                 | Amphenol FCI            | 75869-132LF        |                                  |

| 3 JP1, JP2, JP8                                                            | JUMPER SMD                             | Harwin                  | S1621-46R          |                                  |

| 1 JP3                                                                      | CONN HEADER .100" DUAL STR 4POS        | Sullins                 | PRPC002DAAN-RC     |                                  |

| 4 JP4, JP5, JP6, JP7                                                       | CONN HEADER .100" DUAL STR 12POS       | Sullins                 | PRPC006DAAN-RC     |                                  |

| 2 M1. M2                                                                   | FAN AXIAL 50X20MM 12VDC WIRE           | Delta                   | AFB0512VHD         | USE TIE WRAP TO MOUNT M1/M2.     |

| 2                                                                          |                                        | Dona                    | 71 000121110       | CRIMP WIRES FROM FAN TO          |

|                                                                            |                                        |                         |                    | RCPT1/RCPT2, RED(+) at Pin1, and |

| 2 RCPT1, RCPT2                                                             | CONN RECEPT 2POS 24AWG MTA100          | TE Connectivity         | 3-640441-2         | connect to J1/J3                 |

| 3 R1. R2. R3                                                               | RES AXIAL 6 MM DIA L=15.5MM            | KOA Speer               | MOS3CT631R473J     |                                  |

| 3 R4, R6, R8                                                               | RES, 0.05 %, 0603                      | Vishay / Dale           | TNPU060310K0AWEN00 |                                  |

| 2 R5, R10                                                                  | RES, 1%, 0603                          | Yageo                   | RC0603FR-07100RL   |                                  |

| 4 R7, R9, R11, R12                                                         | RES, 1%, 0603                          | Philips Mepco           | RC0603FR-071KL     |                                  |

| TP1, TP2, TP3, TP4, TP5, TP6, TP7,                                         |                                        |                         | Reddoor R-or IRE   |                                  |

| 12 TP8, TP9, TP10, TP11, TP12                                              | TESTPOINT SCOPE GRABBER                | Keystone Electronics    | 5010               |                                  |

| 4 TR1, TR2, TR3, TR4                                                       | TRIMMABLE RESISTOR                     | Bourns                  | PV36W202C01B00     | DO NOT INSTALL                   |

| 1 U1                                                                       | LINEAR REGULATOR 5.0V                  | STMicroelectronics      | L7805CDT-TR        |                                  |

| 1 U2                                                                       | OCP/SSCB MODULE                        | GAN SYSTEMS             | 2.000021111        | DO NOT INSTALL                   |

| 2 U3, U4                                                                   | QUAD 2-IN POS NAND SCH                 | Fairchild Semiconductor | 74VHC132MX         |                                  |

| 2 00, 01                                                                   |                                        |                         | 14110102007        |                                  |

| 1 J2-PLUG                                                                  | TERM BLOCK BLUG 2POS 5.08MM            | TE Connectivity         | 796634-2           | INSTALL ON J2                    |

| 5 JMP1, JMP2, JMP3, JMP4, JMP5                                             | JUMPER SHUNT SHUNT                     | TE Connectivity         | 382811-8           |                                  |

| 8 M4, M5, M6, M7, M8, M9, M10, M11                                         | MNT HOLE STDOFF 8/32 1-1/2" NYLON      | Keystone Electronics    | 4838               | INSTALL STDOFF ON BOTTOM SID     |

| M13, M14, M15, M16, M17, M8, M9, M10, M11<br>M13, M14, M15, M16, M17, M18, | WINT HOLE STOUFF 0/32 1-1/2 NYLON      | Reysione Electronics    | 4030               | INSTALL STOUFF UN BUTTOM SIDI    |

| 8 M19, M20,                                                                | HEX NUT 5/16" NYLON 8-32               | Keystone Electronics    | 9607               |                                  |

| 5 m 10, m 20,                                                              |                                        |                         |                    | FOLLOW ASSEMBLY PROCEDURES       |

| 1 C20                                                                      | CAP CER 0.1UF 25V X7R RADIAL           | Murata                  | RDER71E104K0P1H03B | FOR INSTALLATION OF C20          |

#### **Evaluation Board/kit Important Notice**

GaN Systems Inc. (GaN Systems) provides the enclosed product(s) under the following AS IS conditions:

This evaluation board/kit being sold or provided by GaN Systems is intended for use for ENGINEERING DEVELOPMENT, DEMONSTRATION, and OR EVALUATION PURPOSES ONLY and is not considered by GaN Systems to be a finished end-product fit for general consumer use. As such, the goods being sold or provided are not intended to be complete in terms of required design-, marketing-, and/or manufacturing-related protective considerations, including but not limited to product safety and environmental measures typically found in end products that incorporate such semiconductor components or circuit boards. This evaluation board/kit does not fall within the scope of the European Union directives regarding electromagnetic compatibility, restricted substances (RoHS), recycling (WEEE), FCC, CE or UL, and therefore may not meet the technical requirements of these directives, or other related regulations.

If this evaluation board/kit does not meet the specifications indicated in the Technical Manual, the board/kit may be returned within 30 days from the date of delivery for a full refund. THE FOREGOING WARRANTY IS THE EXCLUSIVE WARRANTY MADE BY THE SELLER TO BUYER AND IS IN LIEU OF ALL OTHER WARRANTIES, EXPRESSED, IMPLIED, OR STATUTORY, INCLUDING ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE. EXCEPT TO THE EXTENT OF THIS INDEMNITY, NEITHER PARTY SHALL BE LIABLE TO THE OTHER FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES.

The user assumes all responsibility and liability for proper and safe handling of the goods. Further, the user indemnifies GaN Systems from all claims arising from the handling or use of the goods. Due to the open construction of the product, it is the user's responsibility to take any and all appropriate precautions with regard to electrostatic discharge.

No License is granted under any patent right or other intellectual property right of GaN Systems whatsoever. GaN Systems assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or any other intellectual property rights of any kind.

GaN Systems currently services a variety of customers for products around the world, and therefore this transaction **is not exclusive**.

**Please read the Technical Manual and, specifically, the Warnings and Restrictions notice in the Technical Manual prior to handling the product.** Persons handling the product(s) must have electronics training and observe good engineering practice standards.

This notice contains important safety information about temperatures and voltages. For further safety concerns, please contact a GaN Systems' application engineer.