# 16-Channel Serial to Parallel Converter with High Voltage Backplane Driver and Push-Pull Outputs

#### **Features**

- ► HVCMOS® technology

- Output voltage up to +200V

- ► Shift register speed 500kHz @ V<sub>DD</sub> = 2.0V

- 16 high voltage outputs

- ► High voltage backplane driver

- CMOS input levels

#### **Applications**

- Multiple segment EL display

- Piezoelectric transducer driver

- Braille driver

#### **General Description**

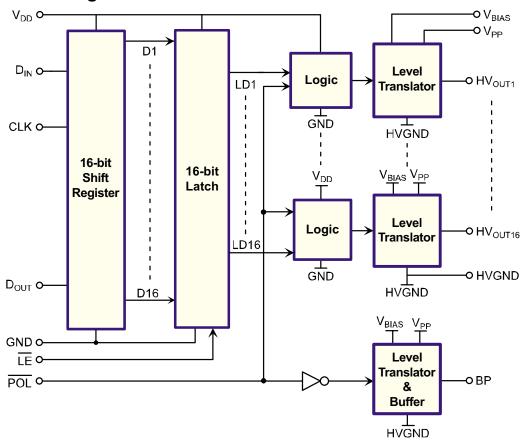

The HV509 is a 200V, 16-channel serial to parallel converter. The high voltage outputs and the backplane driver are designed to source and sink ±1.0mA.

The high voltage outputs are controlled by a 16-bit serial shift register, followed by a 16-bit latch. Data is shifted through the shift registers during the low to high clock transition. A data output buffer is provided for cascading multiple devices. Data is transferred to the 16-bit latch when a logic level low is applied to the  $\overline{\text{LE}}$  input. Data is stored in the latch when  $\overline{\text{LE}}$  is high. Output states are controlled by the data in the latch and by the  $\overline{\text{POL}}$  pin.

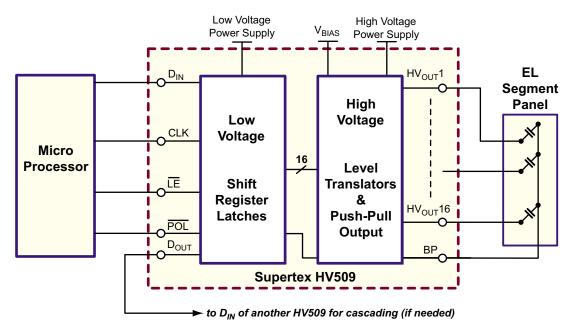

## **Typical Application Circuit**

## **Ordering Information**

| •      |                     |

|--------|---------------------|

| Device | Package Option      |

|        | 32-Lead QFN         |

|        | 5.00x5.00mm body    |

|        | 1.00mm height (max) |

|        | 0.50mm pitch        |

| HV509  | HV509K6-G           |

|        |                     |

-G indicates package is RoHS compliant ('Green')

## **Absolute Maximum Ratings**

| Parameter                                                | Value                           |

|----------------------------------------------------------|---------------------------------|

| Logic supply, V <sub>DD</sub>                            | -0.5V to 7.0V                   |

| High voltage supply, V <sub>PP</sub>                     | 215V                            |

| Translator supply voltage, $V_{\scriptscriptstyle BIAS}$ | -0.5V to 7.0V                   |

| Logic input levels                                       | -0.5V to V <sub>DD</sub> + 0.5V |

| Operating junction temperature                           | -40°C to +125°C                 |

| Storage temperature range                                | -65°C to +150°C                 |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. Continuous operation of the device at the absolute rating level may affect device reliability. All voltages are referenced to device ground.

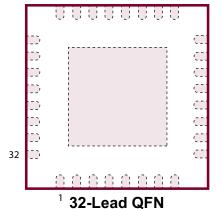

## **Pin Configuration**

(top view)

Pads are at the bottom of the package. Exposed heat slug is at  $V_{PP}$  potential.

## **Product Marking**

L = Lot Number

YY = Year Sealed

WW = Week Sealed

A = Assembler ID

C = Country of Origin

\_\_\_\_ = "Green" Packaging

32-Lead QFN (K6)

## **Operating Supply Voltages and Conditions**

| Sym               | Parameter                       | Min                | Тур | Max                | Units | Conditions |

|-------------------|---------------------------------|--------------------|-----|--------------------|-------|------------|

| V <sub>DD</sub>   | Logic supply voltage            | 2.0                | 3.0 | 5.5                | V     |            |

| V <sub>BIAS</sub> | Level translator supply voltage | 2.6                | -   | 6.6                | V     |            |

| V <sub>PP</sub>   | Positive high voltage supply    | 50                 | -   | 200                | V     |            |

| V <sub>IH</sub>   | High-level input voltage        | 0.9V <sub>DD</sub> | -   | V <sub>DD</sub>    | V     |            |

| V <sub>IL</sub>   | Low-level input voltage         | 0                  | -   | 0.1V <sub>DD</sub> | V     |            |

| T <sub>A</sub>    | Operating temperature           | 0                  | -   | +70                | °C    |            |

#### Notes:

- 1. External ground noise reduction circuit will be provided by design upon characterization.

- 2. Power-up sequence should be the following\*:

- Apply ground

- 2. Apply V<sub>DD</sub>

- 3. Set all inputs (D<sub>IN</sub>, CLK, LE, POL) to a known state

- 4. Apply  $V_{\text{BIAS}}$

- 5. Apply V<sub>PP</sub>

- 3. Power-down sequence should be the reverse of the above.

\*This power up sequence requires an external high voltage diode between VDD and VPP. Without the diode, power up VPP to a VDD level first to bias the silicon substrate. After all other signals are powered, finish raising the  $V_{pp}$  to its final level.

## DC Electrical Characteristics (Over operating supply voltages and temperature, unless otherwise noted)

| Sym                | Parameter                                |                        | Min                    | Тур | Max | Units | Conditions                                                                                                 |

|--------------------|------------------------------------------|------------------------|------------------------|-----|-----|-------|------------------------------------------------------------------------------------------------------------|

| I <sub>DD</sub>    | V <sub>DD</sub> supply current           |                        | -                      | -   | 1.0 | mA    | f <sub>CLK</sub> = 500kHz                                                                                  |

| I <sub>DDQ</sub>   | Quiescent V <sub>DD</sub> supply         | current                | -                      | -   | 10  | μA    | All logic inputs = V <sub>DD</sub> or 0V                                                                   |

| I <sub>BIAS</sub>  | V <sub>BIAS</sub> supply current         |                        | -                      | -   | 100 | μA    | All HV <sub>OUTS</sub> switching at 1kHz.<br>Peak I <sub>BIAS</sub> = 200mA with all<br>channels switching |

| I <sub>BIASQ</sub> | Quiescent V <sub>BIAS</sub> curre        | nt                     | -                      | -   | 10  | μA    | No HV <sub>OUT</sub> switching                                                                             |

| l <sub>PPQ</sub>   | Quiescent V <sub>PP</sub> supply current |                        | -                      | -   | 100 | μA    | V <sub>PP</sub> = 200V, outputs are static                                                                 |

| I <sub>IH</sub>    | High-level logic input current           |                        | -                      | -   | 10  | μA    | $V_{IH} = V_{DD}$                                                                                          |

| I                  | Low-level logic input current            |                        | -                      | -   | -10 | μA    | V <sub>IL</sub> = 0V                                                                                       |

|                    | High level output                        | HV <sub>OUT</sub> & BP | V <sub>PP</sub> - 12V  | -   | -   | V     | $IHV_{OUT} = -1.0 \text{mA}, V_{PP} = +200 \text{V}$                                                       |

| V <sub>OH</sub>    |                                          |                        | V <sub>PP</sub> - 12V  |     | -   | V     | IHV <sub>OUT</sub> = -1.0mA, V <sub>PP</sub> = +50V                                                        |

|                    |                                          | D <sub>OUT</sub>       | V <sub>DD</sub> - 1.0V | -   | -   | V     | ID <sub>OUT</sub> = -1.0mA                                                                                 |

| V <sub>OI</sub>    | V <sub>oL</sub> Low level output         | HV <sub>OUT</sub> & BP | -                      | -   | 12  | V     | $IHV_{OUT} = 1.0 \text{mA}, V_{BIAS} = 5.4 \text{V}, V_{PP} = +50 \text{ to } +200 \text{V}$               |

|                    |                                          | D <sub>OUT</sub>       | -                      | -   | 1.0 | V     | ID <sub>OUT</sub> = 1.0mA                                                                                  |

| C <sub>DIN</sub>   | Logic input capacitance                  |                        | -                      | -   | 10  | pF    |                                                                                                            |

| C <sub>DOUT</sub>  | Logic output capacitance                 |                        | -                      | -   | 10  | pF    |                                                                                                            |

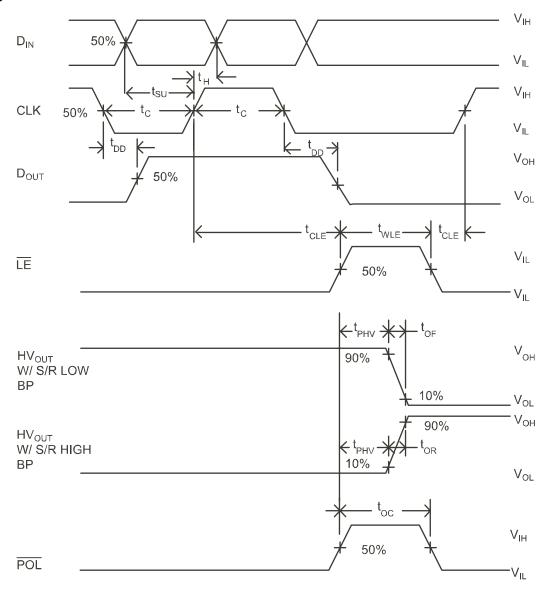

## AC Electrical Characteristics (Over operating supply voltages and temperature, unless otherwise noted)

| Sym              | Parameter                                                            | Min                                                 | Тур | Max | Units | Conditions                                                                                           |  |

|------------------|----------------------------------------------------------------------|-----------------------------------------------------|-----|-----|-------|------------------------------------------------------------------------------------------------------|--|

| f <sub>CLK</sub> | Clock frequency                                                      | 0                                                   | -   | 500 | kHz   |                                                                                                      |  |

| t <sub>c</sub>   | Clock high / low pulse width                                         | 1.0                                                 | -   | -   | μs    |                                                                                                      |  |

| t <sub>su</sub>  | Data setup time before clock rises                                   | 50                                                  | -   | -   | ns    |                                                                                                      |  |

| t <sub>H</sub>   | Data hold time after clock rises                                     | 50                                                  | -   | -   | ns    |                                                                                                      |  |

| t <sub>CLE</sub> | LE from CLK setup time                                               | 15                                                  | -   | -   | ns    |                                                                                                      |  |

| t <sub>WLE</sub> | LE pulse width                                                       | 100                                                 | -   | -   | ns    |                                                                                                      |  |

| t <sub>DD</sub>  | Clock negative edge to D <sub>OUT</sub> delay                        | -                                                   | -   | 150 | ns    | $C_{\text{LDOUT}}$ = 50pF,<br>( $C_{\text{LDOUT}}$ includes $C_{\text{DIN}}$ and $C_{\text{DOUT}}$ ) |  |

| t <sub>PHV</sub> | Delay time from inputs for HV <sub>OUT</sub> / BP to start rise/fall | -                                                   | -   | 500 | ns    | V <sub>PP</sub> = 200V, V <sub>BIAS</sub> = 5.4V                                                     |  |

| t <sub>or</sub>  | HV <sub>OUTPUT</sub> / BP rise time                                  | -                                                   | -   | 300 | μs    | C <sub>L</sub> = 1500pF, V <sub>PP</sub> = 200V                                                      |  |

| t <sub>OF</sub>  | HV <sub>OUTPUT</sub> / BP fall time                                  | -                                                   | -   | 300 | μs    | $C_L = 1500 pF, V_{BIAS} = 5.4 V,$<br>$V_{PP} = 200 V$                                               |  |

| t <sub>oc</sub>  | Width of POL pulses                                                  | t <sub>PHV</sub> + t <sub>OR</sub> /t <sub>OF</sub> | -   | -   | μs    |                                                                                                      |  |

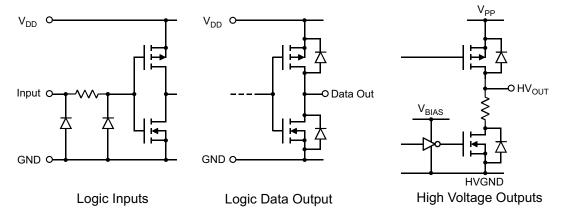

## **Input and Output Equivalent Circuits**

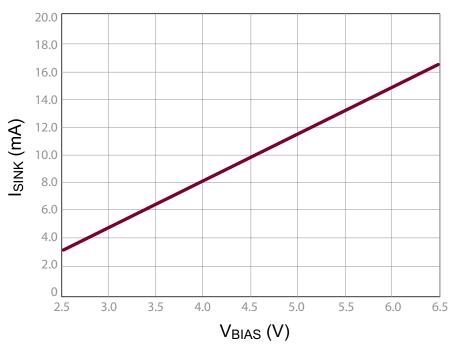

## **V**<sub>BIAS</sub> SUPPLY

The  $V_{BIAS}$  supply operates from 2.6V to 6.6V. It is the gate drive voltage for all of the output N-channel MOSFETs. This allows the output peak current sink to be set by varying the  $V_{BIAS}$  voltage. A higher  $V_{BIAS}$  voltage will increase the current sinking capability.

If large peak currents are not required,  $V_{\rm DD}$  and  $V_{\rm BIAS}$  can be connected to the same power supply, provided they are both within the operating range. The operating  $V_{\rm DD}$  range is 2.0V to 5.5V. A plot showing the typical characteristics of  $I_{\rm SINK}$  vs  $V_{\rm RIAS}$  is shown below.

# Typical HV<sub>OUT</sub> $I_{SINK}$ vs $V_{BIAS}$ ( $V_{PP} = 200V$ , $C_{LOAD} = 1nF$ )

## **Switching Waveforms**

## **Functional Block Diagram**

## **Function Table**

|                       | Inputs          |     |    |     | Outputs            |                     |    |                  |

|-----------------------|-----------------|-----|----|-----|--------------------|---------------------|----|------------------|

| Function              | D <sub>IN</sub> | CLK | LE | POL | Shift Reg<br>1 216 | HV Outputs<br>1 216 | ВР | D <sub>out</sub> |

| Load S/R              | H OR L          | 1   | Н  | Х   | HorL ••            | • ••                | Х  | •                |

| Transfer data in      | Х               | L   | L  | Н   | * **               | * **                | L  | •                |

| latch                 | Х               | L   | L  | L   | * **               | * **<br>(b)         | Н  | •                |

|                       | Х               | Х   | Н  | Н   | • ••               | • ••                | L  | •                |

| Store data in latches | Х               | X   | Н  | L   | • ••               | • ••<br>(b)         | Н  | •                |

| Transparent mode      | L               | 1   | L  | Н   | L ••               | L ••                | L  | •                |

|                       | Н               | 1   | L  | Н   | Н ••               | Н ••                | L  | •                |

| Invert mode           | Х               | Х   | Н  | L   | • ••               | • ••<br>(b)         | Н  | x                |

|                       | Х               | Х   | Н  | Н   | • ••               | • ••                | L  | Х                |

#### Notes:

- H = high level, L = low level, X = irrelevant, ↑ = low-to-high transition\_

- = dependent on previous stage's state before the last CLK or last LE low

- \* = data at the last CLK ↑

- (b) = bar over all symbols

# **Pin Description**

| Pin # | Function             | Description                   |

|-------|----------------------|-------------------------------|

| 1     | HV <sub>OUT</sub> 12 | High voltage push-pull output |

| 2     | HV <sub>OUT</sub> 11 | High voltage push-pull output |

| 3     | HV <sub>OUT</sub> 10 | High voltage push-pull output |

| 4     | HV <sub>ouT</sub> 9  | High voltage push-pull output |

| 5     | HV <sub>out</sub> 8  | High voltage push-pull output |

| 6     | HV <sub>out</sub> 7  | High voltage push-pull output |

| 7     | HV <sub>OUT</sub> 6  | High voltage push-pull output |

| 8     | HV <sub>out</sub> 5  | High voltage push-pull output |

| 9     | HV <sub>OUT</sub> 4  | High voltage push-pull output |

| 10    | HV <sub>OUT</sub> 3  | High voltage push-pull output |

| 11    | HV <sub>OUT</sub> 2  | High voltage push-pull output |

| 12    | HV <sub>out</sub> 1  | High voltage push-pull output |

| 13    | NC                   | No connect                    |

| 14    | VPP                  | High voltage supply           |

| 15    | GND                  | Logic ground                  |

| 16    | NC                   | No connect                    |

| 17    | DIN                  | Data in                       |

| 18    | NC                   | No connect                    |

| 19    | CLK                  | Clock input logic             |

| 20    | VDD                  | Logic supply voltage          |

| 21    | POL                  | Polarity bar input logic      |

| 22    | ĪĒ                   | Latch enable bar input logic  |

| 23    | NC                   | No connect                    |

| 24    | DOUT                 | Data out                      |

| 25    | NC                   | No connect                    |

| 26    | VBIAS                | Level translator bias voltage |

| 27    | HVGND                | High voltage ground           |

| 28    | BP                   | High voltage backplane output |

| 29    | HV <sub>out</sub> 16 | High voltage push-pull output |

| 30    | HV <sub>out</sub> 15 | High voltage push-pull output |

| 31    | HV <sub>out</sub> 14 | High voltage push-pull output |

| 32    | HV <sub>OUT</sub> 13 | High voltage push-pull output |