## **Product Highlights**

- Active Burst Mode to reach the lowest Standby Power Requirements < 100mW

- Adjustable Blanking Window for High Load Jumps to increase Reliability

- Frequency Jittering for Low EMI

- Pb-free lead plating, RoHS compliant

#### **Features**

- 650V Avalanche Rugged CoolMOS™ with built in switchable Startup Cell

- Active Burst Mode for lowest Standby Power

@ light load controlled by Feedback Signal

- Fast Load Jump Response in Active Burst Mode

- 67 kHz fixed Switching Frequency

- Auto Restart Mode for Over temperature Detection

- Auto Restart Mode for Overvoltage Detection

- Auto Restart Mode for Overload and Open Loop

- Auto Restart Mode for VCC Undervoltage

- User defined Soft Start

- Minimum of external Components required

- Max Duty Cycle 75%

- Overall Tolerance of Current Limiting < ±5%</li>

- Internal Leading Edge Blanking

- BiCMOS technology provides wide VCC Range

- Frequency jittering for Low EMI

# **Applications**

Adapter/Charger, Blue Ray/DVD player, Set-top Box, Digital Photo Frame

RoHS

Auxiliary power supply of Server, PC, Printer, TV, Home theater/Audio System, White Goods, etc

#### **Description**

The CoolSET<sup>™</sup>-F3 (Jitter version) meets the requirements for Off-Line Battery Adapters and low cost SMPS for the lower power range. By use of a BiCMOS technology a wide VCC range up to 26 V is provided. This covers the changes in the auxiliary supply voltage if a CV/CC regulation is implemented on the secondary side. Furthermore an Active Burst Mode is integrated to fullfill the lowest Standby Power Requirements <100 mW at no load and VIN = 270 V<sub>AC</sub>. As during Active Burst Mode the controller is always active there is an immediate response on load jumps possible without any black out in the SMPS. In Active Burst Mode the ripple of the output voltage can be reduced <1%. Furthermore Auto Restart Mode is entered in case of Overtemperature, VCC Overvoltage, Output Open loop or Overload and VCC Undervoltage. By means of the internal precise peak current limitation, the dimension of the transformer and the secondary diode can be lowered which leads to more cost efficiency.

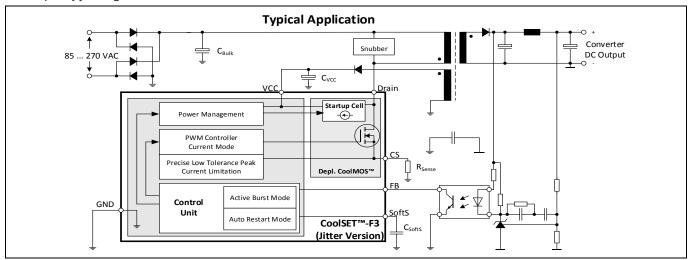

Figure 1 Typical application

| Туре        | Package   | Marking     | V <sub>DS</sub> | Fosc   | R <sub>DSon</sub> <sup>1</sup> | 230V <sub>AC</sub> ±15% <sup>2</sup> | 85-265 V <sub>AC</sub> <sup>2</sup> |

|-------------|-----------|-------------|-----------------|--------|--------------------------------|--------------------------------------|-------------------------------------|

| ICE3B0365JG | PG-DSO-12 | ICE3B0365JG | 650 V           | 67 kHz | 6.45 Ω                         | 22 W                                 | 10 W                                |

| ICE3B0565JG | PG-DSO-12 | ICE3B0565JG | 650 V           | 67 kHz | 4.70 Ω                         | 25 W                                 | 12 W                                |

$<sup>^{1}</sup>$  typ at T=25°C

Datasheet www.infineon.com

$<sup>^2</sup>$  Calculated maximum input power rating at Ta=75°C, Tj=125°C and without copper area as heat sink

#### **Table of contents**

# **Table of contents**

| Table  | le of contents                       |    |

|--------|--------------------------------------|----|

| 1      | Pin Configuration and Functionality  |    |

| 2      | Representative Block Diagram         |    |

| 3      | Functional Description               |    |

| 3.1    | Introduction                         |    |

| 3.2    | Power Management                     |    |

| 3.3    | Startup Phase                        |    |

| 3.4    | PWM Section                          |    |

| 3.4.1  | Oscillator and Jittering             |    |

| 3.4.2  | PWM-Latch FF1                        |    |

| 3.4.3  | Gate Driver                          |    |

| 3.5    | Current Limiting                     |    |

| 3.5.1  | Leading Edge Blanking                | 10 |

| 3.5.2  | Propagation Delay Compensation       | 10 |

| 3.6    | Control Unit                         | 11 |

| 3.6.1  | Adjustable Blanking Window           | 12 |

| 3.6.2  | 2 Active Burst Mode                  | 12 |

| 3.6.2. | 2.1 Entering Active Burst Mode       | 13 |

| 3.6.2. | 2.2 Working in Active Burst Mode     | 13 |

| 3.6.2. | 0                                    |    |

| 3.6.3  |                                      |    |

| 3.6.3. |                                      |    |

| 3.6.3. | 3.2 Auto Restart Mode II             | 16 |

| 4      | Electrical Characteristics           | 17 |

| 4.1    | Absolute Maximum Ratings             | 17 |

| 4.2    | Operating Range                      | 18 |

| 4.3    | Characteristics                      | 18 |

| 4.3.1  | Supply Section                       | 18 |

| 4.3.2  | 2 Internal Voltage Reference         | 19 |

| 4.3.3  |                                      |    |

| 4.3.4  |                                      |    |

| 4.3.5  | •                                    |    |

| 4.3.6  | G CoolMOS™ Section                   | 21 |

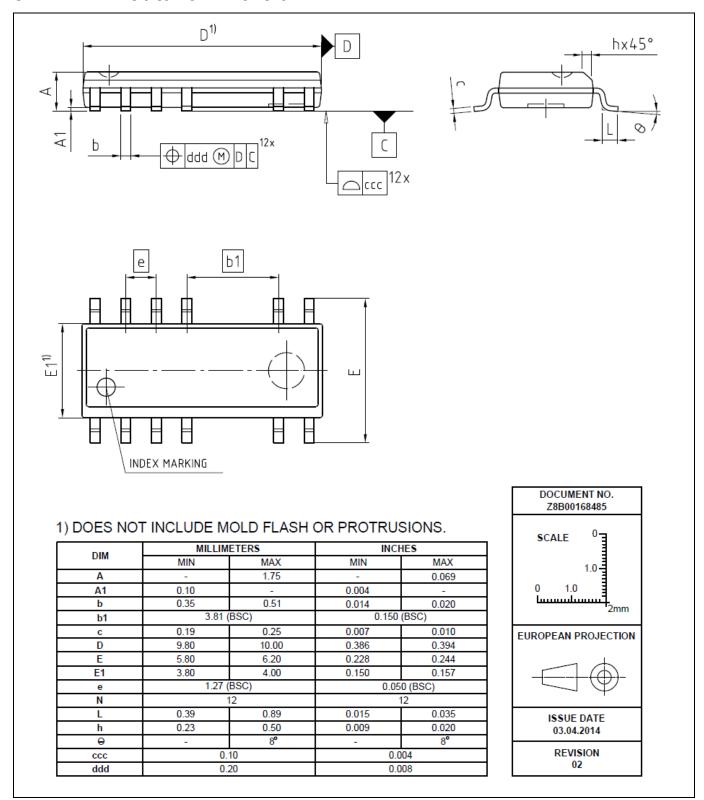

| 5      | Outline Dimension                    | 22 |

| 6      | Marking                              | 23 |

| 7      | Schematic for recommended PCB layout | 24 |

| Pavid  | ision history                        | 21 |

V 2.2

# **Pin Configuration and Functionality**

# 1 Pin Configuration and Functionality

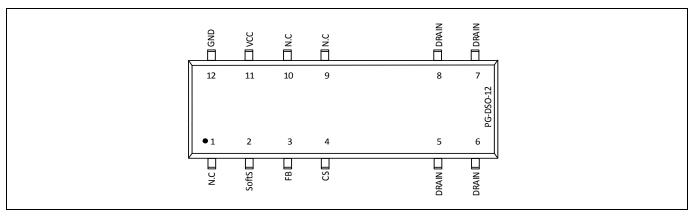

Table 1 Pin definitions and functions

| Pin        | Symbol | Function                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 9, 10   | N.C    | Not Connected                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2          | SoftS  | Soft-Start (Soft Start, Auto Restart & Frequency Jittering Control)                                                                                                                                                                                                                                                                                                                                                                                    |

|            |        | The SoftS pin combines the function of Soft Start during Start Up and error detection for Auto Restart Mode. These functions are implemented and can be adjusted by means of an external capacitor at SoftS to ground. This capacitor also provides an adjustable blanking window for high load jumps, before the IC enters into Auto Restart Mode. Furthermore this pin is also used to control the period of frequency jittering during normal load. |

| 3          | FB     | FB (Feedback)                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|            |        | The information about the regulation is provided by the FB Pin to the internal                                                                                                                                                                                                                                                                                                                                                                         |

|            |        | Protection Unit and to the internal PWM-Comparator to control the duty cycle. The FB-Signal controls in case of light load the Active Burst Mode of the controller.                                                                                                                                                                                                                                                                                    |

| 4          | CS     | CS (Current Sense)                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|            |        | The Current Sense pin senses the voltage developed on the series resistor inserted in the source of the integrated Depl-CoolMOS™. If CS reaches the internal threshold of the Current Limit Comparator, the Driver output is immediately switched off. Furthermore the current information is provided for the PWM-Comparator to realize the Current Mode.                                                                                             |

| 5, 6, 7, 8 | Drain  | Drain (Drain of 650 V¹ integrated CoolMOS™)                                                                                                                                                                                                                                                                                                                                                                                                            |

|            |        | Drain pins are connected to the Drain of integrated CoolMOS™.                                                                                                                                                                                                                                                                                                                                                                                          |

| 11         | VCC    | VCC (Power supply)                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|            |        | The VCC pin is the positive supply of the IC. The operating range is between 10.3 V and 26 V.                                                                                                                                                                                                                                                                                                                                                          |

| 12         | GND    | GND (Ground)                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|            |        | This is the common ground of the controller.                                                                                                                                                                                                                                                                                                                                                                                                           |

Figure 2 Pin configuration PG-DSO-12(top view)

V 2.2

# Representative Block Diagram

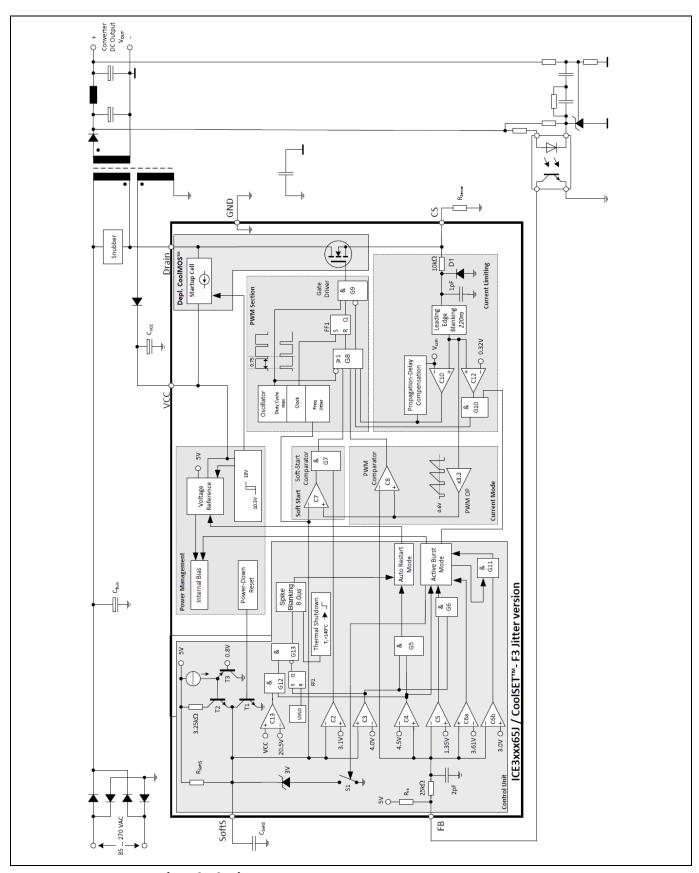

# 2 Representative Block Diagram

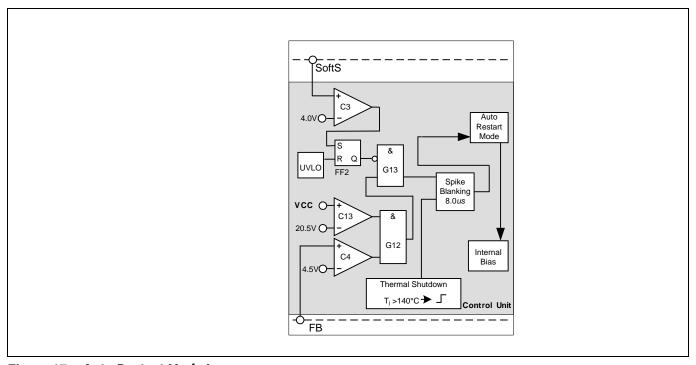

Figure 3 Representative Block Diagram

#### **Functional Description**

# **3** Functional Description

All values which are used in the functional description are typical values. For calculating the worst cases the min/max values which can be found in section 4 Electrical Characteristics have to be considered.

### 3.1 Introduction

CoolSET™-F3 Jitter version is the further development of the CoolSET™-F2 to meet the requirements for the lowest Standby Power at minimum load and no load conditions. A new fully integrated Standby Power concept is implemented into the IC in order to keep the application design easy. Compared to CoolSET™-F2 no further external parts are needed to achieve the lowest Standby Power. An intelligent Active Burst Mode is used for this Standby Mode. After entering this mode there is still a full control of the power conversion by the secondary side via the same optocoupler that is used for the normal PWM control. The response on load jumps is optimized. The voltage ripple on Vout is minimized. Vout is further on well controlled in this mode.

The usually external connected RC-filter in the feedback line after the optocoupler is integrated in the IC to reduce the external part count.

Furthermore a high voltage Startup Cell is integrated into the IC which is switched off once the Undervoltage Lockout on-threshold of 18V is exceeded. This Startup Cell is part of the integrated Depl. CoolMOS™. The external startup resistor is no longer necessary as this Startup Cell is connected to the Drain. Power losses are therefore reduced. This increases the efficiency under light load conditions drastically.

The Soft-Start capacitor is also used for providing an adjustable blanking window for high load jumps. During this time window the overload detection is disabled. With this concept no further external components are necessary to adjust the blanking window.

An Auto Restart Mode is implemented in the IC to reduce the average power conversion to in the event of malfunction or unsafe operating condition in the SMPS system. This feature increases the system's robustness and safety which would otherwise lead to a destruction of the SMPS. Once the malfunction is removed, normal operation is automatically initiated after the next Start Up Phase.

The internal precise peak current limitation reduces the costs for the transformer and the secondary diode. The influence of the change in the input voltage on the power limitation can be avoided together with the integrated Propagation Delay Compensation. Therefore the maximum power is nearly independent on the input voltage which is required for wide range SMPS. There is no need for an extra over-sizing of the SMPS, e.g. the transformer or the secondary diode.

#### **Functional Description**

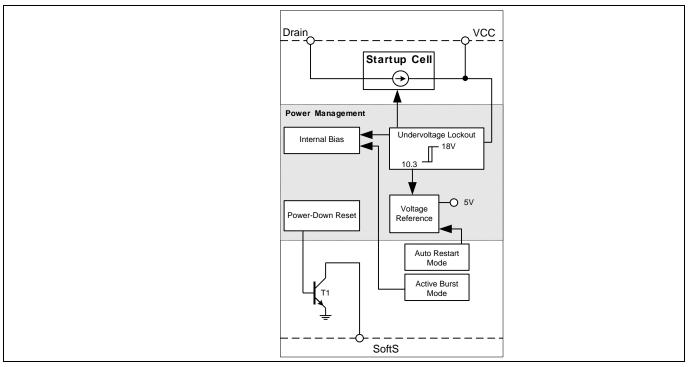

#### 3.2 Power Management

Figure 4 Power Management

The Undervoltage Lockout monitors the external supply voltage  $V_{VCC}$ . When the SMPS is plugged to the main line the internal Startup Cell is biased and starts to charge the external capacitor  $C_{VCC}$  which is connected to the VCC pin. The VCC charge current that is provided by the Startup Cell from the Drain pin is 1.05 mA. When  $V_{VCC}$  exceeds the on-threshold  $V_{CCO}=18$  V, bias circuit is switched on. Then the Startup Cell is switched off by the Undervoltage Lockout and therefore no power losses present due to the connection of the Startup Cell to the Drain voltage. To avoid uncontrolled ringing at switch-on a hysteresis is implemented. The switch-off of the controller can only take place after Active Mode was entered and  $V_{VCC}$  falls below 10.3V.

The maximum current consumption before the controller is activated is about 300 µA.

When  $V_{\text{VCC}}$  falls below the off-threshold  $V_{\text{CCoff}}$ =10.3 V the bias circuit is switched off and the Power Down reset let T1 discharging the soft-start capacitor  $C_{\text{SoftS}}$  at pin SoftS. Thus it is ensured that at every startup cycle the voltage ramp at pin SoftS starts at zero.

The bias circuit is switched off if Auto Restart Mode is entered. The current consumption is then reduced to  $300 \,\mu\text{A}$ .

Once the malfunction condition is removed, this block will then turn back on. The recovery from Auto Restart Mode does not require disconnecting the SMPS from the AC line.

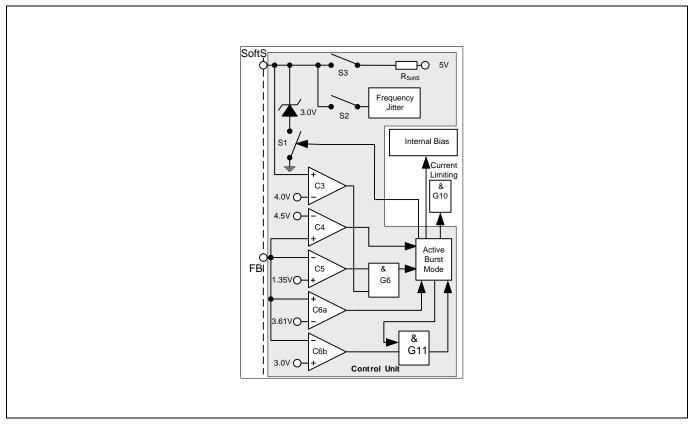

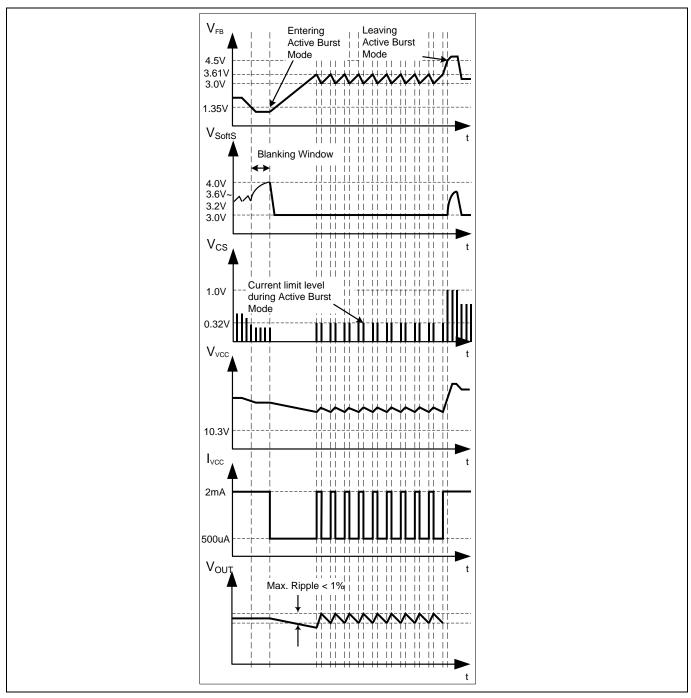

When Active Burst Mode is entered, some internal Bias is switched off in order to reduce the current consumption to about 500  $\mu$ A while keeping a comparator (which trigger if  $V_{FB}$  has exceeded 3.61 V) and the Soft Start capacitor clamped at 3.0 V as this is necessary in this mode.

#### **Functional Description**

## 3.3 Startup Phase

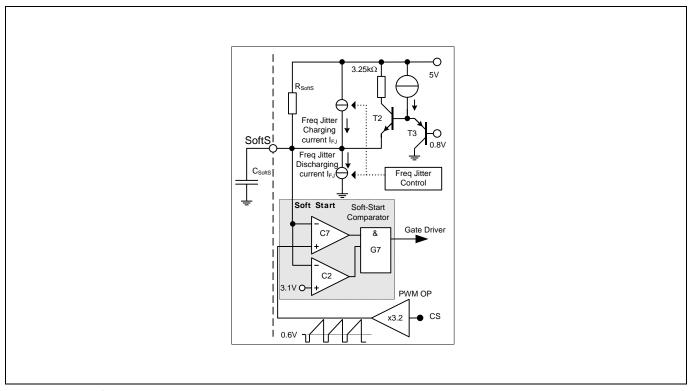

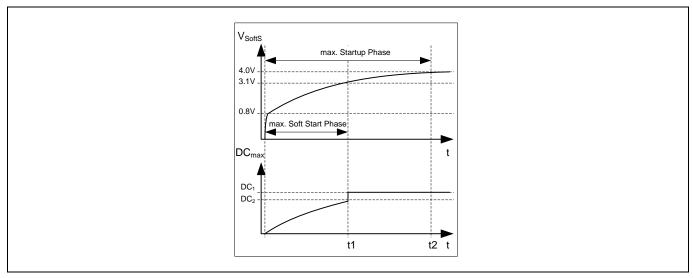

Figure 5 Soft Start

At the beginning of the Startup Phase, the IC provides a Soft Start duration whereby it controls the maximum primary current by means of a duty cycle limitation. A capacitor  $C_{\text{Softs}}$  in combination with the internal pull up resistor  $R_{\text{Softs}}$  determines the duty cycle until  $V_{\text{Softs}}$  exceeds 3.1 V.

When the Soft Start begins,  $C_{SoftS}$  is immediately charged up to approx. 0.8 V by T2. Therefore the Soft Start Phase takes place between 0.8 V and 3.1 V. Above  $V_{SoftS}$  = 3.1 V there is no longer duty cycle limitation  $DC_{max}$  which is controlled by comparator C7 since comparator C2 blocks the gate G7 (see Figure 5). This maximum charge current in the very first stage when  $V_{SoftS}$  is below 0.8 V, is limited to 1.5 mA.

Figure 6 Startup Phase

#### **Functional Description**

By means of this extra charge stage, there is no delay in the beginning of the Startup Phase when there is still no switching. Furthermore Soft Start is finished at 3.1 V to have faster the maximum power capability. The duty cycles  $DC_1$  and  $DC_2$  are depending on the mains and the primary inductance of the transformer. The limitation of the primary current by  $DC_2$  is related to  $V_{SoftS} = 3.1$  V. But  $DC_1$  is related to a maximum primary current which is limited by the internal Current Limiting with CS = 1 V. Therefore the maximum Startup Phase is divided into a Soft Start Phase until t1 and a phase from t1 until t2 where maximum power is provided if demanded by the FB signal.

#### 3.4 PWM Section

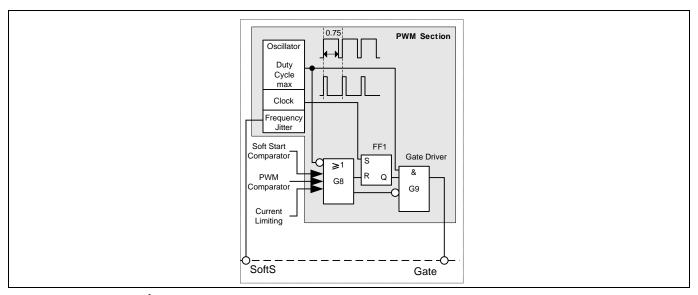

Figure 7 PWM Section

# 3.4.1 Oscillator and Jittering

The oscillator generates a fixed frequency with frequency jittering of  $\pm 4\%$  from the fixed frequency (which is  $\pm 2.7$  kHz from 67 kHz) at a jittering period  $T_{FJ}$ . The switching frequency of ICE3B0x65JG is  $f_{switch} = 67$  kHz.

A resistor, a capacitor and a current source and current sink which determine the frequency are integrated. The charging and discharging current of the implemented oscillator capacitor are internally trimmed, in order to achieve a very accurate switching frequency. The ratio of controlled charge to discharge current is adjusted to reach a maximum duty cycle limitation of  $D_{max}$ =0.75.

Once the Soft Start period is over and when the IC goes into normal mode, the Soft Start capacitor will be charged and discharged through internal current source, I<sub>FJ</sub> to generate a triangular waveform with a jittering period, T<sub>FJ</sub> which is externally adjustable by the Soft Start capacitor, C<sub>Softs</sub> (See Figure 5).

$$T_{FJ} = k_{FJ} * C_{SoftS}$$

where  $k_{FJ}$  is a constant = 4 ms/ $\mu$ F

eg.

$$T_{FJ} = 4$$

ms if  $C_{SoftS} = 1 \mu F$

#### **Functional Description**

#### 3.4.2 PWM-Latch FF1

The oscillator clock output provides a set pulse to the PWM-Latch when initiating the internal CoolMOS™ conduction. After setting the PWM-Latch can be reset by the PWM comparator, the Soft Start comparator or the Current-Limit comparator. In case of resetting the driver is shut down immediately.

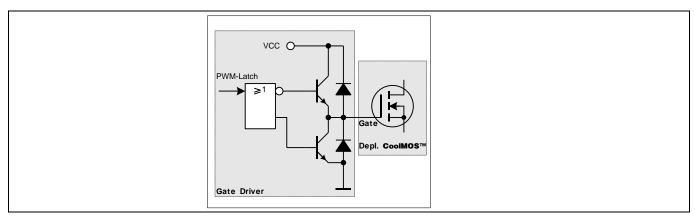

#### 3.4.3 Gate Driver

The Gate Driver is a fast totem pole gate drive which is designed to avoid cross conduction currents.

The Gate Driver is active low at voltages below the undervoltage lockout threshold V<sub>VCCoff</sub>.

Figure 8 Gate Driver

# 3.5 Current Limiting

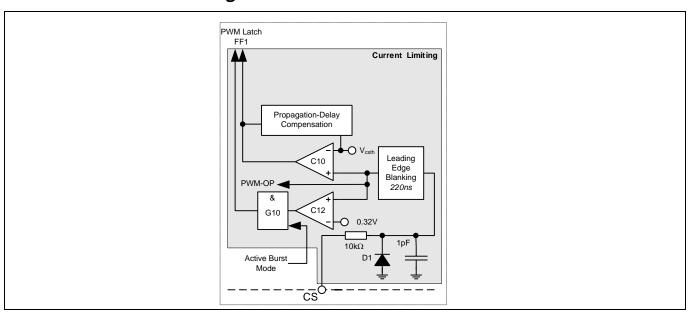

Figure 9 Current Limiting

There is a cycle by cycle Current Limiting realized by the Current-Limit comparator C10 to provide an overcurrent detection. The source current of the integrated Depl. CoolMOS<sup>TM</sup> is sensed via an external sense resistor  $R_{Sense}$ . By means of  $R_{Sense}$  the source current is transformed to a sense voltage  $V_{Sense}$  which is fed into the pin CS. If the voltage  $V_{Sense}$  exceeds the internal threshold voltage  $V_{csth}$  the comparator C10 immediately turns off the gate drive by resetting the PWM Latch FF1. A Propagation Delay Compensation is added to support the immediate shut down without delay of the integrated internal CoolMOS<sup>TM</sup> in case of

#### **Functional Description**

Current Limiting. The influence of the AC input voltage on the maximum output power can thereby be avoided.

To prevent the Current Limiting from distortions caused by leading edge spikes a Leading Edge Blanking is integrated in the current sense path for the comparators C10, C12 and the PWM-OP.

The output of comparator C12 is activated by the Gate G10 if Active Burst Mode is entered. Once activated the current limiting is thereby reduced to 0.32 V. This voltage level determines the power level when the Active Burst Mode is left if there is a higher power demand.

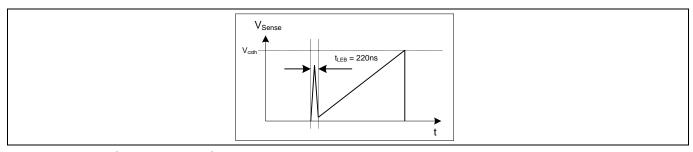

## 3.5.1 Leading Edge Blanking

Figure 10 Leading Edge Blanking

Each time when the integrated internal CoolMOS™ is switched on a leading edge spike is generated due to the primary-side capacitances and secondary-side rectifier reverse recovery time. This spike can cause the gate drive to switch off unintentionally. To avoid a premature termination of the switching pulse, this spike is blanked out with a time constant of t<sub>LEB</sub> = 220 ns. During this time, the gate drive will not be switched off.

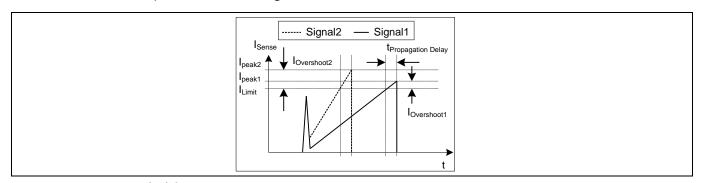

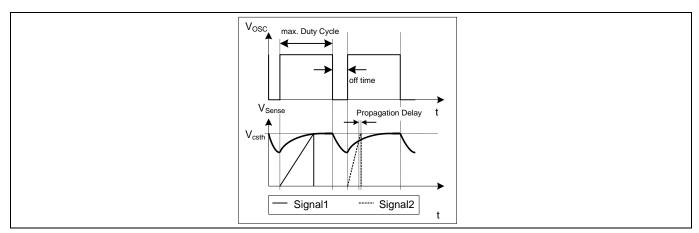

# 3.5.2 Propagation Delay Compensation

In case of overcurrent detection, the switch-off of the integrated internal CoolMOS<sup>™</sup> is delayed due to the propagation delay of the circuit. This delay causes an overshoot of the peak current I<sub>peak</sub> which depends on the ratio of dI/dt of the peak current (see Figure 10).

Figure 11 Current Limiting

The overshoot of Signal2 is bigger than of Signal1 due to the steeper rising waveform. This change in the slope is depending on the AC input voltage. Propagation Delay Compensation is integrated to limit the overshoot dependency on dI/dt of the rising primary current. That means the propagation delay time between exceeding the current sense threshold  $V_{csth}$  and the switch off of the integrated internal  $CoolMOS^{TM}$  is compensated over temperature within a wide range.

#### **Functional Description**

Current Limiting is now possible in a very accurate way.

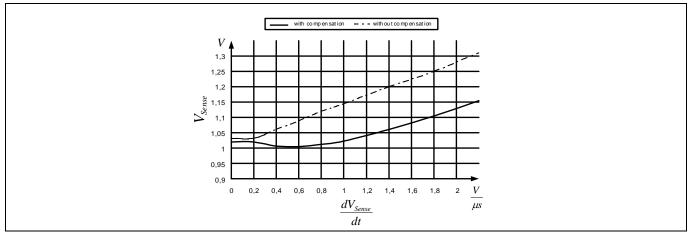

E.g.  $I_{peak} = 0.5$  A with  $R_{Sense} = 2 \Omega$ . Without Propagation Delay Compensation the current sense threshold is set to a static voltage level  $V_{csth}=1$  V. A current ramp of dI/dt=0.4 A/ $\mu$ s, that means  $dV_{Sense}/dt=0.8$  V/ $\mu$ s, and a propagation delay time of i.e.  $t_{Propagation\ Delay}=180$  ns leads then to an Ipeak overshoot of 14.4%. By means of propagation delay compensation the overshoot is only about 2% (see Figure 12).

Figure 12 Overcurrent Shutdown

The Propagation Delay Compensation is realized by means of a dynamic threshold voltage V<sub>csth</sub> (see Figure 13). In case of a steeper slope the switch off of the driver is earlier to compensate the delay.

Figure 13 Dynamic Voltage Threshold Vcsth

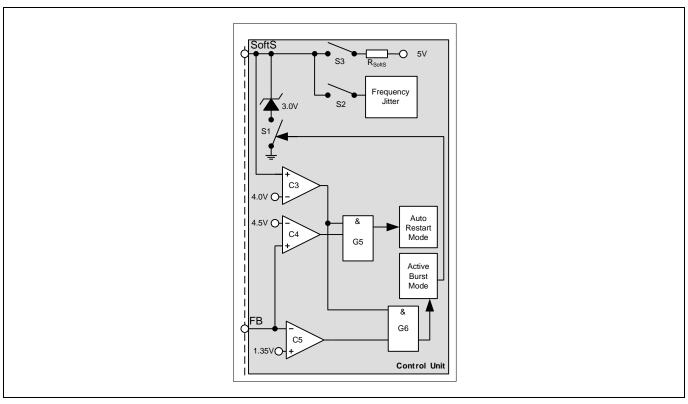

#### 3.6 Control Unit

The Control Unit contains the functions for Active Burst Mode and Auto Restart Mode. The Active Burst Mode and the Auto Restart Mode are combined with an Adjustable Blanking Window which is depending on the external Soft Start capacitor. By means of this Adjustable Blanking Window, the IC avoids entering into these two modes accidentally. Furthermore it also provides a certain time whereby the overload detection is delayed. This delay is useful for applications which normally works with a low current and occasionally require a short duration of high current.

#### **Functional Description**

### 3.6.1 Adjustable Blanking Window

Figure 14 Adjustable Blanking Window

$V_{SoftS}$  swings between 3.2 V and 3.6 V after the SMPS is settled and S2 is on while S3 is off, this is due to the frequency jittering function that is making use of the Soft Start pin. If overload occurs  $V_{FB}$  is exceeding 4.5 V. Auto Restart Mode can't be entered as the gate G5 is still blocked by the comparator C3. But after  $V_{FB}$  has exceeded 4.5 V the switch S2 is opened and S3 is closed. The external Soft Start capacitor can now be charged further by the integrated pull up resistor  $R_{SoftS}$  via switch S3. The comparator C3 releases the gates G5 and G6 once  $V_{SoftS}$  has exceeded 4.0 V. Therefore there is no entering of Auto Restart Mode possible during this charging time of the external capacitor  $C_{SoftS}$ . The same procedure happens to the external Soft Start capacitor if a low load condition is detected by comparator C5 when  $V_{FB}$  is falling below 1.35 V. Only after  $V_{SoftS}$  has exceeded 4.0 V and  $V_{FB}$  is still below 1.35 V Active Burst Mode is entered.

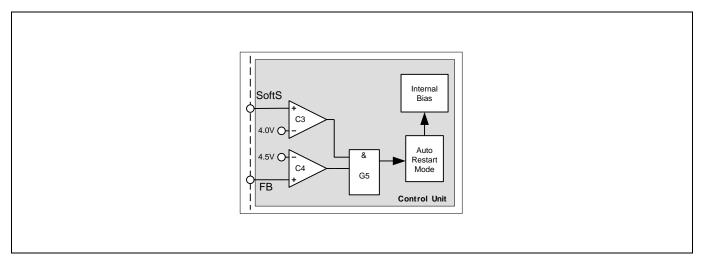

#### 3.6.2 Active Burst Mode

The controller provides Active Burst Mode for low load conditions at  $V_{OUT}$ . Active Burst Mode increases significantly the efficiency at light load conditions while supporting a low ripple on  $V_{OUT}$  and fast response on load jumps. During Active Burst Mode which is controlled only by the FB signal the IC is always active and can therefore immediately response on fast changes at the FB signal. The Startup Cell is kept switched off to avoid increased power losses for the self supply.

#### **Functional Description**

Figure 15 Active Burst Mode

The Active Burst Mode is located in the Control Unit. Figure 15 shows the related components.

## 3.6.2.1 Entering Active Burst Mode

The FB signal is always observed by the comparator C5 if the voltage level falls below 1.35 V. In that case the switch S1 and S2 is released which allow the capacitor  $C_{\text{softs}}$  to be charged via S3 starting from the swinging voltage level between 3.2 V and 3.6 V in normal operating mode. If  $V_{\text{softs}}$  exceeds 4.0 V the comparator C3 releases the gate G6 to enter the Active Burst Mode. The time window that is generated by combining the FB and SoftS signals with gate G6 avoids a sudden entering of the Active Burst Mode due to large load jumps. This time window can be adjusted by the external capacitor  $C_{\text{softs}}$ .

After entering Active Burst Mode a burst flag is set and the internal bias is switched off in order to reduce the current consumption of the IC down to approx.  $500 \,\mu\text{A}$ . Also, switch S1 is closed to clamp the Soft Start voltage to  $3.0 \,\text{V}$ . In this Off State Phase the IC is no longer self supplied so that therefore  $C_{VCC}$  has to provide the VCC current (see Figure 16). Furthermore gate G11 is then released to start the next burst cycle once  $V_{FB}$  has  $3.0 \,\text{V}$  exceeded.

It has to be ensured by the application that the VCC remains above the Undervoltage Lockout Level of 10.3 V to avoid that the Startup Cell is accidentally switched on. Otherwise power losses are significantly increased. The minimum VCC level during Active Burst Mode is depending on the load conditions and the application. The lowest VCC level is reached at no load conditions at V<sub>OUT</sub>.

# 3.6.2.2 Working in Active Burst Mode

After entering the Active Burst Mode the FB voltage rises as  $V_{OUT}$  starts to decrease due to the inactive PWM section. Comparator C6a observes the FB signal if the voltage level 3.6 V is exceeded. In that case the internal circuit is again activated by the internal Bias to start with switching. As now in Active Burst Mode

#### **Functional Description**

the gate G10 is released the current limit is only  $0.32\,V$  to reduce the conduction losses and to avoid audible noise. If the load at  $V_{OUT}$  is still below the starting level for the Active Burst Mode the FB signal decreases down to  $3.0\,V$ . At this level C6b deactivates again the internal circuit by switching off the internal Bias. The gate G11 is released as after entering Active Burst Mode the burst flag is set. If working in Active Burst Mode the FB voltage is changing like a saw tooth between  $3.0\,V$  and  $3.61\,V$  (see Figure 16).

### 3.6.2.3 Leaving Active Burst Mode

The FB voltage immediately increases if there is a high load jump. This is observed by comparator C4. As the current limit is ca. 32% during Active Burst Mode a certain load jump is needed that FB can exceed 4.5 V. At this time C4 resets the Active Burst Mode which also blocks C12 by the gate G10. Maximum current can now be provided to stabilize  $V_{\text{OUT}}$ .

Figure 16 Signals in Active Burst Mode

#### **Functional Description**

#### 3.6.3 Protection Modes

The IC provides several protection features that increase the SMPS system's robustness and safety. The following table shows the possible system failures and the corresponding protection modes.

Table 2 Protection Modes

| Protection function | <b>Protection Mode</b> |

|---------------------|------------------------|

| VCC Overvoltage     | Auto Restart Mode I    |

| Over temperature    | Auto Restart Mode I    |

| Over load           | Auto Restart Mode II   |

| Open Loop           | Auto Restart Mode II   |

| VCC Undervoltage    | Auto Restart Mode II   |

| Short Optocoupler   | Auto Restart Mode II   |

#### 3.6.3.1 Auto Restart Mode I

Figure 17 Auto Restart Mode I

The VCC voltage is observed by comparator C13 if 20.5 V is exceeded. The output of C13 is combined with both the output of C3 which checks for  $V_{SoftS} < 4.0 \text{ V}$  and the output of C4 which checks for  $V_{FB} > 4.5 \text{ V}$ . Therefore the overvoltage detection can only be active during Soft Start Phase ( $V_{SoftS} < 4.0 \text{ V}$ ) and when FB signal is outside the operating range > 4.5 V. This means any small voltage overshoots of  $V_{VCC}$  during normal operating cannot trigger the Auto Restart Mode I.

In Order to ensure system reliability and prevent any false activation, a blanking time is implemented before the IC can enter into the Auto Restart Mode I. The output of the VCC overvoltage detection is fed into a spike blanking with a time constant of  $8.0~\mu s$ .

The other fault detection which can result in the Auto Restart Mode I and has this 8.0  $\mu$ s blanking time is the Overtemperature detection. This block checks for a junction temperature of higher than 140°C for malfunction operation.

#### **Functional Description**

Once Auto Restart Mode is entered, the internal bias is switched off in order to reduce the current consumption of the IC as much as possible. In this mode, the average current consumption is only 300  $\mu$ A as the only working blocks are the reference block and the Undervoltage Lockout (UVLO) which controls the Startup Cell by switching on/off at  $V_{VCCon}/V_{VCCoff}$ .

As there is no longer a self supply by the auxiliary winding, VCC starts to drop. The UVLO switches on the integrated Startup Cell when VCC falls below 10.3 V. It will continue to charge VCC up to 18 V whereby it is switched off again and the IC enters into the Start Up Phase.

As long as all fault conditions have been removed, the IC will automatically power up as usual with switching cycle at the GATE output after Soft Start duration. Thus it is called Auto Restart Mode.

#### 3.6.3.2 Auto Restart Mode II

Figure 18 Auto Restart Mode II

In case of Overload or Open Loop, FB exceeds 4.5 V which will be observed by C4. At this time, the external Soft Start capacitor can now be charged further by the integrated pull up resistor RSoftS via switch S3 (see Figure 14). If V<sub>SoftS</sub> exceeds 4.0 V which is observed by C3, Auto Restart Mode II is entered as both inputs of the gate G5 are high.

This charging of the Soft Start capacitor from  $3.2 \text{ V} \sim 3.6 \text{ V}$  to 4.0 V defines a blanking window which prevents the system from entering into Auto Restart Mode II unintentionally during large load jumps. In this event, FB will rise close to 5.0 V for a short duration before the loop regulates with FB less than 4.5 V. This is the same blanking time window as for the Active Burst Mode and can therefore be adjusted by the external  $C_{\text{Softs}}$ .

In case of VCC undervoltage, i.e. VCC falls below 10.3 V, the IC will be turned off with the Startup Cell charging VCC as described earlier in this section. Once VCC is charged above 18 V, the IC will start a new startup cycle. The same procedure applies when the system is under Short Optocoupler fault condition, as it will lead to VCC undervoltage.

#### **Electrical Characteristics**

## 4 Electrical Characteristics

Note: All voltages are measured with respect to ground (Pin 12). The voltage levels are valid if other

ratings are not violated.

# 4.1 Absolute Maximum Ratings

Note: Absolute maximum ratings are defined as ratings, which when being exceeded may lead to

destruction of the integrated circuit. For the same reason make sure, that any capacitor that will be connected to pin 11 (VCC) is discharged before assembling the application circuit.  $T_{\sigma}$ =25°C

unless otherwise specified.

Table 3 Absolute Maximum Ratings

| Parameter  Drain Source Voltage                        |             | Symbol               | Limit V   | alues | Unit | Remarks                       |  |

|--------------------------------------------------------|-------------|----------------------|-----------|-------|------|-------------------------------|--|

|                                                        |             |                      | min. max. |       |      |                               |  |

|                                                        |             | V <sub>DS</sub>      | -         | 650   | V    | <i>T</i> <sub>j</sub> =110 °C |  |

| Pulse drain current, pulse width $t_{ m p}$ limited by | ICE3B0365JG | I <sub>D_Plus1</sub> | -         | 1.6   | А    |                               |  |

| <i>T</i> <sub>j</sub> =150 °C                          | ICE3B0565JG | I <sub>D_Plus2</sub> | -         | 2.3   | А    |                               |  |

| Avalanche energy, repetitive $t_{AR}$ limited by       | ICE3B0365JG | E <sub>AR1</sub>     | -         | 0.005 | mJ   |                               |  |

| max. <i>T</i> <sub>j</sub> =150 °C¹                    | ICE3B0565JG | E <sub>AR2</sub>     | -         | 0.01  | mJ   |                               |  |

| Avalanche current, repetitive $t_{AR}$ limited by      | ICE3B0365JG | I <sub>AR1</sub>     | -         | 0.3   | А    |                               |  |

| max. $T_j$ =150 °C <sup>1</sup>                        | ICE3B0565JG | I <sub>AR2</sub>     | -         | 0.5   | Α    |                               |  |

| VCC Supply Voltage                                     |             | V <sub>vcc</sub>     | -0.3      | 27    | ٧    |                               |  |

| FB Voltage                                             |             | V <sub>FB</sub>      | -0.3      | 5.0   | ٧    |                               |  |

| SoftS Voltage                                          |             | V <sub>SoftS</sub>   | -0.3      | 5.0   | V    |                               |  |

| CS Voltage                                             |             | V <sub>CS</sub>      | -0.3      | 5.0   | V    |                               |  |

| Junction Temperature                                   |             | Tj                   | -40       | 150   | °C   | Controller & CoolMOS™         |  |

| Storage Temperature                                    |             | Ts                   | -55       | 150   | °C   |                               |  |

| Thermal Resistance                                     |             | R <sub>thJA</sub>    | -         | 110   | K/W  | PG-DSO-16/12                  |  |

| (Junction–Ambient)                                     |             |                      |           |       |      |                               |  |

| ESD Capability                                         |             | $V_{ESD}$            | -         | 2     | kV   | Human body model <sup>2</sup> |  |

$<sup>^{1}</sup>$  Repetitive avalanche causes additional power losses that can be calculated as  $P_{AV}=E_{AR}{}^{\star}f$

$<sup>^2</sup>$  According to EIA/JESD22-A114-B (discharging a 100 pF capacitor through a 1.5 kΩ series resistor) Datasheet 17 of 26

#### **Electrical Characteristics**

# 4.2 Operating Range

Note: Within the operating range the IC operates as described in the functional description.

Table 4 Operating Range

| Parameter                          | Symbol                | Limit Va            | alues | Unit | Remarks                                                  |  |

|------------------------------------|-----------------------|---------------------|-------|------|----------------------------------------------------------|--|

|                                    |                       | min.                | max.  |      |                                                          |  |

| VCC Supply Voltage                 | $V_{ m vcc}$          | $V_{\text{VCCoff}}$ | 26    | V    |                                                          |  |

| Junction Temperature of Controller | $T_{jCon}$            | -25                 | 130   | °C   | Max value limited due to thermal shut down of controller |  |

| Junction Temperature of CoolMOS™   | $T_{\text{jCoolMOS}}$ | -25                 | 150   | °C   |                                                          |  |

## 4.3 Characteristics

# 4.3.1 Supply Section

Note:

The electrical characteristics involve the spread of values within the specified supply voltage and junction temperature range  $T_J$  from – 25 °C to 130 °C. Typical values represent the median values, which are related to 25 °C. If not otherwise stated, a supply voltage of  $V_{VCC}$  = 18 V is assumed.

Table 5 Supply Section

| Parameter                                              | Symbol                  | Limit | Values |      | Unit | <b>Test Condition</b>                                                    |  |

|--------------------------------------------------------|-------------------------|-------|--------|------|------|--------------------------------------------------------------------------|--|

|                                                        |                         | min.  | typ.   | max. |      |                                                                          |  |

| Start Up Current                                       | I <sub>VCCstart</sub>   | -     | 300    | 450  | μΑ   | V <sub>VCC</sub> =17 V                                                   |  |

| VCC Charge Current                                     | I <sub>VCCcharge1</sub> | -     | -      | 5.0  | mA   | V <sub>VCC</sub> = 0V                                                    |  |

|                                                        | I <sub>VCCcharge2</sub> | 0.55  | 1.05   | 1.60 | mA   | V <sub>VCC</sub> = 1 V                                                   |  |

|                                                        | I <sub>VCCcharge3</sub> | -     | 0.88   | -    | mA   | V <sub>VCC</sub> =17 V                                                   |  |

| Leakage Current of                                     | I <sub>StartLeak</sub>  | -     | 0.2    | 50   | μΑ   | V <sub>Drain</sub> = 450 V                                               |  |

| Start Up Cell and CoolMOS™                             |                         |       |        |      |      | at T <sub>j</sub> =100 °C                                                |  |

| Supply Current with Inactive Gate                      | I <sub>VCCsup_ng</sub>  | -     | 1.7    | 2.5  | mA   | Soft Start pin is open                                                   |  |

| Supply Current with Active Gate                        | I <sub>VCCsup_g</sub>   | -     | 2.5    | 3.6  | mA   | $V_{SoftS} = 3.0 \text{ V}, I_{FB} = 0 \text{ A}$                        |  |

| Supply Current in Auto Restart Mode with Inactive Gate | I <sub>VCCrestart</sub> | -     | 300    | -    | μΑ   | $I_{FB} = 0 A$ , $I_{SoftS} = 0 A$                                       |  |

| Supply Current in Active Burst Mode with Inactive Gate | I <sub>VCCburst1</sub>  | -     | 500    | 950  | μΑ   | $V_{FB} = 2.5 \text{ V}, V_{SoftS} = 3.0 \text{ V}$                      |  |

| with mactive date                                      | I <sub>VCCburst2</sub>  | -     | 500    | 950  | μΑ   | $V_{VCC} = 11.5 \text{ V}, V_{FB} = 2.5 \text{ V}, V_{SoftS}$<br>= 3.0 V |  |

### **Electrical Characteristics**

| VCC Turn-On Threshold      | $V_{VCCon}$         | 17.0 | 18.0 | 19.0 | ٧ |

|----------------------------|---------------------|------|------|------|---|

| VCC Turn-Off Threshold     | $V_{\text{VCCoff}}$ | 9.6  | 10.3 | 11.0 | V |

| VCC Turn-On/Off Hysteresis | $V_{\text{VCChys}}$ | -    | 7.7  | -    | V |

# 4.3.2 Internal Voltage Reference

### Table 6 Internal Voltage Reference

| Parameter                 | Symbol    | Limit Values |      |      | Unit | Test Condition                          |

|---------------------------|-----------|--------------|------|------|------|-----------------------------------------|

|                           |           | min.         | typ. | max. |      |                                         |

| Trimmed Reference Voltage | $V_{REF}$ | 4.90         | 5.00 | 5.10 | ٧    | measured at pin FB, I <sub>FB</sub> = 0 |

### 4.3.3 PWM Section

Table 7 PWM Section

| Parameter                                 | Symbol             | Limit Values |      |      | Unit | <b>Test Condition</b>                            |

|-------------------------------------------|--------------------|--------------|------|------|------|--------------------------------------------------|

|                                           |                    | min.         | typ. | max. |      |                                                  |

| Fixed Oscillator Frequency                | f <sub>OSC1</sub>  | 58           | 67   | 76   | kHz  |                                                  |

|                                           | f <sub>osc2</sub>  | 62           | 67   | 74.5 | kHz  | <i>T</i> <sub>j</sub> = 25°C                     |

| Frequency Jittering Range                 | f <sub>delta</sub> | -            | ±2.7 | -    | kHz  | <i>T</i> <sub>j</sub> = 25°C                     |

| Max. Duty Cycle                           | D <sub>max</sub>   | 0.70         | 0.75 | 0.80 |      |                                                  |

| Min. Duty Cycle                           | $D_{min}$          | 0            | -    | -    |      | V <sub>FB</sub> < 0.3 V                          |

| PWM-OP Gain                               | A <sub>V</sub>     | 3.0          | 3.2  | 3.4  |      |                                                  |

| Max. Level of Voltage Ramp                | V <sub>max</sub> - | -            | 0.6  | -    | V    |                                                  |

| V <sub>FB</sub> Operating Range Min Level | $V_{FBmin}$        | -            | 0.5  | -    | ٧    |                                                  |

| V <sub>FB</sub> Operating Range Max level | $V_{FBmax}$        | -            | -    | 4.3  | V    | CS=1 V, limited by<br>Comparator C4 <sup>1</sup> |

| FB Pull-Up Resistor                       | R <sub>FB</sub>    | 9            | 14   | 22   | kΩ   |                                                  |

| Soft_Start Pull-Up Resistor               | R <sub>SoftS</sub> | 30           | 45   | 62   | kΩ   |                                                  |

$<sup>^{1}</sup>$  The parameter is not subjected to production test - verified by design/characterization Datasheet 19 of 26

#### **Electrical Characteristics**

### 4.3.4 Control Unit

Table 8 Control Unit

| Parameter                                                  | Symbol                  | Limit Values |        |      | Unit | <b>Test Condition</b>                             |  |

|------------------------------------------------------------|-------------------------|--------------|--------|------|------|---------------------------------------------------|--|

|                                                            |                         | min.         | . typ. | max. |      |                                                   |  |

| Deactivation Level for SoftS<br>Comparator C7 by C2        | $V_{SoftSC2}$           | 2.98         | 3.10   | 3.22 | V    | V <sub>FB</sub> = 5 V                             |  |

| Clamped V <sub>Softs</sub> Voltage during Burst<br>Mode    | $V_{SoftSclmp\_bm}$     | 2.88         | 3.0    | 3.12 | V    |                                                   |  |

| Activation limit for Comparator C3                         | $V_{SoftSC3}$           | 3.85         | 4.00   | 4.15 | V    | $V_{FB} = 5 V$                                    |  |

| SoftS Startup Current                                      | I <sub>SoftSstart</sub> | -            | 0.9    | -    | mA   | V <sub>SoftS</sub> = 0 V                          |  |

| Over Load & Open Loop Detection<br>Limit for Comparator C4 | V <sub>FBC4</sub>       | 4.33         | 4.50   | 4.67 | V    | V <sub>SoftS</sub> = 4.5 V                        |  |

| Active Burst Mode Level for Comparator C5                  | $V_{FBC5}$              | 1.23         | 1.35   | 1.43 | V    | $V_{SoftS} = 4.5 \text{ V}$                       |  |

| Active Burst Mode Level for Comparator C6a                 | $V_{FBC6a}$             | 3.48         | 3.61   | 3.76 | V    | After Active Burst Mode is entered                |  |

| Active Burst Mode Level for<br>Comparator C6b              | $V_{FBC6b}$             | 2.88         | 3.00   | 3.12 | V    | After Active Burst Mode is entered                |  |

| Overvoltage Detection Limit                                | V <sub>VCCOVP</sub>     | 19.5         | 20.5   | 21.5 | V    | $V_{FB} = 5 \text{ V}, V_{SoftS} = 3.0 \text{ V}$ |  |

| Thermal Shutdown <sup>1</sup>                              | T <sub>jSD</sub>        | 130          | 140    | 150  | °C   |                                                   |  |

| Spike Blanking                                             | t <sub>Spike</sub>      | -            | 8      | -    | μs   |                                                   |  |

Note: The trend of all voltage levels in the Control Units is the same regarding the deviation except  $V_{VCCOVP}$

# 4.3.5 Current Limiting

Table 9 Current Limiting

| Parameter                                                               | Symbol              | Limit ' | Values |      | Unit | Test Condition                                     |

|-------------------------------------------------------------------------|---------------------|---------|--------|------|------|----------------------------------------------------|

|                                                                         |                     | min.    | typ.   | max. |      |                                                    |

| Peak Current Limitation<br>(incl. Propagation Delay)<br>(see Figure 12) | V <sub>csth</sub>   | 1.02    | 1.07   | 1.12 | V    | $dV_{\text{sense}}/dt = 0.6 \text{ V/}\mu\text{s}$ |

| Peak Current Limitation during Active<br>Burst Mode                     | V <sub>CS2</sub>    | 0.27    | 0.32   | 0.37 | V    |                                                    |

| Leading Edge Blanking                                                   | t <sub>LEB</sub>    | -       | 220    | -    | ns   | V <sub>SoftS</sub> = 3 V                           |

| CS Input Bias Current                                                   | I <sub>CSbias</sub> | -1.0    | -0.2   | 0    | μΑ   | V <sub>cs</sub> =0 V                               |

<sup>&</sup>lt;sup>1</sup> The parameter is not subjected to production test - verified by design/characterization. The thermal shutdown temperature refers to the junction temperature of the controller.

Datasheet 20 of 26 V 2.2

### **Electrical Characteristics**

# 4.3.6 CoolMOS™ Section

Table 10 CoolMOS™ Section

| Parameter                                    | Symbol               | Limit Values |       |       | Unit | Test Condition                 |

|----------------------------------------------|----------------------|--------------|-------|-------|------|--------------------------------|

|                                              |                      | min.         | typ.  | max.  |      |                                |

| Drain Source Breakdown Voltage               | V <sub>(BR)DSS</sub> | 600          | -     | -     | ٧    | <i>T</i> <sub>j</sub> = 25 °C  |

|                                              |                      | 650          | -     | -     |      | <i>T</i> <sub>j</sub> = 110 °C |

| Drain Source On-Resistance                   | R <sub>DSon</sub>    |              |       |       | Ω    |                                |

| ICE3B0365JG                                  |                      | -            | 6.45  | 7.50  |      | <i>T</i> <sub>j</sub> = 25 °C  |

|                                              |                      | -            | 13.70 | 17.00 |      | <i>T</i> <sub>j</sub> =125 °C¹ |

| ICE3B0565JG                                  |                      | -            | 4.70  | 5.44  |      | <i>T</i> <sub>j</sub> = 25 °C  |

|                                              |                      | -            | 10.00 | 12.50 |      | <i>T</i> <sub>j</sub> =125 °C¹ |

| Effective output capacitance, energy related | C <sub>o(er)</sub>   |              |       |       | pF   | V <sub>DS</sub> = 0 V to 480 V |

| ICE3B0365JG                                  |                      | -            | 3.65  | -     |      |                                |

| ICE3B0565JG                                  |                      | -            | 4.75  |       |      |                                |

| Rise Time <sup>2</sup>                       | t <sub>rise</sub>    | -            | 30    | -     | ns   |                                |

| Fall Time <sup>2</sup>                       | t <sub>fall</sub>    | -            | 30    | -     | ns   |                                |

$<sup>^{\</sup>rm 1}\, {\rm The}\, {\rm parameter}\, {\rm is}\, {\rm not}\, {\rm subjected}\, {\rm to}\, {\rm production}\, {\rm test}$  - verified by design/characterization

<sup>&</sup>lt;sup>2</sup> Measured in a Typical Flyback Converter Application Datasheet

#### **Outline Dimension**

#### **Outline Dimension** 5

Figure 19 PG-DSO-12 (Pb-free lead plating Plastic Dual-in-Line Outline)

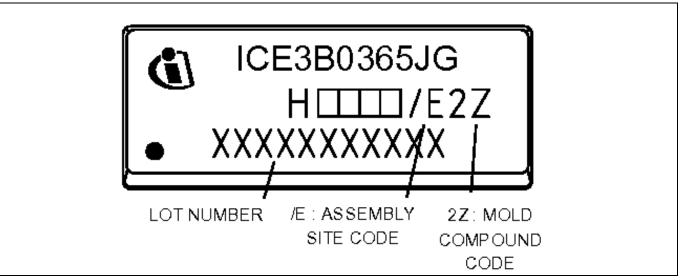

Marking

# 6 Marking

Figure 20 Marking for ICE3B0365JG

Figure 21 Marking for ICE3B0565JG

#### **Schematic for recommended PCB layout**

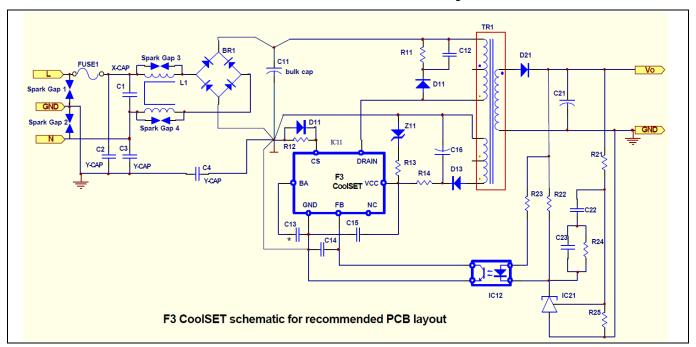

# 7 Schematic for recommended PCB layout

Figure 22 Schematic for recommended PCB layout

General guideline for PCB layout design using F3 CoolSET™ (Figure 22):

1. "Star Ground "at bulk capacitor ground, C11:

"Star Ground "means all primary DC grounds should be connected to the ground of bulk capacitor C11 separately in one point. It can reduce the switching noise going into the sensitive pins of the CoolSET™ device effectively. The primary DC grounds include the followings.

- a. DC ground of the primary auxiliary winding in power transformer, TR1, and ground of C16 and Z11.

- b. DC ground of the current sense resistor, R12

- c. DC ground of the CoolSET<sup>™</sup> device, GND pin of IC11; the signal grounds from C13, C14, C15 and collector of IC12 should be connected to the GND pin of IC11 and then "star "connect to the bulk capacitor ground.

- d. DC ground from bridge rectifier, BR1

- e. DC ground from the bridging Y-capacitor, C4

- 2. High voltage traces clearance:

High voltage traces should keep enough spacing to the nearby traces. Otherwise, arcing would incur.

- a. 400 V traces (positive rail of bulk capacitor C11) to nearby trace: > 2.0 mm

- b. 600 V traces (drain voltage of CoolSET™ IC11) to nearby trace: > 2.5 mm

- 3. Filter capacitor close to the controller ground:

Filter capacitors, C13, C14 and C15 should be placed as close to the controller ground and the controller pin as possible so as to reduce the switching noise coupled into the controller.

Guideline for PCB layout design when > 3 kV lightning surge test applied (Figure 22)

#### 1. Add spark gap

#### **Schematic for recommended PCB layout**

Spark gap is a pair of saw-tooth like copper plate facing each other which can discharge the accumulated charge during surge test through the sharp point of the saw-tooth plate.

- a. Spark Gap 3 and Spark Gap 4, input common mode choke,

- L1: Gap separation is around 1.5 mm (no safety concern)

- b. Spark Gap 1 and Spark Gap 2, Live / Neutral to GROUND:

These 2 Spark Gaps can be used when the lightning surge requirement is > 6 kV.

- 230 V<sub>AC</sub> input voltage application, the gap separation is around 5.5mm

- 115 V<sub>AC</sub> input voltage application, the gap separation is around 3mm

- 2. Add Y-capacitor (C2 and C3) in the Live and Neutral to ground even though it is a 2-pin input

- 3. Add negative pulse clamping diode, D11 to the Current sense resistor, R12:

The negative pulse clamping diode can reduce the negative pulse going into the CS pin of the CoolSET™ and reduce the abnormal behavior of the CoolSET™. The diode can be a fast speed diode such as 1N4148.

The principle behind is to drain the high surge voltage from Live/Neutral to Ground without passing through the sensitive components such as the primary controller, IC11.

### **Revision history**

#### Major changes since the last revision

| Page or Reference | Description of change     |

|-------------------|---------------------------|

| 1, 23             | Revise wrong marking text |

|                   |                           |

|                   |                           |