## **E-tile Hard IP User Guide**

# E-Tile Hard IP for Ethernet and E-Tile CPRI PHY Intel® FPGA IPs

Updated for Intel® Quartus® Prime Design Suite: 21.2

Version: **2021.08.04**

ID: 683468

## **Contents**

| 1. A | bout E-tile Hard IP User Guide                                              | net Intel FPGA IP Core |

|------|-----------------------------------------------------------------------------|------------------------|

| 2. A | bout the E-Tile Hard IP for Ethernet Intel FPGA IP Core                     | 6                      |

|      | 2.1. E-Tile Hard IP for Ethernet Intel FPGA IP Supported Features           | 8                      |

|      | 2.2. E-Tile Hard IP for Ethernet Intel FPGA IP Overview                     |                        |

|      | 2.3. IP Core Device Family and Speed Grade Support                          |                        |

|      | 2.3.1. E-Tile Hard IP for Ethernet Intel FPGA IP Device Family Support      |                        |

|      | 2.3.2. E-Tile Hard IP for Ethernet Intel FPGA IP Device Speed Grade Support |                        |

|      | 2.4. IP Core Verification                                                   |                        |

|      | 2.4.1. Simulation Environment                                               | 18                     |

|      | 2.4.2. Compilation Checking                                                 | 18                     |

|      | 2.4.3. Hardware Testing                                                     | 18                     |

|      | 2.5. Resource Utilization                                                   | 18                     |

|      | 2.6. Release Information                                                    | 20                     |

|      | 2.7. Getting Started                                                        | 21                     |

|      | 2.7.1. Installing and Licensing Intel FPGA IP Cores                         | 21                     |

|      | 2.7.2. Specifying the IP Core Parameters and Options                        |                        |

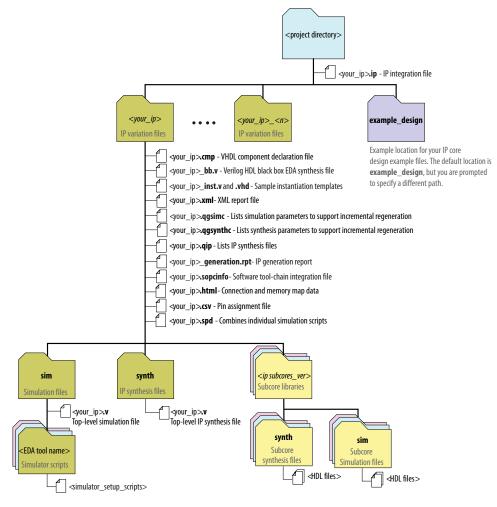

|      | 2.7.3. Generated File Structure                                             | 25                     |

|      | 2.7.4. Integrating Your IP Core in Your Design                              | 27                     |

|      | 2.7.5. IP Core Testbenches                                                  |                        |

|      | 2.7.6. Compiling the Full Design                                            |                        |

|      | 2.8. E-Tile Hard IP for Ethernet Intel FPGA IP Parameters                   | 53                     |

|      | 2.8.1. Parameter Editor Parameters                                          |                        |

|      | 2.8.2. RTL Parameters                                                       |                        |

|      | 2.9. Functional Description                                                 |                        |

|      | 2.9.1. E-Tile Hard IP for Ethernet Intel FPGA IP MAC                        |                        |

|      | 2.9.2. 1588 Precision Time Protocol Interfaces                              |                        |

|      | 2.9.3. PCS, OTN, FlexE, and Custom PCS Modes                                |                        |

|      | 2.9.4. Auto-Negotiation and Link Training                                   |                        |

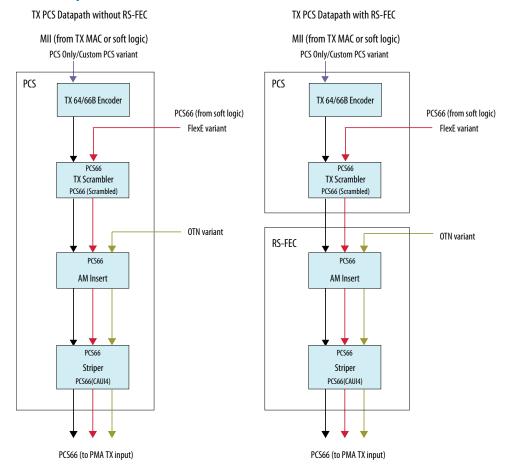

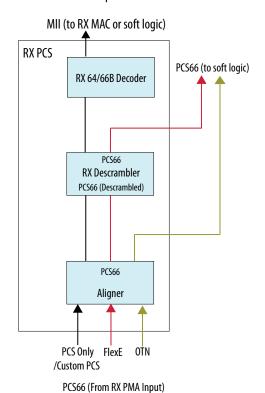

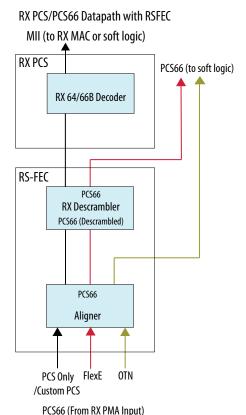

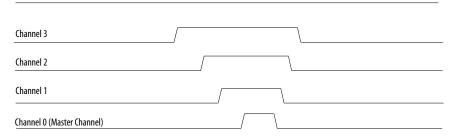

|      | 2.9.5. TX and RX RS-FEC                                                     |                        |

|      | 2.9.6. PMA Direct Mode                                                      |                        |

|      | 2.9.7. Dynamic Reconfiguration                                              | 110                    |

|      | 2.9.8. Ethernet Adaptation Flow for 10G/25G and 100G/4x25G Dynamic          |                        |

|      |                                                                             |                        |

|      | 2.9.9. Ethernet Adaptation Flow with PTP or with External AIB Clocking      |                        |

|      | 2.9.10. Ethernet Adaptation Flow with Non-external AIB Clocking             |                        |

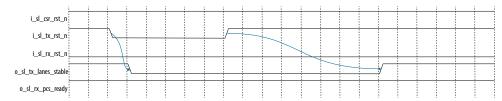

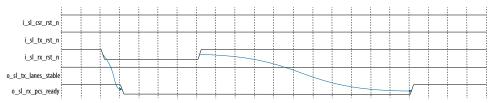

|      | 2.10. Reset                                                                 |                        |

|      | 2.10.1. Reset Sequence                                                      |                        |

|      | 2.11. Interfaces and Signals                                                |                        |

|      | 2.11.1. TX MAC Interface to User Logic                                      |                        |

|      | 2.11.2. RX MAC Interface to User Logic                                      |                        |

|      | 2.11.3. TX PCS Interface to User Logic                                      |                        |

|      | 2.11.4. RX PCS Interface to User Logic                                      |                        |

|      | 2.11.5. FlexE and OTN Mode TX Interface                                     |                        |

|      | 2.11.6. FlexE and OTN Mode RX Interface                                     |                        |

|      | 2.11.7. TX Custom PCS Interface to User Logic                               |                        |

|      | 2.11.8. RX Custom PCS Interface to User Logic                               | 142                    |

|      | 2.11.9. PMA Direct Interface                                                           | 144 |

|------|----------------------------------------------------------------------------------------|-----|

|      | 2.11.10. Custom Rate Interface                                                         | 144 |

|      | 2.11.11. Deterministic Latency Interface                                               |     |

|      | 2.11.12. 1588 PTP Interface                                                            |     |

|      | 2.11.13. Ethernet Link and Transceiver Signals                                         |     |

|      | 2.11.14. Reconfiguration Interfaces and Signals                                        |     |

|      | 2.11.15. Miscellaneous Status and Debug Signals                                        |     |

|      | 2.11.16. Reset Signals                                                                 |     |

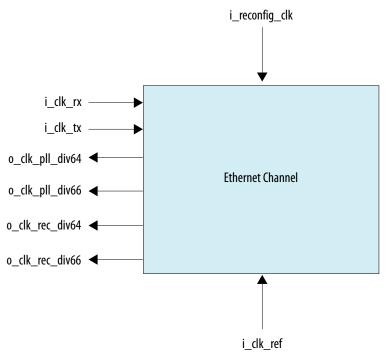

|      | 2.11.17. Clocks                                                                        |     |

|      | 2.12. Register Descriptions                                                            |     |

|      | 2.12.1. Auto Negotiation and Link Training Registers                                   |     |

|      | 2.12.2. PHY Registers                                                                  |     |

|      | 2.12.3. TX MAC Registers                                                               |     |

|      | 2.12.4. RX MAC Registers                                                               |     |

|      | 2.12.5. Pause and Priority- Based Flow Control Registers                               |     |

|      | 2.12.6. TX Statistics Counter Registers                                                |     |

|      | 2.12.7. RX Statistics Counter Registers                                                |     |

|      | 2.12.8. 1588 PTP Registers                                                             |     |

|      | 2.12.9. RS-FEC Registers                                                               |     |

|      | 2.12.10. PMA Registers                                                                 |     |

|      | 2.13. Document Revision History for the E-tile Hard IP for Ethernet Intel FPGA IP Core | 269 |

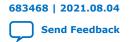

| 3. A | bout the E-Tile CPRI PHY Intel FPGA IP                                                 | 281 |

|      | 3.1. Supported Features                                                                | 281 |

|      | 3.2. E-Tile CPRI PHY Intel FPGA IP Overview                                            |     |

|      | 3.3. E-Tile CPRI PHY Device Family Support                                             |     |

|      | 3.4. Resource Utilization                                                              |     |

|      | 3.5. Release Information                                                               |     |

|      | 3.6. E-Tile CPRI PHY Intel FPGA IP Core Device Speed Grade Support                     |     |

|      | 3.7. Getting Started                                                                   |     |

|      | 3.7.1. Installing and Licensing Intel FPGA IP Cores                                    |     |

|      | 3.7.2. Specifying the IP Core Parameters and Options                                   |     |

|      | 3.7.3. Generated File Structure                                                        |     |

|      | 3.7.4. E-Tile CPRI PHY Intel FPGA IP Channel Placement                                 | 291 |

|      | 3.7.5. IP Core Testbenches                                                             | 298 |

|      | 3.7.6. Compiling the Full Design                                                       | 298 |

|      | 3.8. Parameter Settings                                                                | 298 |

|      | 3.9. Functional Description                                                            | 300 |

|      | 3.9.1. CPRI PHY Functional Blocks                                                      | 300 |

|      | 3.9.2. Dynamic Reconfiguration                                                         | 305 |

|      | 3.10. E-Tile CPRI PHY Intel FPGA IP Interface Signals                                  | 305 |

|      | 3.10.1. Clock Signals                                                                  | 305 |

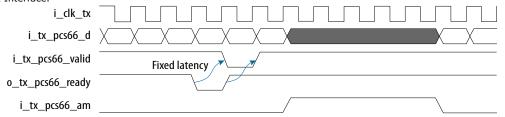

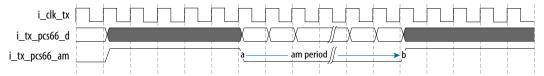

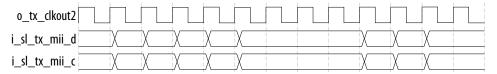

|      | 3.10.2. TX MII Interface                                                               | 307 |

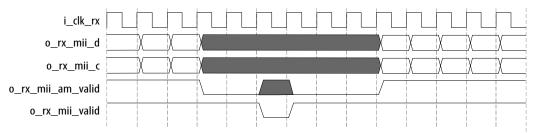

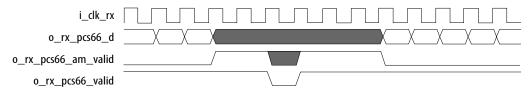

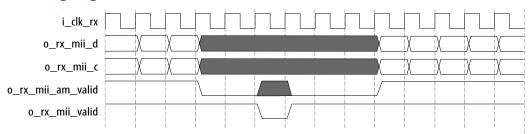

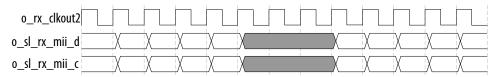

|      | 3.10.3. RX MII Interface                                                               | 308 |

|      | 3.10.4. TX 8B/10B Interface                                                            | 309 |

|      | 3.10.5. RX 8B/10B Interface                                                            |     |

|      | 3.10.6. Status Interface for 64B/66B Line Rate                                         | 310 |

|      | 3.10.7. Status Interface for 8B/10B Line Rate                                          | 311 |

|      | 3.10.8. Serial I/O Pins                                                                |     |

|      | 3.10.9. Reconfiguration Interfaces (Avalon-MM)                                         | 313 |

|      | 3.11. Registers                                                                        | 315 |

|      |                                                                                        |     |

## Contents

| 3.11.1. PHY Registers                                                                                | 315 |

|------------------------------------------------------------------------------------------------------|-----|

| 3.11.2. CPRI PHY Registers                                                                           | 320 |

| 3.11.3. PMA Registers                                                                                | 322 |

| 3.11.4. RS-FEC Registers                                                                             | 323 |

| 3.12. Document Revision History for the E-tile CPRI PHY Intel FPGA IP                                | 323 |

| 4. Supported Tools                                                                                   | 326 |

| 4.1. E-Tile Channel Placement Tool                                                                   | 326 |

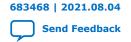

| 4.2. Ethernet Toolkit Overview                                                                       | 326 |

| 4.2.1. Features                                                                                      | 327 |

| 4.3. Document Revision History for the E-tile Channel Placement Tool and the Ethernet Link Inspector |     |

| 5 F-tile Hard TD User Guide Archives                                                                 | 320 |

## 1. About E-tile Hard IP User Guide

This user guide consists of information for the following IP cores:

- E-Tile Hard IP for Ethernet Intel® FPGA IP (Intel Stratix® 10)

- E-Tile Ethernet IP for Intel Agilex<sup>™</sup> FPGA

- E-Tile CPRI PHY Intel FPGA IP

For more information on specific IP release, refer to the *Release Information* sections.

#### **Related Information**

- E-Tile Hard IP for Ethernet Intel FPGA IP Core Release Information on page 20

- E-Tile Ethernet IP for Intel Agilex FPGA Core Release Information on page 20

- E-Tile CPRI PHY IP Core Release Information on page 285

- E-tile Hard IP Intel Stratix 10 Design Examples User Guide Describes the Ethernet, CPRI PHY, and Dynamic Reconfiguration design example generation, simulation, compilation, and testing for Intel Stratix 10 devices.

- E-tile Hard IP Intel Agilex Design Examples User Guide Describes the Ethernet, CPRI PHY, and Dynamic Reconfiguration design example generation, simulation, compilation, and testing for Intel Agilex devices.

- E-Tile Transceiver PHY User Guide

## 2. About the E-Tile Hard IP for Ethernet Intel FPGA IP Core

Intel Stratix 10 and Intel Agilex E-tile FPGA production devices include a configurable, hardened protocol stack for Ethernet that is compatible with the *IEEE 802.3 High Speed Ethernet Standard* and the *25G/50G Ethernet Specification, Draft 1.6* from the 25 Gigabit Ethernet Consortium.

## **Table 1. Ethernet IP Naming Convention**

The table shows the Ethernet-based IPs available in IP Catalog.

| Supported Device Family | IP Catalog                                |

|-------------------------|-------------------------------------------|

| Intel Stratix 10        | E-Tile Hard IP for Ethernet Intel FPGA IP |

| Intel Agilex            | E-Tile Ethernet IP for Intel Agilex FPGA  |

Note:

Unless specified, the E-Tile Hard IP for Ethernet Intel FPGA IP applies to all supported device families.

The E-Tile Hard IP for Ethernet Intel FPGA IP provides access to this hard IP at Ethernet data rates of 10 Gbps, 25 Gbps, and 100 Gbps. The IP core is included in the Intel FPGA IP Library and is available from the Intel Quartus<sup>®</sup> Prime Pro Edition IP Catalog.

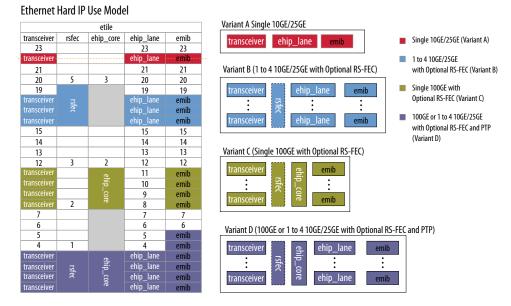

The IP core is available in the following variants, each providing a different combination of Ethernet channels and features:

- Single 10GE/25GE channel

- 1 to 4 10GE/25GE channels with optional Reed-Solomon Forward Error Correction (RS-FEC)

- 100GE channel with optional RS-FEC

- 100GE or 1 to 4 10GE/25GE channels with optional RS-FEC, and optional 1588 Precision Time Protocol (PTP)

- Custom PCS with optional RS-FEC

The 100GE or 1 to 4 10GE/25GE channels with optional RS-FEC, and optional 1588 Precision Time Protocol (PTP) variant contains a 100G Ethernet channel, and up to 4 single-lane channels that can run at 10G or 25G. However, the single-lane channels and the 100GE channel cannot run at the same time.

For any variant except the custom PCS with RS-FEC variant, you can choose a Media Access Control (MAC) + Physical Coding Sublayer(PCS) variation, a PCS-only variation, a custom PCS variation, a Flexible Ethernet (FlexE) variation, or an Optical Transport Network (OTN) variation.

Figure 1. Variant Selection

For any variant, you can choose a MAC + PCS variation, a PCS-only variation, a FlexE variation, an OTN variation or a custom PCS variation.

| Ethernet IP Layers                     | Protocol Layers Include |              |                             |                       |                             |                        | d                            |                                        |                                        |                            | 5   |     |                          |                                              |               |                                                                |                                    |

|----------------------------------------|-------------------------|--------------|-----------------------------|-----------------------|-----------------------------|------------------------|------------------------------|----------------------------------------|----------------------------------------|----------------------------|-----|-----|--------------------------|----------------------------------------------|---------------|----------------------------------------------------------------|------------------------------------|

|                                        | MAC                     | Flow Control | IEEE 1588 PTP 1-Step/2-Step | PCS Encoding/Decoding | PCS Scrambling/Descrambling | PCS Striping/Alignment | RS-FEC Transcode/Detranscode | RS-FEC (528,514) Encode/Decode/Correct | RS-FEC (544,514) Encode/Decode/Correct | RS-FEC Stripping/Alignment | PMA | PMD | Single 10GE/25GE Channel | 1 to 410GE/25GE Channels with optional RSFEC | 100G Channels | 100GE or 1 to 410GE/25GE Channels with optional RS-FEC and PTP | Custom PCS with Optional RSFEC (3) |

| MAC + PCS                              | Yes                     | Yes          | _                           | Yes                   | Yes                         | Yes                    | _                            | _                                      | _                                      | _                          | Yes | Yes | Yes                      | Yes                                          | Yes           | Yes                                                            | _                                  |

| MAC + 1588 PTP + PCS                   | Yes                     | Yes          | Yes                         | Yes                   | Yes                         | Yes                    | _                            | _                                      | _                                      | _                          | Yes | Yes | _                        | _                                            | _             | Yes                                                            | _                                  |

| MAC + PCS + (528,514 RSFEC)            | Yes                     | Yes          | -                           | Yes                   | Yes                         | _                      | Yes                          | Yes                                    | _                                      | Yes                        | Yes | Yes | Yes <sup>(1)</sup>       | Yes <sup>(1)</sup>                           | Yes           | Yes <sup>(1)</sup>                                             | _                                  |

| MAC + PCS + (544,514 RSFEC)            | Yes                     | Yes          | _                           | Yes                   | Yes                         | _                      | Yes                          | _                                      | Yes                                    | Yes                        | Yes | Yes | _                        | _                                            | Yes           | Yes <sup>(2)</sup>                                             | _                                  |

| MAC + 1588 PTP + PCS + (528,514 RSFEC) | Yes                     | Yes          | Yes                         | Yes                   | Yes                         | _                      | Yes                          | Yes                                    | _                                      | Yes                        | Yes | Yes | _                        | _                                            | _             | Yes <sup>(1)</sup>                                             | _                                  |

| PCS Only                               | _                       | _            | _                           | Yes                   | Yes                         | Yes                    | _                            | _                                      | _                                      | _                          | Yes | Yes | Yes                      | Yes                                          | Yes           | Yes                                                            | Yes                                |

| OTN                                    |                         | _            | _                           | _                     | _                           | Yes                    | _                            |                                        | _                                      | _                          | Yes | Yes | Yes                      | Yes                                          | Yes           | Yes                                                            | _                                  |

| FlexE                                  | _                       | _            | -                           | _                     | Yes                         | Yes                    | _                            | 1                                      | _                                      | _                          | Yes | Yes | Yes                      | Yes                                          | Yes           | Yes                                                            | _                                  |

| PCS + (528,514 RSFEC)                  | _                       | -            |                             | Yes                   | Yes                         | -                      | Yes                          | Yes                                    | _                                      | Yes                        | Yes | Yes | Yes <sup>(1)</sup>       | Yes                                          | Yes           | Yes <sup>(1)</sup>                                             | Yes                                |

| PCS + (544,514 RSFEC)                  | _                       | -            | -                           | Yes                   | Yes                         | -                      | Yes                          | _                                      | Yes                                    | Yes                        | Yes | Yes | _                        | _                                            | Yes           | Yes <sup>(2)</sup>                                             | _                                  |

| OTN + (528,514 RSFEC)                  | _                       | _            | _                           | _                     | _                           | _                      | Yes                          | Yes                                    | _                                      | Yes                        | Yes | Yes | Yes <sup>(1)</sup>       | Yes <sup>(1)</sup>                           | Yes           | Yes <sup>(1)</sup>                                             | _                                  |

| OTN + (544,514 RSFEC)                  | _                       | _            | _                           |                       | _                           | _                      | Yes                          | _                                      | Yes                                    | Yes                        | Yes | Yes | _                        | _                                            | Yes           | Yes <sup>(2)</sup>                                             | -                                  |

| FlexE + (528,514 RSFEC)                | _                       | _            | _                           |                       | Yes                         |                        | Yes                          | Yes                                    | -                                      | Yes                        | Yes | Yes | Yes <sup>(1)</sup>       | Yes <sup>(1)</sup>                           | Yes           | Yes <sup>(1)</sup>                                             |                                    |

| FlexE + (544,514 RSFEC)                | _                       | 1            | 1                           | 1                     | Yes                         | -                      | Yes                          | _                                      | Yes                                    | Yes                        | Yes | Yes | _                        | _                                            | Yes           | Yes <sup>(2)</sup>                                             | -                                  |

| Custom PCS Only                        | _                       | _            | _                           | Yes                   | Yes                         | Yes                    | _                            | _                                      | _                                      | _                          | Yes | Yes | _                        | _                                            | _             | _                                                              | Yes                                |

| Custom PCS + RSFEC                     | _                       | _            | _                           | Yes                   | Yes                         | _                      | Yes                          | Yes                                    | _                                      | Yes                        | Yes | Yes | _                        | _                                            | _             | _                                                              | Yes                                |

<sup>(1) 10</sup>G data rate does not support RSFEC.

**Table 2.** Client Interfaces for IP Core Variations

| IP Core Variation | Client Interface Type                        |

|-------------------|----------------------------------------------|

| MAC+PCS           | Avalon® Streaming (Avalon-ST) <sup>(1)</sup> |

| PCS_Only          | Media Independent Interface (MII)            |

| Custom PCS        | MII                                          |

| FlexE             | PCS66                                        |

| OTN               | PCS66                                        |

Note:

The E-Tile Hard IP for Ethernet Intel FPGA IP provides support for the OTN feature. For further inquiries, contact your nearest Intel sales representative.

<sup>(2)</sup> Only 100G data rate supports (544,514) RSFEC.

<sup>(3)</sup> Customizable data rate PCS from 2.5 to 28 Gbps for protocols other than Ethernet...

<sup>(1)</sup> The E-Tile Hard IP for Ethernet Intel FPGA IP MAC interface uses a modified AVST interface. For recommended usage of the TX MAC interface, refer to the Figure 37 on page 124.

E-Tile Hard IP for Ethernet Intel FPGA IP core supports a variety of protocol implementations.

Table 3. Ethernet Protocols

| Ethernet Channel | Protocol                  | Number of Lanes and Line Rate                                                |

|------------------|---------------------------|------------------------------------------------------------------------------|

| 100GE            | 100GBASE-KR4              | 4x25.78125 Gbps Non-Return-to-Zero (NRZ) lanes for Copper Backplane          |

|                  | 100GBASE-CR4              | 4x25.78125 Gbps NRZ lanes for Direct Attach Copper Cable                     |

|                  | CAUI-4                    | 4x25.78125 Gbps NRZ lanes for Low Loss Links: Chip-to-Chip or Chip-to-Module |

|                  | 100GBASE-KR2              | 2x53.125 Gbps PAM4 lanes for Copper Backplane                                |

|                  | 100GBASE-CR2              | 2x53.125 Gbps PAM4 lanes for Direct Attach Copper Cable                      |

|                  | CAUI-2                    | 2x53.125 Gbps PAM4 lanes for Low Loss Links: Chip-to-Chip, Chip-to-Module    |

| 25GE             | 25GBASE-KR                | 1x25.78125 Gbps NRZ lane for Copper Backplane                                |

|                  | 25GBASE-CR                | 1x25.78125 Gbps NRZ lane for Direct Attach Copper Cable                      |

|                  | 25GBASE-R AUI             | 1x25.78125 Gbps NRZ lane for Low Loss Connections to External PHY Modules    |

|                  | 25GBASE-R Consortium Link | 1x25.78125 Gbps NRZ lane based on the 25G/50G Consortium Specification       |

| 10GE             | 10GBASE-KR                | 1x10.3125 Gbps NRZ lane for Copper Backplane                                 |

|                  | 10GBASE-CR                | 1x10.3125 Gbps NRZ lane for Direct Attach Copper Cable                       |

|                  | XAUI                      | 1x10.3125 Gbps NRZ lane for Low Loss Connections to External PHY Modules     |

#### **Related Information**

• IEEE Website

The IEEE 802.3-2015 High Speed Ethernet Standard is available on the IEEE website.

- 25G Ethernet Consortium

- Knowledge Data Base (KDB)

Provides links to applicable articles for a variety of FPGA related issues.

• E-tile Hard IP Intel Stratix 10 Design Examples User Guide

Describes the Ethernet, CPRI PHY, and Dynamic Reconfiguration design example generation, simulation, compilation, and testing for Intel Stratix 10 devices.

- E-tile Hard IP Intel Agilex Design Examples User Guide

- Describes the Ethernet, CPRI PHY, and Dynamic Reconfiguration design example generation, simulation, compilation, and testing for Intel Agilex devices.

- E-Tile Transceiver PHY User Guide

## 2.1. E-Tile Hard IP for Ethernet Intel FPGA IP Supported Features

The IP core is designed to the *IEEE 802.3-2015 High Speed Ethernet Standard* available on the IEEE website (www.ieee.org) and the *25G/50G Ethernet Specification, Draft 1.6* available from the 25 Gigabit Ethernet Consortium. The MAC provides cut-

through frame processing to optimize latency, and supports full wire line speed with a 64-byte frame length and back-to-back or mixed length traffic with no dropped packets. All E-Tile Hard IP for Ethernet Intel FPGA IP variations are in full-duplex mode.

Table 4. E-Tile Hard IP for Ethernet Intel FPGA IP Features

| Features                  | Description                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| PCS                       | Hard IP logic that interfaces seamlessly to E-tile transceivers.                                                                                                                                                                                                           |  |  |  |  |  |  |

|                           | CAUI external interface consisting of four transceiver lanes operating at 25.78125 Gbps.                                                                                                                                                                                   |  |  |  |  |  |  |

|                           | CAUI-2 external interface with two transceiver lanes operating at 53.125 Gbps with PAM4 encoding                                                                                                                                                                           |  |  |  |  |  |  |

|                           | 25G AUI external interface with 1 transceiver lane operating at 25.78125 Gbps                                                                                                                                                                                              |  |  |  |  |  |  |

|                           | 10G AUI external interface with 1 transceiver lane operating at 10.3125 Gbps                                                                                                                                                                                               |  |  |  |  |  |  |

|                           | Supports CAUI-4 links based on 64B/66B encoding with data striping and alignment markers to align data from multiple lanes.                                                                                                                                                |  |  |  |  |  |  |

|                           | Supports customizable data rate PCS from 2.5 to 28 Gbps for protocols other than Ethernet.                                                                                                                                                                                 |  |  |  |  |  |  |

|                           | Optional RS-FEC(528,514) or RS-FEC(544,514) for 25G and 100G variations.                                                                                                                                                                                                   |  |  |  |  |  |  |

|                           | Supports 10G, 25G, and 100G variations.  • Auto-negotiation (AN) as defined in <i>IEEE Standard 802.3-2915 Clause 73</i> and the 25G Ethernet Consortium Schedule Draft 1.6, and  • Link training (LT) as defined in <i>IEEE Standard 802.3-2915 Clauses 92 and 93</i> and |  |  |  |  |  |  |

|                           | the 25G Ethernet Consortium Schedule Draft 1.6                                                                                                                                                                                                                             |  |  |  |  |  |  |

|                           | RX Skew Variation tolerance that exceeds the <i>IEEE 802.3-2015 High Speed Ethernet Standard</i> Clause 80.5 requirements.                                                                                                                                                 |  |  |  |  |  |  |

| OTN                       | Optional 25GE constant bit rate (CBR); with TX and RX PCS66 bit encoding/decoding and scrambling/descrambling disabled.                                                                                                                                                    |  |  |  |  |  |  |

|                           | Note: The E-Tile Hard IP for Ethernet Intel FPGA IP provides support for the OTN feature. For further inquiries, contact your nearest Intel sales representative.                                                                                                          |  |  |  |  |  |  |

|                           | Optional RS-FEC(528,514) or RS-FEC(544,514) for 25G and 100G variations.                                                                                                                                                                                                   |  |  |  |  |  |  |

| Flexible Ethernet (FlexE) | Optional CBR; with TX and RX PCS66 bit encoding/decoding disabled and scrambling/descrambling enabled.                                                                                                                                                                     |  |  |  |  |  |  |

|                           | Optional RS-FEC(528,514) or RS-FEC(544,514) for 25G and 100G variations.                                                                                                                                                                                                   |  |  |  |  |  |  |

| PMA Direct Mode           | Optional to switch from MAC+PCS to PMA only mode during run-time.                                                                                                                                                                                                          |  |  |  |  |  |  |

| Frame Structure Control   | Support for jumbo packets.                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|                           | RX CRC pass-through control.                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|                           | 1000 bits RX PCS lane skew tolerance for 100G links, which exceeds the <i>IEEE</i> 802.3-2015 High Speed Ethernet Standard Clause 82.2.12 requirements.                                                                                                                    |  |  |  |  |  |  |

|                           | Optional per-packet TX CRC generation and insertion.                                                                                                                                                                                                                       |  |  |  |  |  |  |

|                           | Optional Deficit Idle Counter (DIC) options to maintain a finely controlled 8-byte, 10-byte, or 12-byte inter-packet gap (IPG) minimum average, or allow the user to drive the IPG from the client interface                                                               |  |  |  |  |  |  |

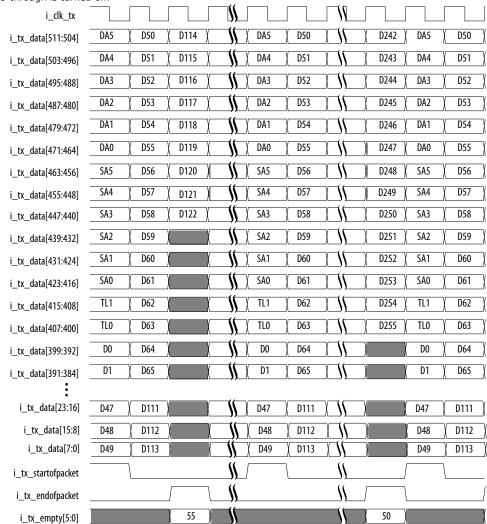

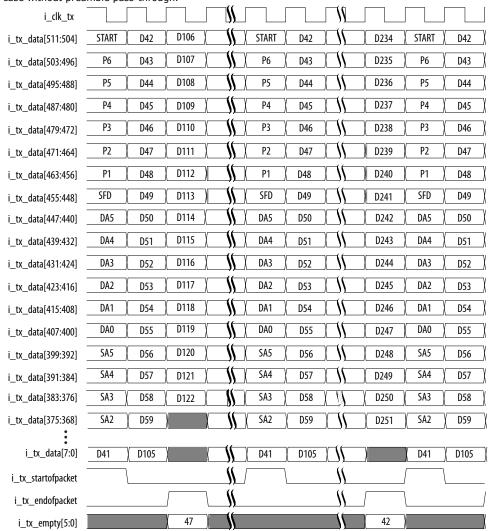

|                           | RX and TX preamble pass-through options for applications that require proprietary user management information transfer.                                                                                                                                                    |  |  |  |  |  |  |

|                           | Optional TX MAC source address insertion.                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|                           | continued                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| Features                        | Description                                                                                                                                                                                                   |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                 | TX automatic frame padding to meet the 64-byte minimum Ethernet frame length on the Ethernet link. Optional per-packet disabling of this feature.                                                             |

|                                 | TX error insertion capability supports client invalidation of in-progress input to TX client interface.                                                                                                       |

| Frame Monitoring and Statistics | RX CRC checking and error reporting.                                                                                                                                                                          |

|                                 | Optional RX strict Start Frame Delimiter (SFD) checking per IEEE specification.                                                                                                                               |

|                                 | Optional RX strict preamble checking per IEEE specification.                                                                                                                                                  |

|                                 | RX malformed packet checking per IEEE specification.                                                                                                                                                          |

|                                 | Received control frame type indication.                                                                                                                                                                       |

|                                 | Statistics counters.                                                                                                                                                                                          |

|                                 | Snapshot feature for precisely timed capture of statistics counter values.                                                                                                                                    |

|                                 | Optional fault signaling: detects and reports local fault and generates remote fault, with support for unidirectional link fault as defined in <i>IEEE 802.3-2015 High Speed Ethernet Standard</i> Clause 66. |

| Flow Control                    | Optional <i>IEEE 802.3-2015 Ethernet Standard</i> Clause 31 Ethernet flow control operation using the pause registers or pause interface.                                                                     |

|                                 | Optional priority-based flow control that complies with the IEEE Standard 802.1Q-2014 —Amendment 17: Priority-based Flow Control.                                                                             |

|                                 | Pause frame filtering control.                                                                                                                                                                                |

|                                 | Software can dynamically toggle local TX MAC data flow to support selective input flow cut-off.                                                                                                               |

| Precision Time Protocol (PTP)   | Optional support for the IEEE Standard 1588-2008 Precision Clock Synchronization Protocol (1588 PTP) (1588v2).                                                                                                |

|                                 | 1-step (1588v1 and 1588v2) and 2-step TX (1588v2) timestamps.                                                                                                                                                 |

|                                 | Support for PTP headers in a variety of frame formats, including Ethernet encapsulated, UDP in IPv4, and UDP in IPv6.                                                                                         |

|                                 | Support for Checksum Zero and Checksum extension byte calculations.                                                                                                                                           |

|                                 | Support for Correction field operations.                                                                                                                                                                      |

|                                 | Programmable extra latency.                                                                                                                                                                                   |

| Debug and testability           | Optional serial PMA loopback (TX to RX) at the serial transceiver for self-diagnostic testing.                                                                                                                |

|                                 | Optional parallel loopback (TX to RX) at the MAC or at the PCS for self-diagnostic testing.                                                                                                                   |

|                                 | Bit-interleaved parity error counters to monitor bit errors per PCS lane.                                                                                                                                     |

|                                 | RX PCS error block counters to monitor errors during and between frames.                                                                                                                                      |

|                                 | Malformed and dropped packet counters.                                                                                                                                                                        |

|                                 | High BER detection to monitor link bit error rates over all PCS lanes.                                                                                                                                        |

|                                 | Optional scrambled Idle test pattern generation and checking.                                                                                                                                                 |

|                                 | Snapshot feature for precisely timed capture of statistics counter values.                                                                                                                                    |

|                                 | TX error insertion capability supports test and debug.                                                                                                                                                        |

|                                 | Support for Ethernet Link Inspector (ELI) tool to monitor an Ethernet link.                                                                                                                                   |

|                                 | continued                                                                                                                                                                                                     |

| Features              | Description                                                                                                                                                                                                                                                       |  |  |  |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                       | Support for Ethernet Tool Kit to monitor an Ethernet link.                                                                                                                                                                                                        |  |  |  |  |  |

| User System Interface | Avalon memory-mapped interface (Avalon-MM) to access the IP core control and status registers.                                                                                                                                                                    |  |  |  |  |  |

|                       | Avalon streaming interface (Avalon-ST) connects the MAC to client logic with the start of frame in the most significant byte (MSB) in MAC+PCS variations. Interface for 100G channel has 512 bits; the 10/25G channels use 64 bits when the MAC layer is enabled. |  |  |  |  |  |

|                       | MII data path interface connects the PCS to client logic in PCS-only variations. Interface for 100G variants has 256 bits of data and 32 bits of control; interface for 10G/25G variants has 64 bits of data and 8 bits of control.                               |  |  |  |  |  |

|                       | Hardware and software reset control.                                                                                                                                                                                                                              |  |  |  |  |  |

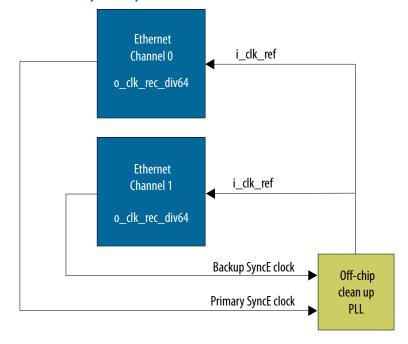

|                       | Supports Synchronous Ethernet (SyncE) by providing a CDR recovered clock output signal to the device fabric.                                                                                                                                                      |  |  |  |  |  |

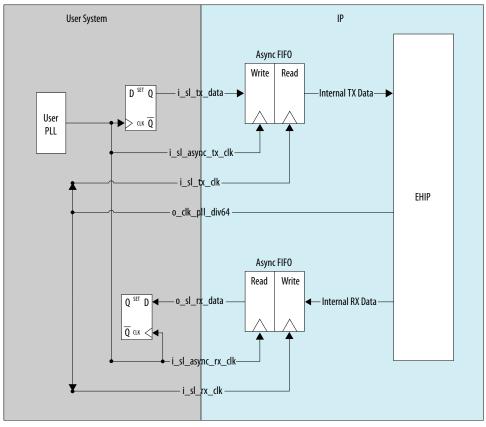

|                       | Supports external source clock for EMIB interface for applications that requires switching transceiver line rate.                                                                                                                                                 |  |  |  |  |  |

For a detailed specification of the Ethernet protocol refer to the *IEEE 802.3-2015 High Speed Ethernet Standard*.

### **Related Information**

- IEEE Website

- The IEEE 802.3-2015 High Speed Ethernet Standard is available on the IEEE website.

- 25G Ethernet Consortium

## 2.2. E-Tile Hard IP for Ethernet Intel FPGA IP Overview

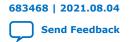

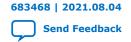

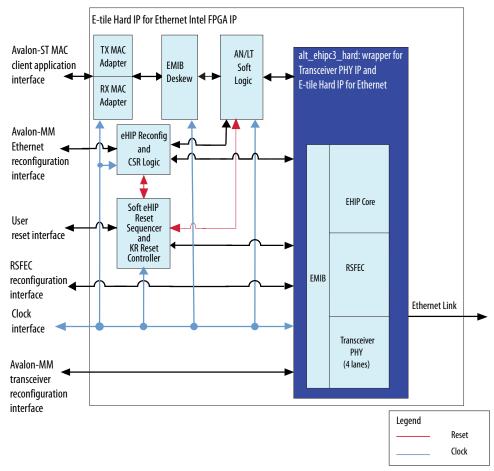

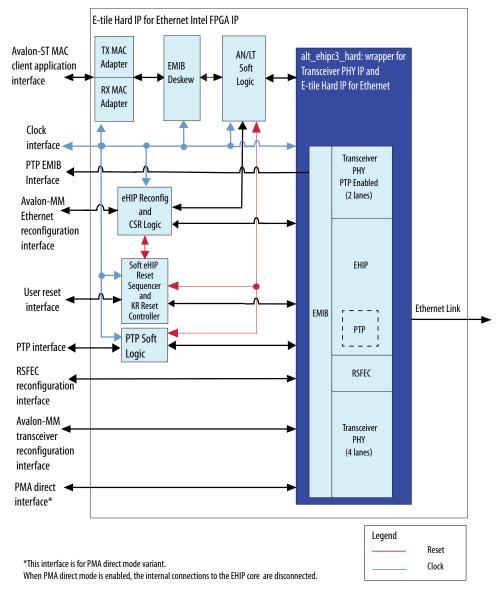

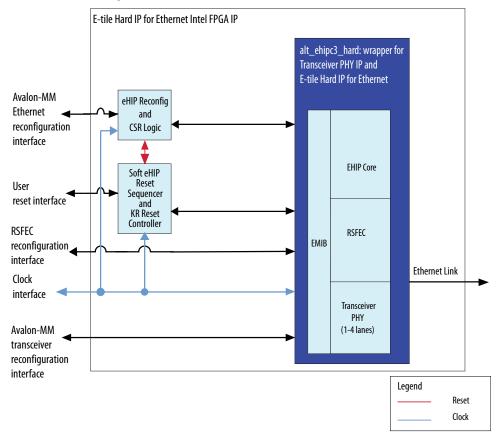

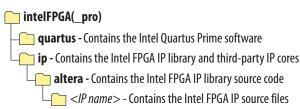

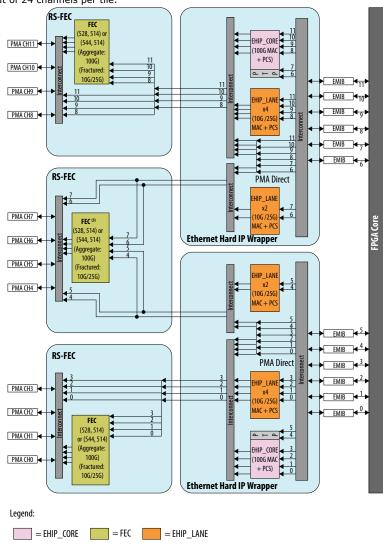

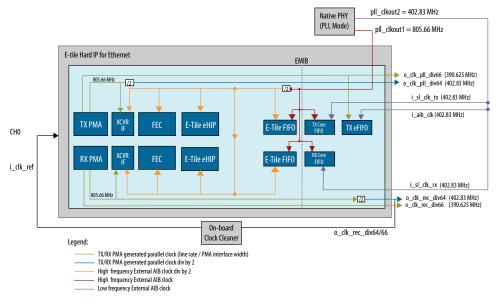

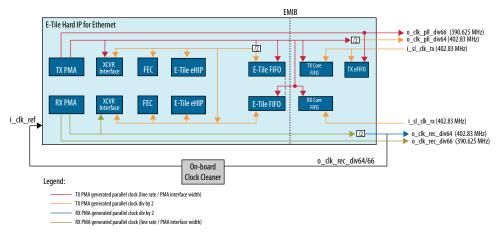

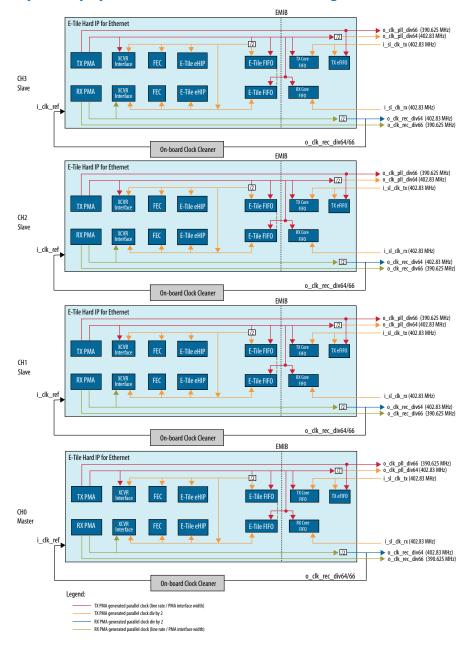

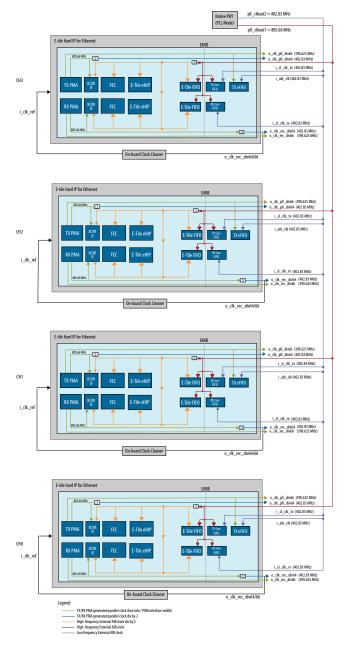

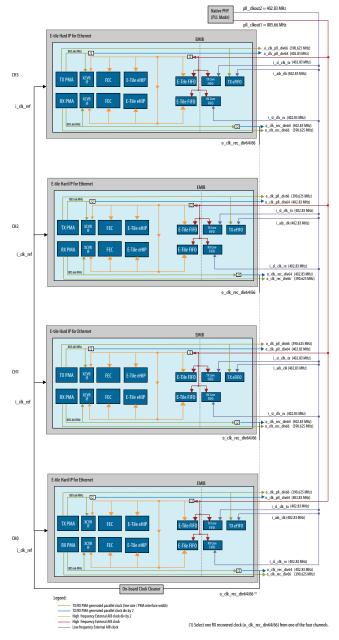

The E-Tile Hard IP for Ethernet Intel FPGA IP block diagrams show the main blocks, and internal and external connections for each variant.

For these block diagrams, the reconfiguration and soft reset sequencer implement the reconfiguration interfaces and resets for the core, respectively. The auto-negotiation and link training (AN/LT) soft logic is only inserted when you select **Enable AN/LT**.

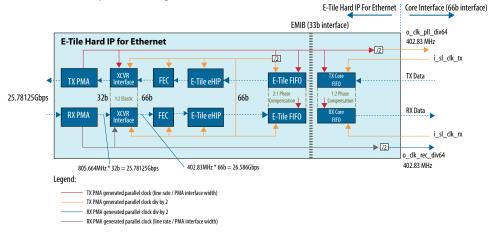

Figure 2. Single 10G/25G Channel

This variant supports only single channel 10G/25G Ethernet without RS-FEC and PTP features.

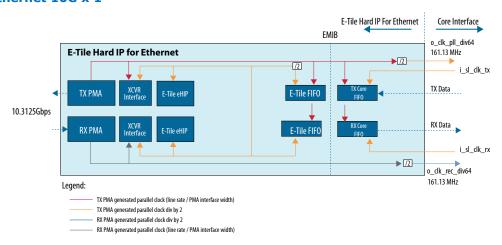

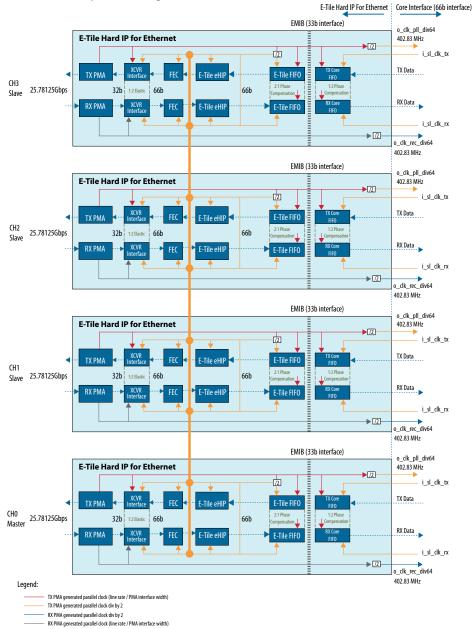

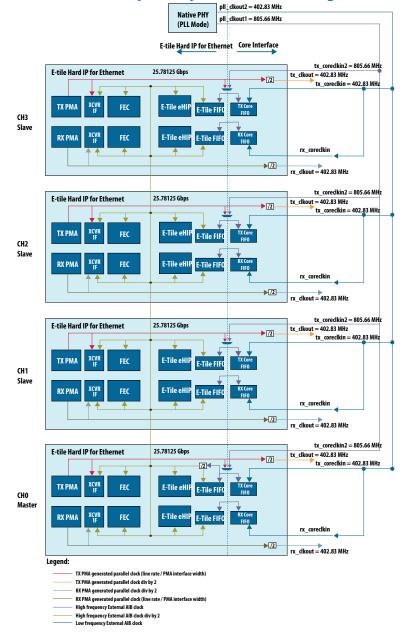

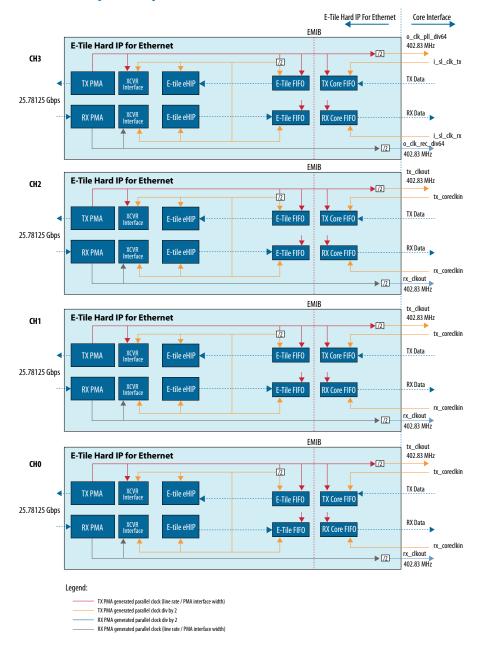

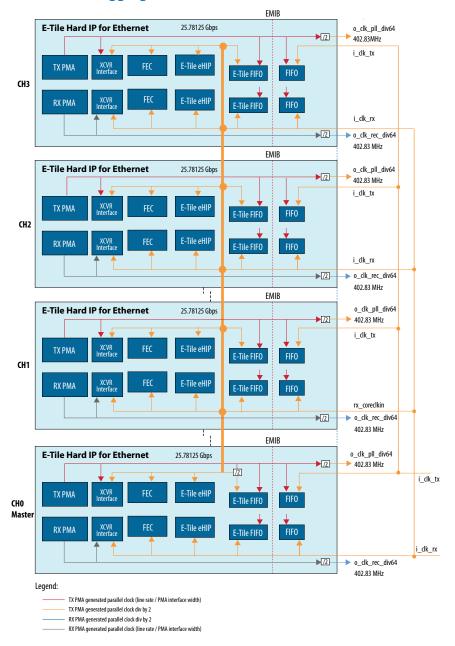

Figure 3. 1 to 4 10G/25G Channels with Optional RS-FEC

- This variant of the IP core includes up to four channels. Each channel has its own set of adapters, reconfiguration logic, AN/LT and reset sequencer logic.

- RS-FEC is optional for this variant.

Figure 4. 100G Channel with Optional RS-FEC

- This variant of the IP core includes a single 100G channel that has its own set of adapters, reconfiguration logic, AN/LT and reset sequencer logic.

- The deskew logic corrects for possible skew over the EMIB interfaces between the main die and the E-tile.

- RS-FEC is optional for this variant. You can select RS-FEC(528,514) or RS-FEC(544,514) for this variant.

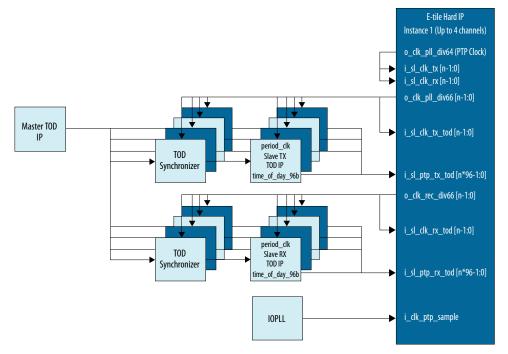

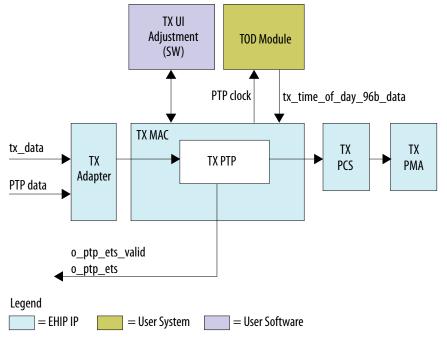

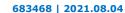

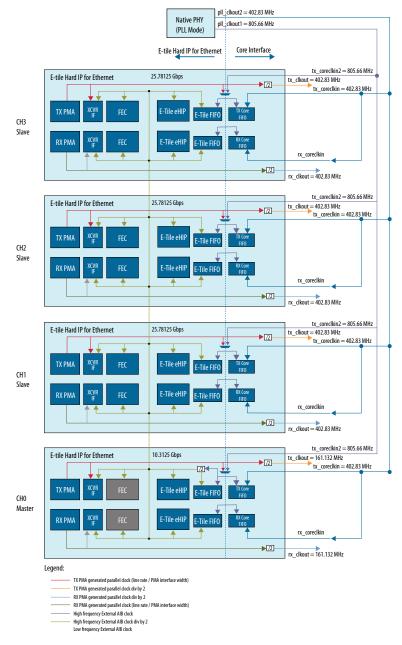

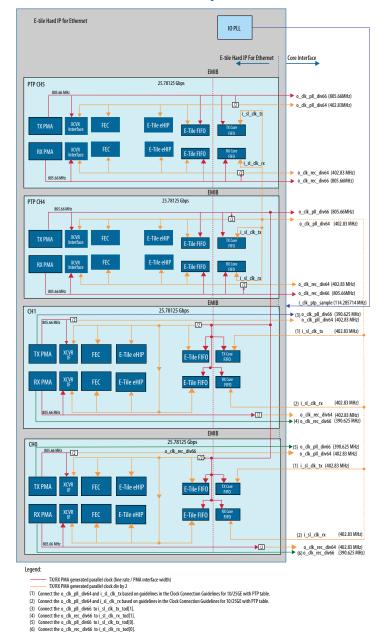

Figure 5. 100G Channel with 1 to 4 10G/25G Channels, RS-FEC, and Precision Time Protocol (PTP)

- This variant of the IP core includes a 100G channel or between 1 to 4 10G/25G channels.

- Because the 100G channel uses the same transceivers as the 10G/25G channels, you cannot use the 100G channel when any of the 10G/25G channels are running. You can switch the reconfiguration interfaces on the core between channels at run time.

- For this variant, each channel has its own set of adapters, reconfiguration logic, AN/LT and reset sequencer logic.

- The deskew logic corrects for possible skew over the EMIB interfaces between the main die and the E-tile. The EMIB deskew logic is always used for 100G channels. For 10G/25G channels, the deskew logic is used when you enable PTP, to ensure the PTP commands to each channel are synchronized to data. The deskew logic is not required for single 10G/25G channel.

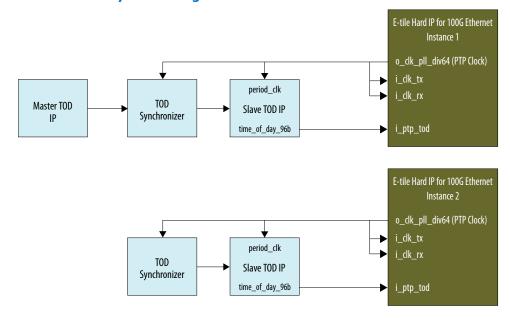

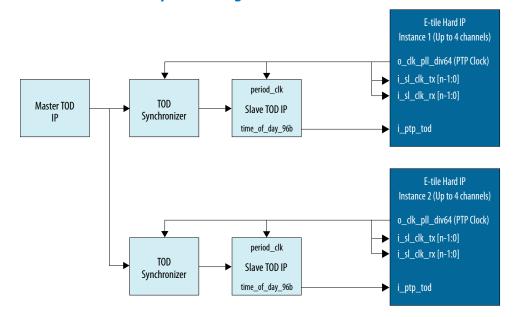

- The PTP soft component logic block provides the user PTP interface, performs the soft logic operations required for the E-tile timestamp system, and interacts with the TOD module (the Time-of-Day clock) that you provide.

- RS-FEC and PTP are optional for this variant. This variant only supports RS-FEC(528,514) with PTP enabled.

Figure 6. Custom PCS with Optional RS-FEC

- This variant of IP core supports customizable line rate PCS up to four channels. Each channel has its own set of adapters, reconfiguration logic, and reset sequencer logic. This variant does not include an Ethernet MAC.

- This variant supports transceiver line rates ranges from 2.5 to 28 Gbps used in other protocols.

- RS-FEC is optional for this variant and it supports RS-FEC for Ethernet and Fibre Channel modes.

## 2.3. IP Core Device Family and Speed Grade Support

The following sections list the device family and device speed grade support offered by the E-Tile Hard IP for Ethernet Intel FPGA:

E-Tile Hard IP for Ethernet Intel FPGA IP Device Family Support on page 17

E-Tile Hard IP for Ethernet Intel FPGA IP Device Speed Grade Support on page 17

## 2.3.1. E-Tile Hard IP for Ethernet Intel FPGA IP Device Family Support

## Table 5. Intel FPGA IP Core Device Support Levels

| Device Support<br>Level | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance                 | The IP core is available for simulation and compilation for this device family. Timing models include initial engineering estimates of delays based on early post-layout information. The timing models are subject to change as silicon testing improves the correlation between the actual silicon and the timing models. You can use this IP core for system architecture and resource utilization studies, simulation, pinout, system latency assessments, basic timing assessments (pipeline budgeting), and I/O transfer strategy (datapath width, burst depth, I/O standards tradeoffs). |

| Preliminary             | The IP core is verified with preliminary timing models for this device family. The IP core meets all functional requirements, but might still be undergoing timing analysis for the device family. It can be used in production designs with caution.                                                                                                                                                                                                                                                                                                                                           |

| Final                   | The IP core is verified with final timing models for this device family. The IP core meets all functional and timing requirements for the device family and can be used in production designs.                                                                                                                                                                                                                                                                                                                                                                                                  |

## Table 6. E-Tile Hard IP for Ethernet Intel FPGA IP Device Family Support

Shows the level of support offered by the E-Tile Hard IP for Ethernet Intel FPGA IP for each Intel FPGA device family.

| Device Family    | Support     |

|------------------|-------------|

| Intel Stratix 10 | Final       |

| Intel Agilex     | Preliminary |

### **Related Information**

Timing and Power Models

Reports the default device support levels in the current version of the Intel Quartus Prime Pro Edition software.

## 2.3.2. E-Tile Hard IP for Ethernet Intel FPGA IP Device Speed Grade Support

The E-Tile Hard IP for Ethernet Intel FPGA IP supports the following speed grades for Intel Stratix 10 and Intel Agilex E-tile devices:

Transceiver speed grade: -1, -2 or -3<sup>(2)</sup>

• Core speed grade: -1 or -2

For information about the applicable device speed grades based on the target data rates, refer to the *Device Data Sheet*.

<sup>(2)</sup> This speed grade only supports the 10G data rate.

#### **Related Information**

- Intel Stratix 10 Device Datasheet

- Intel Agilex Device Data Sheet

### 2.4. IP Core Verification

To ensure functional correctness of the E-Tile Hard IP for Ethernet Intel FPGA IP, Intel performs extensive validation through both simulation and hardware testing. Before releasing a version of the E-Tile Hard IP for Ethernet Intel FPGA IP, Intel runs comprehensive regression tests in the current version of the Intel Quartus Prime Pro Edition software.

Intel verifies that the current version of the Intel Quartus Prime Pro Edition software compiles the previous version of each IP core. Intel does not verify compilation with IP core versions older than the previous release.

### 2.4.1. Simulation Environment

Intel performs the following tests on the E-Tile Hard IP for Ethernet Intel FPGA IP in the simulation environment using internal and third party standard bus functional models (BFM):

- Constrained random tests that cover randomized frame size and contents

- Randomized error injection tests that inject Frame Check Sequence (FCS) field errors, runt packets, and corrupt control characters, and then check for the proper response from the IP core

- Assertion based tests to confirm proper behavior of the IP core with respect to the specification

- Extensive coverage of our runtime configuration space and proper behavior in all possible modes of operation

## 2.4.2. Compilation Checking

Intel performs compilation testing on an extensive set of E-Tile Hard IP for Ethernet Intel FPGA IP variations and designs that target different devices, to ensure the Intel Quartus Prime Pro Edition software places and routes the IP core ports correctly.

## 2.4.3. Hardware Testing

Intel performs hardware testing of the key functions of the E-Tile Hard IP for Ethernet Intel FPGA IP on available FPGA devices using standard 10/25, and 100 Gbps Ethernet network test equipment and optical modules. The Intel hardware tests of the E-Tile Hard IP for Ethernet Intel FPGA IP also ensure reliable solution coverage for hardware related areas such as performance, link synchronization, and reset recovery.

### 2.5. Resource Utilization

The resources for the E-Tile Hard IP for Ethernet Intel FPGA IP were obtained from the Intel Quartus Prime Pro Edition software version 19.1

**Table 7.** Resource Utilization for Selected Variations

| MAC+PCS   2,100   2,900   6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Ethernet Rate | IP Core Variation   | ALMs   | Dedicated Logic<br>Registers | Memory 20K |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------|--------|------------------------------|------------|

| 1588/PTP   PCS Only   1,918   2,484   4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10G           | MAC+PCS             | 2,100  | 2,900                        | 6          |

| OTN 1,936 2,505 4  FlexE 1,950 5,539 4  25G MAC+PCS 2,100 2,900 6  MAC+PCS with RS-FEC 2,400 3,400 6  MAC+PCS WITH RS-FEC and IEEE 1588/PTP  PCS Only 1,929 2,486 4  PCS with RS-FEC 2,308 3,073 4  OTN 1,922 2,537 4  OTN with RS-FEC 2,292 3,064 4  FlexE 1,915 2,475 4  FlexE 1,915 2,475 4  FlexE with RS-FEC 2,281 3,057 4  100G MAC+PCS with RS-FEC 2,281 3,057 4  INGO MAC+PCS 5,777 8,443 6  MAC+PCS S,777 8,443 6  MAC+PCS with (528,514) RS-FEC 6,016 8,739 6  MAC+PCS with (528,514) RS-FEC 1,012 2,013 4  PCS with (544,514) 2,668 3,217 4  RS-FEC 1,012 2,013 4  OTN with (528,514) RS-FEC 1,012 2,013 4  PCS with (544,514) 2,668 3,217 4  RS-FEC 1,012 2,013 4  OTN with (528,514) RS-FEC 1,012 2,013 4  PCS with (544,514) 2,668 3,217 4  RS-FEC 2,647 3,178 4  RS-FEC 0  OTN with (528,514) RS-FEC 1,012 2,013 4  PCS with (544,514) 2,668 3,217 4  RS-FEC 2,648 3,200 4  FlexE 2,400 2,929 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |                     | 5,500  | 11,700                       | 11         |

| FlexE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               | PCS Only            | 1,918  | 2,484                        | 4          |

| 25G MAC+PCS 2,100 2,900 6  MAC+PCS with RS-FEC  MAC+PCS SIEEE 5,500 11,700 11  MAC+PCS with RS-FEC 3,500 11,700 11  MAC+PCS with RS-FEC 5,500 11,700 11  MAC+PCS with RS-FEC 1,929 2,486 4  PCS with RS-FEC 2,208 3,073 4  OTN 1,922 2,537 4  OTN with RS-FEC 2,292 3,064 4  FlexE 1,915 2,475 4  FlexE with RS-FEC 2,281 3,057 4  100G MAC+PCS 5,777 8,443 6  MAC+PCS 5,777 8,443 6  MAC+PCS with (528,514) RS-FEC 6,016 8,739 6  MAC+PCS with (528,514) RS-FEC 6,029 8,827 6  MAC+PCS with (544,514) RS-FEC 6,010 2,913 4  PCS with (544,514) RS-FEC 70 2,668 3,217 4  OTN 2,401 2,905 4  OTN 2,401 2,905 4  OTN with (528,514) RS-FEC 70 2,647 3,178 4  CTN with (528,514) RS-FEC 70 2,648 3,200 4  FlexE 2,400 2,929 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               | OTN                 | 1,936  | 2,505                        | 4          |

| MAC+PCS with RS-FEC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               | FlexE               | 1,950  | 5,539                        | 4          |

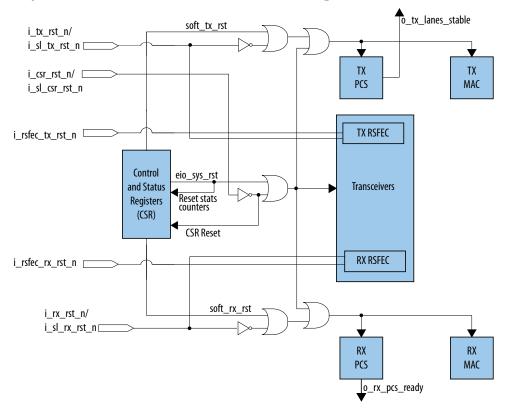

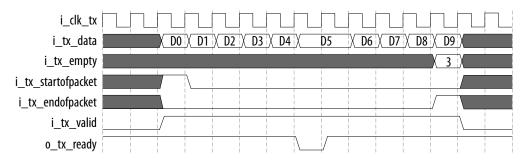

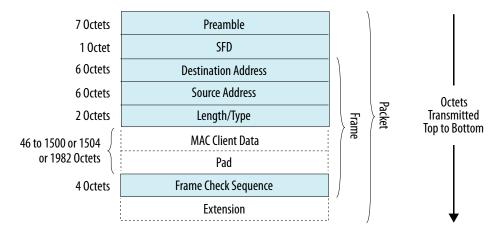

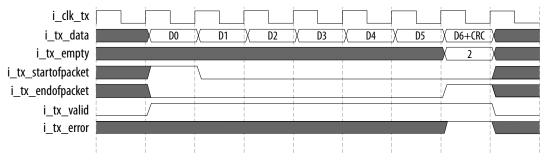

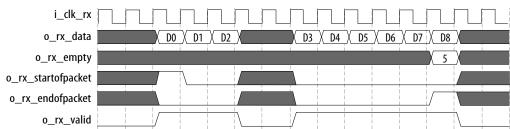

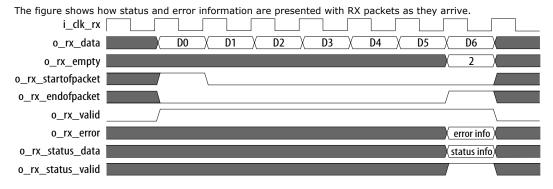

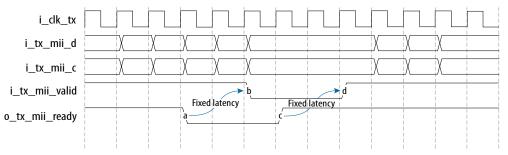

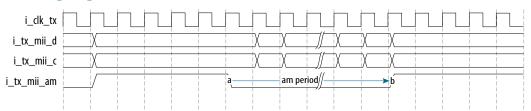

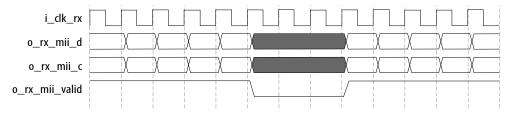

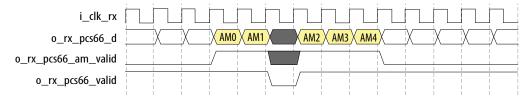

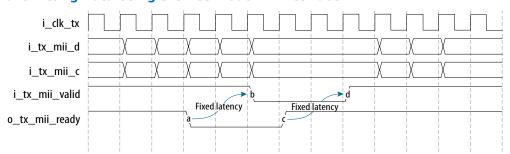

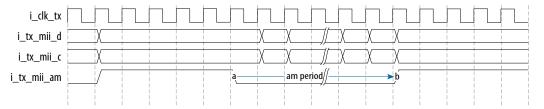

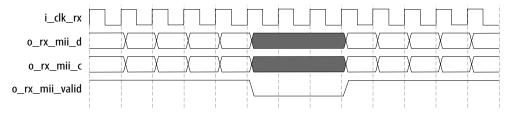

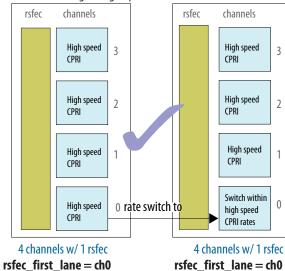

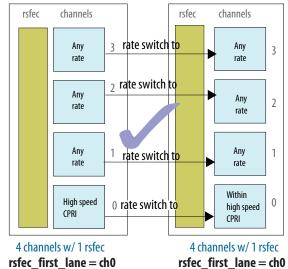

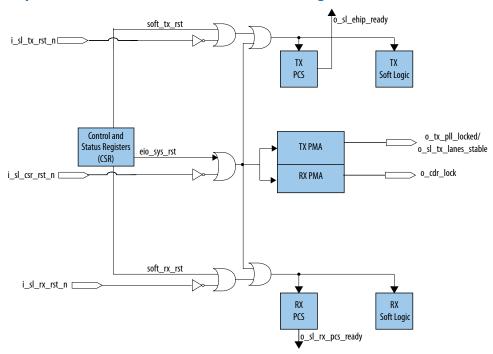

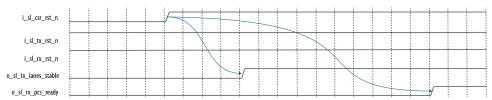

| Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25G           | MAC+PCS             | 2,100  | 2,900                        | 6          |