# Nios II Embedded Evaluation Kit, Cyclone III Edition

# **User Guide**

101 Innovation Drive San Jose, CA 95134 www.altera.com

P25-36209-03

Document Date:

July 2010

© 2010 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX are Reg. U.S. Pat. & Tm. Off. and/or trademarks of Altera Corporation in the U.S. and other countries. All other trademarks and service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

# **Contents**

| Chapter 1. Getting Started                                          |      |

|---------------------------------------------------------------------|------|

| Introduction                                                        | 1-1  |

| Kit Contents                                                        | 1–2  |

| About the Nios II Processor                                         | 1–3  |

| About the Nios II Standard Design                                   | 1–3  |

| About this User Guide                                               | 1–6  |

| Before You Begin                                                    | 1–7  |

| Software Installation                                               |      |

| Installing the Nios II Embedded Evaluation Kit, Cyclone III Edition | 1–7  |

| Installing the Quartus II Web Edition Software                      | 1-9  |

| Licensing the IP                                                    | 1–11 |

| Licensing the EL Camino SD Card Core                                | 1–13 |

| Chapter 2. Development Board Setup                                  |      |

| Features                                                            | 2-1  |

| Requirements                                                        | 2-2  |

| Power Up the Development Board                                      | 2-2  |

| Chapter 3. Nios II Processor Systems                                |      |

| Where to find the Nios II Processor Systems                         | 3–3  |

| Nios II 3C25 Standard Processor System                              |      |

| Nios II 3C25 Video Processor System                                 |      |

| Chapter 4. Application Selector Utility                             |      |

| Overview                                                            | 4–1  |

| Ready-to-Run SD Card Demonstrations                                 |      |

| Running the Application Selector                                    |      |

| In system Update using SD Card                                      |      |

| Remote System Update using Ethernet                                 |      |

| About Remote System Update                                          |      |

| Requirements                                                        |      |

| Operating Instructions                                              |      |

| Creating Flash files for Remote System update                       |      |

| Chapter 5. Design Examples                                          |      |

| About Design Examples                                               | 5–1  |

| Picture Viewer Application                                          |      |

| Picture Viewer                                                      |      |

| Operation                                                           |      |

| Mandelbrot Application                                              |      |

| Using the Mandelbrot application                                            | 5–7  |

|-----------------------------------------------------------------------------|------|

| Operation                                                                   |      |

| Application Selector                                                        |      |

| About the Embedded Web Server                                               | 5–14 |

| Appendix A. Video Pipeline Data Flow                                        |      |

| Introduction                                                                | A-1  |

| Get the full LCD controller Application Note                                | A-2  |

| Creating a new 5:6:5 Pixel-Format component                                 | A-2  |

| Appendix B. Application Selector Details                                    |      |

| SD Card                                                                     | В–1  |

| Application Files                                                           |      |

| SD Card Directory Structure                                                 |      |

| CFI Flash                                                                   |      |

| Hardware images                                                             |      |

| Software Images                                                             |      |

| Application Boot Code                                                       |      |

| Flash Hardware Image Catalog                                                |      |

| Hardware Image Caching                                                      |      |

| Flash Hardware Image Catalog                                                |      |

| Creating Your Own Loadable Applications                                     |      |

| Rebuilding the Application Selector                                         |      |

| Create a BSP                                                                |      |

| Build the project                                                           |      |

| Build the boot code                                                         |      |

| Modifying the Application Selector                                          |      |

| Changing the CFI flash map                                                  | В–9  |

| Annoydiy C. Dostoviny the Fostow Image                                      |      |

| Appendix C. Restoring the Factory Image                                     |      |

| Restoring the Original Flash Image (Application Selector)                   | C-1  |

| Rebuilding the Application Selector from Source Files                       |      |

| Boot Code                                                                   |      |

| Hardware Image Catalog                                                      |      |

| Application Selector Hardware Image                                         |      |

| Application Selector Software Image                                         |      |

| Combining factory recovery image files                                      | C–4  |

| Appendix D. Frequently Asked Questions                                      |      |

| Why is my SOF time-limited?                                                 |      |

| What are Ready-to-Run Demonstrations?                                       |      |

| Where can I find Ready-to-Run Demonstrations?                               |      |

| What is in a ready-to-run demonstration?                                    |      |

| How do ready-to-run demonstrations get loaded from the SD card to the FPGA? |      |

| Where can I get more ready-to-run demonstrations?                           | D-2  |

| Where can I get full Quartus II projects and source code for ready-to-run   |      |

| demonstrations?                                                             | D-2  |

|    | Why do I get the error "Can't find valid feature line for core SD_MMC_SPI_CORE  |      |

|----|---------------------------------------------------------------------------------|------|

|    | (EC11_0002) in current license;                                                 |      |

|    | Error: Error (10003): Can't open encrypted VHDL or Verilog HDL file" when I try |      |

|    | to re-generate the Nios II Standard hardware design?                            | D-3  |

|    | Where can I get the SD-Card Controller IP License?                              | D-3  |

|    | How do I add pictures so the Picture Viewer Application can find them?          | D-3  |

|    | How do I add my own design so the Application Selector can find and run it?     |      |

|    | Where do I go to get more designs for the Nios II Embedded Evaluation Kit?      | D-4  |

|    | How do I open a design example in the Nios II IDE?                              | D-4  |

|    | How do I restore the factory image?                                             | D-5  |

|    | How do I re-build the factory image?                                            | D-5  |

|    | , 0                                                                             |      |

|    |                                                                                 |      |

| Ad | Iditional Information                                                           |      |

|    | Further Information                                                             | i–ii |

Contents Contents

# 1. Getting Started

#### Introduction

The Altera® Nios® II Embedded Evaluation Kit, Cyclone® III Edition includes a full-featured FPGA development board, LCD Multimedia High Speed Mezzanine Card (HSMC), hardware and software development tools, documentation, and accessories needed to begin embedded and system on a programmable chip (SOPC) designs using FPGAs.

The development board includes an Altera Cyclone III FPGA and comes preconfigured with an FPGA hardware reference design stored in flash memory as well as several ready-to-run demonstration applications stored on the SD-Card Flash provided. Hardware designers can use the FPGA reference design as a platform to build complex embedded systems. Software developers can use the hardware reference design plus sample software applications as a starting point for their own applications.

Success for an embedded system start rights from the evaluation stage. Choosing the right platform, development tools, operating systems may be the difference between success and failure. The Altera Nios II Embedded Evaluation Kit, Cyclone III Edition is an evaluation kit that enables you to make these critical decisions with minimal investment.

The Nios II Embedded Evaluation Kit, Cyclone III Edition makes evaluating Altera's embedded solutions easy. Processor systems targeting the low-cost, low-power Cyclone III FPGA can be evaluated by simply using the LCD Color Touch Panel to scroll through and load your demonstration of choice.

These processor systems showcase the unique benefits of FPGA-based processors such as reducing BOM costs by integrating powerful graphics engines within the FPGA, reducing operating costs by upgrading your system over the Internet, or increasing system performance while reducing power using C-to-Hardware (C2H) acceleration.

#### **Kit Contents**

The Nios II Embedded Evaluation kit will acquainting you with the Nios II processor, the hardware and software development flows and the robust embedded ecosystem of operating systems, middleware, IP and third party offerings that support the Nios II processor.

To this end the kit features:

- Pre-built embedded processor systems that serve as starting points to accelerate hardware development

- Nios II Standard Processor System (Standard)

- Nios II Video Based Embedded Processor System (Video)

- Pre-built embedded applications with source code to serve as examples for software device driver development

- Altera Application Selector with embedded Web Server

- Altera Picture Viewer

- Altera Mandelbrot

- Hardware and Software Tutorials to learn the embedded development flows

- My first FPGA design

- My first Nios II Software tutorial

- Ready-to-Run Demonstration applications from Altera's partners

- IP: SD Card Controller (El Camino), Graphics Engines (TES, Imagem, PlanetWeb)

- Operating systems: MicroC-OS II (Micrium Evaluation Licenses) , uC-Linux (SLS)

- Middleware: Filesystems (El Camino, Micrium, SLS), Graphics Libraries (Micrium)

- Altera Evaluation IP license cores and software packages for embedded development

- Nios II IP Core (Evaluation Core)

- DDR SDRAM Memory IP Core (Evaluation Core)

- TSE MAC IP Core (Evaluation Core)

- NicheStack TCP-IP Network Stack, Nios II Edition (Evaluation Core)

#### About the Nios II Processor

Nios II is a fully configurable 32-bit processor optimized for use in Altera's FPGA. The embedded processor system is easily customized for a particular application using the SOPC Builder feature of the Quartus II FPGA design software.

Assembling a microprocessor system involves four elements:

- 1. Adding and configuring of the core processor and memory

- 2. Adding peripherals such as memory interfaces, I/O, or interfaces to external devices (such as the LCD Display)

- Connecting the I/O pins of the processor in the FPGA to the external devices

- 4. Writing C/C++ software application for your custom processor with the Nios II Embedded Design Suite.

In the vast majority of cases, hardware design can be accomplished using drop-down menus and drag and drop operations in SOPC Builder. The sophistication of Altera's designs tools brings creating custom hardware processor systems within the reach of embedded developers.

#### **About the Nios II Standard Design**

The starter reference design for the board entitled "standard" is located in the altera\<version #>\kits\ cycloneIII\_3c25\_niosII\examples folder. The Nios II "standard" is a SOPC Builder system featuring the Nios II processor and common peripherals that has been put together for you. Hardware designers can accelerate their SOPC Builder system development by using the Nios II Standard design example as a starting point. The board boots up with this pre-built design, so software developers can use it for software development without having to concern themselves with the details of generating the FPGA hardware system.

The Nios II Standard System is a pre-generated hardware system that includes:

- Nios II core (32-bit soft processor) Application

- LCD Controller

- Multi-port memory controllers

Communication Interface controllers

#### About the Nios II System Designs

A Nios II system design builds upon a Nios II processor system by including a software application that runs on the processor system.

Software developers can use system designs to see examples of software drivers for the hardware peripherals. Nios II Embedded Evaluation kit contains several system design examples:

- Altera Application Selector

- Altera Picture Viewer

- Altera Mandelbrot C2H

Designs are located in the altera\<version

#>\kits\cycloneIII\_3c25\_niosII in either the examples or

demonstrations directory. You can also find more system

designs from the Nios II Embedded Evaluation Kit (NEEK),

Cyclone III Edition page.

#### About the Demonstrations

In the Nios II I Embedded Evaluation Kit directory, there is a **demos** folder (refer to Figure 1–1 on page 1–8). This is a repository of pre-built example Nios II based processor systems that have been provided for demonstration and evaluation purposes only.

#### How are the demonstrations different from design examples?

Design examples (located in the <*Install Dir*>\examples folder) are prebuilt processor systems that can be used as a starting point for your design.

- Hardware Design Examples: Quartus II projects with pre-generated SOPC Builder systems featuring the Nios II processor (for example, standard)

- System Design Examples: These build upon hardware design examples and include applications and source codes that show examples of software device drivers, operating system usage, and application selector.

**Demonstrations** (located in <*Install Dir*>\demos directory) are pregenerated SOPC Builder systems for evaluation purposes only and are not guaranteed to be updated with each release of the Quartus II software. When source-code is provided, recompiling a demonstration application from this directory may or may not work with the Quartus II

version that was pointed to by the development kit documentation. Any source-code provided should be viewed as diagramatic but not necessarily functional.

Ready-to-run demonstrations are binaries that provide a quick and easy way to demonstrate and evaluate operating systems, middleware, IP and software tools for your Nios II processor system. These demonstrations are easily selected and loaded using the application selector on your LCD touch panel. These demonstrations are implementations of applications such as automotive graphics, consumer GUI, industrial control that are provided for demonstration and evaluation purposes by Altera and third party vendors.

If you want to select a suitable operating system (for example, Micriums uC-OS II or SLS's port of uC-Linux for Nios II), a particular IP core (for example, SD Card core or high performance vector graphics engine), middleware libraries (for example, Networks Stacks, Graphics Library) or graphics development tools (for example, PlanetWeb SpectraWorks, Altia Design), then the ready-to-run demonstrations help you make your evaluation process easy.

Ready-to-run demonstrations are provided in binary format only (.flash), full Quartus II projects, source code, and IP licensing and can be obtained by contacting the provider of the ready-to-run demonstrations. You can locate these demonstrations on your SD Card. Alternatively, you can download the latest ready-to-run demonstrations from the Nios II Embedded Evaluation Kit (NEEK), Cyclone III Edition page.

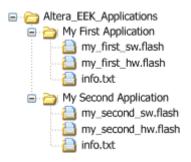

To add ready-to-run demonstrations to your SD Card, download the demonstration and copy it to your SD Card in the **Altera\_EEK\_applications** folder.

Table 1–1 list ready-to-run demonstration applications.

| Table 1–1. List of Example Applications (Part 1 of 2) |        |  |  |

|-------------------------------------------------------|--------|--|--|

| Demonstration                                         | Vendor |  |  |

| Application Selector/Web Server                       | Altera |  |  |

| Altera Picture Viewer                                 | Altera |  |  |

| Altera Mandelbrot C2H                                 | Altera |  |  |

| Altera Spinning Cube                                  | Altera |  |  |

| Imagem Tacquin Game                                   | Imagem |  |  |

| Imagem Watch                                          | Imagem |  |  |

| Imagem Avionics                                       | Imagem |  |  |

| Table 1–1. List of Example Applications (Part 2 of 2) |           |  |  |

|-------------------------------------------------------|-----------|--|--|

| Demonstration                                         | Vendor    |  |  |

| uC-GUI Demonstration                                  | Micrium   |  |  |

| Photo Frame PlanetWeb                                 | PlanetWeb |  |  |

| SpectraWorks GUI Demonstration by PlanetWeb           | PlanetWeb |  |  |

| DAVE 2D Graphics Demonstration                        | TES       |  |  |

| Altia Red HMI                                         | Altia     |  |  |

| Altia Blue HMI                                        | Altia     |  |  |

| Imagem aPhone                                         | Imagem    |  |  |

| Imagem 2-D Demonstration                              | Imagem    |  |  |

| Imagem Instrumentation                                | Imagem    |  |  |

| SLS uClinux                                           | SLS       |  |  |

| PlanetWeb Menu                                        | PlanetWeb |  |  |

# About this User Guide

This user guide describes how to start using the Altera Nios II Embedded Evaluation Kit, including unpacking the kit, installing required software, and running the Application Selector utility and other design examples. This user guide addresses the following topics:

- How to set up, power up, and verify correct operation of the Nios II Embedded Evaluation board

- Nios II standard processor system for the Embedded Evaluation board

- How to install the Nios II Embedded Evaluation Kit, Cyclone III Edition

- How to install the Altera Quartus II Web Edition software

- How to start and run the Application selector utility

- Design examples

- Taking the next step

- Frequently asked questions

For a full description of the development boards and their design and use, refer to the *Cyclone III FPGA Starter Board Reference Manual* and *LCD Multimedia HSMC Reference Manual*.

This user guide provides an overview of some of the applications. For more information about key hardware components and the structure of the application selector utility, refer to Appendix A, Video Pipeline Data Flow, Appendix B, Application Selector Details, Appendix C, Restoring

the Factory Image, and Appendix D, Frequently Asked Questions. However, we opted to provide extensive source-code comments rather than formal documentation regarding the other applications.

We are interested in knowing if this structure for the documentation is adequate for you to be able to develop your applications. If you have comments or suggestions on what we can do to improve the user experience through our documentation, contact us through nios\_docs@altera.com.

To ensure that you have the most up-to-date information on this product, refer to the Nios II Embedded Evaluation Kit (NEEK), Cyclone III Edition page.

#### **Before You Begin**

Before proceeding, check the contents of the kit:

- Nios II Embedded Evaluation Board

- Cables and accessories

### Software Installation

This section describes the following procedures:

- "Installing the Nios II Embedded Evaluation Kit, Cyclone III Edition"

- "Installing the Quartus II Web Edition Software" on page 1–9

- "Licensing the IP" on page 1–11

- "Licensing the EL Camino SD Card Core" on page 1–13

# Installing the Nios II Embedded Evaluation Kit, Cyclone III Edition

The license-free Nios II Embedded Evaluation Kit, Cyclone III Edition installer includes all the documentation and design examples for the kit.

To install the Nios II Embedded Evaluation Kit, Cyclone III Edition, follow these steps:

Download the Nios II Embedded Evaluation Kit, Cyclone III Edition installer from the Nios II Embedded Evaluation Kit (NEEK), Cyclone III Edition page of the Altera website. Alternatively, you can request a development kit DVD from the Development Kits, Daughter Cards & Programming Hardware page of the Altera website. 2. Follow the on-screen instructions to complete the installation process.

The installation program creates the Nios II Embedded Evaluation Kit, Cyclone III Edition directory structure shown in Figure 1–1.

Figure 1–1. Nios II I Embedded Evaluation Kit Installed Directory

Structure

<install dir>

The default Windows installation directory is C:\altera\<version>\.

kits

cycloneIII\_3c25\_niosII

board\_design\_files

demos

documents

examples

factory\_recovery

Table 1–2 lists the file directory names and a description of their contents.

| Table 1–2. Installed Directory Contents (Part 1 of 2) |                                                                                              |  |  |

|-------------------------------------------------------|----------------------------------------------------------------------------------------------|--|--|

| Directory Name                                        | Description of Contents                                                                      |  |  |

| board_design_files                                    | Contains schematic, layout, assembly, and bill of material board design files.               |  |  |

| demos                                                 | Contains a repository of example designs that may be useful for demonstration or evaluation. |  |  |

| Table 1–2. Installed Directory Contents (Part 2 of 2) |                                                                                                                                                                                                   |  |  |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Directory Name                                        | Description of Contents                                                                                                                                                                           |  |  |

| documents                                             | Contains the Nios II Embedded Evaluation Kit,<br>Cyclone III Edition documentation, including<br>hardware and software tutorials.                                                                 |  |  |

| examples                                              | Contains design examples for the Nios II Embedded Evaluation Kit, Cyclone III Edition, Application Selector Utility, and Nios II Embedded Evaluation Standard hardware system.                    |  |  |

| factory_recovery                                      | Contains ready-to-run demonstrations stored on the SD Card as well as Flash image files required to restore the factory default state, presentations and Web page content served up by the board. |  |  |

#### Installing the Quartus II Web Edition Software

The Quartus II Web Edition software provides the necessary tools for developing hardware and software for Altera FPGAs. Included in the Quartus II Web Edition software are the Quartus II software, the Nios II EDS, and the MegaCore® IP Library. The Quartus II software (including SOPC Builder) and the Nios II EDS are the primary FPGA development tools for creating the reference designs in this kit.

To install the Quartus II Web Edition software, follow these steps:

- Download the Quartus II Web Edition software from the Quartus II

Web Edition Software page of the Altera website. Alternatively, you

can request a DVD from the Altera IP and Software DVD Request

Form page of the Altera website.

- 2. Follow the on-screen instructions to complete the installation process.

If you have difficulty installing the Quartus II software, refer to *Quartus II Installation & Licensing for Windows and Linux Workstations*.

The Quartus II Web Edition software includes the following items:

- The Quartus II software—The Quartus II software, including the SOPC Builder system development tool, provides a comprehensive environment for system-on-a-programmable-chip (SOPC) design. The Quartus II software integrates into nearly any design environment and provides interfaces to industry-standard EDA tools.

- To compare the Quartus II subscription and web editions, refer to *Altera Quartus II Software—Subscription Edition vs. Web Edition*. The kit also works with the subscription edition.

- MegaCore IP Library—A library that contains Altera IP MegaCore functions. You can evaluate MegaCore functions with the OpenCore Plus feature to do the following tasks:

- Simulate behavior of a MegaCore function in your system

- Verify functionality of your design, and quickly and easily evaluate its size and speed

- Generate time-limited device programming files for designs that include MegaCore functions

- Program a device and verify your design in hardware

- The OpenCore Plus hardware evaluation feature is an evaluation tool for prototyping only. You must purchase a license to use a MegaCore function in production.

- For more information about OpenCore Plus, refer to *AN 320: OpenCore Plus Evaluation of Megafunctions*.

- Nios II Embedded Design Suite (EDS)—A full-featured tool set that allows you to develop embedded software for the Nios II processor which you can include in your Altera FPGA designs.

#### Licensing Considerations

The Quartus II Web Edition software is license-free and supports Cyclone III devices without any additional licensing requirement. This kit also works with the Quartus II Subscription Edition software, after you obtain the proper license file. To purchase a subscription, contact your Altera sales representative.

#### Licensing the IP

After installing the Quartus II Web Edition software, you will have installed an OpenCore Plus evaluation of the Nios II IP core. Any designs you create operate in Altera's OpenCore Plus evaluation mode and allow you to do the following:

- 1. Simulate the behavior of the Nios II processor IP in your system.

- 2. Verify the functionality of your design, as well as evaluate its size and speed quickly and easily.

- 3. Generate time-limited device programming files for designs that include a Nios II processor.

- 4. Program a device and verify your design in hardware.

OpenCore Plus hardware evaluation supports the following two modes of operation:

**Tethered**—requires a JTAG connection between your board and the host computer. If tethered mode is supported by all megafunctions in a design, the device can operate for a longer time or indefinitely.

**Untethered**—the design runs for a limited time.

To ship designs with the Nios II IP Core you need to obtain a license for the Nios II IP (IP-NIOS). To obtain a license you can:

- Contact your local Altera representative at www.altera.com/corporate/contact/con-index.html

- Use the Altera Tools Support at www.altera.com/corporate/contact/info/con-phone.html to order today.

**Nios II Processor**—To obtain a non-time-limited use license file for the Nios II processor, you must purchase a stand-alone Nios II processor core license (ordering code: IP-NIOS). Contact your local Altera representative or Altera Tools Support to order today.

Nios II C2H Compiler—You can create, compile, and generate timelimited Nios II processor systems and hardware accelerators generated by the Nios II C2H Compiler without obtaining a license file with the OpenCore Plus evaluation feature. You must obtain a license for the Nios II processor core (ordering code: IP-NIOS) and Nios II C2H Compiler (ordering code: IPT-C2H-NIOS) to generate non-time-limited programming files and flash programming files. Contact your local Altera representative or use the Altera Tools Support to order today. You do not need a license if you are developing software with the Nios II IDE.

NicheStack TCP/IP Stack–Nios II Edition—You can develop software for any of the Nios II development kits using the NicheStack TCP/IP Stack, Nios II Edition evaluation. To generate software to run on other boards and/or ship in a product, you must obtain a license (ordering code: IPSW-TCP/IP-NIOS). Contact your local Altera representative or Altera Tools Support to order today.

Micrium MicroC/OS-II RTOS— You can develop software for any of the Nios II development kits using the Micrium MicroC/OS-II RTOS. To generate software to run on other boards, ship in a product, or both, you must obtain a license. To obtain a license for the Micrium MicroC/OS-II RTOS, contact Micrium today.

**Altera IP Base Suite**— A high performance memory controller for the on-board DDR SDRAM memory is available from Altera.

- Finite Impulse Response (FIR) Compiler

- Fast Fourier Transform (FFT) Compiler

- Numerically Controlled Oscillator (NCO) Compiler

- DDR SDRAM Controller

- DDR SDRAM High-Performance Controller

- DDR2 SDRAM Controller

- DDR2 SDRAM High-Performance Controller

- DDR3 SDRAM High-Performance Controller

- QDRII SRAM Controller

- RLDRAM II Controller

- SerialLite II

To help shorten your design time, Altera provides some of its most popular intellectual property (IP) cores with the Altera IP Base Suite, which is completely free with a Quartus II subscription.

For more information about obtaining the Altera IP Base Suite, refer to the Free IP Base Suite Licenses With Active Quartus II Subscription page.

#### **Licensing the EL Camino SD Card Core**

The Nios II Standard hardware design contains the SD MMC SPI CORE which is a component that has been provided by a third party vendor, El Camino. To compile this core in your SOPC Builder system, you must obtain a license from El Camino.

However, if your particular application has no need to access the SD Card then you do not need to include the SD Card core in your system. Simply uncheck this core or delete it and regenerate the system. You should now be able to rebuild the hardware system without error.

If your design requires access to the on-board SD Card then you can request an evaluation license or purchase the SD-Card Controller IP, drivers and FAT File system from El Camino.

El Camino GmbH Landshuter Str. 1 D-84048 Mainburg Germany Tel. +49 - 8751 - 8787 - 0 Fax +49 - 8751 - 842876 Web: www.elcamino.de

E-mail: info@elca.de

# 2. Development Board Setup

#### **Features**

The Nios II Embedded Evaluation Kit features:

- Cyclone III Starter Board

- Cyclone III EP3C25F324 FPGA

- Configuration

- Embedded USB-Blaster<sup>™</sup> circuitry (includes an Altera EPM3128A CPLD) allowing download of FPGA configuration files via the users USB port

- Power and analog devices from Linear Technology

- Memory

- 256-Mbit DDR SDRAM

- 1-Mbyte Synchronous SRAM

- 16-Mbytes Intel P30/P33 flash

- Clocking

- 50-MHz on-board oscillator

- Switches and indicators

- Six push buttons total, 4 user controlled

- Four user-controlled LEDs

- LCD Daughtercard

- LCD Touch-screen Display

- 800 X 480 pixel size

- 10-bit VGA DAC

- Video Decoder

- 24-bit Audio Codec

- RS232 transceiver

- SD Flash

- 10/100 Mbps Ethernet Controller (PHY)

- Connectors

- VGA Output

- Composite Video in

- Serial connector (RS-232 DB9 port)

- PS/2

- Ethernet Connector (RJ 45)

- SD Card Socket

## Requirements

If not already installed, you should:

- Install the Quartus II Web Edition software on the host computer. For more information, refer to "Installing the Quartus II Web Edition Software" on page 1–9.

- Install the Nios II Embedded Evaluation Kit, Cyclone III Edition. For more information, refer to "Installing the Nios II Embedded Evaluation Kit, Cyclone III Edition" on page 1–7.

- Install the USB-Blaster<sup>™</sup> driver software on the host computer. The Cyclone III FPGA starter development board includes integrated USB-Blaster circuitry for FPGA programming.

The USB Blaster driver software is provided with the Quartus II software installation. Communication between the host computer and the development board requires that the USB-Blaster driver software be set up.

# Power Up the Development Board

To power up the development board, perform the following steps:

- 1. Ensure that the red on/off switch (SW1) on the back-side of the development board is in the **OFF** position (up).

- 2. Connect the USB-Blaster cable from the host computer to the USB-Blaster port on the development board.

- 3. Connect the 12-V DC adapter to the development board and to a power source.

Only use the supplied 12-V power supply. Power regulation circuitry on the board could be damaged by supplies greater than 12 V.

- 4. Press the **Power Switch** (SW1).

- 5. A Welcome screen appears as shown in Figure 2–1.

Figure 2–1. Development Board Setup - Welcome Screen

# 3. Nios II Processor Systems

The board in the Nios II Embedded Evaluation kit is comprised of the components shown in the Figure 3–1 below.

Cyclone III FPGA LCD Multimedia Starter Board Daughtercard 24-Bit Audio Codec Cyclone III FPGA MAX II CPLD DDR SDRAN S 10-bit VGA Video DAC C Video Decoder **SSRAM** С PS/2 & RS-232 Ports Nios II Bus 0 Processor Controlle System Touch Panel Module n CFI Flash е 10/100 Ethernet PHY С SD Card **Buttons** O I2C EEPROM **LEDs**

Figure 3–1. Block Diagram of Nios II Embedded Evaluation Kit, Cyclone III Edition

If you examine your Nios II Embedded Evaluation Kit, Cyclone III Edition, you will find that it is comprised of 2 boards, the Cyclone III FPGA Starter Board and the LCD Multimedia Daughtercard. On the Cyclone III FPGA Starter board resides the Cyclone III 3c25 FPGA which configures from flash with the Nios II Standard Processor System on startup.

The HSMC Connector shown in Figure 3–1 is actually a flex extension cable with HSMC connectors on each end going between the two boards. This detail was removed for simplicity.

On the LCD Multimedia Daughtercard resides a MAX II CPLD whose function is to relay data and control signals to the various peripheral devices as shown in the Figure 3–1. The MAX II CPLD performs voltage translation and de-multiplexing of video pipeline signals to the LCD

Touch panel. The video pipeline signals have been multiplexed inside the FPGA and de-multiplexed by the MAX II CPLD to provide a full range of functionality on the daughter card over a limited number of pins on the HSMC connector. (see the *LCD Multimedia Daughtercard Reference Manual* for details)

Within the FPGA is the Nios II Video Processor System. It is a pregenerated Nios II processor based hardware system that can be used as a starting point for embedded application development. The components in this embedded microprocessor system are shown in Figure 3–2.

Figure 3-2. Nios II Processor System Block Diagram

| Nios II Embedded Evaluation Standard Hardware |                          |                                   |                            |                                  |                                 |

|-----------------------------------------------|--------------------------|-----------------------------------|----------------------------|----------------------------------|---------------------------------|

| Memory Interface                              |                          | CPU Platform                      |                            | Communications Interface         |                                 |

| 1 MB<br>SSRAM                                 | 256 Mbit<br>DDR<br>SDRAM | Nios II <i>I</i> f<br>CPU<br>Core | JT AG<br>Debug             | JTAG<br>UART                     | UART                            |

| 16 MB<br>Flash                                | 128 MB<br>SD Card        | 32 KB<br>I-Cache                  | 32 KB<br>D-Cache           | SPI                              | 10/100<br>Ethernet              |

|                                               | System Functions         |                                   |                            |                                  | Pipeline                        |

| Button<br>PIO                                 | LED<br>PIO               | PLL                               | Perfrom<br>ance<br>Counter | PIO for<br>LICD I2C<br>Interface | Pixel<br>Converter              |

| PIO for<br>ID<br>EEPROM<br>(I2C)              | System<br>Clock<br>Timer | System<br>ID                      | Remote<br>Update           | Sync<br>Generator                | Touch<br>panel SPI<br>Interface |

# Where to find the Nios II Processor Systems

There are two pre-generated processor systems that target the Nios II Embedded Evaluation Kit:

#### Nios II 3C25 Standard Processor System

#### Location

You can locate the Nios II 3C25 Standard Processor System in the *<install dir>*/examples/standard folder.

#### **Description**

Simple general purpose Nios II processor system targeted for the Nios II Embedded Evaluation Kit, Cyclone III Edition to be used as a starting point for your embedded system development.

#### IP licenses required to ship design

- Nios II IP evaluation license with Nios II EDS, shipping license from Altera

- DDR SDRAM memory controller core shipping license from Altera (comes free with Quartus II Subscription edition as part of Altera IP Base Suite)

For more information on how to obtain evaluation or shipping licenses for the above refer to "Licensing the IP" on page 1–11.

#### About the Nios II 3C25 Standard Processor

The Nios II 3C25 Standard processor is a general purpose processor system to be used as a starting point for your system design and contains:

- Nios II /f CPU

- PLL

- DDR SDRAM Memory Controller

- SSRAM Memory Controller

- CFI Flash Controller

- JTAG UART

- Remote System Update

- Performance Counter

- System Clock Timer

- High Resolution Timer

- LED PIO

- Button PIO

#### Nios II 3C25 Video Processor System

#### Location

You can locate the Nios II 3C25 Video Processor System in the *<install dir>*/examples/video folder.

#### **Description**

Video, Ethernet and SD Card controller based processor system for LCD Color touch panel control, in-system update using SD Card, remote system update using Ethernet

#### IP licenses required to ship design

- SD/MMC SPI Core IP (with FAT file system) from El Camino

- Triple Speed Ethernet-MAC Core license from Altera

- Nios II IP evaluation license with Nios II EDS, shipping license from Altera

- DDR SDRAM memory controller core shipping license from Altera (comes free with Quartus II Subscription edition)

#### About the Nios II 3C25 Video Processor

CPU Platform

The CPU platform for the Nios II Standard System consists of

- Nios II/f cpu core

- JTAG Debug Port

- 32KB Instruction Cache

- 32KB Data Cache

#### System Functions

- PLL—The PLL accepts the global input clock source from the 50-MHz on-board oscillator and generates the following clocks

- 100-MHz CPU Clock

- 100-MHz SSRAM Clock

- 66.5-MHz DDR SDRAM Clock

- 60-MHz Peripheral Clock ("slow peripherals")

- 40-MHz Remote System Update Clock

- System Clock Timer—General purpose system timer.

- Performance Counter—Counter used for debug and system performance analysis.

- System ID—Used to sync the hardware system generation with the software generation tools.

- Remote System Update Block—Used for automatic configuration at boot-time from the on-board active parallel flash. The Nios II processor writes reset address of the hardware system stored in flash for reconfiguration.

- LED PIO—Output only control block for LED1-LED4

- Pushbutton PIO—Input only control block for the on-board pushbuttons.

- PIO for ID EEPROM (I2C)—Used to communicate with the EEPROM ID chip which stores information about the board including the touch panel calibration data and Ethernet MAC address.

The I2C interface is implemented using software and general purpose I/Os connected to the Nios II Standard System.

#### Memory Interface

There are four different types of on-board memory or storage devices. The memory controllers for three of these devices are provided as part of Altera's IP Suite and include:

- SSRAM Controller

- DDR SDRAM Controller

- CFI Flash Controller

- SD Card

The controller, API, and FAT File System for the SD-Card used in the Nios II Standard System is provided under license agreement by El Camino (http://www.elcamino.de)

For technical details on the components in standard hardware system refer to *Quartus II Handbook Volume 5: Embedded Peripherals.*

#### Communication Interfaces

There are several communication interfaces included in the Nios II Standard System:

- JTAG UART—Used for Serial communication and debugging Nios II applications via the on-board USB-Blaster circuitry.

- UART—Serial communication link for general purpose communications and debug.

- SPI —Used to communicate with the touch panel portion of the LCD Touchscreen.

- 10/100 Ethernet Controller—The Ethernet controller uses the Triple-speed Ethernet MAC to communicate with the PHY on the LCD Multimedia Daughtercard.

- Video Pipeline—The video pipeline outputs the appropriate pixel data and sync signals to the LCD Touch Panel. It provides high bandwidth memory access that allows for flicker free display on the color LCD. A more detailed description of the data flow for the video pipeline can be found in Appendix A.

The video pipeline is comprised of:

- PIO for LCD I<sup>2</sup>C Controller—The I<sup>2</sup>C pins are used to configure the LCD panel for brightness and set the gamma correction curves.

- **SPI Touch Panel Controller**—Used to communicate with the touch panel ADCs.

- Pixel Converter—Logic block that converts parallel 32-bit R-G-B-0 data to an 8-bit data stream. This is required because of the pin-limitation placed on the system by the HSMC connector. The video data-stream is multiplexed in the FPGA on the Cyclone III Starter Board and de-multiplexed in the MAX II device on the LCD Multimedia Daughtercard.

- Sync Generator—Generates the horizontal and vertical sync signals for each frame displayed on the LCD touch screen.

- For more information on the video pipeline (pixel converter and Video Sync Generator) and GPIO components refer to *Quartus II Handbook Chapter 5 Embedded Peripherals*.

# 4. Application Selector Utility

#### Overview

The application selector is the default utility that boots up on power on and allows users to quickly select, load, and run different ready-to-run applications or demonstrations stored on an SD Card using the LCD touch panel. An application consists of a FPGA hardware image and an application software image. When you select an application the application selector copies these images from the SD Card to the Flash memory and reconfigures the FPGA with your selection.

#### Ready-to-Run SD Card Demonstrations

In addition to the prepackaged ready-to-run SD Card demonstration applications which come with the Nios II Embedded Evaluation Kit, Cyclone III Edition, more are available from Altera or through third party vendors.

You can find several ready-to-run SD Card demonstrations in your SD Card as well as in the *<install dir>*\ **factory\_recovery**\**sdcard\_contents**\**altera\_eek\_applications**folder.

Even more ready-to-run SD Card demonstrations and designs examples are available form the Nios II Embedded Evaluation Kit User Community Wiki page.

Also, you can easily convert your own applications to be loadable by the application selector.

For more information see "Creating Your Own Loadable Applications" on page B–6.

# Running the Application Selector

This section describes the general operation of the Application Selector utility.

There are a couple of ways the application selector can update your board.

- In system update via the on board SD Card

- Remote-System Update via Ethernet

#### In system Update using SD Card

In order to run the application selector and load and view demonstrations stored on the SD Card (in-system update) follow the instructions below:

- Connect power to the Nios II Embedded Evaluation Kit board, Cyclone III Edition.

- 2. Switch on the power (SW1).

If the board is already powered, reset the board by pressing the button labeled RECONFIGURE.

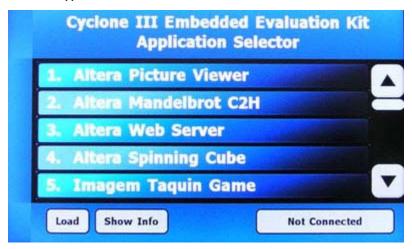

The application selector will boot from flash, and a splash screen will appear while the application selector searches for applications on the SD Card. (see Figure 4–1)

3. Touch the application to highlight your selection.

If there are more than five applications on the SD Card, you can scroll through the list by touching the scroll-up and scroll-down buttons on the right hand side of the screen.

4. View Information about an application. To get more information about a particular application, highlight the application by touching it then touching the button labeled **Show Info**.

If there is additional information available for the application you highlighted, a scrollable text window will appear. To return to the main menu, touch the button labeled **OK**.

5. Load and Run an application. When you've selected the application you want to load, touch the button labeled **Load**.

The application will begin loading, and a small window will be displayed showing the progress. Loading will take between 2 and 30 seconds, depending on the size of the application, and whether it was previously cached in on-board flash memory.

Figure 4–1. View of the Application Selector User Interface

For more detailed information about the Application Selector Utility, see Appendix B: Application Selector Details.

## Remote System Update using Ethernet

#### **About Remote System Update**

In the previous example the FPGA was configured from designs stored on the SD Card. But imagine you are working at your desk and your system is physically located elsewhere (such as in the lab or manufacturing facility or even a customer site). Having remote reconfiguration capability in your FPGA allows you to update your system with a new FPGA image so long as there is a persistent Ethernet connection.

The way this works is that when your kit is connected to a network, it serves up a web page. The contents of this web page are stored in the SD Card in a folder entitled **webserver\_html**. From any PC, you can view this web page by simply typing the correct IP address on a web browser. By following the instructions displayed on the HTTP forms on the web page you can browse to and load a design stored on the local PC and program it to the flash on your board. You can then reset the FPGA on your board and the FPGA should reconfigure from the newly downloaded Flash image.

#### Requirements

- 1. A host PC with a connection to a working Ethernet port.

- 2. A separate working Ethernet port to connect your board to.

- Flash files for hardware and software image to update the board with. These must be present on your host PC. Several flash files examples are provided in the altera/<version #>/kits/ cycloneIII\_3c25\_niosII/ examples/ application\_selector/remote\_system\_update folder.

Please note that .flash files from SD Card content directories cannot be used for remote system update as the web reconfiguration interface expects to see a hardware image at 0xe00000 upon reset.

#### **Operating Instructions**

Apply power to the board by plugging in the power cable and pressing switch SW1.

2. Using an Ethernet cable, connect the Ethernet RJ-45 jack on the LCD Multimedia HSMC to a working Ethernet port.

3. Please wait while the web server application establishes a connection to the internet and acquires an IP Address via DHCP. On completion, the IP Address will be displayed on the LCD Screen.

- 4. On your host PC ensure that it is connected to a working Ethernet port and launch a web browser.

- 5. In the web browser window, type the IP address displayed on the LCD screen (e.g. 168.57.231.12) and hit Enter.

You should now see a web page displayed on the web browser which is being served up by the board from the contents of the webserver\_html directory on the SD Card.

- On the upper left hand side on the web form, click on the link under Go to instructions. You will be directed to the remote configuration instruction page. Carefully read the instructions for remote configuration.

- 7. Click on the Left hand side of the web page you will see a CFI Flash Upload section. Click **Browse** button and browse to the hardware Flash image on your PC and click **Open.**

Browse to the altera/<version # >/kits/

cycloneIII\_3c25\_niosII/examples/application\_selector/

remote\_system\_update folder, choose an application e.g.

mandelbrot and click on C2H\_Mandelbrot\_hw.flash

8. On the web page, click **Upload**.

Please wait while the hardware Flash image is uploaded to your board. When this is done you will be directed to another web form entitled Program CFI Flash.

- 9. Click on the **Program Flash** Button to program the on-board flash with the uploaded Flash image.

- 10. If your remote update system has a software Flash image, then click on **Return to Instructions** and **repeat** the previous three steps to upload and program the **software Flash**.

Upon completion you will be directed to a form entitled Reset System

11. Click on the **Reset System** button. The FPGA should now reconfigure from the newly programmed contents of the Flash file.

# Creating Flash files for Remote System update

The image required for remote system update consists of a Flash image for FPGA configuration and if your system has a software application then it consist of a Flash image for the software application. To create the flash files you must have the Nios II EDS and Quartus II FPGA design software installed on your PC.

- A hardware SRAM object file (\*.SOF) must have the cpu reset address configured from the Flash device at offset 0x0.

- Create the software Executable link format file (ELF) in the standard fashion.

- On your host PC, launch a Nios II Command Shell from Start -> Programs -> Altera -> Nios II < version #> EDS -> Nios II Command Shell

- From the command shell navigate to where your SOF file is located and create your hardware Flash image using the following command:

```

sof2flash --activeparallel --input="your SOF.sof" -

-output="your SOF.flash" --

offset="RECONFIG ADDRESS"

```

From the command shell navigate to where your ELF file is located and create your software Flash image using the following command:

```

elf2flash --base=0x04000000 --end=0x04FFFFFF --

reset=0x04240000 --input="your ELF.efl" --

output="your FLASH.flash" --

boot=$SOPC_KIT_NIOS2/components/altera_nios2/boot_

loader_cfi.srec

```

## 5. Design Examples

# About Design Examples

The Nios II Embedded Evaluation kit comes with several applications that showcase the versatility of the Nios II processor in various applications such as imaging, graphics, networking etc.

To aid in the learning process of software developer, several design examples have been provided in source code form in the examples directory in the Nios II Embedded Evaluation Kit. These designs are

- Altera Picture Viewer

- Altera Mandelbrot C2H

- Altera Application Selector

For each of these applications a basic overview and discussion of operation is given. However much more detailed information can be found in the source-code which is loaded after installing the Nios II Embedded Evaluation Kit.

The Nios II Embedded Evaluation Kit also contains more applications provided from third party vendors to showcase available graphics libraries and middleware that have been ported to the Nios II processor, but these designs are shipped in binary format as ready-to-run demonstrations. Full designs for the ready-to-run demonstrations may be obtained by directly contacting the provider of the demonstration in the Nios II Embedded Evaluation Kit (NEEK), Cyclone III Edition page.

# Picture Viewer Application

#### **Picture Viewer**

The picture viewer application is based on the Nios II 3C25 Video Processor System. You can locate this application in the <install dir>/demos/picture\_viewer folder.

**Description**: Video and SD Card controller based processor system for LCD Color touch panel control for displaying JPEG and BMP images

#### IP licenses required to ship design:

- SD/MMC SPI Core IP (with FAT file system) from El Camino

- Nios II IP from Altera

- DDR SDRAM memory controller core from Altera

#### Software and middleware licenses required to ship design:

MicroC/OS-II real time operating system from Micrium

For more information on how to obtain evaluation or shipping licenses for the above refer to "Licensing the IP" on page 1–11.

The picture viewer application takes JPEG images or bitmaps stored on the SD Card and displays them on the LCD Touch Panel. The Nios II CPU decodes the images and stores the pixels in a video buffer in DDR SDRAM. A Scatter-Gather DMA is used to transfer pixel data from the video buffer to the video pipeline.

You can customize the picture viewer application's image selection by adding your own images in to the folder on the SD-Card entitled **images**.

#### Operation

The Picture Viewer application displays a new picture on the LCD screen after a settable delay (1,2,3,4,5,10,15,20 seconds). If decoding the image takes longer than this delay time, then the image is displayed as soon as it has been decoded. The image is scaled to optimally fit the LCD screen.

The operation of Picture Viewer application is explained below:

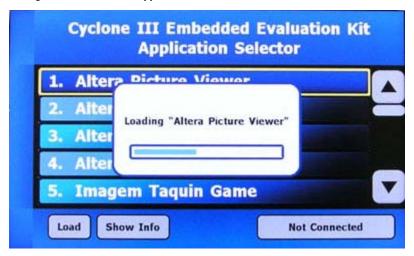

Power on the board by pressing the switch SW1. You will see the Application Selector menu on the LCD Touch Screen Display. See Figure 5–1.

Figure 5-1. Application Selector Menu

- 2. Select the **Pic Viewer** option by touching it in the application selector menu.

- 3. Touch the **Load** button located on the bottom left corner of the Touch Screen to load the Pic Viewer application. You will see the progress bar on the screen. See Figure 5–2.

Figure 5-2. Loading the Picture Viewer Application

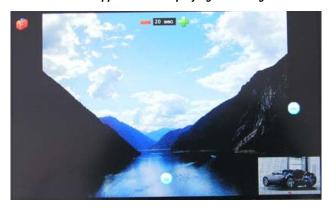

4. After loading the Pic Viewer application you will see the a slide show of pictures stored on the SD card. Figures 5–4. shows the first image stored on the SD card. The miniature view on the bottom right corner shows the next image of the slide show.

Figure 5-3. Running the Picture Viewer Application - Displaying First Image

5. The next image will be displayed after the delay period. See Figure 5–4.

Show/Hide Show Play/Stop Stirts Show

Figure 5-4. Running the Picture Viewer Application

You can control the slide show as explained below:

- To display the next image before the delay time is finished, touch the Forward button located at the right center of the touch panel.

- To display the previous image, touch the **Reverse** button located at the left center of the touch panel.

- To play or stop the slide, touch the **Play** /Stop button.

- On the top center of touch panel you will see the **Delay-period** (in **Sec.**). You can increase or decrease the delay period by

touching the **Plus** or **Minus** buttons respectively. The maximum delay period you can set is **20** seconds. The minimum is 1 second. The default delay period is **5** seconds.

- You can hide the control buttons by clicking on the **Hide** button located at the top left corner of the touch screen. To show the control buttons again touch anywhere on the LCD Touch panel.

- On the bottom right corner, you will see the miniature view of the next picture being decoded in the background.

- 6. The slide show continues until you tap the **Stop** button.

- To return to the Application Selector menu press the **Reconfigure** push-button switch on Cyclone III Starter Board.

## Mandelbrot **Application**

This application is based on the C2H\_Mandelbrot processor system.

You can locate this application in the <install dir>/demos/mandelbrot c2h folder.

This application is also a video based processor system with custom hardware acceleration engine for calculation of Mandelbrot algorithm

#### IP licenses required to ship design:

- Nios II IP from Altera (Ordering Code IP-NIOS)

- DDR SDRAM memory controller core from Altera (Available free with Quartus II Subscription as part of Altera IP Base Suite)

#### Software and middleware licenses required to ship design:

None

#### Software tools required to ship your hardware accelerators:

Nios II C2H Compiler (Ordering Code IPT-C2H-NIOS)

For more information on how to obtain evaluation or shipping licenses for the above refer to "Licensing the IP" on page 1–11

The Mandelbrot set is a mathematical set of complex numbers that form a fractal. The Mandelbrot set is generated from a surprisingly simple formula involving only multiplication and addition to produce a shape of great organic beauty and infinite subtle variation. Though the Mandelbrot set is intriguing in itself, the Mandelbrot C2H demonstration on the Nios II Embedded Evaluation kit showcases a powerful solution to a common engineering problem by increasing the performance of a system bound by processing throughput.

This example design shows a greater than 100x improvement in performance between software only and software with hardware accelerators. The Nios II C-to-Hardware (C2H) acceleration tool was used to take working software code and automatically generate the hardware accelerators that provide this performance improvement.

There are two processes at play here:

- 1. The calculation of the Mandelbrot Set to generate pixel data

- 2. The rendering of the pixel data on the LCD screen

Traditional processors will perform these functions purely in software. Options available to increase throughput once the processor and clock frequency are selected are extremely limited. The unfortunate trade-off of porting the entire application to a faster processor is the increase in cost and power.

The Nios II Embedded Evaluation kit, features not a traditional processor but a Nios II-based FPGA and using automated hardware acceleration. The Nios II C-to-Hardware (C2H) Acceleration Compiler, takes standard ANSI C code, in this case the Mandelbrot algorithm and automatically generates hardware accelerators.

In the hardware accelerated version of the design the Nios II processor handles common video functions such as the rendering the image, panning, zooming etc. The hardware accelerator concentrates on generating the pixels by computing the Mandelbrot function all in time for the next frame.

You can use the demonstration to observe the differences between a general purpose processor executing software and a group of hardware accelerators performing the same functionality. When comparing the software-only version with the software plus hardware accelerators you should expect to see a 250 times speed improvement between the software and hardware in the image rendering.

#### Using the Mandelbrot application

The Mandelbrot application utilizes the LCD and touchscreen for all user interactions. When the application starts you will be prompted with a blue welcome screen that you must touch to continue. The operation of Mandelbrot application is explained below:

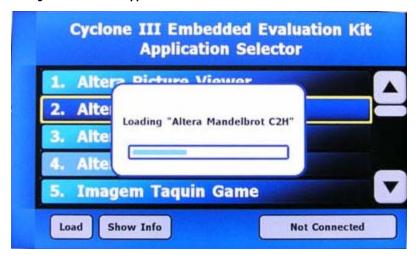

1. Power on the board (**SW1**). You will see the **Application Selector** menu on the LCD Touch Screen Display.

- 2. Select **Manelbrot Application** by choosing it in the application selector menu via the LCD touchscreen.

- 3. Touch the button marked **Load**. The LCD Touch panel display begins loading the Mandelbrot C2H application as shown in Figure 5–5.

Figure 5–5. Loading the Mandelbrot Application

4. After complete loading of application, you will see a **welcome screen** as shown in Figure 5–6.

Figure 5-6. Welcome Screen of Mandelbrot Application

Welcome to the C2H Mandelbrot design example

This example will render the Mandelbrot set in 800x480x24 using a software algorithm and in hardware generated from this software algorithm using Alteras C to Hardware Acceleration Tool (C2H).

Press anywhere on the screen to continue or load the menu to make operation mode changes.

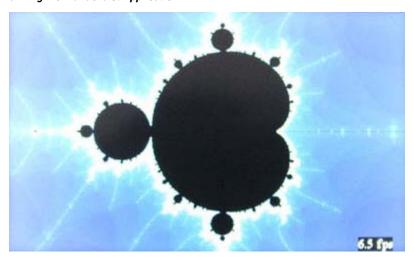

When you tap the touchscreen, the hardware accelerated version of the Mandelbrot application will begin running, changing coordinates and zooming in and out of the complex space. See Figure 5–7

Figure 5-7. Running the Mandelbrot Application

The default mode used in the design uses hardware acceleration.

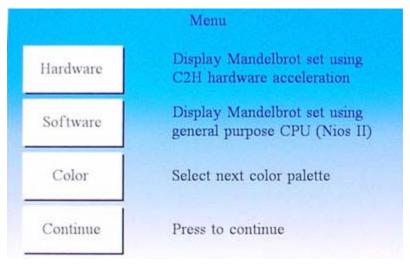

- 6. To change modes, color palettes, or pause the design simply tap the touch panel to bring up the menu.

- 7. The menu will offer you the choice of using hardware or software rendering. To select software rendering press the **Software** button followed by the **Continue** button. See Figure 5–8.

It is important to note that software rendering can be very slow so you may have to wait a long time for a single frame to be displayed.

Figure 5–8. Mandelbrot Application Menu

8. To change the color palette used in the final image simply press the **Color** button followed by the **Continue** button. See Figure 5–8.

While the menu is being displayed, all rendering will be paused as well. If you opened the menu and wish to continue without changing any settings press the **Continue** button.

Whether the design is rendering data using hardware or software, benchmark data is being collected and displayed to the screen.

- When hardware rendering is selected the benchmark data is updated every 5 frames.

- When software rendering is selected the benchmark data is updated every frame.

The benchmark data is displayed in the bottom right of the screen and it represents the instantaneous frames per second being rendered and displayed.

Consider the implications of what you have observed: What one would traditionally do with an expensive, power hungry GHz processor was just accomplished using an inexpensive Cyclone III FPGA, running at 100 MHz. Such is the power of hardware acceleration using FPGAs.

#### Operation

The design performs panning and zooming on the complex plane which gives a video like effect. Every time a new frame is rendered, a new set of coordinates must be calculated. These coordinates contain a center point, zoom factor, and maximum number of iterations. Knowing the center point and zoom factor the top left point of the screen is then determine and passed to the Mandelbrot algorithm. The maximum number of iterations is used to determine how much effort is spent per pixel before it is determined that the point is included in the Mandelbrot set (these points appear as black pixels). The pixel calculation is based on the following software segment:

```

inline int int_mandelbrot(long long cr, long long ci,

int max iter)

long long xsgr=0, ysgr=0, x=0, y=0;

int iter=0;

// go ahead and shift these up to the new decimal

offset

ci = ci<<28;

cr = cr << 28;

while ((xsqr + ysqr) < 0x04000000000000000LL) \&\&

(iter < max_iter) )</pre>

xsqr = x * x;

ysqr = y * y;

y = ((2 * x * y) + ci) >> 28;

x = (xsqr - ysqr + cr) >> 28;

iter++;

return(iter);

```

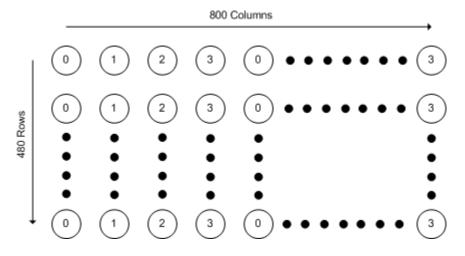

The implementation is fixed point with all values pre-scaled by 0x10000000. The loop will continue until the number of iterations reaches 'max\_iter' or  $x^2 + y^2$  converges to the value of 4. This function is called for each pixel so for this design that would be 384000 times since the screen resolution is 800x480. The value of 'iter' is used as the index into the color palette which picks the color of the pixel displayed on the screen. Even though the main processor supports dynamic branch prediction and contains cache memory, this operation of filling the screen can be very time consuming.

The approach taken for the C2H accelerated version is to offload this algorithm to pipelined and parallel hardware. Each Mandelbrot engine contains dedicated multiply, addition, and subtraction logic to perform multiple operations in parallel. Each Mandelbrot accelerator operates on a quarter of the frame and is only called once per frame. The workload is distributed on a pixel basis so each accelerator handles every fourth pixel.

Figure 5-9. Mandelbrot Engine Pixel Interleaving

While the hardware accelerators are calculating a frame, the coordinates of the next frame are prepared by the main i.e. the Nios II processor. The hardware accelerators contain a C pragma that instructs the compiler to implement non-blocking accelerators which allows both the main processor and Mandelbrot hardware accelerators to operate in parallel. The main processor polls the hardware accelerator to determine if the entire frame has been rendered.

# Application Selector

This application is based on the Application Selector processor system.

You can locate this application in the <install dir>/examples/application\_selector folder.

**Description**: Video, Ethernet and SD Card controller based processor system for LCD Color touch panel control, in-system update using SD Card, remote system update using Ethernet

#### IP licenses required to ship design:

- SD/MMC SPI Core IP (with FAT file system) from El Camino

- Triple Speed Ethernet-MAC Core license from Altera (Ordering code IP-TRIETHERNET)

- Nios II IP evaluation license with Nios II EDS, shipping license from Altera (Ordering Code IP-NIOS)

- DDR SDRAM memory controller core shipping license from Altera (comes free with Quartus II Subscription edition as part of Altera IP Base Suite)

#### Software and middleware licenses required to ship design:

- NicheStack TCP/IP Network Stack, Nios II Edition free evaluation license available with Nios II EDS, shipping license from Altera (Ordering Code IPSW-TCP/IP-NIOS)

- MicroC/OS-II real time operating system free evaluation license available with Nios II EDS, shipping license to be purchased from Micrium

For more information on how to obtain evaluation or shipping licenses for the above refer to "Licensing the IP" on page 1–11.

The full design example for the application selector utility is available in your Nios II Embedded Evaluation kit installed under the examples directory.

The application selector design examples illustrates several aspects of developing designs and using software device drivers for the Nios II Embedded Evaluation Kit.

- Interfacing to the LCD touch panel

- Interfacing to the SD Card using the FAT file system

- Implementing a HTTP web server application using the sockets interface of NicheStack TCP/IP Network Stack, Nios II Edition

- Implementing remote system update over Ethernet

- Managing multiple FPGA configurations from Flash

- Using the MicroC/OS-II real time operating system

#### **About the Embedded Web Server**

The application selector also features an embedded web server which serves up web pages to enable the remote system update capability. The way this works is as follows:

When your kit is connected to a network, the application will serve up a web page

The HTTP server looks for content contained in the **webserver\_html** directory at the top level of the SD card. Though default content is provided, the server will read any valid files that are placed into this directory.

- If DHCP is available, the application will attempt to obtain an IP address from a DHCP server. Otherwise, a static IP address (defined in web\_server.h) will be assigned after a time-out.

- The server can process basic requests to serve HTML, JPEG, and GIF files from the Altera FAT file system on an SD card.

The embedded web server is in no way a complete implementation of a full-featured HTTP server. This example uses the sockets interface.

To learn more about the application selector with embedded web server refer to the source code and design example in the *<install\_dir>I* examples/application\_selector folder.

A good introduction to sockets programming is the book Unix Network Programming by Richard Stevens. Additionally, the text **Sockets in C**, by Donahoo & Calvert, is a concise and inexpensive text for getting started with sockets programming.

# Appendix A. Video Pipeline Data Flow

#### Introduction

The video display subsystem embodied in the Nios II Embedded Evaluation Kit designs was intentionally-designed to be modular & flexible to make customizing a snap. The design style used for the video pipeline highlights the use of several simple **microcores** which can be configured or customized for other video applications.

The video subsystem consists of these operational components, in roughly-logical order:

- A frame-buffer (which happens to reside in DDR SDRAM memory)

- A memory-to-stream **DMA controller**, which reads memory 64 bits at a time and produces a stream of 64-bit data values.

- A width (data format adapter) to break the 64-bit stream into sequential 32-bit (pixel) values.

- A FIFO

- A Pixel Format Converter

- Another **Data Format Adapter**, to produce a stream of 8-bit values.

- A **sync-generator** (which you could think of as an LCD-display PHY)

If you actually look at the design, there are several other Avalon Streaming components in this flow. These have been omitted from this discussion for clarity because they are not **operational**. They are just timing-adapters which allow the operational pieces to fit together properly.

Starting from the end of the chain: The sync-generator just takes a stream of 8-bit-wide data values on its streaming input. Three consecutive 8-bit values make a single color pixel (R, G, B, R, G, B...) An start of packet (SOP)-pulse marks the start of each frame. The sync-generator drives external pins so that the pixel-stream appears on the display.

The DMA controller fetches pixel-data from the in-memory frame-buffer and drives it in row-major (raster) order on its streaming output-port and, through the video-subsystem pipeline, to the sync-generator termination.

The system has a FIFO because all systems like this always have FIFOs. It's there to "take up the slack" and keep the display fed even when the DDR SDRAM memory is unavailable (due to contention, refresh, etc.).

The **Pixel Format Converter** subsystem assumes that the frame-buffer is storing 32-bit pixel values in (0:R:G:B) (8:8:8:8) format. The sync-generator, however, accepts 24-bit values. So the **Pixel Format Converter** takes-in a stream of 32-bit (0:R:G:B) pixels and produces a stream of 24-bit (R:G:B) values. This is done by throwing-away the unused 8 bits.

Once the Pixel Format Converter has produced a stream of 24-bit (8:8:8) (R:G:B) values, the data format adapter serializes the data into a stream of 8-bit (R, then G, then B) values. This is the input to the sync generator block which produces the horizontal and vertical timing signals.

The video pipeline used in the Nios II Standard System is just one implementation for video systems. FPGAs give you the power of flexibility to change this with just a few lines of code. For example, the next section describes what is necessary to support a 5:6:5 pixel format.

# Get the full LCD controller Application Note

For more information about the video pipeline and LCD controller, refer to *AN527: Implementing an LCD Controller*.

# Creating a new 5:6:5 Pixel-Format component

The Nios II Standard System is designed to use a 32-bit 0:R:G:B data format. Suppose you wanted to change the entire display subsystem to work with 16-bit 5:6:5 pixels instead of 32-bit 0:R:G:B pixels. This can be accomplished with a few simple steps:

- 1. Copy the **Nios II Standard System** into your own project directory.

- 2. Create a new Verilog module called **pixel\_converter\_565** starting from the Verilog in **altera\_avalon\_pixel\_converter.v**, modify this Verilog so it has a 16-bit data\_in port and a 24-bit data\_out port. All the other ports remain the same. You create the data\_out value by inserting 8 new bits (3xR, 2xG, and 3xB) at the right points in the 16-bit word to "pad" it to a 24-bit word. You can use either zero- or LSB-padding.

- Import your Verilog module into SOPC Builder using the Component Editor.

- 4. From an Nios II Standard System, replace the existing **Pixel Format Converter** with your new pixel\_converter\_565 component.

- 5. Edit the data-format-adapter named lcd\_64\_to\_32\_bits\_dfa. Change its (Output Interface Parameters)/(Data Symbols Per Beat) from 4 to 2.

- This changes its width-adaptation from  $64 \rightarrow 32$  to  $64 \rightarrow 16$ .

- Rename it to lcd\_64\_to\_16\_bits\_dfa.

- 6. Regenerate your system.

Your software application is now responsible for filling the frame-buffer with aligned 16-bit 5:6:5 pixel data; and the firmware which controls the DMA must be modified to understand the different memory-buffer size implications of 16-bit (instead of 32-bit) pixels.

# Appendix B. Application Selector Details

This section describes some details about the operation of the Application Selector.

#### SD Card

The Application Selector uses the SD Card for storing applications and data used by these applications (such as the pictures used by the picture viewer or the HTML pages used by the Web Server application). The SD Card must be formatted with the FAT 16 file system, and can be any capacity up to 2GB. Long file names are supported.

## **Application Files**

Each loadable application consists of two flash files, and an optional text file, all stored on an SD Card.