# FIR Compiler II

# **User Guide**

101 Innovation Drive San Jose, CA 95134 www.altera.com

UG-01072-9.2

© 2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

# **Contents**

| Chapter 1. About This IP Core                                  |     |

|----------------------------------------------------------------|-----|

| Features                                                       |     |

| Device Family Support                                          |     |

| MegaCore Verification                                          |     |

| Performance and Resource Utilization                           |     |

| Release Information                                            | 1–9 |

| Chapter 2. Getting Started                                     |     |

| Installing and Licensing IP Cores                              | 2–1 |

| OpenCore Plus Evaluation                                       | 2–1 |

| Open Core Plus Time-Out Behavior                               | 2–1 |

| Customizing and Generating IP Cores                            | 2–2 |

| Files Generated for Altera IP Cores                            | 2–3 |

| Simulating IP Cores                                            | 2–3 |

| Simulating Your FIR II Compiler Design                         | 2–4 |

| Simulating in the ModelSim-Altera Software                     | 2–4 |

| Simulating in MATLAB                                           |     |

| Simulating in Third-Party Simulation Tools Using NativeLink    | 2–4 |

| Including Other IP Libraries and Files                         | 2-5 |

| Upgrading Outdated IP Cores                                    | 2-6 |

| Upgrading IP Cores at the Command Line                         |     |

| DSP Builder Design Flow                                        | 2–8 |

| Chapter 3. Parameters                                          |     |

| Filter Specification Parameters                                | 3–1 |

| Loading Coefficients from a File                               |     |

| Input and Output Options Page                                  |     |

| Signed Fractional Binary                                       |     |

| MSB and LSB Truncation, Saturation, and Rounding               |     |

| Implementation Options                                         |     |

| Memory and Multiplier Trade-Offs                               |     |

| Chapter 4. Functional Description                              |     |

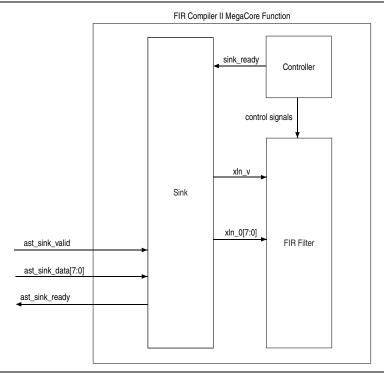

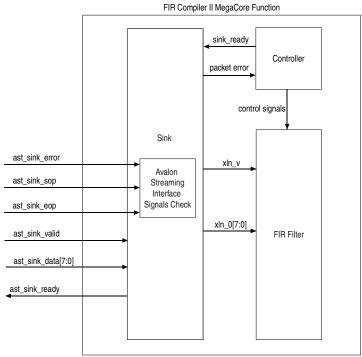

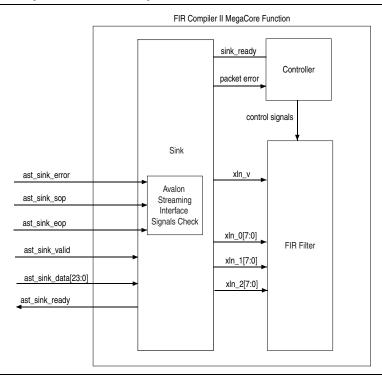

| Interfaces                                                     | 1_1 |

| Avalon-ST Sink and Source Interfaces                           |     |

| Avalon-ST Sink Interface                                       |     |

| Avalon-ST Source Interface                                     |     |

| Clock and Reset Interfaces                                     |     |

| Signals                                                        |     |

| Time-Division Multiplexing                                     |     |

| Multichannel Operation                                         |     |

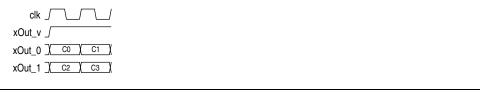

| Vectorized Inputs                                              |     |

| Channelization                                                 |     |

| Channel Input/Output Format                                    |     |

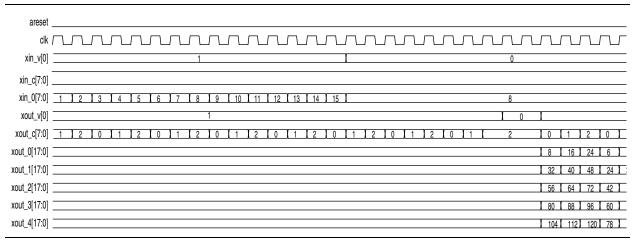

| Example—Eight Channels on Three Wires                          |     |

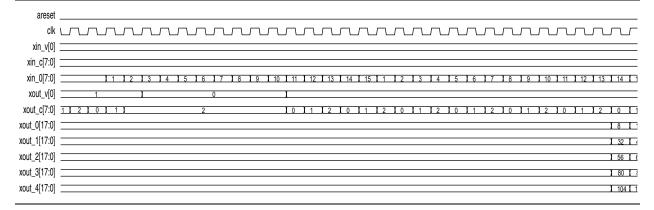

| Example—Four Channels on Four Wires                            |     |

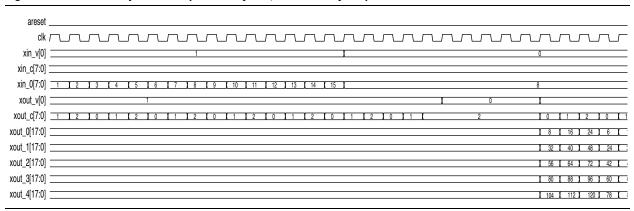

| Example—15 Channels with 15 Valid Cycles and 17 Invalid Cycles |     |

| Example—22 Channels with 11 Valid Cycles and 9 Invalid Cycles  |     |

| Zampie 22 Chamelo water i vana Cycles and / nivana Cycles      |     |

iv Contents

| Example—Super Sample Rate  | 4_19   |

|----------------------------|--------|

| Multiple Coefficient Banks | 4–20   |

| Coefficient Reloading      |        |

| Additional Information     |        |

| Document Revision History  | Info-1 |

| How to Contact Altera      | Info-2 |

| Typographic Conventions    | Info–3 |

#### 1. About This IP Core

This document describes the Altera® FIR Compiler II intellectual property (IP) core. The FIR Compiler II provides a fully-integrated finite impulse response (FIR) filter function optimized for use with Altera FPGA devices. The FIR Compiler II has an interactive parameter editor that allows you to easily create custom FIR filters. The parameter editor outputs IP functional simulation model files for use with Verilog HDL and VHDL simulators.

You can use the parameter editor to implement a variety of filter types, including single rate, decimation, interpolation, and fractional rate filters.

Many digital systems use signal filtering to remove unwanted noise, to provide spectral shaping, or to perform signal detection or analysis. FIR filters and infinite impulse response (IIR) filters provide these functions. Typical filter applications include signal preconditioning, band selection, and low-pass filtering.

Figure 1–1 shows a weighted, tapped delay line, FIR filter.

Figure 1-1. Basic FIR Filter

To design a filter, identify coefficients that match the frequency response you specify for the system. These coefficients determine the response of the filter. You can change which signal frequencies pass through the filter by changing the coefficient values in the parameter editor.

1–2 Chapter 1: About This IP Core

Features

#### **Features**

The Altera FIR Compiler II implements a finite impulse response (FIR) filter and supports the following features:

- Exploiting maximal designs efficiency through hardware optimizations such as:

- Interpolation

- Decimation

- Symmetry

- Decimation half-band

- Time sharing

- Easy system integration using Avalon® Streaming (Avalon-ST) interfaces.

- Memory and multiplier trade-offs to balance the implementation between logic elements (LEs) and memory blocks (M512, M4K, M9K, M10K, M20K, or M144K).

- Support for run-time coefficient reloading capability and multiple coefficient banks.

- User-selectable output precision via truncation, saturation, and rounding.

## **Device Family Support**

Altera offers the following device support levels for Altera IP cores:

- Preliminary support—Altera verifies the IP core with preliminary timing models for this device family. The IP core meets all functional requirements, but might still be undergoing timing analysis for the device family. You can use it in production designs with caution.

- Final support—Altera verifies the IP core with final timing models for this device family. The IP core meets all functional and timing requirements for the device family and can be used in production designs.

Table 1–1 lists the level of support for the FIR Compiler II for each Altera device family.

Table 1-1. Device Family Support

| Device Family           | Support     |

|-------------------------|-------------|

| Arria® II GX            | Final       |

| Arria II GZ             | Final       |

| Arria V                 | Final       |

| Arria V GZ              | Final       |

| Arria 10                | Preliminary |

| Cyclone® IV GX/E        | Final       |

| Cyclone V               | Final       |

| MAX® 10                 | Preliminary |

| Stratix <sup>®</sup> IV | Final       |

| Stratix IV GT           | Final       |

| Stratix IV GX           | Final       |

| Stratix V               | Final       |

| Other device families   | No support  |

# **MegaCore Verification**

Before releasing a version of the FIR Compiler II, Altera runs comprehensive regression tests to verify its quality and correctness. Altera generates custom variations of the FIR Compiler II to exercise its various parameter options. Altera simulates the resulting simulation models and verifies the results against master simulation models.

# **Performance and Resource Utilization**

Table 1–2 through Table 1–4 show typical expected performance for a FIR II IP Core using the Quartus II software with Arria V (5AGXFB3H4F40C4), Cyclone V (5CGXFC7D6F31C6), and Stratix V (5SGSMD4H2F35C2) devices:

Table 1-2. FIR II IP Core Performance—Arria V Devices

|                   | Pa    | arameters          |                          |       | DSP    | Mer  | nory | Re      | gisters   | f <sub>MAX</sub> |

|-------------------|-------|--------------------|--------------------------|-------|--------|------|------|---------|-----------|------------------|

| Channel           | Wires | Filter Type        | Coefficients             | ALM   | Blocks | M10K | M20K | Primary | Secondary | (MHz)            |

| 8                 | 2     | Decimation         | _                        | 1,607 | 24     | 0    | _    | 1,232   | 64        | 308              |

| 8                 | 2     | Decimation         | Write                    | 2,120 | 24     | 0    | _    | 1,298   | 141       | 308              |

| 8                 | 2     | Fractional<br>Rate | _                        | 1,395 | 16     | 0    | _    | 2,074   | 99        | 281              |

| 8                 | 2     | Fractional<br>Rate | Write                    | 1,745 | 16     | 0    | _    | 2,171   | 91        | 282              |

| 8                 | 2     | Fractional<br>Rate | _                        | 1,493 | 16     | 0    | _    | 2,167   | 117       | 280              |

| 8                 | 2     | Fractional<br>Rate | Write                    | 1,852 | 16     | 0    | _    | 2,287   | 116       | 270              |

| 8                 | 2     | Interpolation      | _                        | 1,841 | 32     | 0    | _    | 2,429   | 52        | 282              |

| 8                 | 2     | Interpolation      | Write                    | 1,994 | 32     | 0    | _    | 2,826   | 41        | 278              |

| 8                 | 2     | Interpolation      | Multiple<br>banks        | 2,001 | 32     | 0    | _    | 2,737   | 74        | 279              |

| 8                 | 2     | Interpolation      | Multiple<br>banks; Write | 2,700 | 32     | 0    | _    | 2,972   | 130       | 282              |

| 8                 | 2     | Single rate        | _                        | 932   | 20     | 0    | _    | 318     | 20        | 278              |

| 8                 | 2     | Single rate        | Write                    | 1,057 | 20     | 0    | _    | 713     | 3         | 279              |

| 8                 | 1     | Decimation         | _                        | 329   | 3      | 1    | _    | 321     | 33        | 301              |

| 8                 | 1     | Decimation         | Write                    | 430   | 3      | 1    | _    | 366     | 34        | 307              |

| 8                 | 1     | Decimation         | Multiple<br>banks        | 395   | 3      | 3    | _    | 483     | 44        | 310              |

| 8                 | 1     | Decimation         | Multiple<br>banks; Write | 510   | 3      | 3    | _    | 472     | 40        | 291              |

| 8                 | 1     | Fractional<br>Rate | _                        | 661   | 5      | 4    | _    | 877     | 75        | 310              |

| 8                 | 1     | Fractional<br>Rate | Write                    | 788   | 5      | 4    | _    | 936     | 98        | 309              |

| 8                 | 1     | Interpolation      | _                        | 381   | 5      | 0    | _    | 442     | 32        | 278              |

| 8                 | 1     | Interpolation      | Write                    | 514   | 5      | 0    | _    | 540     | 27        | 278              |

| 8                 | 1     | Single Rate        | _                        | 493   | 10     | 0    |      | 191     | 20        | 278              |

| 8                 | 1     | Single Rate        | Write                    | 633   | 10     | 0    | _    | 588     | 1         | 278              |

| 1                 | _     | Decimation         | _                        | 220   | 3      | 0    | _    | 158     | 27        | 310              |

| 1 super<br>sample | _     | Decimation         | _                        | 404   | 20     | 0    |      | 400     | 41        | 305              |

Table 1–2. FIR II IP Core Performance—Arria V Devices

|                   | Pa    | arameters          |                          | A . B . | DSP    | Mer  | nory | Registers |           | f <sub>MAX</sub> |

|-------------------|-------|--------------------|--------------------------|---------|--------|------|------|-----------|-----------|------------------|

| Channel           | Wires | Filter Type        | Coefficients             | ALM     | Blocks | M10K | M20K | Primary   | Secondary | (MHz)            |

| 1 super<br>sample | _     | Decimation         | Write                    | 505     | 20     | 0    | _    | 785       | 35        | 308              |

| 1                 |       | Decimation         | Write                    | 318     | 3      | 0    | _    | 208       | 26        | 309              |

| 1 Half Band       | _     | Decimation         | _                        | 234     | 3      | 0    | _    | 192       | 34        | 308              |

| 1 Half Band       | _     | Decimation         | Write                    | 320     | 3      | 0    | _    | 232       | 27        | 309              |

| 1                 | _     | Fractional<br>Rate | _                        | 297     | 3      | 0    | _    | 504       | 57        | 310              |

| 1                 | _     | Fractional<br>Rate | Write                    | 391     | 3      | 0    | _    | 563       | 56        | 310              |

| 1 Half Band       | _     | Fractional<br>Rate | _                        | 196     | 2      | 0    | _    | 251       | 5         | 277              |

| 1 Half Band       | _     | Fractional<br>Rate | Write                    | 266     | 2      | 0    | _    | 301       | 15        | 280              |

| 1                 | _     | Interpolation      | _                        | 266     | 5      | 0    | _    | 290       | 30        | 278              |

| 1 super<br>sample | _     | Interpolation      | _                        | 717     | 32     | 0    | _    | 903       | 45        | 308              |

| 1 super<br>sample | _     | Interpolation      | Write                    | 842     | 32     | 0    | _    | 1,281     | 48        | 308              |

| 1                 | _     | Interpolation      | Write                    | 405     | 5      | 0    | _    | 380       | 15        | 278              |

| 1 Half Band       |       | Interpolation      | _                        | 254     | 3      | 0    | _    | 293       | 8         | 310              |

| 1 Half Band       |       | Interpolation      | Write                    | 333     | 4      | 0    | _    | 314       | 10        | 309              |

| 1                 |       | Single rate        | _                        | 93      | 10     | 0    | _    | 129       | 27        | 299              |

| 1 super<br>sample |       | Single rate        | _                        | 262     | 20     | 0    | _    | 307       | 41        | 309              |

| 1 super<br>sample | _     | Single rate        | Write                    | 373     | 20     | 0    | _    | 687       | 40        | 302              |

| 1                 | _     | Single rate        | Write                    | 228     | 10     | 0    | _    | 519       | 16        | 300              |

| 1 Half Band       | _     | Single rate        | _                        | 189     | 5      | 0    | _    | 254       | 63        | 309              |

| 1 Half Band       |       | Single rate        | Write                    | 272     | 5      | 0    |      | 496       | 29        | 310              |

| 1                 | _     | Single rate        | Multiple<br>banks        | 109     | 10     | 0    | _    | 199       | 29        | 283              |

| 1                 | _     | Single rate        | Multiple<br>banks; Write | 395     | 10     | 0    | _    | 361       | 19        | 282              |

Table 1–3. FIR II IP Core Performance—Cyclone V Devices

|                   | Pa    | arameters          |                          | A1 54 | DSP    | Mer  | nory | Re      | gisters   | f <sub>MAX</sub> |

|-------------------|-------|--------------------|--------------------------|-------|--------|------|------|---------|-----------|------------------|

| Channel           | Wires | Filter Type        | Coefficients             | ALM   | Blocks | M10K | M20K | Primary | Secondary | (MHz)            |

| 8                 | 2     | Decimation         | _                        | 1,607 | 24     | 0    | _    | 1,231   | 46        | 273              |

| 8                 | 2     | Decimation         | Write                    | 2,092 | 24     | 0    | _    | 1,352   | 63        | 273              |

| 8                 | 2     | Fractional<br>Rate | _                        | 1,852 | 16     | 0    | _    | 3,551   | 309       | 254              |

| 8                 | 2     | Fractional<br>Rate | Write                    | 2,203 | 16     | 0    | _    | 3,675   | 269       | 255              |

| 8                 | 2     | Fractional<br>Rate | _                        | 1,951 | 16     | 0    | _    | 3,543   | 421       | 227              |

| 8                 | 2     | Fractional<br>Rate | Write                    | 2,301 | 16     | 0    | _    | 3,601   | 476       | 250              |

| 8                 | 2     | Interpolation      | _                        | 1,840 | 32     | 0    | _    | 2,431   | 48        | 255              |

| 8                 | 2     | Interpolation      | Write                    | 1,988 | 32     | 0    |      | 2,813   | 57        | 252              |

| 8                 | 2     | Interpolation      | Multiple<br>banks        | 2,006 | 32     | 0    | _    | 2,711   | 98        | 253              |

| 8                 | 2     | Interpolation      | Multiple<br>banks; Write | 2,704 | 32     | 0    | _    | 2,990   | 100       | 250              |

| 8                 | 2     | Single rate        | _                        | 934   | 20     | 0    | _    | 317     | 19        | 252              |

| 8                 | 2     | Single rate        | Write                    | 1,053 | 20     | 0    | _    | 704     | 12        | 251              |

| 8                 | 1     | Decimation         | _                        | 474   | 3      | 1    | _    | 541     | 50        | 275              |

| 8                 | 1     | Decimation         | Write                    | 559   | 3      | 1    | _    | 574     | 58        | 273              |

| 8                 | 1     | Decimation         | Multiple<br>banks        | 544   | 3      | 3    | _    | 691     | 83        | 275              |

| 8                 | 1     | Decimation         | Multiple<br>banks; Write | 636   | 3      | 3    | _    | 677     | 82        | 275              |

| 8                 | 1     | Fractional<br>Rate | _                        | 1,165 | 5      | 4    | _    | 1,715   | 205       | 275              |

| 8                 | 1     | Fractional<br>Rate | Write                    | 1,287 | 5      | 4    | _    | 1,770   | 198       | 275              |

| 8                 | 1     | Interpolation      | _                        | 381   | 5      | 0    | _    | 433     | 42        | 248              |

| 8                 | 1     | Interpolation      | Write                    | 513   | 5      | 0    | _    | 540     | 26        | 250              |

| 8                 | 1     | Single Rate        | _                        | 493   | 10     | 0    | _    | 191     | 18        | 249              |

| 8                 | 1     | Single Rate        | Write                    | 624   | 10     | 0    |      | 563     | 26        | 251              |

| 1                 |       | Decimation         | _                        | 219   | 3      | 0    | —    | 159     | 23        | 289              |

| 1 super<br>sample | _     | Decimation         | _                        | 404   | 20     | 0    | _    | 398     | 43        | 288              |

| 1 super<br>sample | _     | Decimation         | Write                    | 503   | 20     | 0    | _    | 774     | 46        | 256              |

| 1                 |       | Decimation         | Write                    | 312   | 3      | 0    | _    | 208     | 26        | 289              |

| 1 Half Band       |       | Decimation         | _                        | 234   | 3      | 0    | _    | 192     | 29        | 289              |

| 1 Half Band       | _     | Decimation         | Write                    | 323   | 3      | 0    | _    | 228     | 32        | 288              |

Table 1–3. FIR II IP Core Performance—Cyclone V Devices

|                   | Pa    | arameters          |                          | A1 84 | DSP    | Memory |      | Re      | gisters   | f <sub>MAX</sub> |

|-------------------|-------|--------------------|--------------------------|-------|--------|--------|------|---------|-----------|------------------|

| Channel           | Wires | Filter Type        | Coefficients             | ALM   | Blocks | M10K   | M20K | Primary | Secondary | (MHz)            |

| 1                 | _     | Fractional<br>Rate | _                        | 422   | 3      | 0      | _    | 723     | 94        | 310              |

| 1                 | _     | Fractional<br>Rate | Write                    | 516   | 3      | 0      | _    | 787     | 86        | 292              |

| 1 Half Band       | _     | Fractional<br>Rate | _                        | 195   | 2      | 0      | _    | 251     | 12        | 261              |

| 1 Half Band       | _     | Fractional<br>Rate | Write                    | 267   | 2      | 0      | _    | 299     | 15        | 252              |

| 1                 | _     | Interpolation      | _                        | 262   | 5      | 0      | _    | 296     | 25        | 252              |

| 1 super sample    | _     | Interpolation      | _                        | 708   | 32     | 0      | _    | 914     | 34        | 272              |

| 1 super<br>sample | _     | Interpolation      | Write                    | 841   | 32     | 0      | _    | 1,297   | 32        | 259              |

| 1                 | _     | Interpolation      | Write                    | 400   | 5      | 0      | _    | 382     | 12        | 258              |

| 1 Half Band       |       | Interpolation      | _                        | 288   | 3      | 0      | _    | 456     | 13        | 290              |

| 1 Half Band       | _     | Interpolation      | Write                    | 331   | 4      | 0      | _    | 315     | 9         | 290              |

| 1                 |       | Single rate        | _                        | 87    | 10     | 0      | _    | 142     | 14        | 253              |

| 1 super<br>sample | _     | Single rate        | _                        | 258   | 20     | 0      | _    | 315     | 33        | 260              |

| 1 super<br>sample |       | Single rate        | Write                    | 369   | 20     | 0      | _    | 704     | 23        | 274              |

| 1                 | _     | Single rate        | Write                    | 227   | 10     | 0      | _    | 535     | 0         | 251              |

| 1 Half Band       | _     | Single rate        | _                        | 187   | 5      | 0      | _    | 273     | 44        | 288              |

| 1 Half Band       | _     | Single rate        | Write                    | 274   | 5      | 0      | _    | 506     | 19        | 275              |

| 1                 | _     | Single rate        | Multiple<br>banks        | 110   | 10     | 0      | _    | 187     | 41        | 255              |

| 1                 | _     | Single rate        | Multiple<br>banks; Write | 375   | 10     | 0      | _    | 349     | 32        | 255              |

Table 1-4. FIR II IP Core Performance—Stratix V Devices

|         | Pa    | arameters          |              | ALM   | ALM | ALBA | A1 84 | DSP     | Men       | nory  | Re | gisters | f <sub>MAX</sub> |

|---------|-------|--------------------|--------------|-------|-----|------|-------|---------|-----------|-------|----|---------|------------------|

| Channel | Wires | Filter Type        | Coefficients | ALIVI |     | M10K | M20K  | Primary | Secondary | (MHz) |    |         |                  |

| 8       | 2     | Decimation         | _            | 1,609 | 24  | _    | 0     | 1,231   | 60        | 450   |    |         |                  |

| 8       | 2     | Decimation         | Write        | 2,319 | 24  | _    | 0     | 2,077   | 66        | 450   |    |         |                  |

| 8       | 2     | Fractional<br>Rate | _            | 1,350 | 16  | _    | 0     | 2,099   | 88        | 448   |    |         |                  |

| 8       | 2     | Fractional<br>Rate | Write        | 1,771 | 16  | _    | 0     | 2,291   | 78        | 450   |    |         |                  |

Table 1-4. FIR II IP Core Performance—Stratix V Devices

|                   | Pa    | arameters          |                          |       | DSP    | Mer  | nory | Re      | gisters   | f <sub>MAX</sub> |

|-------------------|-------|--------------------|--------------------------|-------|--------|------|------|---------|-----------|------------------|

| Channel           | Wires | Filter Type        | Coefficients             | ALM   | Blocks | M10K | M20K | Primary | Secondary | (MHz)            |

| 8                 | 2     | Fractional<br>Rate | _                        | 1,457 | 16     | _    | 0    | 2,213   | 88        | 444              |

| 8                 | 2     | Fractional<br>Rate | Write                    | 1,873 | 16     | _    | 0    | 2,418   | 89        | 450              |

| 8                 | 2     | Interpolation      | _                        | 1,777 | 32     | _    | 0    | 2,303   | 15        | 444              |

| 8                 | 2     | Interpolation      | Write                    | 2,081 | 32     | _    | 0    | 3,009   | 26        | 450              |

| 8                 | 2     | Interpolation      | Multiple<br>banks        | 1,825 | 32     | _    | 0    | 2,473   | 39        | 430              |

| 8                 | 2     | Interpolation      | Multiple<br>banks; Write | 2,652 | 32     | _    | 0    | 2,842   | 236       | 424              |

| 8                 | 2     | Single rate        | _                        | 920   | 20     | _    | 0    | 332     | 2         | 444              |

| 8                 | 2     | Single rate        | Write                    | 1,359 | 20     | _    | 0    | 1,323   | 1         | 450              |

| 8                 | 1     | Decimation         | _                        | 340   | 3      | _    | 0    | 324     | 25        | 450              |

| 8                 | 1     | Decimation         | Write                    | 463   | 3      | _    | 0    | 457     | 29        | 450              |

| 8                 | 1     | Decimation         | Multiple<br>banks        | 466   | 3      | _    | 0    | 569     | 42        | 450              |

| 8                 | 1     | Decimation         | Multiple<br>banks; Write | 577   | 3      | _    | 0    | 567     | 41        | 450              |

| 8                 | 1     | Fractional<br>Rate | _                        | 709   | 5      | _    | 0    | 870     | 45        | 450              |

| 8                 | 1     | Fractional<br>Rate | Write                    | 852   | 5      | _    | 0    | 991     | 65        | 450              |

| 8                 | 1     | Interpolation      | _                        | 216   | 5      | _    | 0    | 197     | 13        | 450              |

| 8                 | 1     | Interpolation      | Write                    | 361   | 5      | _    | 0    | 290     | 22        | 450              |

| 8                 | 1     | Single Rate        | _                        | 483   | 10     | _    | 0    | 212     | 4         | 447              |

| 8                 | 1     | Single Rate        | Write                    | 783   | 10     | _    | 0    | 894     | 4         | 450              |

| 1                 |       | Decimation         | _                        | 215   | 3      | _    | 0    | 175     | 10        | 450              |

| 1 super<br>sample | _     | Decimation         | _                        | 547   | 20     | _    | 0    | 1,167   | 88        | 450              |

| 1 super<br>sample | _     | Decimation         | Write                    | 989   | 20     | _    | 0    | 2,214   | 105       | 450              |

| 1                 |       | Decimation         | Write                    | 331   | 3      | _    | 0    | 310     | 7         | 450              |

| 1 Half Band       | _     | Decimation         | _                        | 226   | 3      | _    | 0    | 206     | 16        | 450              |

| 1 Half Band       | _     | Decimation         | Write                    | 343   | 3      | _    | 0    | 327     | 18        | 450              |

| 1                 | _     | Fractional<br>Rate | _                        | 252   | 3      | _    | 0    | 318     | 21        | 445              |

| 1                 | _     | Fractional<br>Rate | Write                    | 353   | 3      | _    | 0    | 380     | 13        | 450              |

| 1 Half Band       | _     | Fractional<br>Rate | _                        | 140   | 2      | _    | 0    | 185     | 13        | 450              |

| 1 Half Band       | _     | Fractional<br>Rate | Write                    | 214   | 2      | _    | 0    | 235     | 21        | 450              |

Table 1-4. FIR II IP Core Performance—Stratix V Devices

|                | Pa    | arameters     |                          | ALBA | DSP    | Men  | nory | Re      | gisters   | f <sub>MAX</sub> |

|----------------|-------|---------------|--------------------------|------|--------|------|------|---------|-----------|------------------|

| Channel        | Wires | Filter Type   | Coefficients             | ALM  | Blocks | M10K | M20K | Primary | Secondary | (MHz)            |

| 1              | _     | Interpolation | _                        | 168  | 5      | _    | 0    | 127     | 19        | 450              |

| 1 super sample | _     | Interpolation | _                        | 573  | 32     | _    | 0    | 1,084   | 51        | 446              |

| 1 super sample | _     | Interpolation | Write                    | 870  | 32     | _    | 0    | 1,774   | 136       | 450              |

| 1              | _     | Interpolation | Write                    | 313  | 5      | _    | 0    | 196     | 5         | 450              |

| 1 Half Band    | _     | Interpolation | _                        | 253  | 3      | _    | 0    | 292     | 9         | 450              |

| 1 Half Band    |       | Interpolation | Write                    | 370  | 4      | _    | 0    | 418     | 9         | 450              |

| 1              | _     | Single rate   | _                        | 226  | 10     | _    | 0    | 706     | 31        | 447              |

| 1_ssample      | _     | Single rate   | _                        | 468  | 20     | _    | 0    | 1,354   | 53        | 450              |

| 1_ssample      | _     | Single rate   | Write                    | 927  | 20     | _    | 0    | 2,267   | 203       | 450              |

| 1              | _     | Single rate   | Write                    | 524  | 10     | _    | 0    | 1,391   | 31        | 500              |

| 1 Half Band    | _     | Single rate   | _                        | 195  | 5      | _    | 0    | 270     | 50        | 450              |

| 1 Half Band    | _     | Single rate   | Write                    | 351  | 5      | _    | 0    | 645     | 28        | 450              |

| 1              | _     | Single rate   | Multiple<br>banks        | 250  | 10     | _    | 0    | 716     | 93        | 449              |

| 1              | _     | Single rate   | Multiple<br>banks; Write | 671  | 10     | _    | 0    | 1,228   | 50        | 450              |

# **Release Information**

Table 1–5 provides information about this release of the Altera FIR Compiler II.

Table 1-5. FIR Compiler II Release Information

| Item          | Description                     |

|---------------|---------------------------------|

| Version       | 13.1                            |

| Release Date  | November 2013                   |

| Ordering Code | IP-FIRII<br>IPR-FIRII (renewal) |

| Product ID    | 00D8                            |

| Vendor ID     | 6AF7                            |

For more information about this release, refer to the MegaCore IP Library Release Notes and Errata.

Altera verifies that the current version of the Quartus® II software compiles the previous version of each IP core. The MegaCore IP Library Release Notes and Errata report any exceptions to this verification. Altera does not verify compilation with IP core versions older than one release.

August 2014 Altera Corporation

### **Installing and Licensing IP Cores**

The Quartus II software includes the Altera IP Library. The library provides many useful IP core functions for production use without additional license. You can fully evaluate any licensed Altera IP core in simulation and in hardware until you are satisfied with its functionality and performance.

Some Altera IP cores, such as MegaCore<sup>®</sup> functions, require that you purchase a separate license for production use. After you purchase a license, visit the Self Service Licensing Center to obtain a license number for any Altera product. For additional information, refer to *Altera Software Installation and Licensing*.

Figure 2–1. IP core Installation Path

The default installation directory on Windows is *<drive>*:\altera\*<version number>*; on Linux it is *<home directory>*/altera/*<version number>*.

### **OpenCore Plus Evaluation**

The Altera IP library contains both free and individually licenced IP cores. With the Altera free OpenCore Plus evaluation feature, you can evaluate separately licenced IP cores in the following ways prior to purchasing a production license:

- Simulate the behavior of an Altera IP core in your system using the Quartus II software and Altera-supported VHDL and Verilog HDL simulators.

- Verify the functionality of your design and evaluate its size and speed quickly and easily.

- Generate device programming files for designs that include IP cores. These files are time-limited under the OpenCore Plus evaluation program.

- Program a device and verify your design in hardware.

## **Open Core Plus Time-Out Behavior**

OpenCore Plus hardware evaluation supports the following two operation modes:

- Untethered—the design runs for a limited time.

- *Tethered*—requires a connection between your board and the host computer. If all Altera IP cores in a design support tethered mode, the device can operate for a longer time or indefinitely.

All IP cores in a device time out simultaneously when the most restrictive evaluation time is reached. If there is more than one IP core in a design, a specific IP core's time-out behavior may be masked by the time-out behavior of the other IP cores.

For IP cores, the untethered time-out is 1 hour; the tethered time-out value is indefinite.

Your design stops working after the hardware evaluation time expires.

The Quartus II software uses OpenCore Plus Files (.ocp) in your project directory to identify your use of the OpenCore Plus evaluation program. After you activate the feature, do not delete these files.

For information about the OpenCore Plus evaluation program, refer to *AN320: OpenCore Plus Evaluation of Megafunctions*.

# **Customizing and Generating IP Cores**

You can customize IP cores to support a wide variety of applications. The Quartus II IP Catalog displays IP cores available for the current target device. The parameter editor guides you to set parameter values for optional ports, features, and output files.

To customize and generate a custom IP core variation, follow these steps:

- 1. In the IP Catalog (**Tools > IP Catalog**), locate and double-click the name of the IP core to customize. The parameter editor appears.

- 2. Specify a top-level name for your custom IP variation. This name identifies the IP core variation files in your project. If prompted, also specify the target Altera device family and output file HDL preference. Click **OK**.

- 3. Specify the desired parameters, output, and options for your IP core variation:

- Optionally select preset parameter values. Presets specify all initial parameter values for specific applications (where provided).

- Specify parameters defining the IP core functionality, port configuration, and device-specific features.

- Specify options for generation of a timing netlist, simulation model, testbench, or example design (where applicable).

- Specify options for processing the IP core files in other EDA tools.

- 4. Click **Finish** or **Generate** to generate synthesis and other optional files matching your IP variation specifications. The parameter editor generates the top-level **.qip** or **.qsys** IP variation file and HDL files for synthesis and simulation. Some IP cores also simultaneously generate a testbench or example design for hardware testing.

- 5. To generate a simulation testbench, click **Generate > Generate Testbench System**. **Generate > Generate Testbench System** is not available for some IP cores.

- To generate a top-level HDL design example for hardware verification, click Generate > HDL Example. Generate > HDL Example is not available for some IP cores.

When you generate the IP variation with a Quartus II project open, the parameter editor automatically adds the IP variation to the project. Alternatively, click **Project** > **Add/Remove Files in Project** to manually add a top-level .qip or .qsys IP variation file to a Quartus II project. To fully integrate the IP into the design, make appropriate pin assignments to connect ports. You can define a virtual pin to avoid making specific pin assignments to top-level signals.

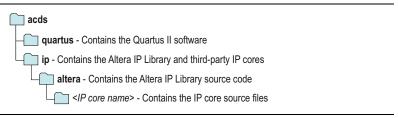

#### Files Generated for Altera IP Cores

The Quartus II software version 14.0 Arria 10 Edition and later generates the following output file structure for Altera IP cores:

Figure 2–2. IP Core Generated Files

# **Simulating IP Cores**

The Quartus II software supports RTL- and gate-level design simulation of Altera IP cores in supported EDA simulators. Simulation involves setting up your simulator working environment, compiling simulation model libraries, and running your simulation.

You can use the functional simulation model and the testbench or example design generated with your IP core for simulation. The functional simulation model and testbench files are generated in a project subdirectory. This directory may also include scripts to compile and run the testbench. For a complete list of models or libraries required to simulate your IP core, refer to the scripts generated with the testbench. You can use the Quartus II NativeLink feature to automatically generate simulation files and scripts. NativeLink launches your preferred simulator from within the Quartus II software.

For more information about simulating Altera IP cores, refer to *Simulating Altera Designs* in volume 3 of the *Quartus II Handbook*.

### **Simulating Your FIR II Compiler Design**

The FIR Compiler II MegaCore function generates a number of output files for design simulation. After you have created a custom FIR filter, you can simulate your design in the ModelSim®-Altera software, MATLAB, or another third-party simulation tool.

#### Simulating in the ModelSim-Altera Software

Use the Tcl script (*<variation name*>\_msim.tcl) to load the VHDL testbench into the ModelSim-Altera software.

This script uses the file *<variation name>\_input.txt* to provide input data to the FIR filter. The output from the simulation is stored in a file *<variation name>\_output.txt*.

#### Simulating in MATLAB

To simulate in a MATLAB environment, run the <code><variation\_name>\_model.m</code> testbench m-file, which also is located in your design directory. This script also uses the file <code><variation name>\_input.txt</code> to provide input data. The output from the MATLAB simulation is stored in the file <code><variation name>\_model\_output.txt</code>.

#### Simulating in Third-Party Simulation Tools Using NativeLink

You can perform a simulation in a third-party simulation tool from within the Quartus II software, using NativeLink.

The Tcl script file *<variation name>*\_nativelink.tcl can be used to assign default NativeLink testbench settings to the Quartus II project.

To perform a simulation in the Quartus II software using NativeLink, perform the following steps:

- Create a custom MegaCore function variation as described earlier in this chapter but ensure you specify a variation name that exactly matches the Quartus II project name.

- 2. Verify that the absolute path to your third-party EDA tool is set in the **Options** page under the Tools menu in the Quartus II software.

- 3. On the Processing menu, point to Start and click Start Analysis & Elaboration.

- 4. On the Tools menu, click **Tcl scripts**. In the **Tcl Scripts** dialog box, select <*variation name*>\_nativelink.tcl and click **Run**. A message indicates that the Tcl script is successfully loaded.

- 5. On the Assignments menu, click Settings, expand EDA Tool Settings, and select Simulation. Select a simulator under Tool name then in NativeLink Settings, select **Compile test bench** and click **Test Benches**.

- 6. On the Tools menu, point to EDA Simulation Tool and click Run EDA RTL Simulation.

The Quartus II software selects the simulator, and compiles the Altera libraries, design files, and testbenches. The testbench runs and the waveform window shows the design signals for analysis.

For more information, refer to the Simulating Altera IP in Third-Party Simulation Tools chapter in volume 3 of the Quartus II Handbook.

IP functional simulation models output correct data only when data storage is clear. When data storage is not clear, functional simulation models will output non-relevant data. The number of clock cycles it takes before relevant samples are available is N; where  $N = \text{(number of channels)} \times \text{(number of coefficients)} \times \text{(number of clock cycles)}$ to calculate an output).

### **Including Other IP Libraries and Files**

The Quartus II software searches for IP cores in the project directory, in the Altera installation directory, and in the defined IP search path. You can include IP libraries and files from other locations by modifying the IP search path. To use the GUI to modify the global or project-specific search path, click Tools > Options > IP Search **Locations** and specify the path to your IP.

Adds new global IP search paths Changes search path order Lists current project and global search paths Adds new project-specific IP search paths OK Cancel Help

Figure 2-3. Specifying IP Search Locations

As an alternative to the GUI, use the following SEARCH PATH assignment to include one or more project libraries. Specify only one source directory for each SEARCH\_PATH assignment.

set global assignment -name SEARCH PATH < library or file path>

If your project includes two IP core files of the same name, the following search path precedence rules determine the resolution of files:

- 1. Project directory files.

- 2. Project database directory files.

- 3. Project libraries specified in **IP Search Locations**, or with the SEARCH\_PATH assignment in the Quartus II Settings File (.qsf).

- 4. Global libraries specified in **IP Search Locations**, or with the SEARCH\_PATH assignment in the Quartus II Settings File (.qsf).

- 5. Quartus II software libraries directory, such as *Quartus II Installation*>\libraries.

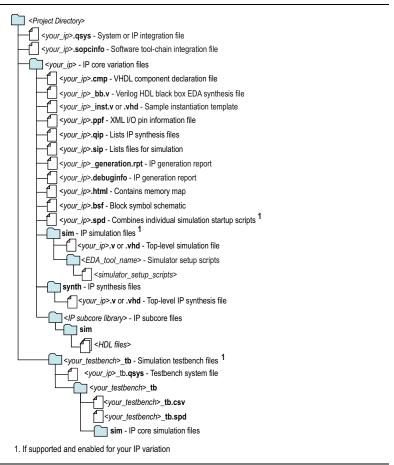

### **Upgrading Outdated IP Cores**

IP cores generated with a previous version of the Quartus II software may require upgrade before use in the current version of the Quartus II software. Click **Project > Upgrade IP Components** to identify and upgrade outdated IP cores.

The **Upgrade IP Components** dialog box provides instructions when IP upgrade is required, optional, or unsupported for specific IP cores in your design. Most Altera IP cores support one-click, automatic simultaneous upgrade. You can individually migrate IP cores unsupported by auto-upgrade.

The **Upgrade IP Components** dialog box also reports legacy Altera IP cores that support compilation-only (without modification), as well as IP cores that do not support migration. Replace unsupported IP cores in your project with an equivalent Altera IP core or design logic. Upgrading IP cores changes your original design files.

#### Before you begin

- Migrate your Quartus II project containing outdated IP cores to the latest version of the Quartus II software. In a previous version of the Quartus II software, click Project > Archive Project to save the project. This archive preserves your original design source and project files after migration. le paths in the archive must be relative to the project directory. File paths in the archive must reference the IP variation .v or .vhd file or .qsys file, not the .qip file.

- Restore the project in the latest version of the Quartus II software. Click Project > Restore Archived Project. Click Ok if prompted to change to a supported device or overwrite the project database.

To upgrade outdated IP cores, follow these steps:

1. In the latest version of the Quartus II software, open the Quartus II project containing an outdated IP core variation.

File paths in a restored project archive must be relative to the project directory and you must reference the IP variation .v or .vhd file or .qsys file, not the .qip file.

- 2. Click Project > Upgrade IP Components. The Upgrade IP Components dialog box displays all outdated IP cores in your project, along with basic instructions for upgrading each core.

- 3. To simultaneously upgrade all IP cores that support automatic upgrade, click Perform Automatic Upgrade. The IP cores upgrade to the latest version. The Status and Version columns reflect the update.

Figure 2-4. Upgrading IP Cores

### **Upgrading IP Cores at the Command Line**

Alternatively, you can upgrade IP cores at the command line. To upgrade a single IP core, type the following command:

```

quartus_sh --ip_upgrade -variation_files <my_ip_path> <project>

```

To upgrade a list of IP cores, type the following command:

```

quartus sh --ip upgrade -variation files

```

IP cores older than Quartus II software version 12.0 do not support upgrade. Altera verifies that the current version of the Quartus II software compiles the previous version of each IP core. The MegaCore IP Library Release Notes reports any verification exceptions for MegaCore IP. The Quartus II Software and Device Support Release Notes reports any verification exceptions for other IP cores. Altera does not verify compilation for IP cores older than the previous two releases.

## **DSP Builder Design Flow**

DSP Builder shortens digital signal processing (DSP) design cycles by helping you create the hardware representation of a DSP design in an algorithm-friendly development environment.

This IP core supports DSP Builder. Use the DSP Builder flow if you want to create a DSP Builder model that includes an IP core variation; use IP Catalog if you want to create an IP core variation that you can instantiate manually in your design.

For more information about the DSP Builder flow, refer to the *Using MegaCore* Functions chapter in the DSP Builder Handbook.

This chapter describes the FIR Compiler II parameters.

For information about using the parameter editor, refer to "Customizing and Generating IP Cores" on page 2–2.

The **Parameters** contains the following three pages:

- Filter Specification Parameters

- Input and Output Options Page

- Implementation Options

### **Filter Specification Parameters**

A FIR filter is defined by its coefficients. The FIR Compiler II provides the following options for obtaining coefficients:

- Specify the filter settings and coefficient options in the parameter editor. The FIR Compiler II provides a default 37-tap coefficient set regardless of the configurations from filter settings. The scaled value and fixed point value are recalculated based on the coefficient bit width setting. The higher the coefficient bit width, the closer the fixed frequency response is to the intended original frequency response with the expense of higher resource usage.

- Load the coefficients from a file. For example, you can create the coefficients in another application such as MATLAB or a user-created program, save the coefficients to a file, and import them into the FIR Compiler II. For more information, refer to "Loading Coefficients from a File" on page 3–2.

Table 3–1 lists the filter specification parameters.

Table 3-1. Filter Specification Parameters (Part 1 of 2)

| Parameter            | Value           | Description                                                                                                    |  |  |  |  |  |  |  |

|----------------------|-----------------|----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Filter Settings      |                 |                                                                                                                |  |  |  |  |  |  |  |

|                      | Single Rate     |                                                                                                                |  |  |  |  |  |  |  |

| Filter Type          | Decimation      | Specifies the type of FIR filter. The default value is <b>Single</b>                                           |  |  |  |  |  |  |  |

|                      | Interpolation   | Rate.                                                                                                          |  |  |  |  |  |  |  |

|                      | Fractional Rate |                                                                                                                |  |  |  |  |  |  |  |

| Interpolation Factor | 1 to 128        | Specifies the number of extra points to generate between the original samples. The default value is <b>1</b> . |  |  |  |  |  |  |  |

| Decimation Factor    | 1 to 128        | Specifies the number of data points to remove between the original samples. The default value is <b>1</b> .    |  |  |  |  |  |  |  |

|                      | All taps        | Specifies the appropriate L-band Nyquist filters. Every <i>L</i> th                                            |  |  |  |  |  |  |  |

| L-th Band Filter     | Half band       | coefficient of these filters is zero, counting out from the                                                    |  |  |  |  |  |  |  |

|                      | 3rd-5th         | center tap. The default value is <b>All taps</b> .                                                             |  |  |  |  |  |  |  |

| Number of Channels   | 1–128           | Specifies the number of unique input channels to process. The default is <b>1</b> .                            |  |  |  |  |  |  |  |

Table 3–1. Filter Specification Parameters (Part 2 of 2)

| Parameter                           | Value                                  | Description                                                                                                                                                                                                                                                                                 |  |

|-------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Coefficient Options                 |                                        |                                                                                                                                                                                                                                                                                             |  |

| Coefficient Scaling                 | Auto<br>None                           | Specifies the coefficient scaling mode. Select <b>Auto</b> to apply a scaling factor in which the maximum coefficient value equals the maximum possible value for a given number of bits. Select <b>None</b> to read in pre-scaled integer values for the coefficients and disable scaling. |  |

| Coefficient Data Type               | Signed Binary Signed Fractional Binary | Specifies the coefficient input data type. Select <b>Signed Fractional Binary</b> to monitor which bits are preserved and which bits are removed during the filtering process.                                                                                                              |  |

| Coefficient Bit Width               | 2–32                                   | Specifies the width of the coefficients. The default value is <b>8</b> bits.                                                                                                                                                                                                                |  |

| Coefficient Fractional Bit<br>Width | 0–32                                   | Specifies the width of the coefficient data input into the filter when you select <b>Signed Fractional Binary</b> as your coefficient data type.                                                                                                                                            |  |

| Frequency Response Display          |                                        |                                                                                                                                                                                                                                                                                             |  |

| Show Coeffificient Bank             | 0-Number of coefficient bank -1        | Specifies the coefficient bank to display in the coefficient table and frequency response graph.                                                                                                                                                                                            |  |

| File Path                           |                                        |                                                                                                                                                                                                                                                                                             |  |

| File Path                           | URL                                    | Specifes the file from which to load coefficients. Refer to "Loading Coefficients from a File".                                                                                                                                                                                             |  |

### **Loading Coefficients from a File**

To load a coefficient set from a file, perform the following steps:

- 1. In the **File Path** box, specify the name of the **.txt** file containing the coefficient set.

- In the .txt file, separate the coefficients file by either white space or commas or both.

- Use new lines to separate banks.

- You may use blank lines as the FIR Compiler II ignores them.

- You may use floating-point or fixed-point numbers, and scientific notation.

- Use a # character to add comments.

- Specify an array of coefficient sets to support multiple coefficient sets.

- Specify the number of rows to specify the number of banks.

- All coefficient sets must have the same symmetry type and number of taps. For example:

# bank 1 and 2 are symmetric

1, 2, 3, 2, 1

$1\,3\,4\,3\,1$

# bank 3 is anti-symmetric 1 2 0 -2 -1

# bank 4 is asymmetric 1,2,3,4,5

The file must have a minimum of five non-zero coefficients.

2. In the **Filter Specification** tab of the parameter editor, click **Apply** to import the coefficient set.

When you import a coefficient set, the frequency response of the floating-point coefficients is displayed in blue and the frequency response of the fixed-point coefficients is displayed in red.

The FIR Compiler II supports scaling on the coefficient set.

# **Input and Output Options Page**

Table 3–2 lists the parameter options.

Table 3-2. Input and Output Options

| Parameter                   | Value                                     | Description                                                                                                                                                                                                                              |  |

|-----------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Input Options               |                                           |                                                                                                                                                                                                                                          |  |

| Input Data Type             | Signed Binary<br>Signed Fractional Binary | Specifies whether the input data is in a signed binary or a signed fractional binary format. Select <b>Signed Fractional Binary</b> to monitor which bits the IP core preserves and which bits it removes during the filtering process.  |  |

| Input Bit Width             | 1–32                                      | Specifies the width of the input data sent to the filter. The default value is <b>8</b> bits.                                                                                                                                            |  |

| Input Fractional Bit Width  | 0–32                                      | Specifies the width of the data input into the filter when you select <b>Signed Fractional Binary</b> as your input data type. The default value is <b>0</b> bits.                                                                       |  |

|                             | Output O                                  | ptions                                                                                                                                                                                                                                   |  |

| Output Data Type            | Signed Binary<br>Signed Fractional Binary | Specifies whether the output data is in a signed binary or a signed fractional binary format. Select <b>Signed Fractional Binary</b> to monitor which bits the IP core preserves and which bits it removes during the filtering process. |  |

| Output Bit Width            | 0–32                                      | Specifies the width of the output data (with limited precision) from the filter.                                                                                                                                                         |  |

| Output Fractional Bit Width | 0–32                                      | Specifies the width of the output data (with limited precision) from the filter when you select <b>Signed Fractional Binary</b> as your output data.                                                                                     |  |

| Output MSB rounding         | Truncation/ Saturating                    | Specifies whether to truncate or saturate the most significant bit (MSB).                                                                                                                                                                |  |

| MSB Bits to Remove          | 0–32                                      | Specifies the number of MSB bits to truncate or saturate. The value must not be greater than its corresponding integer bits or fractional bits.                                                                                          |  |

Table 3-2. Input and Output Options

| Parameter           | Value                | Description                                                                                                                                  |

|---------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Output LSB rounding | Truncation/ Rounding | Specifies whether to truncate or round the least significant bit (LSB).                                                                      |

| LSB Bits to Remove  | 0–32                 | Specifies the number of LSB bits to truncate or round. The value must not be greater than its corresponding integer bits or fractional bits. |

### **Signed Fractional Binary**

The FIR Compiler II supports two's complement, signed fractional binary notation, which allows you to monitor which bits the IP core preserves and which bits it removes during filtering. A signed binary fractional number has the format:

<sign> <integer bits>.<fractional bits>

A signed binary fractional number is interpreted as shown below:

$\langle sign \rangle \langle x_1 | integer bits \rangle. \langle y_1 | fractional bits \rangle$  Original input data  $\langle sign \rangle \langle x_2 | integer bits \rangle. \langle y_2 | fractional bits \rangle$  Original coefficient data  $\langle sign \rangle \langle i | integer bits \rangle. \langle y_1 + y_2 | fractional bits \rangle$  Full precision after FIR calculation  $\langle sign \rangle \langle x_3 | integer bits \rangle. \langle y_3 | fractional bits \rangle$  Output data after limiting precision where  $i = \text{ceil}(\log_2(number \ of \ coefficients)) + x_1 + x_2$

For example, if the number has 3 fractional bits and 4 integer bits plus a sign bit, the entire 8-bit integer number is divided by 8, which gives a number with a binary fractional component.

The total number of bits equals to the sign bits + integer bits + fractional bits. The sign + integer bits is equal to **Input Bit Width** – **Input Fractional Bit Width** with a constraint that at least 1 bit must be specified for the sign.

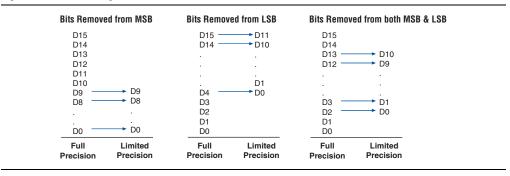

### **MSB** and **LSB** Truncation, Saturation, and Rounding

The output options on the parameter editor allow you to truncate or saturate the MSB and to truncate or round the LSB. Saturation, truncation, and rounding are non-linear operations.

Table 3–1 lists the options for limiting the precision of your filter.

Table 3-1. Options for Limiting Precision

| Bit Range | Option   | Result                                                                                                                                                                                               |

|-----------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSB       | Truncate | In truncation, the filter disregards specified bits. (Figure 3–1).                                                                                                                                   |

|           | Saturate | In saturation, if the filtered output is greater than the maximum positive or negative value that can be represented, the output is forced (or saturated) to the maximum positive or negative value. |

| LSB       | Truncate | Same process as for MSB.                                                                                                                                                                             |

|           | Round    | The output is rounded away from zero.                                                                                                                                                                |

Figure 3–1 shows an example of removing bits from the MSB and LSB.

Figure 3-1. Removing Bits from the MSB and LSB

# **Implementation Options**

Table 3–3 lists the implementation options.

Table 3-3. Implementation Options (Part 1 of 2)

| Parameter                | Value            | Description                                                                                                                                                                                             |

|--------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Frequency Specification  |                  |                                                                                                                                                                                                         |

| Clock Frequency (MHz)    | 1–500            | Specifies the frequency of the input clock. The default value is <b>100</b> MHz.                                                                                                                        |

| Clock Slack              | Integer          | Enables you to control the amount of pipelining independently of the clock frequency and therefore independently of the clock to sample rate ratio. The default value is <b>0</b> .                     |

| Input Sample Rate (MSPS) | Integer          | Specifies the sample rate of the incoming data. The default is <b>100</b> .                                                                                                                             |

|                          | Fast             | Specifies the speed grade of the target device to balance the                                                                                                                                           |

| Speed Grade              | Medium           | size of the hardware against the resources required to meet the                                                                                                                                         |

|                          | Slow             | clock frequency. The default value is <b>Medium</b> .                                                                                                                                                   |

|                          | Symm             | etry Option                                                                                                                                                                                             |

|                          | Non Symmetry     | Specifies whether your filter design uses non-symmetric,                                                                                                                                                |

| Symmetry Mode            | Symmetrical      | symmetric, or anti-symmetric coefficients. The default value is                                                                                                                                         |

|                          | Anti-Symmetrical | Non Symmetry.                                                                                                                                                                                           |

|                          | Coefficients     | Reload Options                                                                                                                                                                                          |

| Coefficients Reload      | _                | Turn on this option to allow coefficient reloading. This option allows you to change coefficient values during run time. When this option is turned on, additional input ports are added to the filter. |

| Base Address             | Integer          | Specifies the base address of the memory-mapped coefficients.                                                                                                                                           |

| Read/Write mode          | Read             | Consider the read and write made that determines the time of                                                                                                                                            |

|                          | Write            | Specifies the read and write mode that determines the type of address decode to build.                                                                                                                  |

|                          | Read/Write       |                                                                                                                                                                                                         |

**Chapter 3: Parameters** Implementation Options

Table 3–3. Implementation Options (Part 2 of 2)

| Parameter                               | Value                     | Description                                                                                                                                                                                                            |  |

|-----------------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Flow Control                            |                           |                                                                                                                                                                                                                        |  |

| Back Pressure Support                   | _                         | Turn on this option to enable backpressure support. When this option is turned on, the sink signals the source to stop the flow of data when its FIFO buffers are full or when there is congestion on its output port. |  |

| Resource Optimization Settings          |                           |                                                                                                                                                                                                                        |  |

| Device Family                           | Menu of supported devices | Specifies the target device family.                                                                                                                                                                                    |  |

| LEs / Small RAM Block<br>Threshold      | Integer                   | Specifies the balance of resources between LEs/Small RAM block threshold in bits. The default value is <b>20</b> . For more information, refer to "Memory and Multiplier Trade-Offs" on page 3–6.                      |  |

| Small / Medium RAM<br>Block Threshold   | Integer                   | Specifies the balance of resources between small to medium RAM block threshold in bits. The default value is <b>1280</b> . For more information, refer to "Memory and Multiplier Trade-Offs" on page 3–6.              |  |

| Medium / Large RAM<br>Block Threshold   | Integer                   | Specifies the balance of resources between medium to large RAM block threshold in bits. The default value is <b>1000000</b> . For more information, refer to "Memory and Multiplier Trade-Offs" on page 3–6.           |  |

| LEs / DSP Block Multiplier<br>Threshold | Integer                   | Specifies the balance of resources between LEs/ DSP block multiplier threshold in bits. The default value is <b>-1</b> . For more information, refer to "Memory and Multiplier Trade-Offs" on page 3–6.                |  |

## **Memory and Multiplier Trade-Offs**

When the quartus II software synthesizes your design to logic, it often creates delay blocks. The FIR Compiler II tries to balance the implementation between logic elements (LEs) and memory blocks (M512, M4K, M9K, or M144K). The exact trade-off depends on the target FPGA family, but generally the trade-off attempts to minimize the absolute silicon area used. For example, if a block of RAM occupies the silicon area of two logic array blocks (LABs), a delay requiring more than 20 LEs (two LABs) is implemented as a block of RAM. However, you want to influence this trade-off.

These topics describe the memory and multiplier threshold trade-offs, and provide some usage examples.

#### **Using LEs / Small RAM Block Threshold**

This threshold is the trade-off between simple delay LEs and small ROM blocks. If any delay's size is such that the number of LEs is greater than this parameter, the IP core implements delay as block RAM. The default value is 20 bits.

- 1. To make more delays using block RAM, enter a lower number, such as a value in the range of 20–30.

- 2. To use fewer block memories, enter a larger number, such as 100.

- 3. To never use block memory for simple delays, enter a very large number, such as 10000.

- 4. Implement delays of less than three cycles in LEs because of block RAM behavior.

This threshold only applies to implementing simple delays in memory blocks or logic elements. You cannot push dual memories back into logic elements.

#### **Using Small / Medium RAM Block Threshold**

This threshold is trade-off between small and medium RAM blocks. This threshold is similar to the **Using LEs / Small RAM Block Threshold** except that it applies only to the dual-port memories.

The IP core implements any dual-port memory in a block memory rather than logic elements, but for some device families different sizes of block memory may be available. The threshold value determines which medium-size RAM memory blocks IP core implements instead of small-memory RAM blocks. For example, the threshold that determines whether to use M9K blocks rather than MLAB blocks on Stratix IV devices.

The default value is 1,290 bits.

- 1. Set the default threshold value, to implement dual memories greater than 1,280 bits as M9K blocks and dual memories less than or equal to 1,280 bits as MLABs.

- 2. Change this threshold to a lower value such as 200, to implement dual memories greater than 200 bits as M9K blocks and dual memories less than or equal to 200 bits as MLAB blocks.

For device families with only one type of memory block, this threshold has no effect.

#### **Using Medium / Large RAM Block Threshold**

This threshold is the trade-off between medium and large RAM blocks. For larger delays, implement memory in medium-block RAM (M4K, M9K) or use larger M-RAM blocks (M512K, M144K).

The default value is 1,000,000 bits.

- 1. Set the number of bits in a memory or delay greater than this threshold, to use M-RAM.

- 2. Set a large value such as the default of 1,000,000 bits, to never uses M-RAM blocks.

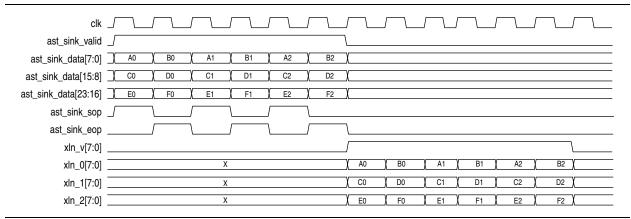

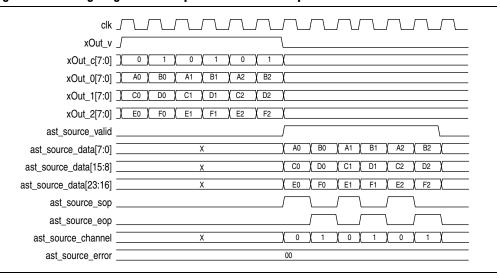

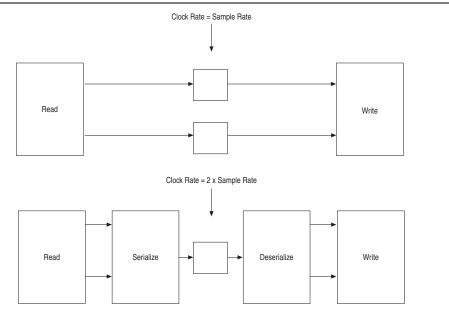

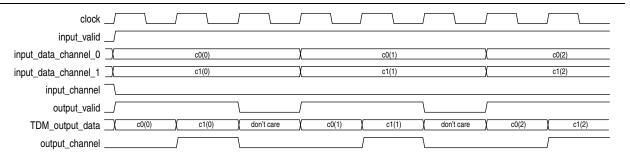

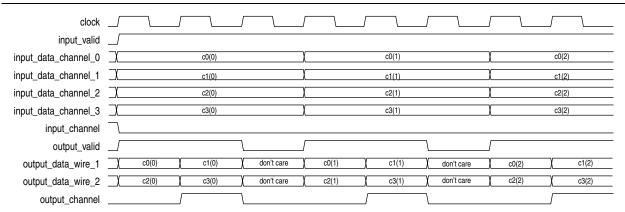

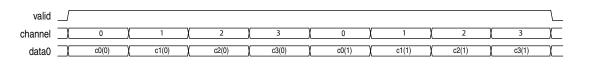

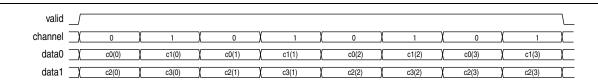

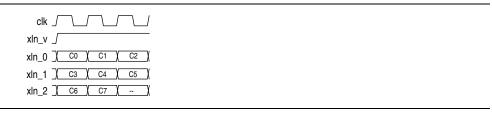

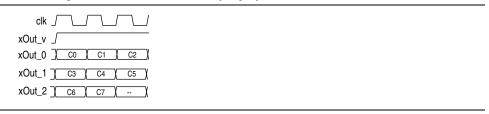

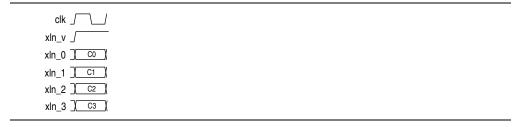

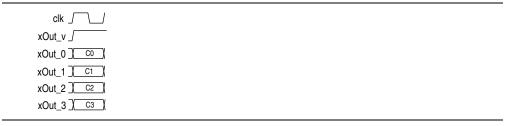

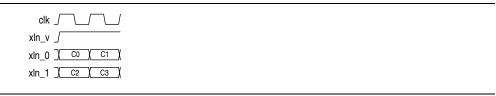

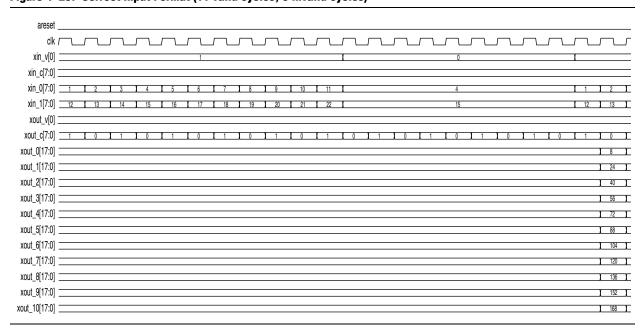

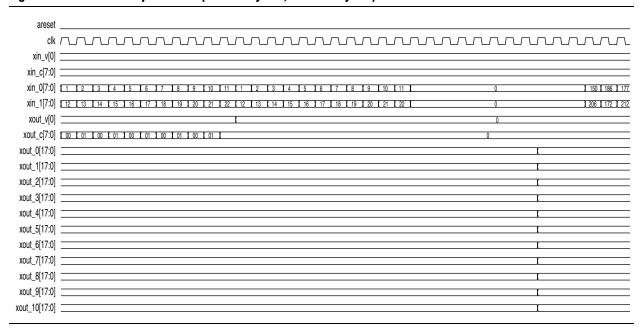

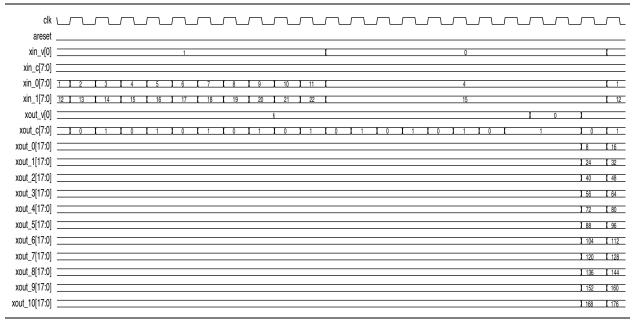

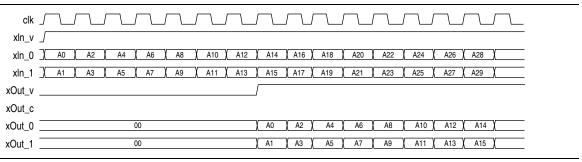

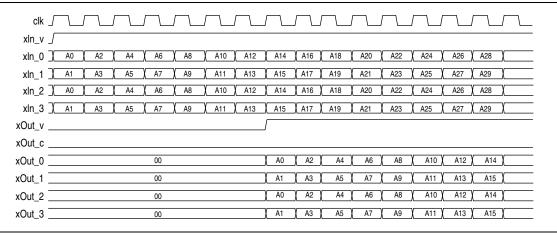

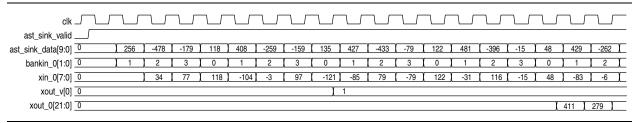

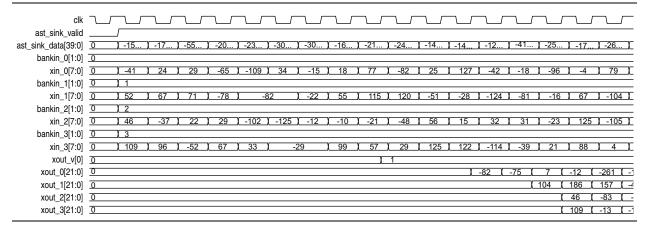

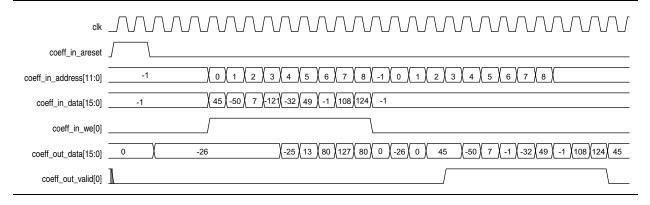

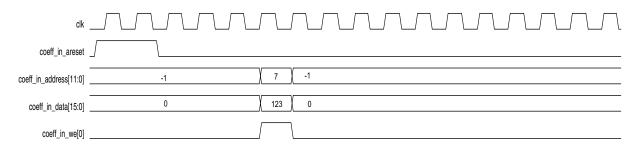

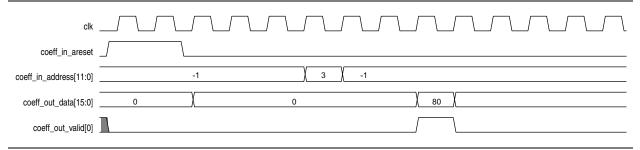

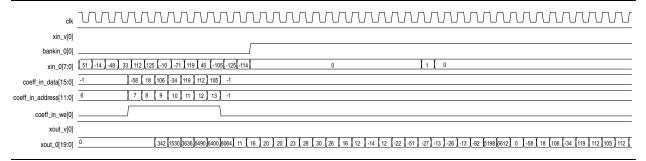

#### Using the LEs / DSP Block Multiplier Threshold