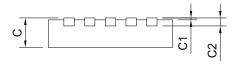

**DFN10**

Representations only, not actual markings

# **IQS624 DATASHEET**

Combination sensor including: Hall-effect rotation sensing, along with dual-channel capacitive proximity/touch sensing, or single-channel inductive sensing.

The IQS624 ProxFusion® IC is a multifunctional capacitive and Hall-effect sensor designed for applications where any or all the technologies may be required. The two Hall-effect sensors calculate the angle of a magnet rotating parallel with the sensor. The sensor is fully I2C compatible and onchip calculations enable the IC to stream the current angle of the magnet without extra calculations.

#### **Features**

- Hall effect angle sensor:

- On-chip Hall plates

- 360° Absolute Output

- 1° Resolution\*, calculated on chip

- Relative rotation angle.

- Detect movement and the direction of movement.

- Raw data: can be used to calculate degrees on external processor.

- Wide operational range

- No external components required

- Partial auto calibration:

- Continuous auto-calibration, compensation for wear or small displacements of the sensor or magnet.

- Flexible gain control

- Automatic Tuning Implementation (ATI) -Performance enhancement (10 bit).

- Capacitive sensing

- Full auto-tuning with adjustable sensitivity

- 2pF to 200pF external capacitive load capability

#### Inductive sensing

Only external sense coil required (PCB trace)

- Proximity / Touch

- Proximity wake-up

- Event mode

- Wake Hall sensing on proximity

- Minimal external components

- Standard I<sup>2</sup>C interface

- Optional RDY indication for event mode operation

- Low power consumption:

- 240uA (100Hz response, Hall),

- 55uA (100Hz response, capacitive),

- 65uA (20Hz response, Hall)

- 15uA (20Hz response, capacitive)

- 5uA (5Hz response, capacitive)

- Supply Voltage: 2.0V to 3.6V\*\*

#### **Applications**

- Anemometer

- Dial or Selector knob

- Mouse wheel

- Measuring wheel

- Digital angle gauge

- Speedometer for bicycle

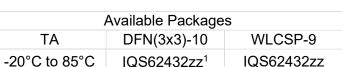

| Available Packages     |                         |            |  |  |  |  |

|------------------------|-------------------------|------------|--|--|--|--|

| TA DFN(3x3)-10 WLCSP-9 |                         |            |  |  |  |  |

| -20°C to 85°C          | IQS62432zz <sup>1</sup> | IQS62432zz |  |  |  |  |

<sup>1</sup>All versions

<sup>\*</sup>Optimal conditions

<sup>\*\*5</sup>V solution available on demand.

### **Contents**

| IC | QS624 DATA | <b>\</b> SHEET                             | 1  |

|----|------------|--------------------------------------------|----|

| 1  | INTROD     | UCTION                                     | 5  |

|    | 1.1        | ProxFusion®                                | 5  |

|    | 1.2        | PACKAGING AND PIN-OUT                      |    |

|    | 1.3        | REFERENCE SCHEMATIC                        |    |

|    | 1.4        | SENSOR CHANNEL COMBINATIONS                | 7  |

|    | 1.5        | ProxFusion® Sensitivity                    | 8  |

| 2  | CAPACI     | TIVE SENSING                               | 9  |

|    | 2.1        | Introduction                               | O  |

|    | 2.2        | CHANNEL SPECIFICATIONS                     |    |

|    | 2.3        | HARDWARE CONFIGURATION                     |    |

|    | 2.4        | REGISTER CONFIGURATION                     |    |

|    | 2.5        | SENSOR DATA OUTPUT AND FLAGS               |    |

| 3  |            | IVE SENSING                                |    |

|    | 3.1        | INTRODUCTION TO INDUCTIVE SENSING          |    |

|    | 3.2        | CHANNEL SPECIFICATIONS                     |    |

|    | 3.3        | HARDWARE CONFIGURATION.                    |    |

|    | 3.4        | REGISTER CONFIGURATION                     |    |

|    | 3.5        | SENSOR DATA OUTPUT AND FLAGS               |    |

| 4  |            | FFECT SENSING                              |    |

| _  | 4.1        | INTRODUCTION TO HALL-EFFECT SENSING        |    |

|    | 4.1        | CHANNEL SPECIFICATIONS                     |    |

|    | 4.3        | HARDWARE CONFIGURATION                     |    |

|    | 4.4        | REGISTER CONFIGURATION                     |    |

|    | 4.5        | EXAMPLE CODE:                              |    |

|    | 4.6        | SENSOR DATA OUTPUT AND FLAGS               |    |

|    | 4.7        | IQS62432 INTERVAL UI                       |    |

|    | 4.8        | IQS62432 EXAMPLE                           |    |

|    | 4.9        | IQS62432 WHEEL WAKE PRELOAD (0x7C)         |    |

|    | 4.10       | IQS62432 EVENT MODE OPTIONS                |    |

| 5  | DEVICE     | CLOCK, POWER MANAGEMENT AND MODE OPERATION | 22 |

|    | 5.1        | DEVICE MAIN OSCILLATOR                     | 22 |

|    | 5.2        | DEVICE MODES                               | 22 |

| 6  | REPORT     | 「RATES                                     | 24 |

|    | 6.1        | NORMAL POWER MAXIMUM REPORT RATE           | 24 |

| 7  | SYSTEM     | I RESET                                    | 24 |

| 8  | COMMU      | NICATION                                   | 25 |

|    | 8.1        | CONTROL BYTE                               | 25 |

|    | 8.2        | I2C READ                                   |    |

|    | 8.3        | I2C Write                                  |    |

|    | 8.4        | END OF COMMUNICATION SESSION / WINDOW      |    |

|    | 8.5        | STOP-BIT DISABLE OPTION(IQS62432)          |    |

|    | 8.6        | DEVICE ADDRESS AND SUB-ADDRESSES           |    |

|    | 8.7        | ADDITIONAL OTP OPTIONS                     | 27 |

|    | 8.8        | REQUEST COMMUNICATION WINDOW               | 28 |

|    |            |                                            |    |

| 8.9    | I <sup>2</sup> C SPECIFIC COMMANDS                 | 28 |

|--------|----------------------------------------------------|----|

| 8.10   | RECOMMENDED COMMUNICATION AND RUNTIME FLOW DIAGRAM | 29 |

| 9 IQS  | 6624 MEMORY MAP                                    | 30 |

| 9.2    | DEVICE INFORMATION                                 | 32 |

| 9.3    | DEVICE SPECIFIC DATA                               |    |

| 9.4    | COUNT DATA                                         |    |

| 9.5    | PROXFUSION SENSOR SETTINGS                         | 36 |

| 9.6    | Touch / Proximity UI settings                      | 39 |

| 9.7    | HALL SENSOR SETTINGS                               | 40 |

| 9.8    | HALL WHEEL OUTPUT                                  |    |

| 9.9    | DEVICE AND POWER MODE SETTINGS                     | 47 |

| 10 ELE | ECTRICAL CHARACTERISTICS                           | 51 |

| 10.1   | ABSOLUTE MAXIMUM SPECIFICATIONS                    | 51 |

| 10.2   | VOLTAGE REGULATION SPECIFICATIONS                  | 51 |

| 10.3   | RESET CONDITIONS                                   | 51 |

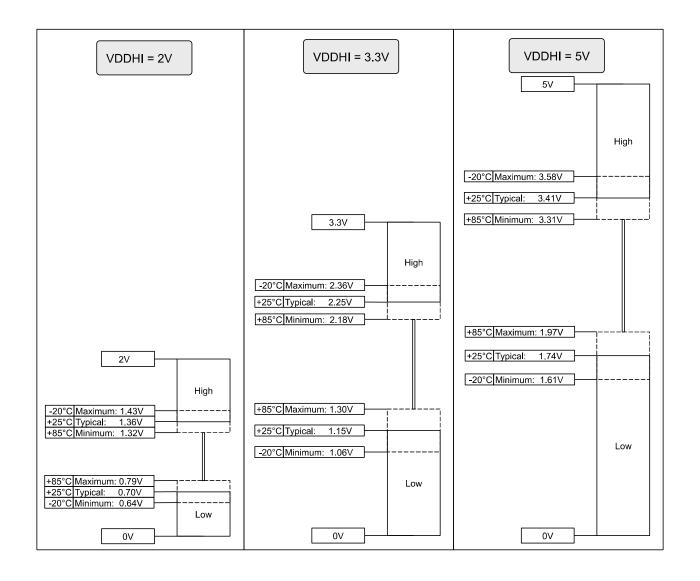

| 10.4   | DIGITAL INPUT/OUTPUT TRIGGER LEVELS                | 52 |

| 10.5   | CURRENT CONSUMPTIONS                               | 53 |

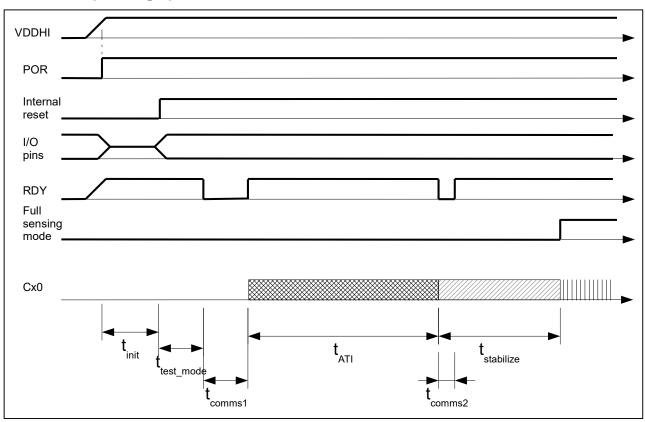

| 10.6   | START-UP TIMING SPECIFICATIONS                     | 55 |

| 11 PA  | CKAGE INFORMATION                                  | 56 |

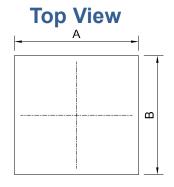

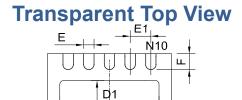

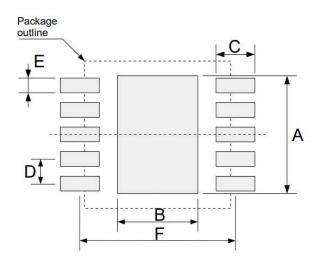

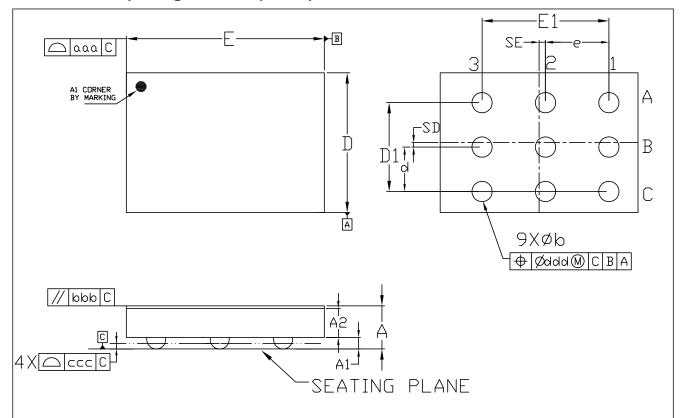

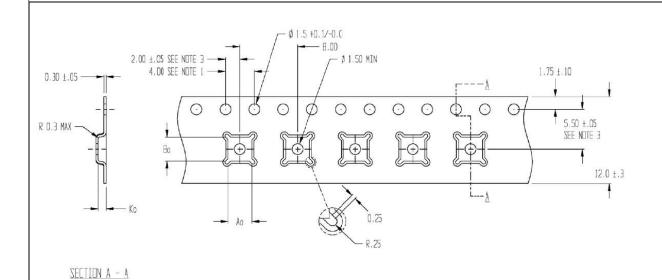

| 11.1   | DFN10 PACKAGE AND FOOTPRINT SPECIFICATIONS         | 56 |

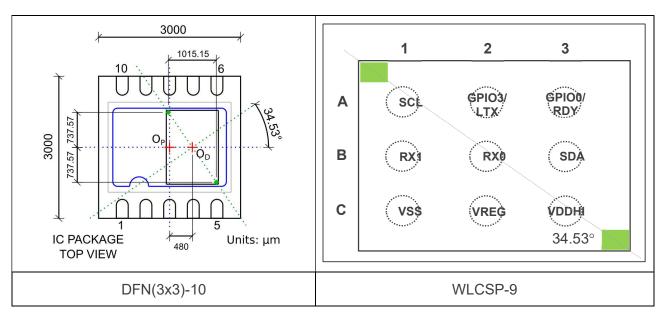

| 11.2   | WLCSP-9 PACKAGE AND FOOTPRINT SPECIFICATIONS       | 57 |

| 11.3   | DEVICE MARKING AND ORDERING INFORMATION            | 58 |

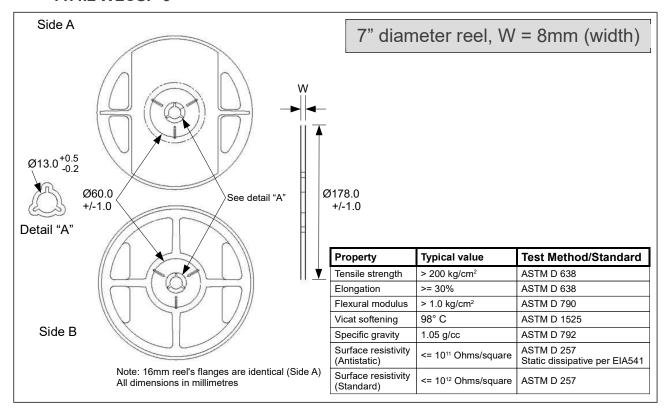

| 11.4   | TAPE AND REEL SPECIFICATION                        | 59 |

| 11.5   | MSL Level                                          | 60 |

| 12 DA  | TASHEET REVISIONS                                  | 61 |

| 12.1   | REVISION HISTORY                                   | 61 |

| 12.2   | ERRATA                                             | 62 |

| 13 API | PENDICES                                           | 64 |

| 13.1   | APPENDIX A: MAGNET ORIENTATION                     | 64 |

| 13.2   | APPENDIX B: MAGNET CALIBRATION                     | 67 |

| 13.3   | APPENDIX C: HALL ATI                               | 73 |

|        |                                                    |    |

#### List of abbreviations

PXS - ProxSense®

ATI – Automatic Tuning Implementation

LTA – Long term average

Thr - Threshold

UI – User interface

AC – Alternating current

DSP - Digital signal processing

RX - Receiving electrode

TX – Transmitting electrode

CS - Sampling capacitor

C - Capacitive

NP - Normal power

LP - Low power

ULP - Ultra low power

ACK – I<sup>2</sup>C Acknowledge condition

NACK – I<sup>2</sup>C Not Acknowledge condition

FG - Floating gate

### 1 Introduction

#### 1.1 ProxFusion®

The ProxFusion® sensor series provide all the proven ProxSense® engine capabilities with additional sensors types. A combined sensor solution is available within a single platform.

## 1.2 Packaging and Pin-Out

# 1.2.1 DFN(3x3)-10

Figure 1.1 Pin out of IQS624 DFN (3X3)-10 package.

# Table 1.1 IQS624 Pin-out

|     | IQS624 Pin-out       |                        |                              |  |  |  |  |  |  |

|-----|----------------------|------------------------|------------------------------|--|--|--|--|--|--|

| Pin | Name                 | Type                   | Function                     |  |  |  |  |  |  |

| 1   | SDA                  | Digital Input / Output | I <sup>2</sup> C: SDA Output |  |  |  |  |  |  |

| 2   | 2 RDY Digital Output |                        | I <sup>2</sup> C: RDY Output |  |  |  |  |  |  |

| 3   | VDDHI                | Supply Input           | Supply Voltage Input         |  |  |  |  |  |  |

| 4   | VREG                 | Regulator Output       | Internal Regulator Pin       |  |  |  |  |  |  |

| 5   | LTX                  | Analogue               | Transmit Electrode 1         |  |  |  |  |  |  |

| 6   | CRX0                 | Analogue               | Sense Electrode 0            |  |  |  |  |  |  |

| 7   | CRX1                 | Analogue               | Sense Electrode 1            |  |  |  |  |  |  |

| 8   | SCL                  | Digital Input / Output | I <sup>2</sup> C: SCL Output |  |  |  |  |  |  |

| 9   | NC                   | Not connect            | Not connect                  |  |  |  |  |  |  |

| 10  | VSS                  | Supply Input           | Ground Reference             |  |  |  |  |  |  |

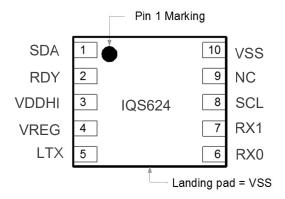

### 1.2.2 WLCSP-9

Figure 1.2 IQS624 pin-out (WLCSP-9 package top view; markings may differ)

Table 1.2 WLCSP-9 pin-out description

#### IQS620A in WLCSP-9

| Pin | Name           | Туре                                            | Function                                                                          |

|-----|----------------|-------------------------------------------------|-----------------------------------------------------------------------------------|

| A1  | SCL            | Digital input / output                          | SCL (I <sup>2</sup> C Clock signal)                                               |

| A2  | GPIO3 /<br>LTX | Digital output / Analogue transmitter electrode | Connect to inductive sensor's transmitting coil                                   |

| АЗ  | GPIO0 /<br>RDY | Digital output Open drain active low logic      | RDY (I <sup>2</sup> C Ready interrupt signal)                                     |

| B1  | RX1            | Analogue receiving electrode                    | Sense Electrode 1                                                                 |

| B2  | RX0            | Analogue receiving electrode                    | Sense Electrode 0                                                                 |

| B3  | SDA            | Digital input / output                          | SDA (I <sup>2</sup> C Data signal)                                                |

| C1  | VSS            | Supply input                                    | Common ground reference                                                           |

| C2  | VREG           | Voltage regulator output                        | Regulates the system's internal voltage<br>Requires external capacitors to ground |

| C3  | VDDHI          | Supply input                                    | Supply Voltage Input                                                              |

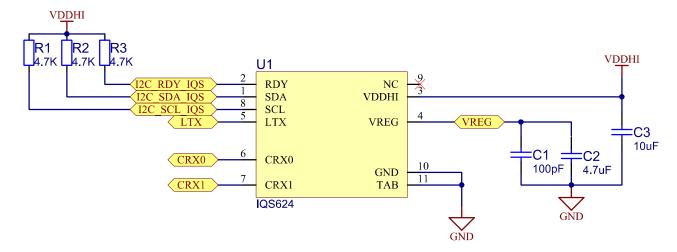

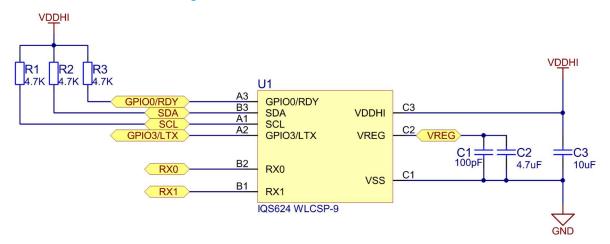

#### 1.3 Reference schematic

Figure 1.3 IQS624 reference schematic

Figure 1.4 IQS624 WLCSP-9 reference schematic

#### 1.4 Sensor channel combinations

The table below summarizes the IQS624's sensor and channel associations.

Sensor type CH<sub>0</sub> CH1 CH<sub>2</sub> CH3 CH4 CH<sub>5</sub> **Discreet Self** 0 Capacitive Hall effect rotary 1st plate 2<sup>nd</sup> plate 2<sup>nd</sup> plate 1st plate UI Positive Negative Positive Negative **Mutual Inductive** 0  $\circ$

Table 1.3 Sensor - channel allocation

#### Key:

- o Optional implementation

- Fixed use for UI

## 1.5 ProxFusion® Sensitivity

The measurement circuitry uses a temperature stable internal sample capacitor ( $C_S$ ) and internal regulated voltage ( $V_{REG}$ ). Internal regulation provides for more accurate measurements over temperature variation. The size of the sample capacitor can be decreased to increase sensitivity on the capacitive channels of the IQS624.

Sensitivity

$$\propto \frac{1}{C_s}$$

The Automatic Tuning Implementation (ATI) is a sophisticated technology implemented on the ProxFusion® series devices. It allows for optimal performance of the devices for a wide range of sense electrode capacitances, without modification or addition of external components. The ATI functionality ensures that sensor sensitivity is not affected by external influences such as temperate, parasitic capacitance and ground reference changes.

The ATI process adjusts three values (Coarse multiplier, Fine multiplier, Compensation) using two parameters (ATI base and ATI target) as inputs. A 10-bit compensation value ensures that an accurate target is reached. The base value influences the overall sensitivity of the channel and establishes a base count from where the ATI algorithm starts adding compensation. A rough estimation of sensitivity can be calculated as:

Sensitivity

$$\propto \frac{Target}{Base}$$

As seen from this equation, the sensitivity can be increased by either increasing the Target value or decreasing the Base value. A lower base value will typically result in lower multipliers and more compensation would be required. It should, however, be noted that a higher sensitivity will yield a higher noise susceptibility. Refer to <a href="Appendix B">Appendix B</a> and <a href="Appendix C">Appendix C</a> for more information on Hall ATI.

## 2 Capacitive sensing

### 2.1 Introduction

Building on the previous successes from the ProxSense® range of capacitive sensors, the same fundamental sensor engine has been implemented in the ProxFusion® series.

## 2.2 Channel specifications

The IQS624 provides a maximum of 2 channels available to be configured for capacitive sensing. Each channel can be setup separately using the channel's associated settings registers.

Table 2.1 Capacitive sensing - channel allocation

| Sensor type              | СН0 | CH1 | CH2 | СНЗ | CH4 | CH5 |

|--------------------------|-----|-----|-----|-----|-----|-----|

| Discreet Self Capacitive | 0   | 0   |     |     |     |     |

#### Key:

Optional implementation

- o Optional implementation

- Fixed use for UI

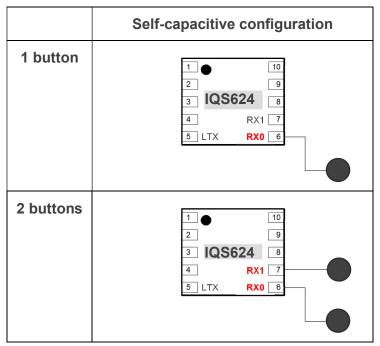

## 2.3 Hardware configuration

In the table below are two options of configuring sensing (Rx) electrodes.

Table 2.2 Capacitive hardware description

## 2.4 Register configuration

#### 2.4.1 Registers to configure for the capacitive sensing:

Table 2.3 Capacitive sensing settings registers

| Address           | Name                             | Description                                       | Recommended setting                                                                       |  |  |

|-------------------|----------------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------|--|--|

| <u>0x40, 0x41</u> | Ch0/Ch1 ProxFusion<br>Settings 0 | Sensor mode and configuration of each channel.    | Sensor mode should be set to capacitive mode An appropriate RX should be chosen and no TX |  |  |

| <u>0x42</u>       | Ch0&Ch1 ProxFusion Settings 1    | Global settings for the ProxFusion sensors        | None                                                                                      |  |  |

| <u>0x43, 0x44</u> | Ch0/Ch1 ProxFusion<br>Settings 2 | ATI settings for ProxFusion sensors               | ATI target should be more than ATI base to achieve an ATI                                 |  |  |

| <u>0x45</u>       | Ch0&Ch1 ProxFusion Settings 3    | Additional Global settings for ProxFusion sensors | AC filter should be enabled                                                               |  |  |

| <u>0x50, 0x52</u> | Proximity threshold              | Proximity Threshold for UI                        | Preferably more than touch threshold                                                      |  |  |

| 0x51, 0x53        | Touch threshold                  | Touch Threshold for UI                            | None                                                                                      |  |  |

## 2.4.2 Proximity Thresholds

A proximity threshold for both channels can be selected for the application, to obtain the desired proximity trigger level. The proximity threshold is selectable between 1 (most sensitive) and 255 (least sensitive) counts. These threshold values (i.e. 1-255) are specified in Counts (CS) in the

Ch0 Proximity threshold (0x50) and Ch1 Proximity threshold (0x51) registers for the discreet button UI.

#### 2.4.3 Touch Thresholds

A touch threshold for each channel can be selected by the designer to obtain the desired touch sensitivity and is selectable between 1/256 (most sensitive) to 255/256 (least sensitive). The touch threshold is calculated as a fraction of the Long-Term Average (LTA) given by,

$$T_{THR} = \frac{x}{256} \times LTA$$

With lower target values (therefore lower LTA's) the touch threshold will be lower and vice versa.

Individual touch thresholds can be set for each channel, by writing to the <u>Ch0 Touch threshold (0x51)</u> and <u>Ch1 Touch threshold (0x53)</u> for the discreet button UI.

## 2.4.4 Example code:

Example code for an Arduino Uno can be downloaded at:

www.azoteq.com//images/stories/software/IQS62x Demo.zip

## 2.5 Sensor data output and flags

The following register should be monitored by the master to detect capacitive sensor output.

a) The <u>Proximity/Touch UI Flags (0x12)</u> provide more detail regarding the outputs. A proximity and touch output bit for each channel 0 and 1 is provided in the Proximity/Touch UI Flags register.

| Proximity/Touch UI Flags (0x12) |   |      |                        |                  |   |   |                            |                            |

|---------------------------------|---|------|------------------------|------------------|---|---|----------------------------|----------------------------|

| Bit Number                      | 7 | 6    | 5                      | 4                | 3 | 2 | 1                          | 0                          |

| Data Access                     |   | Read |                        |                  |   |   |                            |                            |

| Name                            |   |      | Chan 1<br>Touch<br>out | Chan 0 touch out |   |   | Chan 1<br>proximity<br>out | Chan 0<br>proximity<br>out |

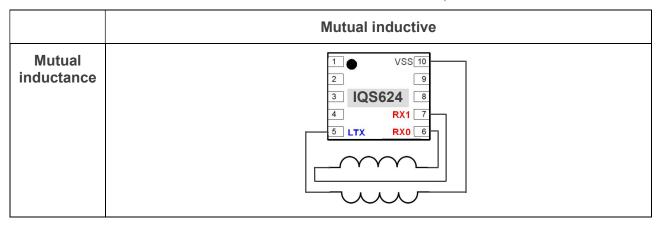

## 3 Inductive sensing

## 3.1 Introduction to inductive sensing

The IQS624 provides inductive sensing capabilities to detect the presence of metal/metal-type objects.

## 3.2 Channel specifications

The IQS624 requires 3 sensing lines for mutual inductive sensing.

A single inductance user interface is available.

a) Discreet proximity/touch UI (always enabled)

Table 3.1 Mutual inductive sensor – channel allocation

| Mode             | СН0 | CH1 | CH2 | СНЗ | CH4 | CH5 |

|------------------|-----|-----|-----|-----|-----|-----|

| Mutual inductive | 0   | 0   |     |     |     |     |

#### Key:

- o Optional implementation

- · Fixed use for UI

## 3.3 Hardware configuration

Rudimentary hardware configurations (to be completed).

Table 3.2 Mutual inductive hardware description

## 3.4 Register configuration

Table 3.3 Inductive sensing settings registers.

| Address           | Name                             | Description                                       | Recommended setting                                                                                                                      |  |  |  |  |

|-------------------|----------------------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| <u>0x40, 0x41</u> | Ch0/Ch1 ProxFusion<br>Settings 0 | Sensor mode and configuration of each channel.    | Sensor mode should be set to Inductive mode Choose one channel and deactivate the other channel Enable both RX for the activated channel |  |  |  |  |

| <u>0x42</u>       | Ch0&Ch1 ProxFusion Settings 1    | Global settings for the ProxFusion sensors        | CS divider should be enabled                                                                                                             |  |  |  |  |

| 0x43, 0x44        | Ch0/Ch1 ProxFusion Settings 2    | ATI settings for<br>ProxFusion sensors            | ATI target should be more than ATI base to achieve an ATI                                                                                |  |  |  |  |

| <u>0x45</u>       | Ch0&Ch1 ProxFusion Settings 3    | Additional Global settings for ProxFusion sensors | None                                                                                                                                     |  |  |  |  |

| <u>0x50, 0x52</u> | Proximity threshold              | Proximity Threshold for UI                        | Less than touch threshold                                                                                                                |  |  |  |  |

| <u>0x51, 0x53</u> | Touch threshold                  | Touch Threshold for UI                            | None                                                                                                                                     |  |  |  |  |

## 3.4.2 Example code:

Example code for an Arduino Uno can be downloaded at:

www.azoteg.com//images/stories/software/IQS62x Demo.zip

### 3.5 Sensor data output and flags

The following register should be monitored by the master to detect capacitive sensor output.

a) The <u>Proximity/Touch UI Flags (0x12)</u> provide more detail regarding the outputs. A proximity and touch output bit for each channel 0 and 1 is provided in the Proximity/Touch UI Flags register.

| Proximity/Touch UI Flags (0x12) |   |      |                        |                        |   |   |                            |                      |

|---------------------------------|---|------|------------------------|------------------------|---|---|----------------------------|----------------------|

| Bit Number                      | 7 | 6    | 5                      | 4                      | 3 | 2 | 1                          | 0                    |

| Data Access                     |   | Read |                        |                        |   |   |                            |                      |

| Name                            |   |      | Chan 1<br>Touch<br>out | Chan 0<br>touch<br>out |   |   | Chan 1<br>proximity<br>out | Chan 0 proximity out |

## 4 Hall-effect sensing

## 4.1 Introduction to Hall-effect sensing

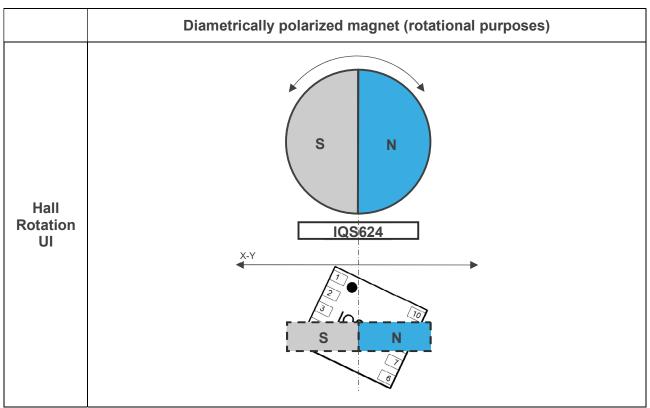

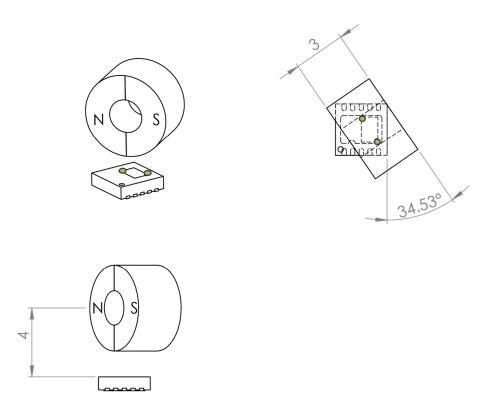

The IQS624 has two internal Hall-effect sensing plates (on die). No external sensing hardware is required for Hall-effect sensing.

The Hall-effect sensor measures the generated voltage difference across the plate, which can be modelled as a Wheatstone bridge. The voltage difference is converted to a current using an operational amplifier in order to be measured by the same ProxSense® sensor engine.

Advanced digital signal processing is performed to provide sensible output data.

- Calculates absolute position in degrees.

- Auto calibration attempts to linearize degrees output on the fly

- Differential Hall-Effect sensing:

- o Removes common mode disturbances

Refer to the Errata for correct setup of the IC.

#### 4.2 Channel specifications

Channels 2 to 5 are dedicated to Hall-effect sensing. Channel 2 & 4 performs the positive direction measurements while channel 3 & 5 handle all measurements in the negative direction. Differential data is obtained from these four channels. This differential data is used as input data to calculate the output angle of the Hall-effect rotation UI. Channel 2 & 3 is used for the one plate and channel 4 & 5 for the second plate.

Table 4.1 Hall-effect sensor – channel allocation

| Mode              | CH0 | CH1 | CH2                                    | CH3                                    | CH4                                    | CH5                                    |

|-------------------|-----|-----|----------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|

| Hall rotary<br>UI |     |     | •<br>1 <sup>st</sup> plate<br>Positive | •<br>1 <sup>st</sup> plate<br>Negative | •<br>2 <sup>nd</sup> plate<br>Positive | •<br>2 <sup>nd</sup> plate<br>Negative |

#### Key:

- O Optional implementation

- Fixed use for UI

# 4.3 Hardware configuration

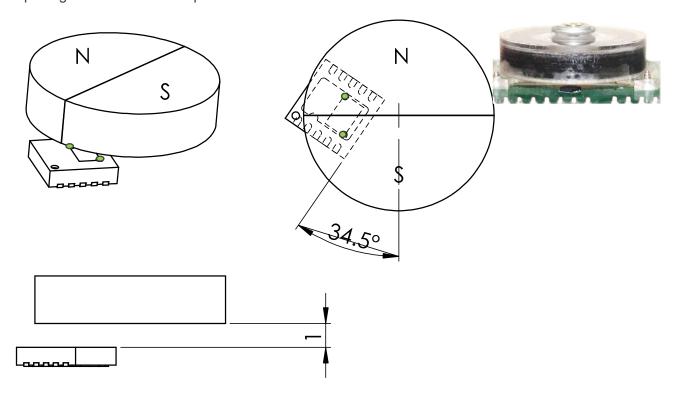

Rudimentary hardware configurations. For more detail and alternative placement options, refer to Appendix A.

# 4.4 Register configuration

For more detail on the setup of the IQS624 refer to Appendix B.

Table 4.2 Table 4-1 Hall sensing settings registers

| Address     | Name                           | Description                            | Recommended setting                                                      |

|-------------|--------------------------------|----------------------------------------|--------------------------------------------------------------------------|

| <u>0x70</u> | Hall Rotation UI<br>Settings   | Hall wheel UI settings                 | Hall UI should be enabled for degree output; enable Auto Calibration     |

| <u>0x71</u> | Hall sensor settings           | Auto ATI and charge frequency settings | Auto ATI should be enabled for temperature drift compensation            |

| 0x72,0x73   | Hall ATI Settings <sup>1</sup> | Hall channels ATI settings             | ATI Target should be more than base                                      |

| <u>0x78</u> | Hall ratio Settings            | Invert Direction setting for Hall UI   | None                                                                     |

| <u>0x79</u> | Sin(phase)<br>constant         | Sin phase calibration value            | Calculate this value using the GUI or the calculations in the Appendix A |

| <u>0x7A</u> | Cos(phase)<br>constant         | Cos phase calibration value            | Calculate this value using the GUI or the calculations in the Appendix A |

<sup>&</sup>lt;sup>1</sup> Refer to the errata and Appendix B

| <u>0x7B</u> 1     | Wheel Filter Beta     | Degree filter value                | Adjust filter value based on the amount of noise on the degree value |

|-------------------|-----------------------|------------------------------------|----------------------------------------------------------------------|

| 0x7C <sup>1</sup> | Wheel Wake<br>Preload | Wheel wakeup settings              | Use default values                                                   |

| 0x7D1             | Interval UI Divider   | Divider for filtered degree values | Depending on the application (should be equal or greater than 3)     |

| 0x7E <sup>1</sup> | Wheel Offset          | Wheel offset from zero position    | Can be used for accurate intervals                                   |

### 4.5 Example code:

Example code for an Arduino Uno can be downloaded at:

www.azoteq.com//images/stories/software/IQS62x Demo.zip

For ARM mbed resources refer to:

https://os.mbed.com/components/IQS624/

## 4.6 Sensor data output and flags

a) The Hall UI Flags (0x14) register. Bit7 is dedicated to indicating a movement of the magnet. Bit6 indicates the direction of the movement. Bit 1 is set when the movement counts are negative and bit 0 is set when the relative angle is negative. Bit 6 can be used to determine the magnet direction. Please note that these bits will be set for small movements, therefore litter may change the direction of movement bit.

|             | <u> </u>       |                    |   | Flags (0x |   |   |   |   |  |  |

|-------------|----------------|--------------------|---|-----------|---|---|---|---|--|--|

| Bit Number  | 7              | 6                  | 5 | 4         | 3 | 2 | 1 | 0 |  |  |

| Data Access |                | Read               |   |           |   |   |   |   |  |  |

| Name        | Wheel movement | Movement direction |   |           |   |   |   |   |  |  |

b) The Filtered Degree Output (0x17-0x16) 1 A 16-bit value for the filtered degrees can be read from these registers. (0-359 degrees)

|             |    |      |                                    | F     | iltere | d Deg | gree ( | Dutpu | t1 (0x | 17-0> | (16) |      |     |      |  |  |

|-------------|----|------|------------------------------------|-------|--------|-------|--------|-------|--------|-------|------|------|-----|------|--|--|

| Bit Number  | 15 | 14   | 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |       |        |       |        |       |        |       |      | 0    |     |      |  |  |

| Data Access |    | Read |                                    |       |        |       |        |       |        |       |      |      |     |      |  |  |

| Name        |    |      | Degr                               | ees l | High   | Byte  |        |       |        |       | Deg  | rees | Low | Byte |  |  |

Bit definitions:

- 0-360: Filtered absolute degree position of magnet

- c) The <u>Interval Number (0x18)</u> An 8-bit value for the current interval number can be read from this register.

<sup>&</sup>lt;sup>1</sup> Only Available on IQS62432

|             |   |                         | Interv | al Number | -1 (0x18) |   |   |   |  |  |  |

|-------------|---|-------------------------|--------|-----------|-----------|---|---|---|--|--|--|

| Bit Number  | 7 | 6                       | 5      | 4         | 3         | 2 | 1 | 0 |  |  |  |

| Data Access |   | Read/Write              |        |           |           |   |   |   |  |  |  |

| Name        |   | Current Interval Number |        |           |           |   |   |   |  |  |  |

- Bit 7-0: Current interval number

- d) The <u>Degree Output (0x81-0x80)</u>. A 16-bit value for the degrees can be read from these registers. (0-360 degrees)

|             |            |                                                                                            |  |  | De | egree | Outp | out (0: | x81-0 | x80) |  |  |  |  |  |  |

|-------------|------------|--------------------------------------------------------------------------------------------|--|--|----|-------|------|---------|-------|------|--|--|--|--|--|--|

| Bit Number  | 15         | 14     13     12     11     10     9     8     7     6     5     4     3     2     1     0 |  |  |    |       |      |         |       |      |  |  |  |  |  |  |

| Data Access | Read/Write |                                                                                            |  |  |    |       |      |         |       |      |  |  |  |  |  |  |

| Name        |            | Degrees High Byte Degrees Low Byte                                                         |  |  |    |       |      |         |       |      |  |  |  |  |  |  |

e) The <u>Relative Rotation Angle (0x8E)</u>. The delta in degrees from the previous cycle to the current cycle can be read from this register. (0-180 degrees)

|             |   |                  | Relative | Rotation A | ngle (0x8E | Ξ) |   |   |  |  |

|-------------|---|------------------|----------|------------|------------|----|---|---|--|--|

| Bit Number  | 7 | 6                | 5        | 4          | 3          | 2  | 1 | 0 |  |  |

| Data Access |   | Read/Write       |          |            |            |    |   |   |  |  |

| Name        |   | Relative degrees |          |            |            |    |   |   |  |  |

#### 4.7 IQS62432 Interval UI

The IQS62432 offers a new on-chip interval UI specifically designed for applications with discreet mechanical intervals or reduced resolution requirements.

#### 4.7.1 Interval UI Features

- > Adjustable interval size (3°-180°)

- > The wheel can be zeroed at startup

- > Adjustable wheel offset value

- > An event is generated for changes to the Interval Number Register (0x18)

## 4.7.2 Interval UI Settings Registers

|             |                             | Hall Rotation UI Settings (0x70)       |                            |                                             |                                           |                     |   |                 |  |  |

|-------------|-----------------------------|----------------------------------------|----------------------------|---------------------------------------------|-------------------------------------------|---------------------|---|-----------------|--|--|

| Bit Number  | 7                           | 6                                      | 5                          | 4                                           | 3                                         | 2                   | 1 | 0               |  |  |

| Data Access |                             |                                        | Read/Write                 |                                             |                                           |                     |   |                 |  |  |

| Name        | Hall<br>Wheel<br>UI disable | Interval<br>UI<br>disable <sup>1</sup> | Zero<br>Wheel <sup>1</sup> | Hall Wheel<br>Event<br>disable <sup>1</sup> | Interval<br>Event<br>Disable <sup>1</sup> | Auto<br>calibration | - | Wheel<br>wakeup |  |  |

| UI Setting  | 0                           | 0                                      | 0                          | 1                                           | 0                                         | 1                   | - | 0               |  |  |

#### Bit definitions:

• Bit 5: Zero Wheel angle<sup>1</sup>

o 1: Zero angle, automatically cleared by firmware

Bit 3: Interval UI Event disable<sup>1</sup>

o 0: Event UI is enabled

1: Event UI is disabled

|             |   | . Event evil e diedeled  |         |              |            |   |   |   |  |  |

|-------------|---|--------------------------|---------|--------------|------------|---|---|---|--|--|

|             |   |                          | Interva | al UI Divide | er1 (0x7D) |   |   |   |  |  |

| Bit Number  | 7 | 6                        | 5       | 4            | 3          | 2 | 1 | 0 |  |  |

| Data Access |   | Read/Write               |         |              |            |   |   |   |  |  |

| Name        |   | Interval size in degrees |         |              |            |   |   |   |  |  |

| Default     |   |                          |         | ,            | 3          |   |   |   |  |  |

#### Bit definitions:

- Bit 7-0: Interval size in degrees (>= 3° and <=180°)

- The <u>Interval Number (0x18)</u> An 8-bit value for the current interval number can be read from this register.

|             |    |                                              |    |    | W  | heel | Offse | t² (0x | 7E-0 | x7F) |   |   |   |   |   |   |

|-------------|----|----------------------------------------------|----|----|----|------|-------|--------|------|------|---|---|---|---|---|---|

| Bit Number  | 15 | 14                                           | 13 | 12 | 11 | 10   | 9     | 8      | 7    | 6    | 5 | 4 | 3 | 2 | 1 | 0 |

| Data Access |    | Read                                         |    |    |    |      |       |        |      |      |   |   |   |   |   |   |

| Name        |    | Wheel Offset High Byte Wheel Offset Low Byte |    |    |    |      |       |        |      |      |   |   |   |   |   |   |

| Default     |    | 0                                            |    |    |    |      |       |        |      |      |   |   |   |   |   |   |

Bit definitions:

<sup>&</sup>lt;sup>1</sup> Only Available on IQS62432

• 0-360: Wheel offset in degrees

#### 4.7.3 Interval UI Output Register

|             |   |   | Interv | al Number   | -1 (0x18) |           |   |   |

|-------------|---|---|--------|-------------|-----------|-----------|---|---|

| Bit Number  | 7 | 6 | 5      | 4           | 3         | 2         | 1 | 0 |

| Data Access |   |   |        | Read        | /Write    |           |   |   |

| Name        |   |   | С      | urrent Inte | rval Numb | <u>er</u> |   |   |

Bit 7-0: Current interval number

#### 4.8 IQS62432 Example

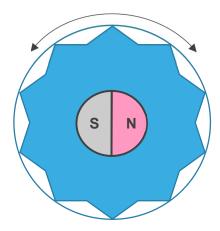

Figure 4.1 illustrates an example wheel with 10 intervals. The IQS62432 can be configured to generate an event on each interval. Configure the following registers for setup:

- 1. Disable Hall Wheel Event and Enable Interval Event in Hall Rotation Settings (0x70)

- Write 0x14 to register 0x70

- 2. Set Interval UI Divider (0x7D) to 36D ( $360^{\circ}/36^{\circ} = 10$  intervals)

- Write 0x24 to register to 0x7D

- 3. If required, the wheel can be zeroed at startup in Hall Rotation UI Settings (0x70)

- Set Bit5 in 0x70

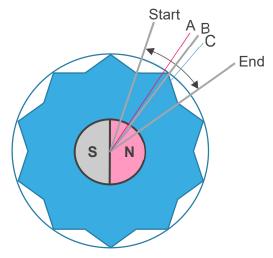

- 4. The interval register will increment every 36 degrees. If the wheel is zeroed using discrete mechanical intervals (Figure 4-1), half an interval should be added to the Wheel Zero Offset (0x7E-0x7F). With this offset, the interval register should increment when the wheel has moved half of the interval as shown by B in Figure 4.2.

- 5. Enable Event Mode in General System Settings (0xD0)

- Set Bit5 in 0xD0

- 6. The interval can be read from the Interval Number (0x18) register.

Figure 4.1 Discrete Mechanical Intervals

A 1-degree hysteresis is applied in the direction of rotation, resulting in two degrees of hysteresis at the interval change. This reduces the influence of jitter. In Figure 4.2, the interval will increase when

point C is reached and will only decrease when the wheel moves back to point A. In this example A =  $35^{\circ}$ ; B =  $36^{\circ}$ ; C =  $37^{\circ}$ .

Figure 4.2 Interval UI Hysteresis

#### 4.9 IQS62432 Wheel Wake Preload (0x7C)

This register was added to improve performance. This register is compared to the Movement counter/timer (0x8F) register. The wheel will wake up if the counter value reaches the counter threshold value before the timer reaches 0. The timer in register 0x8F will count down from the value set in the **Wheel Wake Timer Preload**. The **Counter Threshold** is the amount of degrees the wheel has to move before an event is generated for movement. The wheel movement and movement direction bits in the Hall UI Flags (0x14) register also responds to this register.

The **Wheel Wake Timer Preload** can also be set to zero. In this mode the wheel will wake up if the wheel has moved the amount of degrees specified in the **Counter Threshold**. When the wheel is awake, 31 will be loaded in the **Wheel Wake Timer Preload**.

#### 4.10 IQS62432 Event Mode Options

The IQS62432 provides three event mode options, these are:

#### 4.10.1 Touch on Wheel Wakeup enabled (Bit0, 0x70)

- > The device wakes up from the low-power modes when there is a touch on Ch0.

- > In normal power mode events are only generated when there is a touch on Ch0. Ready events will be continuously generated as long as there is a touch on Ch0. If Touch on Wheel is enabled Interval and Hall Wheel Events are ignored.

#### 4.10.2 Interval Event (Bit3, 0x70)

- > The device wakes up from low-power modes when the wheel increment or decrement the interval register.

- > Ready events are generated in normal power mode when the interval changes. If Interval Events and Hall Wheel Events (below) are enabled the IC will respond to Hall Wheel Events.

#### 4.10.3 Hall Wheel Event (Bit4, 0x70)

> The device wakes up based on the conditions described in Section 4.7. The wheel will wake up if the counter value reaches the counter threshold value before the timer reaches 0.

> Events are generated on the same condition when the device is in low power mode. If Hall Wheel Events and Interval Events are enabled the IC will respond to Hall Wheel Events.

The device can also be set to **Stream in Normal Power (Bit5, 0xD9).** With this bit set the device will wake up from either of the selected modes above. Events will be generated based on the Normal Power Report Rate during Normal Power mode. The device will stop streaming when low-power mode is entered.

Table 4.3: Hall Rotation UI Settings

|                       | Hall Rotation UI Settings (0x70) |

|-----------------------|----------------------------------|

| Touch on Wheel Wakeup | 0x1D                             |

| Interval Event        | 0x14                             |

| Hall Wheel Event      | 0x0C                             |

If all these modes are disabled, there will be no events generated for wheel movements.

## 5 Device clock, power management and mode operation

#### 5.1 Device main oscillator

The IQS624 has a **16MHz** main oscillator (default enabled) to clock all system functionality.

An option exists to reduce the main oscillator to 8MHz. This will result in charge transfers to be slower by half of the default implementations.

To set this option:

- > As a software setting Set the General System Settings (0xD0): bit4 = 1, via an I<sup>2</sup>C command.

- > As a permanent setting Set the OTP option in FG Bank 0: bit2 = 1, using Azoteq USBProg program.

The ProxFusion<sup>®</sup> channels charges at half of the main oscillator frequency. Therefore the frequency multiplier selected in <u>Ch0&1 ProxFusion Settings 1 (0x42; bit 4-5)</u> and <u>Hall sensor settings (0x71; bit 4-5)</u> is multiplied by half of the main oscillator frequency.

#### 5.2 Device modes

The IQS624 supports the following modes of operation;

- > Normal mode (Fixed report rate)

- > **Low Power mode** (Reduced report rate, no UI execution)

- > **Ultra-Low Power mode** (Only channel 0 is sensed for a prox)

- > Halt Mode (Suspended/disabled)

- > Note: Auto modes must be disabled to enter or exit halt mode.

The device will automatically switch between the different operating modes by default. However, this Auto mode feature may be disabled by setting the Disable Auto Modes bit (<u>Power Mode Settings 0xD2</u>; bit 5) to confine device operation to a specific power mode. The Power Mode bits (<u>Power Mode Settings 0xD2</u>; bit 3-4) can then be used to specify the desired mode of operation.

#### 5.2.1 Normal mode

Normal mode is the fully active sensing mode to function at a fixed report rate specified in the Normal Mode report rate (0xD3) register. This 8-bit value is adjustable from 0ms – 255ms in intervals of 1ms.

#### 5.2.2 Low power mode

Low power mode is a reduced sensing mode where all channels are sensed but no UI code are executed. The sample rate can be specified in the <u>Low Power Mode report rate (0xD4)</u> register. The 8-bit value is adjustable from 0ms-255ms in intervals of 1ms. Reduced report rates also reduce the current consumed by the sensor.

#### 5.2.3 Ultra-low power mode

Ultra-low power mode is a reduced sensing mode where only channel 0 is sensed and no other channels or UI code are executed. Set the Enable ULP Mode bit (<u>Power Mode Settings 0xD2; bit 6</u>) to enable use of the ultra-low power mode. The sample rate can be specified in the <u>Low Power Mode report rate (0xD5)</u> register. The 8-bit value is adjustable from 0ms – 4sec in intervals of 16ms.

When in Ultra-low power mode the IQS624 can be configured to update all channels at a specific rate defined in <a href="Power Mode Settings">Power Mode Settings</a> (0xD2) register. A flag will be set in the <a href="System flags">System flags</a> (0x10; bit 0) register when a normal power update is performed. Wake up will occur on proximity detection on channel 0. Ultra-low power mode will not function properly if channel 0 is not enabled.

#### 5.2.4 Halt mode

Halt mode will suspend all sensing and will place the device in a dormant or sleep state. The device requires an I<sup>2</sup>C command from a master to explicitly change the power mode out of the halt state before any sensor functionality can continue.

### 5.2.5 Mode time

The mode time is specified in the <u>Auto Mode Timer (0xD6)</u> register. The 8-bit value is adjustable from 0ms – 2 min in intervals of 500ms.

#### 5.2.6 Streaming and event mode:

Streaming mode is the default. Event mode is enabled by setting bit 5 in the <u>General System</u>

<u>Settings (0xD0)</u> register.

## Streaming mode

The ready is triggered every cycle and per the report rate.

#### **Event mode**

The ready is triggered only when an event has occurred.

The events which trigger the ready can be configured to:

- > Hall wheel movement (If the hall UI is enabled)

- > Touch or proximity events on channel 0 or 1

- Interval Event1

Note: Both these events have built in hysteresis which filters out very slow changes.

<sup>&</sup>lt;sup>1</sup> Only available on IQS62432

## 6 Report rates

## 6.1 Normal Power Maximum Report rate

Note: Assuming normal mode report rate set to 0 (maximum speed) and Auto Power Modes turned off

| Hall UI<br>State | Channels             | Register Address                        | Bytes | Functionality <sup>1</sup>                                        | Report Rate <sup>2</sup> |

|------------------|----------------------|-----------------------------------------|-------|-------------------------------------------------------------------|--------------------------|

| On               | 2 x Prox<br>4 x Hall | 0x02 (PXS Flags)<br>0x80-0x81 (Degrees) | 3     | On-chip calculation of rotation angle and prox channels.          | 4.87 ms                  |

| On               | 4 x Hall             | 0x80-0x81 (Degrees)                     | 2     | On-chip calculation of rotation angle.                            | 3.29 ms                  |

| Off              | 2 x Prox<br>4 x Hall | 0x02 (PXS Flags)<br>0x24-0x2B (Counts)  | 9     | Off-chip calculation of rotation angle and on-chip prox channels. | 3.93 ms                  |

| Off              | 4 x Hall             | 0x24-0x2B (Counts)                      | 8     | Off-chip calculation of rotation angle.                           | 2.94 ms                  |

| Off              | 1 x Hall<br>2 x Prox | 0x24 (CH2 Counts)<br>0x02 (PXS Flags)   | 3     | Off-chip RPM-calculation and 2 Prox channels on-chip              | 2.25 ms                  |

| Off              | 1 x Hall<br>1 x Prox | 0x24 (CH2 Counts)<br>0x02 (PXS Flags)   | 3     | Off-chip RPM-calculation and 1 Prox channels on-<br>chip          | 1.63 ms                  |

| Off              | 1 x Hall             | 0x24 (CH2 Counts)                       | 2     | Off-chip RPM-calculation                                          | 0.82 ms                  |

<sup>-</sup> Report rates are not necessarily an accurate indication of maximum observable rotation rate. On-chip calculations are only accurate at low rotation rates.

- (1) Contact Azoteq for further information on functionality.

- (2) These values were calculated by design and not by testing.

#### 7 System reset

The IQS624 device monitor's system resets and events.

- a) Every device power-on and reset event will set the Show Reset bit in the <a href="System Flags (0x10: bit 7">System Flags (0x10: bit 7">System Flags (0x10: bit 7")</a>) register and the master should explicitly clear this bit by setting the Ack Reset bit in the General System Settings (0xD0; bit 6) register.

- b) The system events will also be indicated with the Event bit in the <u>System Flags (0x10; bit 1)</u> register if any system event occur such as a reset. This event will continuously trigger until the reset has been acknowledged.

#### 8 Communication

The **IQS624** device interfaces to a master controller via a 3-wire (SDA, SCL and RDY) serial interface bus that is I<sup>2</sup>C<sup>TM</sup> compatible with a maximum communication speed of 400 kHz. The communications interface of the IQS624 supports the following:

- > Streaming data as well as event mode.

- > The master may address the device at any time. If the IQS624 is not in a communication window, the device returns an ACK after which clock stretching is induced until a communication window is entered. Additional communication checks are included in the main loop in order to reduce the average clock stretching time.

- > The provided interrupt line (RDY) is push-pull active low on IQS624-3001 and open-drain active low on IQS62432. The RDY indicates a communication window.

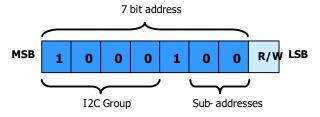

#### 8.1 Control Byte

The Control byte indicates the 7-bit device address (44H default) and the Read/Write indicator bit. The structure of the control byte is shown in Figure 8.1.

Figure 8.1 IQS624 Control Byte

The I<sup>2</sup>C device has a 7 bit Slave Address (default 0x44H) in the control byte. To confirm the address, the software compares the received address with the device address. Sub-address values can be set by OTP programming options.

#### 8.2 I2C Read

To read from the device a *current address read* can be performed. This assumes that the address-command is already setup as desired.

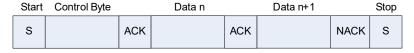

#### Current Address Read

Figure 8.2 Current Address Read

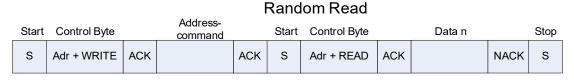

If the address-command must first be specified, then a *random read* must be performed. In this case a WRITE is initially performed to setup the address-command, and then a repeated start is used to initiate the READ section.

Figure 8.3 Random Read

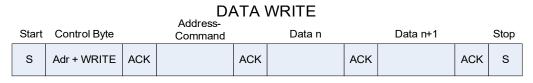

#### 8.3 I2C Write

To write settings to the device a *Data Write* is performed. Here the Address-Command is always required, followed by the relevant data bytes to write to the device.

Figure 8.4 I<sup>2</sup>C Write

#### 8.4 End of Communication Session / Window

Similar to other Azoteq I<sup>2</sup>C devices, to end the I<sup>2</sup>C communication session, a STOP command is given. When sending numerous read and write commands in one communication cycle, a repeated start command must be used to stack them together (since a STOP will jump out of the communication window, which is not desired).

The STOP will then end the communication, and the **IQS624** will return to process a new set of data. Once this is obtained, the communication window will again become available (RDY set LOW).

#### 8.5 Stop-bit disable option(IQS62432)

The IQS62432 part offer:

- an additional <a href="Pieces">PC settings</a> register (0xD9) specifically added for stop-bit disable functionality,

- as well as a <u>RDY timeout period</u> register (0xD8) in order to set the required timeout period for termination of any communication windows (RDY = Low) if no I<sup>2</sup>C activity is present on SDA and SCL pins.

Customers using an MCU with a binary serial-encoder peripheral which is not fully I²C compatible (but provide some crude serial communication functions) can use this option to configure the IQS62432 so that any auto generated stop command from the serial peripheral can be ignored by the IQS62432 I²C hardware. This will restrict the IQS62432 from immediately exiting a communication window during event mode (reduced communication only for events) until all required communication has been completed and a stop command can correctly be transmitted. Please refer to the figures below for serial data transmission examples.

#### Please note:

- 1. Stop-bit disable and enable must be performed at the beginning and end of a communication window. The first and last I<sup>2</sup>C register to be written to ensure no unwanted communication window termination.

- Leaving the Stop-bit disabled will result in successful reading of registers but will not execute

any commands written over I2C in a communication window being terminated after a RDY

timeout and with no IQS recognised stop command.

- 3. The default RDY timeout period for IQS62432 is purposefully long (10.24ms) for slow responding MCU hardware architectures. Please set this register according to your requirements/preference.

- 4. These options are only available on IQS62432 parts and not for IQS6243(1).

#### **Stop-bit Disable**

| Communication window open | Start | Control byte |     | Address-<br>Command |     | Disable stop-bit |     | Ignored<br>stop | Continue with reads / writes |

|---------------------------|-------|--------------|-----|---------------------|-----|------------------|-----|-----------------|------------------------------|

| RDY = ↓LOW                | S     | Addr + WRITE | ACK | 0xD9                | ACK | 0x81             | ACK | S               |                              |

Figure 8.5 I<sup>2</sup>C Stop-bit Disable

#### **Stop-bit Enable**

| Reads / Writes<br>Finished | Start | Control byte |     | Address-<br>Command |     | Enable<br>stop-bit |     | Stop | Communication window closed |

|----------------------------|-------|--------------|-----|---------------------|-----|--------------------|-----|------|-----------------------------|

|                            | S     | Addr + WRITE | ACK | 0xD9                | ACK | 0x01               | ACK | S    | RDY = ↑HIGH                 |

Figure 8.6 I<sup>2</sup>C Stop-bit Enable

#### 8.6 Device address and sub-addresses

The default device address is **0x44 = DEFAULT\_ADDR**.

Alternative sub-address options are definable in the following one-time programmable bits: OTP Bank0 (bit3; 0; bit1; bit0) = SUB\_ADDR\_0 to SUB\_ADDR\_7

| a) | Default address: | 0x44 = DEFAULT_ADDR OR SUB_ADDR_0 |

|----|------------------|-----------------------------------|

| b) | Sub-address:     | 0x45 = DEFAULT_ADDR OR SUB_ADDR_1 |

| c) | Sub-address:     | 0x46 = DEFAULT_ADDR OR SUB_ADDR_2 |

| d) | Sub-address:     | 0x47 = DEFAULT_ADDR OR SUB_ADDR_3 |

| e) | Sub-address:     | 0x4C = DEFAULT_ADDR OR SUB_ADDR_4 |

| f) | Sub-address:     | 0x4D = DEFAULT_ADDR OR SUB_ADDR_5 |

| g) | Sub-address:     | 0x4E = DEFAULT_ADDR OR SUB_ADDR_6 |

| h) | Sub-address:     | 0x4F = DEFAULT_ADDR OR SUB_ADDR_7 |

### 8.7 Additional OTP options

All one-time-programmable device options are located in FG bank 0.

|            | Floating Gate Bank0 |           |   |   |                  |      |                 |   |  |  |  |  |  |

|------------|---------------------|-----------|---|---|------------------|------|-----------------|---|--|--|--|--|--|

| Bit Number | 7                   | 6         | 5 | 4 | 3                | 2    | 1               | 0 |  |  |  |  |  |

| Name       | -                   | Comms ATI | - | - | Sub address<br>2 | 8MHz | Sub address 0-1 |   |  |  |  |  |  |

| Default    | -                   | 0         | - | 0 | 0                | 0    | 0               | 0 |  |  |  |  |  |

#### Bit definitions:

- Bit 6: Comms mode during ATI

- o 0: No streaming events are generated during ATI

- o 1: Comms continue as setup regardless of ATI state.

- Bit 2: Main Clock frequency selection

- o 0: Run FOSC at 16MHz

- 1: Run FOSC at 8MHz

- Bit 0,1,3: I2C sub-address

- I2C address = 0x44

All calibration data are located in FG bank 3 for the latest IQS6243(1) and all IQS62432 IC's.

|            | Floating Gate Bank3 |   |  |  |                             |  |  |  |  |  |  |

|------------|---------------------|---|--|--|-----------------------------|--|--|--|--|--|--|

| Bit Number | 7 6 5 4 3 2 1 0     |   |  |  |                             |  |  |  |  |  |  |

| Name       |                     | - |  |  | Hall Plate Calibration Data |  |  |  |  |  |  |

| Default    |                     | - |  |  | 15-1                        |  |  |  |  |  |  |

#### Bit definitions:

- Bit 3-0: Hall Plate Calibration Data

- o 15-1: The calibration bin of the IC

- o 0: The IC is not calibrated (Before June 2018)

#### Please refer to

Appendix B: Magnet calibration for information regarding hall plate calibration.

#### 8.8 Request Communication Window

The master or host MCU has the capability to request a communication window at any time, by writing the device address to the IQS624. The communication window will open directly following the current conversion cycle.

## 8.9 I<sup>2</sup>C Specific Commands

#### 8.9.1 Show Reset

After start-up, and after every reset event, the "Show Reset" flag will be set in the <u>System Flags</u> register (0x10H; bit 7).

The "Show Reset" bit can be read to determine whether a reset has occurred on the device (it is recommended to be continuously monitored). This bit will be set '1' after a reset.

The "Show Reset" flag will be cleared (set to '0') by writing a '1' into the "Ack reset" bit in the <u>General system settings register (0xD0; bit 6)</u>. A reset will typically take place if a timeout during communication occurs.

### 8.9.2 I2C Timeout

If no communication is initiated from the master/host MCU within the first  $t_{COMMS}$  ( $t_{COMMS}$  = 2.038 ms default) of the RDY line indicating that data is available (i.e. RDY = low), the device will resume with the next cycle of charge transfers and the data from the previous conversions will be lost. The RDY timeout period register (0xD8) can be adjusted on IQS62432. There is also a timeout ( $t_{I2C}$ ) that cannot be disabled, for when communication has started but not been completed, for example when the bus is being held by another device ( $t_{I2C}$  = 33 ms).

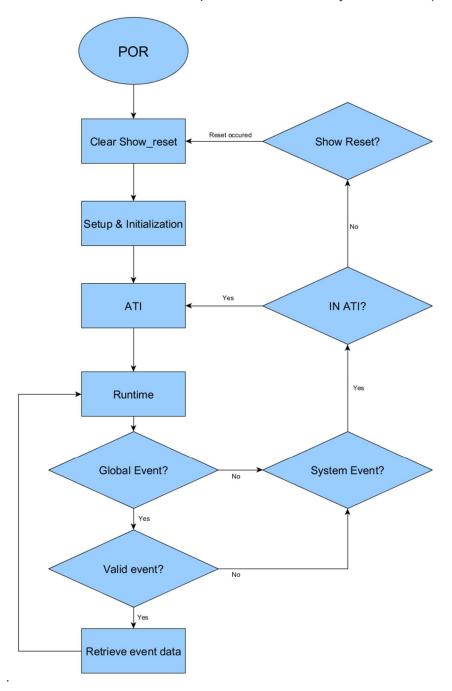

## 8.10 Recommended communication and runtime flow diagram

The following is a basic master program flow diagram to communicate and handle the device. It addresses possible device events such as output events, ATI and system events (resets).

Figure 8.7 Figure 8-1 Master command structure and runtime event handling flow diagram

It is recommended that the master verifies the status of the <u>System Flags (0x10)</u> bits to identify events and resets. Detecting either one of these should prompt the master to the next steps of handling the IQS624.

Streaming mode communication is used for detail sensor evaluation during prototyping and/or development phases. Event mode communication is recommended for runtime use of the IQS624.

# 9 IQS624 Memory map

Table 9.1 IQS624 Register map

| Register Address | <u>Group</u>              | Register Name                      |

|------------------|---------------------------|------------------------------------|

| 0x00             |                           | Product Number                     |

| 0x01             | <u>Device Information</u> | Software Number                    |

| 0x02             |                           | Hardware Number                    |

| 0x10             |                           | System Flags                       |

| 0x12             |                           | Proximity/Touch UI Flags           |

| 0x14             |                           | HALL UI Flags                      |

| 0x15             | Device Specific Data      | Hall Ratio Flags                   |

| 0x16 (IQS62432)  | <u>Data</u>               | Filtered Degree Output (Low byte)  |

| 0x17 (IQS62432)  |                           | Filtered Degree Output (High byte) |

| 0x18 (IQS62432)  |                           | Interval Number Output             |

| 0x20             |                           | CH0 CS Low                         |

| 0x21             |                           | CH0 CS High                        |

| 0x22             |                           | CH1 CS Low                         |

| 0x23             |                           | CH1 CS High                        |

| 0x24             |                           | CH2 CS Low                         |

| 0x25             |                           | CH2 CS High                        |

| 0x26             |                           | CH3 CS Low                         |

| 0x27             | Count Data                | CH3 CS High                        |

| 0x28             | Count Data                | CH4 CS Low                         |

| 0x29             |                           | CH4 CS High                        |

| 0x2A             |                           | CH5 CS Low                         |

| 0x2B             |                           | CH5 CS High                        |

| 0x30             |                           | CH0 LTA Low                        |

| 0x31             |                           | CH0 LTA High                       |

| 0x32             |                           | CH1 LTA Low                        |

| 0x33             |                           | CH1 LTA High                       |

| 0x40             |                           | Ch0 ProxFusion Settings 0          |

| 0x41             |                           | Ch1 ProxFusion Settings 0          |

| 0x42             |                           | Ch0&1 ProxFusion Settings 1        |

| 0x43             | ProxFusion                | Ch0 ProxFusion Settings 2          |

| 0x44             | sensor settings           | Ch1 ProxFusion Settings 2          |

| 0x45             |                           | Ch0&1 ProxFusion Settings 3        |

| 0x46             |                           | Ch0 Compensation                   |

| 0x47             |                           | Ch1 Compensation                   |

| 0x48             | ProxFusion                | Ch0 Multipliers                    |

| 0x49             | sensor settings           | Ch1 Multipliers                    |

| 0x50             |                           | Ch0 Proximity threshold            |

| 0x51             |                           | Ch0 Touch threshold                |

| 0x52             | Touch / Proximity         | Ch1 Proximity threshold            |

| 0x53             | <u>UI settings</u>        | Ch1 Touch threshold                |

| 0x54             |                           | UI Halt period                     |

| 0x70             |                           | Hall Rotation UI Settings          |

| 0x71            |                   | Hall Sensor Settings                              |  |  |  |  |  |  |

|-----------------|-------------------|---------------------------------------------------|--|--|--|--|--|--|

| 0x72            |                   | Ch2&3 Hall ATI Settings                           |  |  |  |  |  |  |

| 0x73            |                   | Ch4&5 Hall ATI Settings                           |  |  |  |  |  |  |

| 0x74            |                   | Ch2&3 Compensation                                |  |  |  |  |  |  |

| 0x75            |                   | Ch4&5 Compensation                                |  |  |  |  |  |  |

| 0x76            |                   | Ch2&3 Multipliers                                 |  |  |  |  |  |  |

| 0x77            |                   | Ch4&5 Multipliers                                 |  |  |  |  |  |  |

| 0x78            | HALL Sensor       | Hall Ratio Settings                               |  |  |  |  |  |  |

| 0x79            | <u>Settings</u>   | Sin Constant                                      |  |  |  |  |  |  |

| 0x7A            |                   | Cos Constant                                      |  |  |  |  |  |  |

| 0x7B (IQS62432) |                   | Wheel Filter Beta                                 |  |  |  |  |  |  |

| 0x7C (IQS62432) |                   | Wheel Wake Preload                                |  |  |  |  |  |  |

| 0x7D (IQS62432) |                   | Interval UI Divider                               |  |  |  |  |  |  |

| 0x7E (IQS62432) |                   | Wheel Offset (Low byte)                           |  |  |  |  |  |  |

| 0x7F (IQS62432) |                   | Wheel Offset (High byte)                          |  |  |  |  |  |  |

| 0x80            |                   | Degree Output (Low byte)                          |  |  |  |  |  |  |

| 0x81            |                   | Degree Output (High byte)                         |  |  |  |  |  |  |

| 0x82            |                   | Ratio Output (Low byte)  Ratio Output (High byte) |  |  |  |  |  |  |

| 0x83            |                   |                                                   |  |  |  |  |  |  |

| 0x84            |                   | Numerator of Ratio (Low byte)                     |  |  |  |  |  |  |

| 0x85            |                   | Numerator of Ratio (High byte)                    |  |  |  |  |  |  |

| 0x86            | HALL Wheel Output | Denominator of Ratio (Low byte)                   |  |  |  |  |  |  |

| 0x87            | <u>Output</u>     | Denominator of Ratio (High byte)                  |  |  |  |  |  |  |

| 0x88            |                   | Rotation Correction factor (Low byte)             |  |  |  |  |  |  |

| 0x89            |                   | Rotation Correction factor (High byte)            |  |  |  |  |  |  |

| A8x0            |                   | Max Numerator of Ratio (Low byte)                 |  |  |  |  |  |  |

| 0x8B            |                   | Max Numerator of Ratio (High byte)                |  |  |  |  |  |  |

| 0x8C            |                   | Max Denominator of Ratio (Low byte)               |  |  |  |  |  |  |

| 0x8D            | 11011 10//1       | Max Denominator of Ratio (High byte)              |  |  |  |  |  |  |

| 0x8E            | HALL Wheel Output | Relative Rotation Angle                           |  |  |  |  |  |  |

| 0x8F            | <u>Output</u>     | Movement counter/timer                            |  |  |  |  |  |  |

| 0xD0            |                   | General System Settings                           |  |  |  |  |  |  |

| 0xD1            |                   | Active Channels                                   |  |  |  |  |  |  |

| 0xD2            |                   | Power Mode Settings                               |  |  |  |  |  |  |

| 0xD3            | Device and Power  | Normal mode report rate                           |  |  |  |  |  |  |

| 0xD4            | <u>mode</u>       | <u>Low power mode report rate</u>                 |  |  |  |  |  |  |

| 0xD5            | <u>Settings</u>   | <u>Ultra-low power mode report rate</u>           |  |  |  |  |  |  |

| 0xD6            |                   | Auto Mode time                                    |  |  |  |  |  |  |

| 0xD8 (IQS62432) |                   | RDY Timeout Period                                |  |  |  |  |  |  |

| 0xD9 (IQS62432) |                   | I2C Settings                                      |  |  |  |  |  |  |

#### 9.2 Device Information

#### 9.2.1 Product Number

|                                            | Product Number (0x00) |      |   |            |           |    |  |  |  |  |

|--------------------------------------------|-----------------------|------|---|------------|-----------|----|--|--|--|--|

| Bit Number   7   6   5   4   3   2   1   0 |                       |      |   |            |           |    |  |  |  |  |

| Data Access                                |                       | Read |   |            |           |    |  |  |  |  |

| Name                                       |                       |      | D | evice Prod | luct Numb | er |  |  |  |  |

#### Bit definitions:

• Bit 7-0: Device Product Number = D'67'

#### 9.2.2 Software Number

|             | Software Number (0x01) |                        |   |   |   |   |   |   |  |  |

|-------------|------------------------|------------------------|---|---|---|---|---|---|--|--|

| Bit Number  | 7                      | 6                      | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

| Data Access |                        | Read                   |   |   |   |   |   |   |  |  |

| Name        |                        | Device Software Number |   |   |   |   |   |   |  |  |

#### Bit definitions:

- Bit 7-0: IQS62431zz Device Software Number = D'02'

- Bit 7-0: IQS62432zz Device Software Number = D'14' (Backwards compatible)

- Bit 7-0: IQS62451zz Device Software Number = D'02'

#### 9.2.3 Hardware Number

|             | Hardware Number (0x02)                                                                     |                        |  |  |  |  |  |  |  |  |

|-------------|--------------------------------------------------------------------------------------------|------------------------|--|--|--|--|--|--|--|--|

| Bit Number  | Bit Number         7         6         5         4         3         2         1         0 |                        |  |  |  |  |  |  |  |  |

| Data Access |                                                                                            | Read                   |  |  |  |  |  |  |  |  |

| Name        |                                                                                            | Device Hardware Number |  |  |  |  |  |  |  |  |

#### Bit definitions:

- Bit 7-0: IQS62431zz Device Hardware Number = D'130'

- Bit 7-0: IQS62432zz Device Hardware Number = D'130'

- Bit 7-0: IQS62432zz Device Hardware Number = D'146'

- Bit 7-0: IQS62451zz Device Hardware Number = D'162'

## 9.3 Device Specific Data

#### 9.3.1 System Flags

|             | System flags (0x10) |                 |  |                                        |  |             |              |                         |  |  |  |  |  |

|-------------|---------------------|-----------------|--|----------------------------------------|--|-------------|--------------|-------------------------|--|--|--|--|--|

| Bit Number  | 7                   | 7 6 5 4 3 2 1 0 |  |                                        |  |             |              |                         |  |  |  |  |  |

| Data Access |                     | Read            |  |                                        |  |             |              |                         |  |  |  |  |  |

| Name        | Show<br>Reset       |                 |  | <u>Current</u><br><u>power</u><br>mode |  | ATI<br>Busy | <u>Event</u> | NP<br>Segment<br>Active |  |  |  |  |  |

#### Bit definitions:

- Bit 7: Reset Indicator:

- o 0: No reset event

- o 1: A device reset has occurred and needs to be acknowledged

- Bit 4-3: Current power mode indicator:

- o 00: Normal power mode

- o 01: Low power mode

- o 10: Ultra-Low power mode

- o 11: Halt power mode

- Bit 2: ATI Busy Indicator:

- o 0: No channels are in ATI

- 1: One or more channels are in ATI

- Bit 1: Global Event Indicator:

- o 0: No new event to service

- 1: An event has occurred and should be handled

- Bit 0: Normal Power segment indicator:

- o 0: Not performing a normal power update

- 1: Busy performing a normal power update

#### 9.3.2 Proximity/Touch UI Flags

|             | Proximity/Touch UI Flags (0x12) |      |                        |                        |   |   |                            |                            |  |  |  |  |  |  |

|-------------|---------------------------------|------|------------------------|------------------------|---|---|----------------------------|----------------------------|--|--|--|--|--|--|

| Bit Number  | 7                               | 6    | 5                      | 4                      | 3 | 2 | 1                          | 0                          |  |  |  |  |  |  |

| Data Access |                                 | Read |                        |                        |   |   |                            |                            |  |  |  |  |  |  |

| Name        |                                 |      | Chan 1<br>Touch<br>out | Chan 0<br>touch<br>out |   |   | Chan 1<br>proximity<br>out | Chan 0<br>proximity<br>out |  |  |  |  |  |  |

#### Bit definitions:

- Bit 5: Channel 1 touch indicator:

- o 0: Channel 1 delta below touch threshold

- 1: Channel 1 delta above touch threshold

- Bit 4: Channel 0 touch indicator:

- 0: Channel 0 delta below touch threshold

- 1: Channel 0 delta above touch threshold

- Bit 1: Channel 1 Proximity indicator:

- o 0: Channel 1 delta below proximity threshold

- 1: Channel 1 delta above proximity threshold

- Bit 0: Channel 0 Proximity indicator:

- o 0: Channel 0 delta below proximity threshold

- o 1: Channel 0 delta above proximity threshold

## 9.3.3 Hall UI Flags

|             | Hall UI Flags (0x14) |                    |   |   |   |   |   |   |  |  |  |  |  |  |

|-------------|----------------------|--------------------|---|---|---|---|---|---|--|--|--|--|--|--|

| Bit Number  | 7                    | 6                  | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |  |  |

| Data Access |                      | Read               |   |   |   |   |   |   |  |  |  |  |  |  |

| Name        | Wheel movement       | Movement direction |   |   |   |   |   |   |  |  |  |  |  |  |

#### Bit definitions:

- Bit 7: Wheel movement indicator:

- 0: No wheel movement detected

- o 1: Wheel movement detected

- Bit 6: Movement direction indicator:

- o 0: If movement is detected it is in positive direction

- o 1: If movement is detected it is in negative direction

- > Please note that these bits will be set for small movements, therefore jitter may change the direction of movement bit.

### 9.3.4 Hall Ratio Flags

|             |   |      | Hal | I Ratio F | lags (0x1 | 15)     |             |           |  |  |  |  |

|-------------|---|------|-----|-----------|-----------|---------|-------------|-----------|--|--|--|--|

| Bit Number  | 7 | 6    | 5   | 4         | 3         | 2       | 1           | 0         |  |  |  |  |

| Data Access |   | Read |     |           |           |         |             |           |  |  |  |  |

|             |   |      |     |           |           | Move    | Max         | Max       |  |  |  |  |

| Name        |   |      |     |           |           | counter | Denominator | Numerator |  |  |  |  |

|             |   |      |     |           |           | full    | set         | set       |  |  |  |  |

#### Bit definitions:

- Bit 2: Move counter full indicator:

- o 0: Movement counter is not full

- o 1: Movement counter is full

- Bit 1: Max Denominator set indicator:

- o 0: Max denominator has not changed

- 1: Max denominator has changed (used for auto calibration)

- Bit 0: Max Numerator set indicator:

- o 0: Max Numerator has not changed

- 1: Max Numerator has changed (used for auto calibration)

### 9.3.5 Filtered Degree Output1

|             | Filtered Degree Output (0x17-0x16) |                                    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|-------------|------------------------------------|------------------------------------|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Bit Number  | 15                                 | 14                                 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Data Access |                                    | Read                               |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Name        |                                    | Degrees High Byte Degrees Low Byte |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

#### Bit definitions:

• 0-360: Filtered absolute degree position of magnet

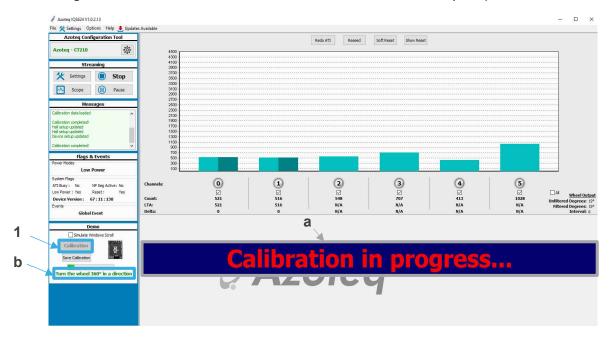

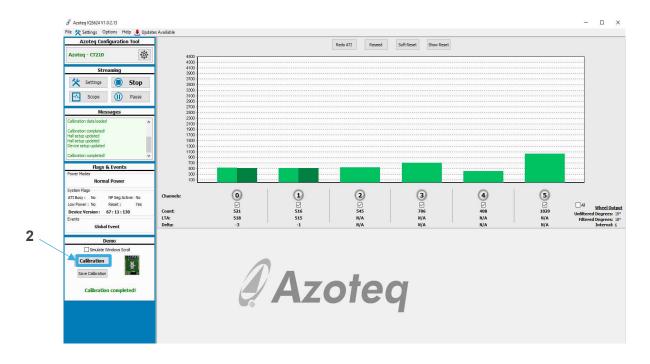

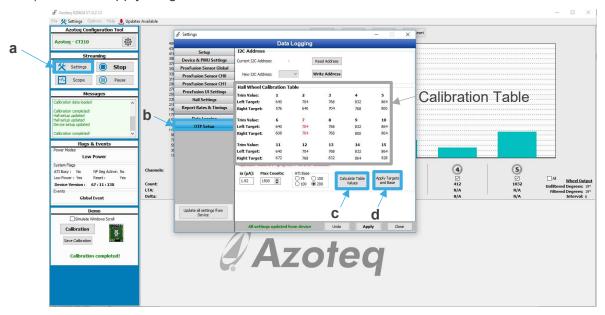

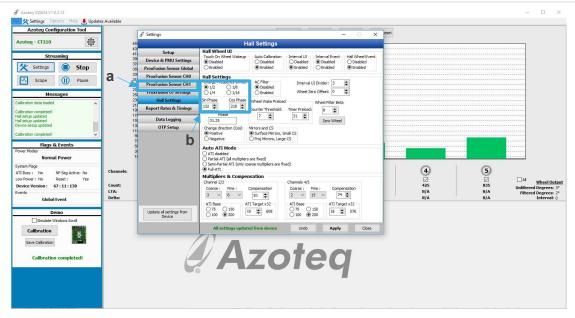

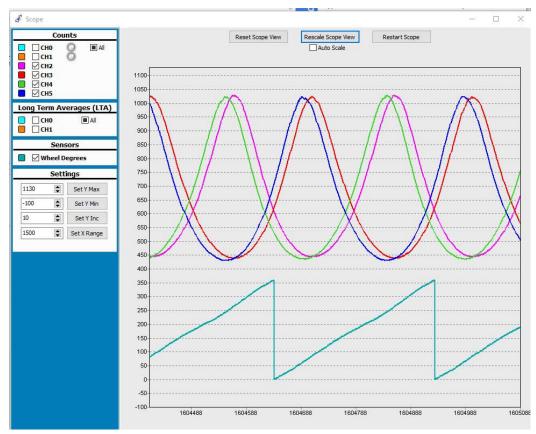

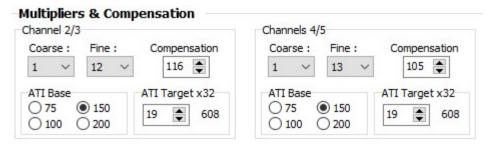

<sup>&</sup>lt;sup>1</sup> Only available on IQS62432