PWM Doubler/Quad Logic

# IR3599/IR3599A

# FEATURES

- 3.3V supply voltage

- Configurable phase multiplier as either doubler or quad from a single PWM input

- Capable of generating high output switching frequencies from 200k-800kHz

- Tri-state PWM input and outputs for power stage shutdown

- IR3599A is configured to accept IR's patented Active Tri-Level (ATL) PWM signals while IR3599 accepts industry's standard tri-state PWM signals

- VCC Power-on-reset

- Dual Flat No-Lead (DFN) Package

- Lead free RoHS compliant package

## **APPLICATIONS**

- Servers and Desktop Computers

- High Phase Count and Phase Shedding

Applications

- High Frequency and High Efficiency VRM

# DESCRIPTION

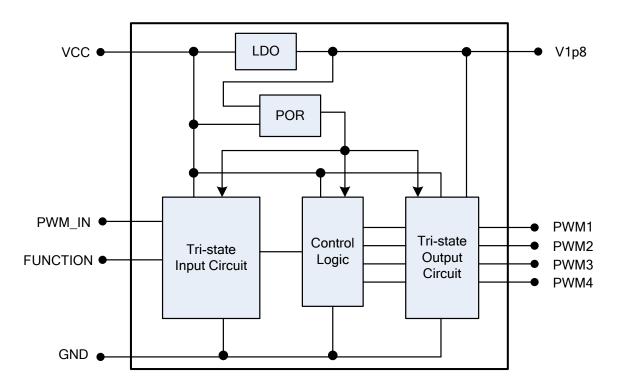

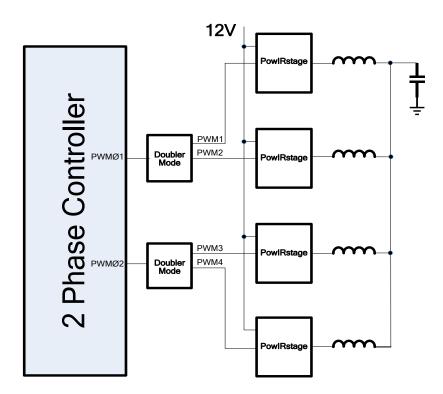

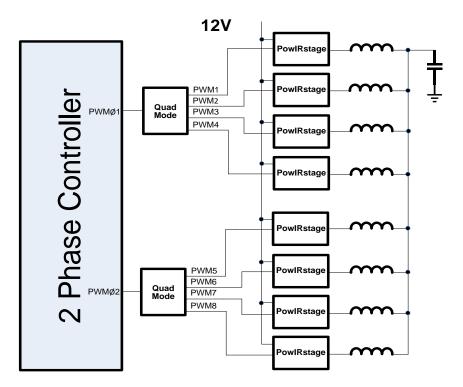

IR3599/IR3599A is a phase multiplier which is designed to double or quadruple the effective maximum phase count from the controller, enabling a well-controlled, high phase count voltage regulator.

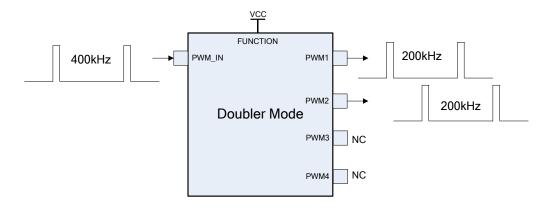

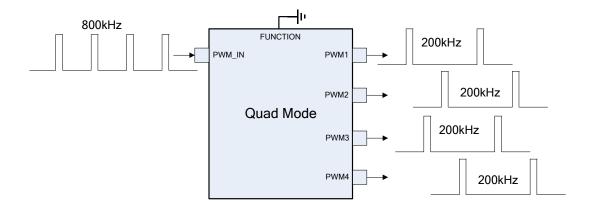

Each IR3599/IR3599A is able to drive up to four independent power stages from one PWM input. The IR3599/IR3599A can be configured as DOUBLER logic where one PWM signal is internally split to drive the two power stages 180° out of phase, each at half of the PWM input frequency. The IR3599/IR3599A can also be configured as QUAD logic where one PWM signal is internally split at 0°, 90°, 180°, and 270° respectively, and each at 1/4 of the PWM input frequency.

IR3599A features the patented IR Active Tri-Level (ATL) PWM input and output, designed to work with IR digital multi-phase controller and IR PowIRstage. The unique doubler/quad mode ATL tri-state timing allows the VR to transition into tri-state faster during load releases. IR3599 features industry's standard tri-state PWM input and output interfaces, designed to work with general multi-phase controllers, drivers or power stages.

IR3599/IR3599A also incorporates a power-on reset feature, which ensures the device is active only after the supply voltage exceeds a certain minimum operating threshold.

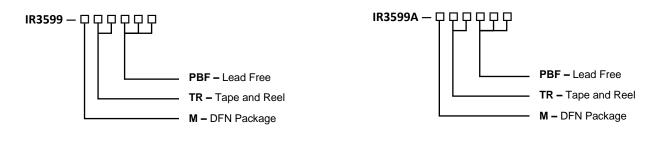

## **ORDERING INFORMATION**

| Base Part | Deekene Ture    | Standard Pack |          | Orderable     |  |

|-----------|-----------------|---------------|----------|---------------|--|

| Number    | Package Type    | Form          | Quantity | Part Number   |  |

| IR3599    | DFN 2 mm x 2 mm | Tape and Reel | 3000     | IR3599MTRPBF  |  |

| IR3599A   | DFN 2 mm x 2 mm | Tape and Reel | 3000     | IR3599AMTRPBF |  |

| IR3599    | DFN 2 mm x 2 mm | Tape and Reel | 100      | IR3599MTRPBF  |  |

| IR3599A   | DFN 2 mm x 2 mm | Tape and Reel | 100      | IR3599AMTRPBF |  |

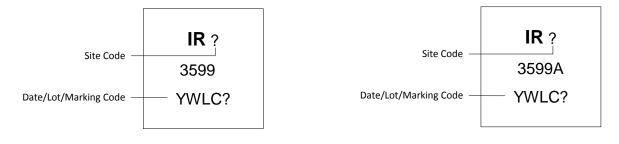

## **ORDERING INFORMATION**

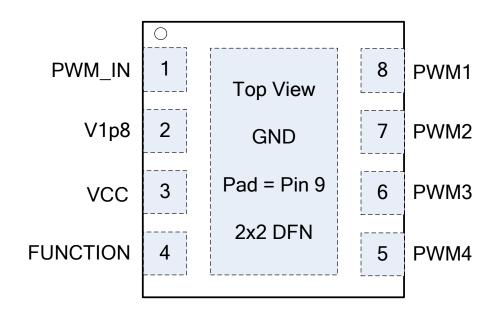

Figure 1: IR3599/IR3599A Package Top View

# FUNCTIONAL BLOCK DIAGRAM

Figure 2: IR3599/IR3599A Simplified Functional Block Diagram

TABLE 1: FUNCTION CONFIGURATION TABLE

| Function | PWM Mode           | Phase Mode | Part number |  |

|----------|--------------------|------------|-------------|--|

| 0        | IR ATL             | Quad       | IR3599A     |  |

| 1        | IR ATL             | Doubler    | IR3599A     |  |

| 0        | Standard Tri-state | Quad       | IR3599      |  |

| 1        | Standard Tri-state | Doubler    | IR3599      |  |

# International

# IR3599/IR3599A

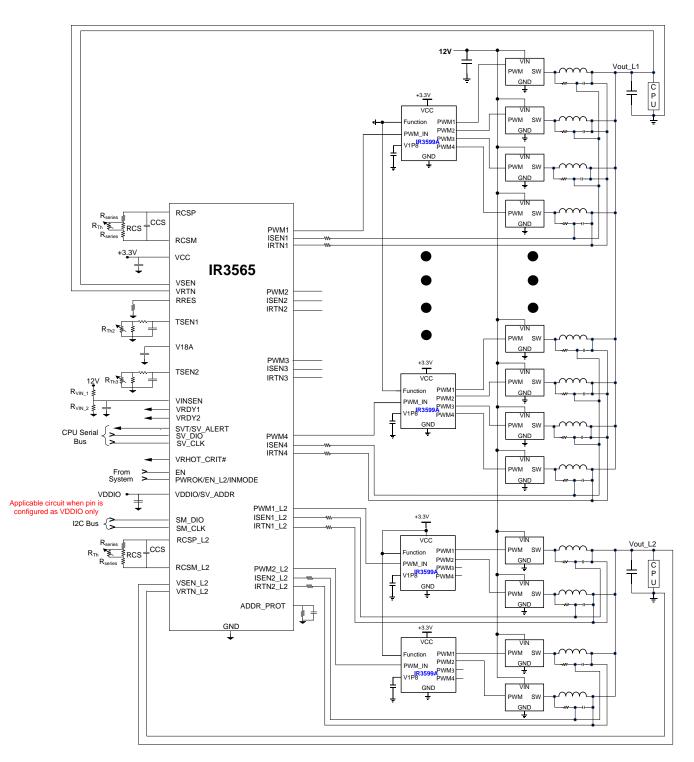

# TYPICAL APPLICATIONS

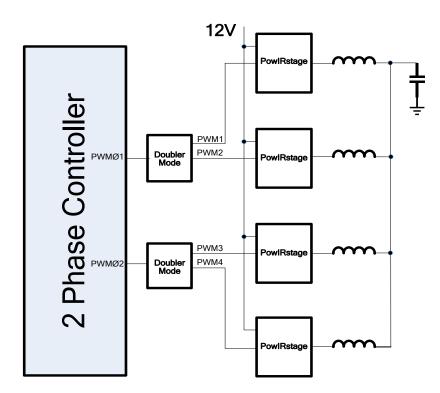

Figure 3: 20-Phase CPU VR solution using IR3599/A in QUAD mode & PowIRstage with the 6-phase Controller

## **PIN DESCRIPTIONS**

| PIN #   | PIN NAME | PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                                                               |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | PWM_IN   | The PWM_IN is the control signal input. Connect this pin to the PWM output of the controller. In Doubler mode, PWM_IN controls the behavior of PWM1 and PWM2. In QUAD mode, PWM_IN controls the behavior of PWM1, PWM2, PWM3, and PWM4.                                                                                                                                       |

| 2       | V1p8     | 1.8V internal LDO output. Place a high quality low ESR 0.47uF ceramic capacitor from this pin to the IR3599/IR3599A GND.                                                                                                                                                                                                                                                      |

| 3       | VCC      | Connect this pin to a +3.3V bias supply. Place a high quality low ESR 0.1uF ceramic capacitor from this pin to the IR3599/IR3599A GND.                                                                                                                                                                                                                                        |

| 4       | FUNCTION | The FUNCTION pin controls the Phase Mode (Doubler or Quad Modes). The FUNCTION pin levels are controlled by connecting the FUNCTION pin to Ground or VCC. Refer to the configuration instructions in Table 1 to program the FUNCTION pin. At power up, the function pin selection is latched into the IR3599/IR3599A, and therefore cannot be changed after initial power up. |

| 5       | PWM4     | Channel 4 PWM signal to the power stage                                                                                                                                                                                                                                                                                                                                       |

| 6       | PWM3     | Channel 3 PWM signal to the power stage                                                                                                                                                                                                                                                                                                                                       |

| 7       | PWM2     | Channel 2 PWM signal to the power stage                                                                                                                                                                                                                                                                                                                                       |

| 8       | PWM1     | Channel 1 PWM signal to the power stage                                                                                                                                                                                                                                                                                                                                       |

| (PAD) 9 | GND      | Bias and reference ground. All signals are referenced to this node.                                                                                                                                                                                                                                                                                                           |

## **ABSOLUTE MAXIMUM RATINGS**

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications are not implied.

| VCC                                      | -0.3V to +4.0V     |  |

|------------------------------------------|--------------------|--|

| PWM_IN, FUNCTION                         | -0.3V to VCC +0.3V |  |

| V1P8                                     | -0.3V to 2.2V      |  |

| PWMx                                     | -0.3V to VCC +0.3V |  |

| ESD                                      | 2KV, HBM Class 1-C |  |

| Thermal Information                      |                    |  |

| Thermal Resistance (OJC)                 | 8.9°C/W            |  |

| Thermal Resistance (OJA) <sup>1</sup>    | 73.2°C/W           |  |

| Maximum Junction Temperature             | 150°C              |  |

| Maximum Storage Temperature Range        | -65°C to 150°C     |  |

| Maximum Lead Temperature (Soldering 10s) | 300°C              |  |

**Note 1:**  $\theta$ JA is measured with the component mounted on a high effective thermal conductivity test board in free air. **TBD:** To be determined by Design Engineer.

## **ELECTRICAL SPECIFICATIONS**

#### **RECOMMENDED OPERATING CONDITIONS FOR RELIABLE OPERATION WITH MARGIN**

| Recommended Operating Ambient Temperature Range | -40°C to 85°C   |

|-------------------------------------------------|-----------------|

| Maximum Operating Junction Temperature          | 125°C           |

| VCC Supply Voltage Range                        | +2.85V to +3.6V |

| PWM Output frequency Range                      | 200k-800kHz     |

#### **ELECTRICAL CHARACTERISTICS**

Unless otherwise specified, these specifications were tested at +25°C. VCC = 3.3V.

| PARAMETER                             | SYMBOL                   | CONDITIONS                                         | MIN  | TYP   | MAX  | UNIT |

|---------------------------------------|--------------------------|----------------------------------------------------|------|-------|------|------|

| Supply                                |                          |                                                    |      |       |      |      |

| Supply Voltage                        | VCC                      |                                                    | 2.85 | 3.3   | 3.6  | V    |

| Supply Bias Current Idle              | I <sub>VCC_ATL</sub>     | IR3599A only. PWM_IN floating. Note 1              | -    | 1.07  | -    | mA   |

|                                       | I <sub>VCC_TRI</sub>     | IR3599 only. PWM_IN floating. Note 1               | -    | 1.48  | -    | mA   |

| Supply Bias Current — DOUBLER<br>Mode | I <sub>VCC_ATL</sub>     | IR3599A only. $f_{PWMx}$ = 400kHz, D=10%, no load. | -    | 3.04  | -    | mA   |

|                                       | I <sub>VCC_TRI</sub>     | IR3599 only. $f_{PWMx}$ = 400kHz, D=10%, no load.  | -    | 1.39  | -    | mA   |

| Supply Bias Current — QUAD Mode       | I <sub>VCC_ATL</sub>     | IR3599A only. $f_{PWMx}$ = 400kHz, D=10%, no load. | -    | 4.08  | -    | mA   |

|                                       | I <sub>VCC_TRI</sub>     | IR3599 only. $f_{PWMx}$ = 400kHz, D=10%, no load.  | -    | 1.38  | -    | mA   |

| VCC Rising Threshold for POR          |                          |                                                    | -    | 2.625 | -    | V    |

| VCC Falling Threshold for POR         |                          |                                                    | -    | 2.56  | -    | V    |

| LDO Output Voltage                    | V <sub>LDO</sub>         | VCC=3.3V                                           | 1.67 | 1.8   | 1.93 | V    |

| PWM Input IR ATL Mode (IR3599A o      | nly)                     | •                                                  |      | •     |      | •    |

| PWM Input High Threshold              | V <sub>IH(PWM)</sub>     |                                                    | -    | 1.0   | -    | V    |

| PWM Input Low Threshold               | V <sub>IL(PWM)</sub>     |                                                    | -    | 0.85  | -    | V    |

| PWM Tri-level High Threshold          | V <sub>TH(PWM)</sub>     |                                                    | -    | 2.51  | -    | V    |

| PWM Tri-level Low Threshold           | V <sub>TL(PWM)</sub>     |                                                    | -    | 2.36  | -    | V    |

| PWM Input Current Low                 | I <sub>IL(PWM_ATL)</sub> | $V_{PWM} = 0V$                                     | -    | 0.92  | -    | mA   |

| PWM Input Current High                | I <sub>IH(PWM_ATL)</sub> | V <sub>PWM</sub> = 1.8V                            | -    | 0.92  | -    | mA   |

| Minimum Recognized PWM Pulse<br>Width |                          | Note 1                                             | -    | 43    | -    | ns   |

| PWM Input Standard Tri-state Mode     | (IR3599 only)            |                                                    |      |       |      |      |

| PWM Input High Rising Threshold       | V <sub>IH(PWM)</sub>     |                                                    | -    | 2.5   | -    | V    |

| PWM Input High Falling Threshold      | V <sub>IL(PWM)</sub>     |                                                    | -    | 2.35  | -    | V    |

| PWM Input Low Rising Threshold        | V <sub>TH(PWM)</sub>     |                                                    | -    | 1.0   | -    | V    |

| PWM Input Low Falling Threshold       | V <sub>TL(PWM)</sub>     |                                                    | -    | 0.85  | -    | V    |

| PWM Input Current Low                 | I <sub>IL(PWM_TRI)</sub> | V <sub>PWM</sub> = 0V                              | -    | 0.35  | -    | mA   |

| PWM Input Current High                | I <sub>IH(PWM_TRI)</sub> | $V_{PWM} = 3.3V$                                   | -    | 0.6   | -    | mA   |

# International

PWM Doubler/Quad Logic

# IR3599/IR3599A

| PARAMETER                             | SYMBOL                 | CONDITIONS                                                                                                                                         | MIN  | TYP  | MAX | UNIT |

|---------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|------|

| PWM Input Tri-State Float Voltage     | V <sub>PWM_IN</sub>    | PWM_IN = floating                                                                                                                                  | -    | 1.55 | -   | V    |

| PWM Input Impedance                   | R <sub>PWM</sub>       |                                                                                                                                                    | -    | 4.2  | -   | kΩ   |

| Minimum Recognized PWM Pulse<br>Width |                        | Note 1                                                                                                                                             | -    | 39   | -   | ns   |

| PWM Output (IR3599A only)             |                        |                                                                                                                                                    |      |      |     |      |

| PWM Output High Threshold             | V <sub>OH(PWM)</sub>   |                                                                                                                                                    | 1.6  | -    | 2.0 | V    |

| PWM Output Low Threshold              | V <sub>OL(PWM)</sub>   |                                                                                                                                                    | -    | -    | 0.4 | V    |

| Transition Time — Rise                | t <sub>R(HS)</sub>     | $C_{PCB}$ =50pF. Measured from 10% to 90% PWM output. Note 1                                                                                       | -    | 12.8 | -   | ns   |

| Transition Time — Fall                | t <sub>F(HS)</sub>     | $C_{\text{PCB}}\text{=}50\text{pF}.$ Measured from 90% to 10% PWM output. Note 1                                                                   | -    | 7.9  | -   | ns   |

| Propagation Delay — Turn-on           | $t_{\text{PDH(HS)}}$   | Unloaded. Measured from PWM_IN rising edge to PWM1 rising edge. Note 1                                                                             | -    | 15.3 | -   | ns   |

| Propagation Delay — Turn-off          | t <sub>PDL(HS)</sub>   | Unloaded. Measured from PWM_IN falling edge to PWM1 falling edge. Note 1                                                                           | -    | 9.2  | -   | ns   |

| Propagation Delay — Enter Tri-State   | $t_{\text{PDTS(en)}}$  | Unloaded. Measured from the edge<br>PWM_IN enters tri-state to PWM1 high<br>impedance. Note 1                                                      | -    | 10.5 | -   | ns   |

| Propagation Delay — Exit Tri-State    | t <sub>PDTS(dis)</sub> | Unloaded. Measured from the edge<br>PWM_IN exits tri-state to PWM1 high or<br>low. Note 1                                                          | -    | 24.3 | -   | ns   |

| Output Impedance — Source             | R <sub>HS_SOURCE</sub> |                                                                                                                                                    | -    | 90   | -   | Ω    |

| Output Impedance — Sinking            | R <sub>HS_SINK</sub>   |                                                                                                                                                    | -    | 57   | -   | Ω    |

| PWM Output (IR3599 only)              | •                      | ·                                                                                                                                                  |      | •    | •   |      |

| PWM Output High Threshold             | V <sub>OH(PWM)</sub>   |                                                                                                                                                    | 2.85 | -    | -   | V    |

| PWM Output Low Threshold              | V <sub>OL(PWM)</sub>   |                                                                                                                                                    | -    | -    | 0.4 | V    |

| Transition Time — Rise                | t <sub>R(HS)</sub>     | C <sub>PCB</sub> =50pF. Measured from 10% to 90%<br>PWM output. Note 1                                                                             | -    | 8.4  | -   | ns   |

| Transition Time — Fall                | t <sub>F(HS)</sub>     | $C_{PCB}$ =50pF. Measured from 90% to 10% PWM output. Note 1                                                                                       | -    | 8.1  | -   | ns   |

| Propagation Delay — Turn-on           | t <sub>PDH(HS)</sub>   | Unloaded. Measured from PWM_IN rising<br>edge to PWM1 rising edge. Note 1                                                                          | -    | 10.8 | -   | ns   |

| Propagation Delay — Turn-off          | $t_{\text{PDL(HS)}}$   | Unloaded. Measured from PWM_IN falling<br>edge to PWM1 falling edge. Note 1                                                                        | -    | 8.6  | -   | ns   |

| Propagation Delay — Enter Tri-State   | t <sub>PDTS(en)</sub>  | Loaded with $5k\Omega$ pull-up and $5k\Omega$ pull-down resistors. Measured from the edge PWM_IN enters tri-state to PWM1 enters tri-state. Note 1 | -    | 34.5 | -   | ns   |

| Propagation Delay — Exit Tri-State    | t <sub>PDTS(dis)</sub> | Loaded with $5k\Omega$ pull-up and $5k\Omega$ pull-down resistors. Measured from the edge PWM_IN exits tri-state to PWM1 high or low. Note 1       | -    | 23.6 | -   | ns   |

| Output Impedance Source               | R <sub>HS_SOURCE</sub> |                                                                                                                                                    | -    | 55   | -   | Ω    |

| Output Impedance — Sinking            | R <sub>HS SINK</sub>   |                                                                                                                                                    | -    | 45   | -   | Ω    |

Note 1: Guaranteed by design but not tested in production.

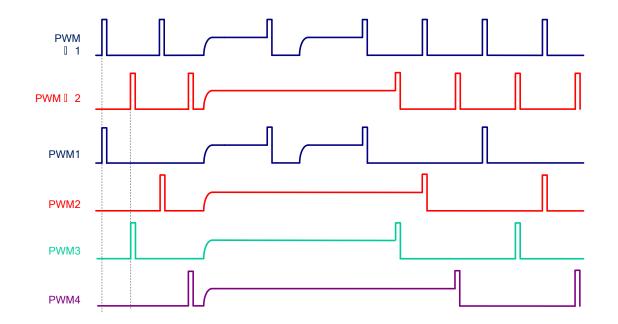

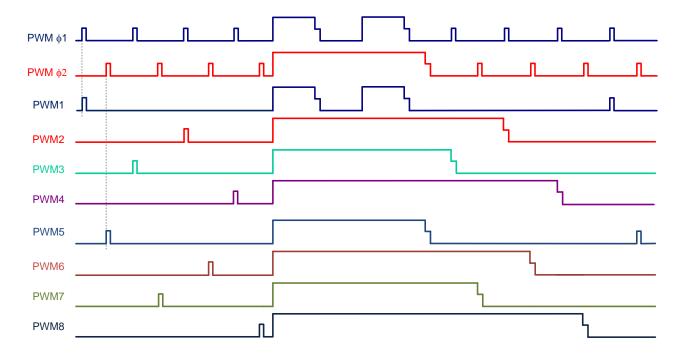

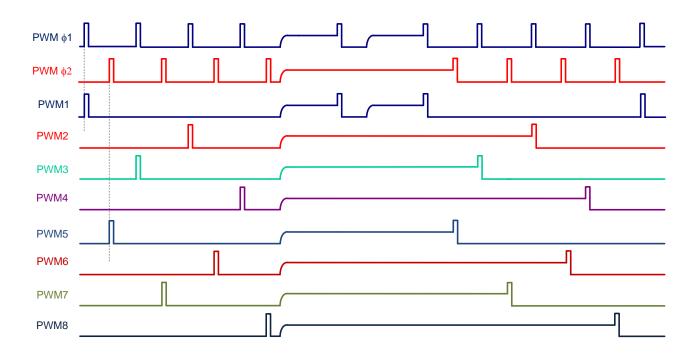

# MODE AND TIMING DIAGRAMS

Figure 4: IR3599/IR3599A Phase Modes

Figure 5: IR3599A timing when configured in DOUBLER mode (IR ATL PWM signals at input)

Figure 6: IR3599 timing when configured in DOUBLER mode (Industry Standard Tri-state PWM signals at input)

# IR3599/IR3599A

# IR3599/IR3599A

Figure 8: IR3599 timing when configured in Quad mode (Industry Standard Tri-state PWM signals at input)

# **GENERAL DESCRIPTION**

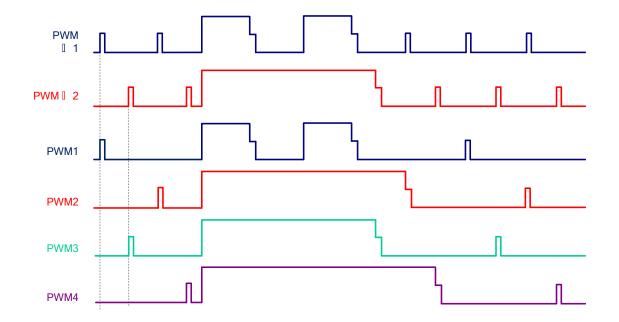

IR3599/IR3599A is a phase multiplier which is designed for high phase count applications to reduce the number of interface signals between controller and drivers. Each IR3599/IR3599A can be configured to drive up to four independent power stages from one PWM input. When it is configured in doubler mode, only two PWM output signals are controlled by the single PWM input. The doubler logic alternates the two PWM outputs at half of the PWM input frequency so that it can generate two out of phase PWM signals. The rest two PWM output are in tri-state. When it is configured in quad mode, all four PWM output are controlled by the single PWM input. The guad logic will alternate the four PWM outputs at 0°, 90°, 180°, and 270° respectively, and each at 1/4 of the PWM input frequency. The phase modes for doubler and quad are shown in Figure 4.

IR3599A features the patented IR Active Tri-Level (ATL) PWM input and output, designed to work with IR digital multi-phase controller and IR PowIRstage. IR3599 features industry's standard tri-state PWM input and output interfaces, designed to work with general multi-phase controllers, drivers or power stages.

# THEORY OF OPERATION

### **POWER-ON RESET (POR)**

14

IR3599/IR3599A incorporates a power-on reset feature, which ensures the device is active only after the supply voltage is high enough to generate 1.8V.

IR3599/IR3599A is powered from 3.3V DC supply. An internal LDO generates a 1.8V rail to power the PWM output in IR3599A. During initial startup, the 1.8V rail follows the rising 3.3V supply voltage, proportional to an internal resistor tree. All PWM outputs are disabled and in a high impedance state before the VCC supply voltage exceeds the POR rising threshold.

During normal operation the IR3599/IR3599A continue to remain active until the VCC supply voltage falls below the POR falling threshold.

## IR ACTIVE TRI-LEVEL (ATL) PWM INPUT/OUTPUT SIGNAL

The IR3599A is driven by a patented active tri-level (ATL) PWM control signal provided by the IR digital PWM controllers and also delivers the ATL PWM signals to the following power stages. During normal operation, PWM input signal swings between 0V and 1.8V and the generated PWM output signals also swings between 0 and 1.8V. When PWM input signal crosses a voltage level higher than the Tri-level high threshold, it will enter tri-state operation. The IR3599A provides a 1.0mA typical pull-up current to drive the PWM input to the tri-state condition of 3.3V when the PWM controller output is in its high impedance state. The 1.0mA typical current is designed for driving worst case stray capacitances and transition the IR3599A into the tri-state condition rapidly to avoid a prolonged period of conduction in the following power stage during faults. This fast tri-state operation eliminates the need for any tri-state hold-off time of the PWM signal to dwell in the shutdown window. Immediately after the IR3599A is driven into the tri-state mode, the 1mA current is disabled so that power is conserved. Once the IR3599A enters tri-state operation, all of the PWM outputs will be transitioned to high impedance states in order to also transition the power stages into tri-state. This allows the system to operate in single phase mode when PS2 mode is the mode mode of operation.

When the PWM input signal level falls below the tri-level low threshold, the IR3599A will switch back into normal operation.

#### INDUSTRY STANDARD TRI-STATE PWM INPUT/OUTPUT SIGNAL

The IR3599 accepts industry's standard 3.3V and 5V tri-state PWM signals. It doubles or quadruples the single PWM input and then delivers multi-phase PWM signals to the drivers or power stages. During normal operation, the PWM input swings from ground to 3.3V or 5V and the generated PWM output signals will swing from ground to VCC. If the PWM input is released from the controller side or if the PWM level is within a range of 1.65V, the IR3599 will enter tri-state operation. The floating PWM input will be driven by the IR3599 to its tri-state window and all the PWM outputs will also transition to tri-state.

#### DOUBLER/QUAD MODE REACTION TO TRI-STATE PWM INPUT

In Doubler or quad mode, anytime there is a tri-state on the PWM\_IN, all PWM outputs (PWMx) are tristated immediately with minimum delays. When the PWM\_IN transitions from a tri-state to a high and then from a high to a low, only the 0 deg phase (PWM1) operates. This allows the VR to operate properly in PS2 mode and during load releases. Once the PWM\_IN sees a transition from a low to a high, the doubler or quad function starts again, with output on the other PWM pins. The tri-state timing when configured in doubler mode or quad mode are shown in Figure 5 - Figure 8.

#### FREQUENCY RANGE

The IR3599/IR3599A is designed to operate over a wide input and output frequency range. When operating in Doubler mode, the input frequency at the PWM\_IN input is 2x the output frequency. When operating in Quad mode, the input frequency at the PWM\_IN input is 4x the output frequency.

The IR3599/IR3599A is designed to operate with output frequencies between 200 kHz and 800 kHz.

### **CONFIGURING THE PHASE MODES**

The IR3599/IR3599A can operate in 2 separate Phase modes which are Doubler and Quad. Table 1 shows the user how to configure the Modes utilizing the FUNCTION pin. The FUNCTION selection (pin 4) is latched into the IR3599/IR3599A at power up, and cannot be changed after power on reset.

### SUPPLY DECOUPLING CAPACITOR

VCC decoupling to the IR3599/IR3599A is provided by a 0.1uF bypass capacitor  $C_{Vcc}$  located close to the supply input pin. A series resistor Rvcc, typically 10 $\Omega$ , is added in series with the supply voltage to filter high frequency ringing and noise. A 0.47uF bypass capacitor located close to V1p8 output pin is recommended for the internal LDO decouple.

# ENVIRONMENTAL QUALIFICATIONS

| Qualification Level        |                                        | Consumer                                   |      |  |

|----------------------------|----------------------------------------|--------------------------------------------|------|--|

| Moisture Sensitivity Level |                                        | "package type"                             | MSL1 |  |

|                            | Machine Model                          | Class B                                    |      |  |

|                            | (JESD22-A115A)                         | Maximum MM ESD Voltage ≥ 200V to ≤400V     |      |  |

| ESD                        | Human Body Model<br>(JESD22-A114F)     | Class 1C                                   |      |  |

| 230                        |                                        | Maximum HBM ESD Voltage ≥ 2000V to ≤ 4000V |      |  |

|                            | Charged Device Model<br>(JESD22-C101D) | Class III                                  |      |  |

|                            |                                        | Maximum CDM ESD Voltage ≥ 500V to ≤1000V   |      |  |

| RoHS Compliant             |                                        | Yes                                        |      |  |

† Qualification standards can be found at International Rectifier web site: <u>http://www.irf.com</u>

†† Exceptions to AEC-Q101 requirements are noted in the qualification report.

# IR3599/IR3599A

## **MARKING INFORMATION**

# **PACKAGE INFORMATION**

DFN 2 x 2mm, 8-pin

0.90±0.10 2.00±0.10 [0.079] [0.035] Pin 1 C0.25 Location [0.010] Ó 2.00±0.10 0.50 🗇 1.60±0.10 +[0.063] [0.079] 0.25 [0.020] [0.010] 0.25 ref 0.30 TOP VIEW [0.010] [0.012] BOTTOM VIEW Recommended PCB Land Pattern 0.85 [0.033] 1.90 ł [0.075] SIDE VIEW 0.95 [0.037] UNLESS OTHERWISE SPECIFIED 0.50 1.60 TOLERANCE ON DIMENSIONS: [0.020] [0.063] .XX ±0.05 ALL DIMENSIONS ARE IN mm [INCH] 0.30 0.90 [0.012] [0.035]

0.50 [0.020]

DFN8 2X2 Package Dimensions