#### **AUTOMOTIVE MCU WITH LIN INTERFACE FOR RGB LED DRIVER**

#### January 2023

#### **GENERAL DESCRIPTIONS**

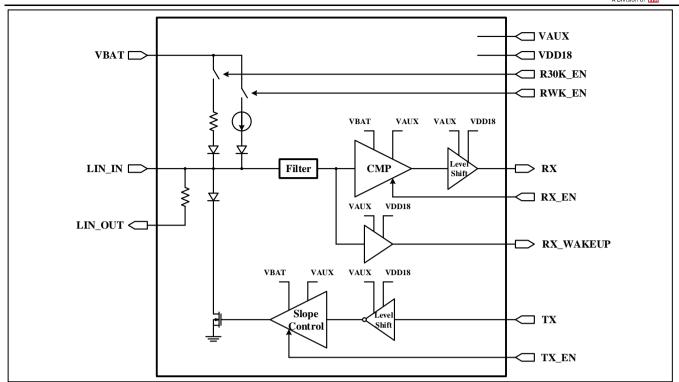

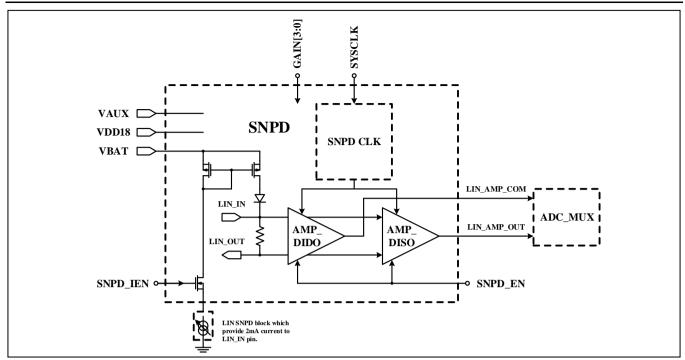

The IS32LT3183A is a single chip RGB driver with a LIN interface suitable for automotive ambient color applications. The LIN master can send RGB color, intensity and control instructions over the LIN Bus and receives back status and error information. It is fully conformed to LIN standard, for transmission rates to 19.2kbps. The up IS32LT3183A supports LIN SNPD (Slave Node Position Detection) using BSM (Bus Shunt Method).

The IS32LT3183A integrates key functional features for developing compact multicolor LED LIN nodes. An integrated low-drop voltage regulator to support internal circuit operation. It can sink a constant current of 60mA to each of the RGBW LEDs. In order to minimize current consumption, the IS32LT3183A supports a Sleep mode to power down with wake-up capability via the LIN bus. The integrated MCU is an 8051 based CPU core with 32kB embedded flash, of which each byte is protected by ECC. This is the highest reliability level of code storage for the challenging environment of automobile applications.

IS32LT3183A offers strong Electro Static Discharge (ESD) performance and can withstand high voltages on the LIN bus. LIN bus signal is designed to minimize Electro Magnetic Emissions (EME).

#### **APPLICATIONS**

- · LIN RGB LED ambient lighting

- Dome LED lighting

- Dash board lighting

- LIN to SPI or LIN to I2C bridge

- General purpose MCU for LIN node slave operation

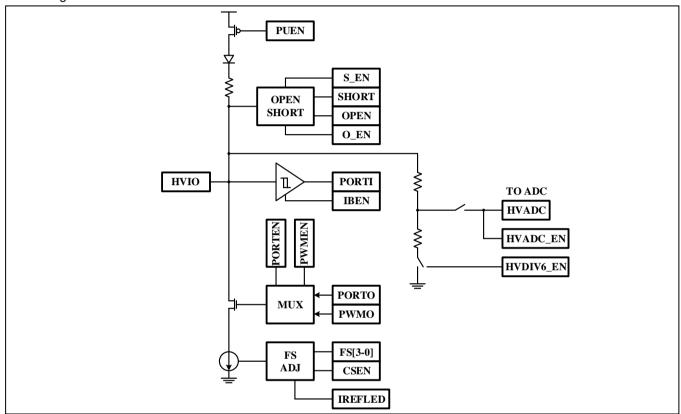

#### **HV I/O CONFIGURATIONS**

- 4x high voltage I/Os with up to 60mA configurable current source for RGBW LEDs

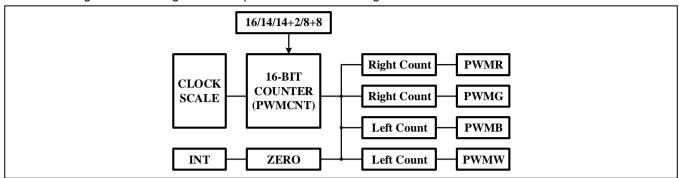

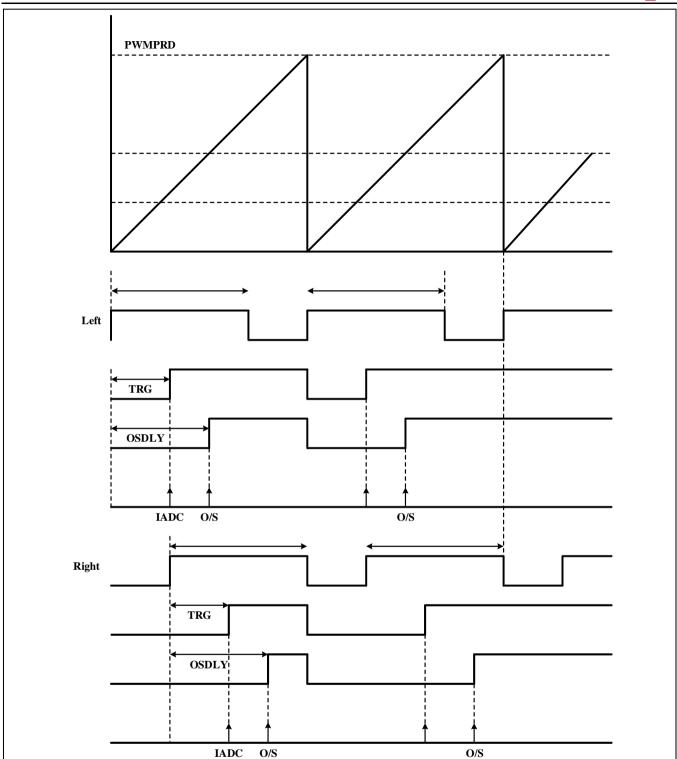

- 4x 16-bit PWM outputs

- Open/short diagnostic capability for LED

- 12-bit ADC

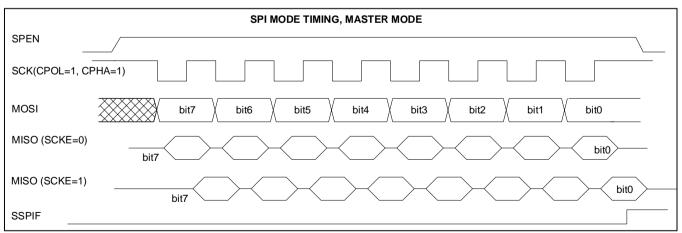

- SPI master interface

- I2C master interface

- Interrupt capability for all inputs

- GPIO with input de-bounce

#### **FEATURES**

Wide supply voltage 5.5V ~ 18V continuous with max input voltage up to 40V

- Sleep mode supply current 60µA(max.) with wake-up via LIN bus capability

- 4 independent LED current sinks

- Software programmable LED current, up to 60mA

- Reconfigurable as GPIO, SPI master interface or I2C master interface

- Integrated MCU for LIN protocol handling and LIN message decoding

- 1-T enhance 8051 core

- 16MHz (±5%) internal OSC

- 32kB Flash and 2kB SRAM

- Each nibble of code is protected by ECC for double bit detection and single bit correction

- LIN Interface

- SPI/I2C master interface

- GPIO and external Interrupt/wake-up

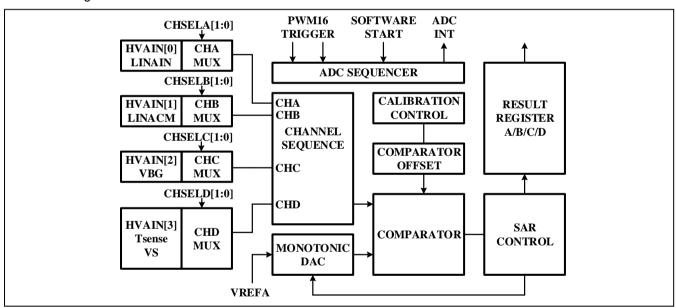

- 12-Bit SAR ADC with conversion time up to 10µs

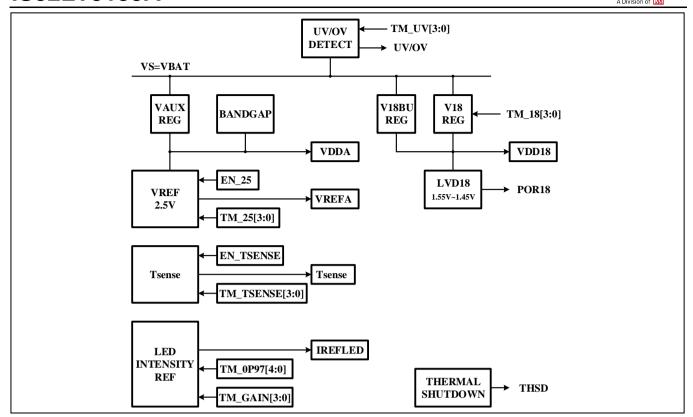

- On-chip temperature sensor

- Math Co-processor for 16-bit MUL and 32-bit DIV Operations

- LIN Interface

- Baud rate up to 19.2kbps

- Integrated LIN transceiver

- Internal LIN slave termination resistor

- Compliant to LIN 2.2A

- Support SNPD (BSM) auto addressing

- Protections and ESD

- 40V load dump protected

- ±8kV for GPIO

- Temperature compensation to protect LED

- LED drivers

- LED color calibration via matrix calculation

- Flash storage for calibration values

- Intensity control (linear or logarithmic)

- Dimming and color transition function with programmable transition time

- Up to 16-Bit LED color range

- PWM with spread spectrum to optimize EMI

- LED temperature compensation

- Diagnostics

- Open/Short LED detection

- High temperature warning and shutdown

- LIN retry mode on error detection

- SOP-8-EP package

- AEC-Q100 Qualified

- RoHS & Halogen-Free Compliance

- TSCA Compliance

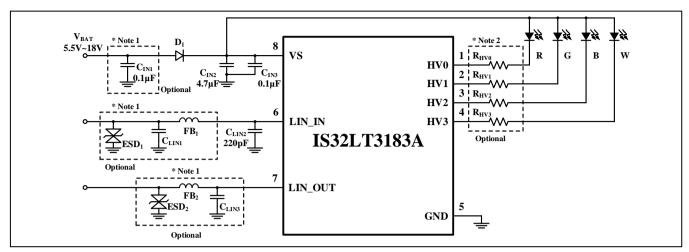

#### **TYPICAL APPLICATION CIRCUITE**

Figure 1 Typical Application Circuit

- Note 1: These components are optional to optimize EMC and ESD performance.

- Note 2: These power resistors are optional to minimize the power consumption on the driver.

### **PIN CONFIGURATION**

| Package  | Pin Configuration (Top View) |  |  |

|----------|------------------------------|--|--|

| SOP-8-EP | HV0                          |  |  |

#### **PIN DESCRIPTION**

| No. | Pin         | Voltage Range | Description                                                                  |

|-----|-------------|---------------|------------------------------------------------------------------------------|

| 1~4 | HV0~HV3     | IO HV         | High voltage I/O.                                                            |

| 5   | GND         | Power         | Ground pin.                                                                  |

| 6   | LIN_IN      | Analogue HV   | Connection to LIN bus, LIN bus shunt input.                                  |

| 7   | LIN_OUT     | Analogue HV   | LIN bus shunt output.                                                        |

| 8   | vs          | Power HV      | Battery supply voltage; external protection against reverse polarity needed. |

|     | Thermal Pad | -             | Must be connected to GND.                                                    |

| Voltage Code | Voltage Range                          |

|--------------|----------------------------------------|

| Analogue     | Analogue pin                           |

| Power        | Power/supply pin                       |

| IO           | Multifunctional pin (configurable pin) |

| HV           | High voltage, VBAT or VS related       |

ORDERING INFORMATION

Automotive Range: -40°C To +125°C

| Order Part No.       | Package             | QTY/Reel |

|----------------------|---------------------|----------|

| IS32LT3183A-GRLA3-TR | SOP-8-EP, Lead-free | 2500     |

Copyright © 2022 Lumissil Microsystems. All rights reserved. Lumissil Microsystems reserves the right to make changes to this specification and its products at any time without notice. Lumissil Microsystems assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.

Lumissil Microsystems does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Lumissil Microsystems receives written assurance to its satisfaction, that:

- a.) the risk of injury or damage has been minimized;

- b.) the user assume all such risks; and

- c.) potential liability of Lumissil Microsystems is adequately protected under the circumstances

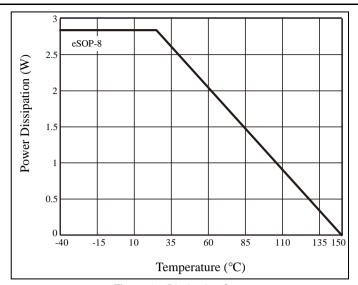

**ABSOLUTE MAXIMUM RATINGS (NOTE 3)**

| Voltage at VS                                                                                                      | -0.3V ~ +44V   |

|--------------------------------------------------------------------------------------------------------------------|----------------|

| Voltage at LIN_IN, LIN_OUT                                                                                         | -30V ~ +40V    |

| Voltage at HV0, HV1, HV2, HV3                                                                                      | -0.3V ~ +44V   |

| Maximum junction temperature, T <sub>JMAX</sub>                                                                    | +150°C         |

| Storage temperature range, T <sub>STG</sub>                                                                        | -65°C ~ +150°C |

| Operating temperature range, T <sub>A</sub> =T <sub>J</sub>                                                        | -40°C ~ +150°C |

| Power dissipation, P <sub>D(MAX)</sub>                                                                             | 2.84W          |

| Package thermal resistance, junction to ambient (4-layer standard test PCB based on JESD 51-2A), $\theta_{JA}$     | 44°C/W         |

| Package thermal resistance, junction to thermal PAD (4-layer standard test PCB based on JESD 51-2A), $\theta_{JP}$ | 1.41°C/W       |

| ESD (HBM)<br>ESD (CDM)                                                                                             | ±8kV<br>±750V  |

**Note 3:** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **OPERATING CONDITIONS**

The IC can have 7 different hardware modes. The exact functionality of these modes depends on the hardware and software configuration:

#### Reset

- Triggered by hardware. When Vs drop below a critical level, the complete chip is powered down

- The analogue and digital supply regulators are disabled. No functionality is available in this mode

#### Normal Mode Main application running

- Microcontroller fully functional

- Analogue fully functional

#### Idle Mode Triggered by the software. Digital part can run at lower frequency (24kHz)

- Internal peripherals inaccessible (T0/T1/T2, UART2, I2C)

- LIN not possible

- External peripherals (external Interrupts) can wake up the CPU from Idle mode

#### **Stop Mode** Triggered by the software

- LIN not possible

- IOSC oscillator is disabled

#### Sleep Mode Triggered by the software

- Microcontroller powered down

- Digital and analogue supply powered down

- Sleep mode and wake-up functionality running on help supply VAUX

#### Under Voltage Triggered by the hardware under voltage detection Interrupt (EXIF\_INT3: UVF)

- Microcontroller fully functional

- Power down behavior can be managed via software

- Reduced current capability on HVx below Vs=5.5V

Over Voltage Triggered by the hardware over voltage detection Interrupt (EXIF\_INT3: OVF)

- Microcontroller fully functional

- Behaviour can be managed via software

**OPERATING CONDITIONS (CONTINUE)**

| Symbol         | Parameter            | Conditions | Min. | Тур. | Max. | Unit |

|----------------|----------------------|------------|------|------|------|------|

| Vs             | Supply voltage range |            | 5.5  |      | 18   | V    |

| T <sub>A</sub> | Ambient temperature  |            | -40  |      | 125  | °C   |

#### **ELECTRICAL CHARACTERISTICS**

Following characteristics are valid over the full temperature range of T<sub>J</sub>=T<sub>A</sub>= -40°C ~ +125°C and a supply range of 5.5V ≤ Vs ≤ 18V unless otherwise noted.

| Symbol                    | Parameter                                              | Conditions                                                                         | Min. | Тур. | Max. | Unit |

|---------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------|------|------|------|------|

| Global Param              | eters                                                  |                                                                                    |      | •    |      |      |

| Іпом                      | Normal mode working current                            | All pins are inputs,<br>R30K_EN=1                                                  |      | 10   | 15   | mA   |

| I <sub>SLEEP</sub>        | Sleep mode current                                     | All pins are inputs, chip in Sleep mode; V <sub>S</sub> =12V, T <sub>A</sub> =25°C |      | 40   | 60   | μA   |

| Frequencies               |                                                        |                                                                                    |      |      |      |      |

| Δlosc                     | Tolerance of RC oscillator                             | losc=16MHz                                                                         | -5   |      | +5   | %    |

| f <sub>SOSC</sub>         | Frequency separate 24kHz<br>RC oscillator              |                                                                                    |      | 24   |      | kHz  |

| tstartup_por              | Startup time of the system after power on              | Time until internal dig reset is inactive (Note 4)                                 |      |      | 500  | μs   |

| tstartup_sleep            | Startup time of the system after release of Sleep Mode | Time until internal dig reset is inactive (Note 4)                                 |      |      | 250  | μs   |

| VS – Program              | nmable Under Voltage Interrup                          | t Parameters                                                                       |      |      |      |      |

|                           |                                                        | 000 (default)                                                                      | 4.5  | 5    | 5.5  |      |

| $V_{UV\_RANGE\_VS}$       |                                                        | 100                                                                                | 6.5  | 7.0  | 7.5  | V    |

|                           | UVOVTRIM (TM_UV [2:0])                                 | 111                                                                                | 8.0  | 8.5  | 9.0  |      |

| $V_{\text{HYST\_UV\_VS}}$ | Hysteresis for under voltage                           |                                                                                    | 0.1  |      | 1    | V    |

| t <sub>UV_VS</sub>        | Debouncing for under voltage                           | (Note 4)                                                                           | 10   | 30   | 60   | ms   |

| VS – Over Vo              | Itage (Load Dump) Interrupt R                          | elated Parameters                                                                  |      |      |      |      |

| $V_{LDH}$                 | Level for load dump Interrupt                          |                                                                                    | 29   | 31   | 33   | V    |

| V <sub>HYST_LD</sub>      | Hysteresis for load dump<br>Interrupt                  |                                                                                    | 1    | 2.5  | 4    | V    |

| T <sub>LD</sub>           | Debouncing for load dump<br>Interrupt                  | (Note 4)                                                                           | 50   |      | 100  | μs   |

| ADC (12Bit) R             | elated Parameters                                      |                                                                                    |      |      |      |      |

| $V_{REF}$                 | Ref voltage                                            |                                                                                    | 2.46 | 2.5  | 2.54 | V    |

| DNL                       | Differential nonlinearity                              | (Note 4)                                                                           | -5   |      | +5   | LSB  |

| INL                       | Integral nonlinearity                                  | (Note 4)                                                                           | -8   |      | +8   | LSB  |

| RESADC                    | Quantization steps                                     |                                                                                    |      | 4096 |      | LSB  |

| ADCERR                    | Quantification error                                   |                                                                                    | -0.5 |      | +0.5 | LSB  |

| tconv                     | Min. conversion Time                                   | For max. ADC input frequency = 4MHz (Note 4)                                       |      | 8    |      | μs   |

ELECTRICAL CHARACTERISTICS (CONTINUE) Following characteristics are valid over the full temperature range of  $T_J = T_A = -40^{\circ}\text{C} \sim +125^{\circ}\text{C}$  and a supply range of  $5.5V \le V_S \le 18V$  unless otherwise noted.

| Symbol                  | Parameter                                  | Conditions                                                         | Min. | Тур.  | Max. | Unit |

|-------------------------|--------------------------------------------|--------------------------------------------------------------------|------|-------|------|------|

| Multi-Purpose           | e High Voltage IOs (HV0~HV3)               |                                                                    |      |       |      | •    |

| Common Par              | ameters                                    |                                                                    |      |       |      |      |

| ILEAKHVX                | Leakage current in case HV0~HV3 are inputs |                                                                    | -5   |       | 5    | μA   |

|                         |                                            | 000 (Default)                                                      |      | 1.33  |      |      |

|                         |                                            | 001                                                                |      | 2.66  |      |      |

|                         |                                            | 010                                                                |      | 5.33  |      |      |

| 4                       | for HV0~HV3<br>HVx_DBWID [2:0] (Note 4)    | 011                                                                |      | 10.6  |      |      |

| t <sub>DEBHVX</sub>     |                                            | 100                                                                |      | 21.3  |      | ms   |

|                         |                                            | 101                                                                |      | 42.6  |      |      |

|                         |                                            | 110                                                                |      | 85.3  |      |      |

|                         |                                            | 111                                                                |      | 170.6 |      |      |

| Digital Input f         | or Wake Up                                 |                                                                    |      |       |      | •    |

| VINLH_WUHVX             | Digital WU input threshold level L => H    | Active in Sleep Mode                                               |      |       | 2.4  | V    |

| VINHL_WUHVX             | Digital WU input threshold level H => L    | Active in Sleep Mode                                               | 1.2  |       |      | V    |

| V <sub>HYST_WUHVX</sub> | Hysteresis                                 |                                                                    | 0.1  |       |      | V    |

| Fast Digital Ir         | nput (Not Active in Sleep Mode             | )                                                                  |      |       |      |      |

| VINLHHVX                | Fast Digital Input threshold level L => H  |                                                                    |      |       | 2.4  | V    |

| Vinhlhvx                | Fast Digital Input threshold level H => L  |                                                                    | 1.2  |       |      | V    |

| V <sub>HYSTHVX</sub>    | Hysteresis                                 |                                                                    | 0.1  |       |      | V    |

| Тмахнух                 | Max. delay                                 | For rising and falling edge (Note 4)                               |      |       | 25   | ns   |

| Open Drain S            | witch                                      |                                                                    |      |       |      | •    |

| Routlhvx                | ON – resistance of HVx                     | Vs=12V, HvxOD_EN=1<br>HV0~HV3=0.2V                                 |      | 20    | 40   | Ω    |

| Open Drain C            | onstant Current Source                     |                                                                    |      |       |      |      |

|                         | Output current of HVx                      | Vs>5.5V                                                            | 0    |       | 60   | mA   |

| l <sub>outhvx</sub>     | Output current of HVx                      | V <sub>S</sub> >5.5V, HVx _FS[4:0]=0x1F<br>TM_GAIN[3:0] adjustment |      | 4     |      | m ^  |

|                         | stepsize                                   | Vs>5.5V, TM_GAIN[3:0]=0x0F<br>HVx _FS[4:0] adjustment              |      | 2     |      | mA   |

#### **ELECTRICAL CHARACTERISTICS (CONTINUE)**

Following characteristics are valid over the full temperature range of  $T_J = T_A = -40$ °C ~ +125°C and a supply range of  $5.5V \le V_S \le 18V$  unless otherwise noted.

| Symbol                     | Parameter                            | Conditions                                                | Min.              | Тур. | Max.   | Unit  |

|----------------------------|--------------------------------------|-----------------------------------------------------------|-------------------|------|--------|-------|

| M                          | Min. handroom valtage                | HVx current = 60mA, Vs=12V                                |                   | 0.9  | 1.2    | V     |

| $V_{HR_{MIN}}$             | Min. headroom voltage                | HVx current = 20mA, V <sub>S</sub> =12V                   |                   | 0.6  | 0.8    | V     |

| lout_errhvx                | Output current of HVx relative error | 5.5V≤ V <sub>S</sub> ≤18V,<br>8mA< I <sub>OUT</sub> ≤60mA | -7                |      | +7     | %     |

| IOUT_ERRHVX                | Output current of HVx relative error | 5.5V≤ V <sub>S</sub> ≤18V,<br>4mA≤ I <sub>OUT</sub> ≤8mA  | -10               |      | +10    | %     |

| HV0 Monitor                |                                      |                                                           |                   |      |        |       |

| Monitor Curre              | ent                                  |                                                           |                   |      |        |       |

| I <sub>MON</sub>           | Monitor current                      | R2MAEN= 1                                                 | 1.8               | 2    | 2.4    | mA    |

| I <sub>MON_VOUTSWING</sub> | Output voltage swing                 |                                                           | V <sub>S</sub> -4 |      | Vs     | V     |

| Differential A             | mplifier                             |                                                           |                   |      |        |       |

| Vs_mon                     | Monitor input voltage range          | Vs≥ 8.5V                                                  | Vs-3.7            |      | Vs-1.5 | V     |

| Gain                       | Vs Monitor Gain                      |                                                           |                   | 0.2  |        | -     |

| Wake Up Rela               | ted Parameters                       |                                                           |                   |      |        |       |

| twu                        | Wake up filter time pins HVx         | Sleep Mode, HVx rising & falling edge (Note 4)            | 25                |      | 50     | μs    |

| twu_LIN                    | Wake up filter time pin LIN          | Time for dominant level after Sleep mode (Note 4)         | 15                |      | 150    | μs    |

| Temperature :              | Sensor related parameters            |                                                           |                   |      |        |       |

| Temperature :              | Shutdown Circuit                     |                                                           |                   |      |        |       |

| T <sub>OT_ON</sub>         |                                      | Tested by special test mode                               |                   | 160  |        | °C    |

| T <sub>OT_OFF</sub>        | Over temperature shutdown            | only                                                      |                   | 140  |        | °C    |

| T <sub>OT_HYST</sub>       |                                      | (Note 4)                                                  |                   | 20   |        | °C    |

| Temperature :              | Sensor (For ADC Measuremen           | t)                                                        |                   |      |        |       |

| T <sub>RANGE</sub>         | Temperature range                    | (Note 4)                                                  | -40               |      | 150    | °C    |

| T <sub>ACC</sub>           | Accuracy                             | (Note 4)                                                  | -10               |      | 10     | °C    |

| ΔV <sub>TC</sub>           | Sensitivity                          | (Note 4)                                                  |                   | 5    |        | mV/°C |

Note 4: Guaranteed by design & characterization, not tested in production.

#### **ELECTRICAL CHARACTERISTICS (CONTINUE)**

Following characteristics are valid over the full temperature range of  $T_J = T_A = -40$ °C ~ +125°C and a supply range of  $8V \le V_S \le 18V$  unless otherwise noted.

|                         | Parameters (adapted from Lin spec                     | T                                                                              |       |      | ļ.    |      |

|-------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------|-------|------|-------|------|

| Symbol                  | Parameter                                             | Conditions                                                                     | Min.  | Тур. | Max.  | Unit |

| Pin LIN_IN              |                                                       |                                                                                |       |      |       |      |

| Transmitter             |                                                       |                                                                                |       |      |       |      |

| I <sub>BUS_LIM</sub>    | Short circuit bus current                             | V <sub>LIN_IN</sub> =V <sub>S</sub> , LIN driver on                            | 40    |      | 200   | mA   |

| Rslave                  | Pull up resistance bus, normal & standby mode         | Vs=12V, V <sub>LIN_IN</sub> =0V                                                | 28    | 30   | 40    | kΩ   |

| LIN_PU-SLEEP            | Pull up current, Sleep mode                           | V <sub>LIN_IN</sub> =0V, V <sub>S</sub> =12V,<br>Sleep mode, RWK_EN=1          | -100  |      |       | μΑ   |

| IBUS_PAS_DOM            | Input Leakage at the receiver include 30k pull up     | V <sub>LIN_IN</sub> =0V, V <sub>S</sub> =12V,<br>R30K_EN=1                     | -1    |      |       | mA   |

| IBUS_PAS_REC            | Bus reverse current, recessive                        | LIN driver off, Vs=8V, V <sub>LIN_IN</sub> =18V                                |       |      | 20    | μΑ   |

| IBUS_NO_BAT             | Bus reverse current loss of battery                   | Vs= 0V, V <sub>LIN_IN</sub> =18V, LIN 2.1                                      |       |      | 50    | μΑ   |

| I <sub>BUS_NO_GND</sub> | Bus current during loss of ground                     | V <sub>S</sub> = V <sub>GND</sub> =12V,<br>0< V <sub>LIN_IN</sub> < 18V, J2602 | -0.5  |      | 1     | mA   |

| Volbus                  | Transmitter dominant voltage                          | Network load= 500Ω,<br>TXD=0 (LIN driver on)                                   | 0     |      | 0.2   | Vs   |

| VohBus                  | Transmitter recessive voltage                         | TXD= High                                                                      | 0.8   |      | 1     | Vs   |

| Свиѕ                    | BUS input capacitance; Value for LIN conformance test | Pulse response via 10kΩ,<br>V LIN_PULSE= 12V,<br>Vs open (Note 10)             |       | 25   | 35    | pF   |

| Receiver                |                                                       |                                                                                |       |      |       |      |

| V <sub>BUSDOM</sub>     | Receiver dominant voltage                             |                                                                                |       |      | 0.4   | Vs   |

| V <sub>BUSREC</sub>     | Receiver recessive voltage                            |                                                                                | 0.6   |      |       | Vs   |

| V <sub>BUS_CNT</sub>    | Centre point of receiver threshold                    | V <sub>BUS_CNT</sub> =<br>(V <sub>BUSDOM</sub> +V <sub>BUSREC</sub> )/2        | 0.475 | 0.5  | 0.525 | Vs   |

| V <sub>BUS_HYS</sub>    | Receiver Hysteresis                                   | VBUS_ HYS = (VBUSREC- VBUSDOM)                                                 |       |      | 0.175 | Vs   |

| AC Paramete             | ers                                                   |                                                                                |       |      |       |      |

| t <sub>RX_PDF</sub>     | Propagation delay receiver (Note 5, 6, 9)             | C <sub>RXD</sub> = 25pF falling edge                                           |       |      | 6     | μs   |

| t <sub>RX_PDR</sub>     | Propagation delay receiver (Note 5, 6, 9)             | C <sub>RXD</sub> = 25pF rising edge                                            |       |      | 6     | μs   |

| t <sub>RX_SYM</sub>     | Prop. Delay receiver symmetry                         | trx_pdf - trx_pdr (Note 9)                                                     | -2    |      | 2     | μs   |

| t <sub>REC_DEB</sub>    | Receiver debounce time (Note 10)                      | LIN rising & falling edge                                                      | 0.5   |      | 4     | μs   |

| D <sub>1</sub>          | LIN duty cycle 1 (Note 6,7)                           | 20kbps operation,<br>Normal mode                                               | 0.396 |      |       | -    |

| D <sub>2</sub>          | LIN duty cycle 2 (Note 6,7)                           | 20kbps operation,<br>Normal mode                                               |       |      | 0.581 | 1    |

| D <sub>3</sub>          | LIN duty cycle 3 (Note 6,7)                           | 10.4kbs operation,<br>Low speed mode                                           | 0.417 |      |       | -    |

#### **ELECTRICAL CHARACTERISTICS (CONTINUE)**

Following characteristics are valid over the full temperature range of  $T_J = T_A = -40$ °C ~ +125°C and a supply range of  $8V \le V_S \le 18V$  unless otherwise noted.

| Symbol                    | Parameter                                      | Conditions                           | Min. | Тур. | Max.  | Unit |

|---------------------------|------------------------------------------------|--------------------------------------|------|------|-------|------|

| D <sub>4</sub>            | LIN duty cycle 4 (Note 6,7)                    | 10.4kbs operation,<br>Low speed mode |      |      | 0.590 | -    |

| Δt <sub>3</sub>           | trec(MAX) —tdom(MIN) (Note 8)                  | 10.4kbs operation,<br>Low speed mode |      |      | 15.9  | μs   |

| ∆t₄                       | trec(MIN) -tdom(MAX) (Note 8)                  | 10.4kbs operation,<br>Low speed mode |      |      | 17.28 | μs   |

| t <sub>TXD_TO</sub>       | TXD dominant time out (Note 10)                | Normal mode, V <sub>TXD</sub> = 0V   |      | 64   |       | ms   |

| LIN Auto-Add              | ressing LIN_IN/LIN_OUT                         |                                      |      |      |       |      |

| V <sub>S_RG</sub>         | Functional range LIN auto-<br>addressing       |                                      | 9    |      | 15    | V    |

| R <sub>PU_LIN_SLAVE</sub> | LIN slave pull up resistance                   |                                      | 28   | 30   | 40    | kΩ   |

| Ishunt                    | Bus pull-up source current for auto-addressing |                                      |      | 2    |       | mA   |

| V <sub>LIN</sub>          | LIN bus voltage range                          |                                      | 0    |      | 2.5   | V    |

| Rshunt                    | LIN shunt resistor (Internal)                  |                                      |      | 1    |       | Ω    |

**Note 5:** This parameter is tested by applying a square wave signal to the LIN. The access to internal signals RXD, TXD will be performed by test mode. The minimum slew rate for the LIN rising and falling edges is 50V/us.

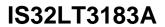

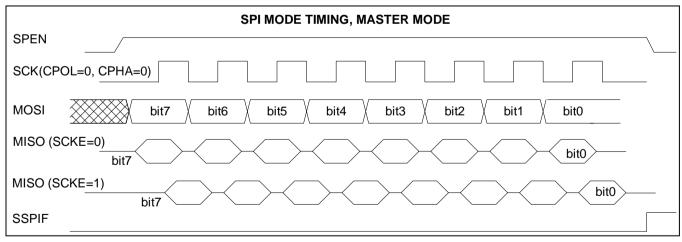

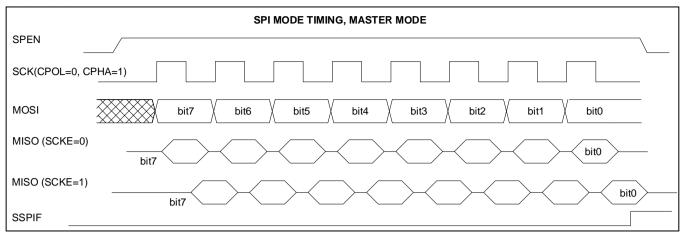

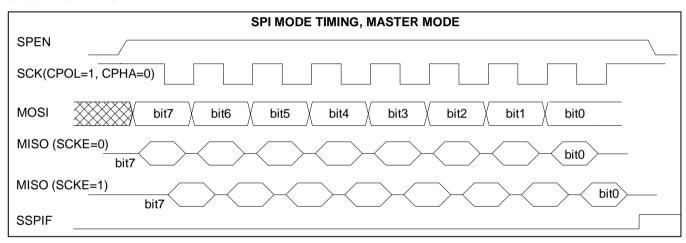

Note 6: See Figure 2: LIN timing diagram

Note 7: Standard loads for duty cycle measurements are  $1K\Omega/1nF$ ,  $660\Omega/6.8nF$ ,  $500\Omega/10nF$ , internal termination disabled

Note 8: In accordance to SAE J2602

Note 9: Parameter in relation to internal signal TXD

Note 10: Guaranteed by design & characterization, not measured in production.

As shown in figure, both worst case duty cycles can be calculated as follows:

Dwc1 =  $t_{BUS rec(min)} / 2 \times t_{Bit}$

$Dwc2 = t_{BUS\_rec(max)} / 2 \times t_{Bit}$

Thresholds for duty cycle calculation in accordance to LIN2.x:

| Baud Rate        | 20k Baud    | 10.4k Baud  |

|------------------|-------------|-------------|

| t <sub>ВІТ</sub> | 50µs        | 96µs        |

| Dwc1             | D1          | D3          |

| Dwc2             | D2          | D4          |

| THREC(MAX)       | 0.744 VS_TX | 0.778 VS_TX |

| THDOM(MAX)       | 0.581 VS_TX | 0.616 VS_TX |

| THREC(MIN)       | 0.422 VS_TX | 0.389 VS_TX |

| THDOM(MIN)       | 0.284 VS_TX | 0.251 VS_TX |

Figure 2 LIN Timing Diagram: Relation Between Propagation Delay And Duty Cycle

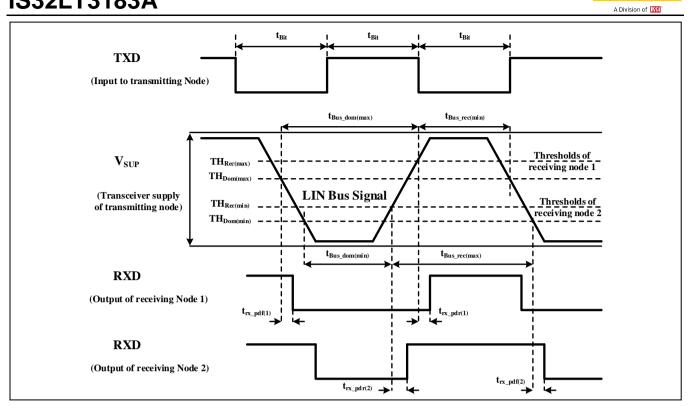

#### **FUNCTIONAL BLOCK DIAGRAM**

#### **APPLICATION INFORMATION**

#### **ENHANCED 1-CYCLE 8051 CPU**

The CPU core is an enhanced version of standard 8051, which a RISC architecture and maintains binary instruction set compatible with the industry standard 8051. An average of 10 times performance enhancement in typical applications can be easily achieved. The CPU operates at 20-bit addressing space that allows up to 1M bytes of program and data space for expansion. It also includes the following enhanced features compared with standard 8051:

- 16-bit LARGE addressing mode and 20-bit FLAT addressing mode control register ACON

- Two data pointers DPTR and DPTR1, and additional DPS, DPX, DPX1, MXAX registers for MOVX instruction

- 8-bit stack pointer for LARGE mode and 16-bit extended stack pointer for FLAT mode control register ESP

- Hardware Multiplication and Division Unit (MDU) provides 12 times faster performance using MD[5-0] and ARCON

- Programmable wait state for program space for on-chip flash memory using WTST register

- 256 Bytes of Direct Data Memory

- Enhanced Interrupt Controller allows 15 Interrupt sources and 2 priority levels.

- Power Saving modes include Idle mode, Sleep mode and Stop mode.

- Access Control of critical registers TA and TB registers

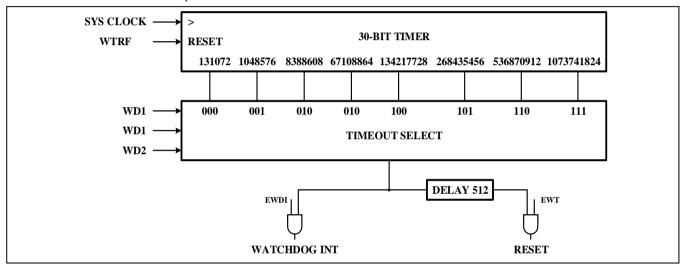

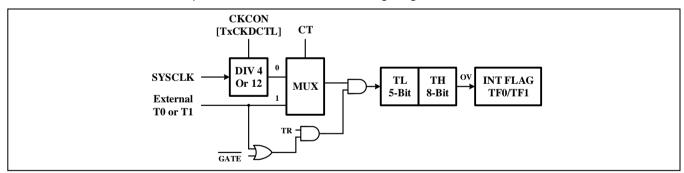

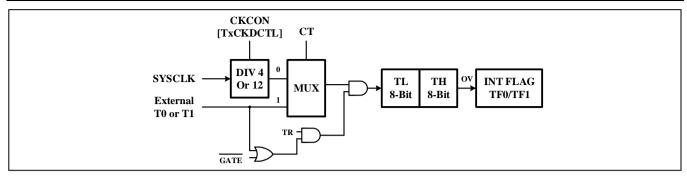

In addition to standard 8051 peripherals, the CPU core also integrates the following peripherals, which are in the same CPU clock domain.

- 4 I/O ports, HV0-HV3 related to port[3:0]

- 30-bit Watchdog Timer. WDT, WDCON, and CKCON registers

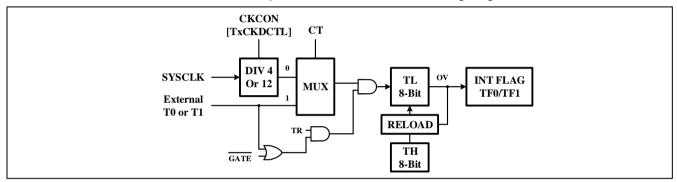

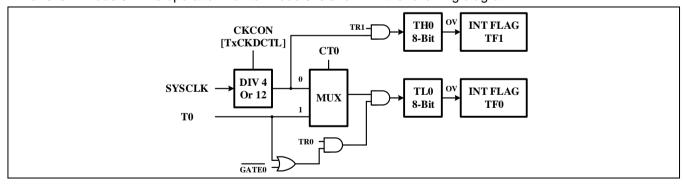

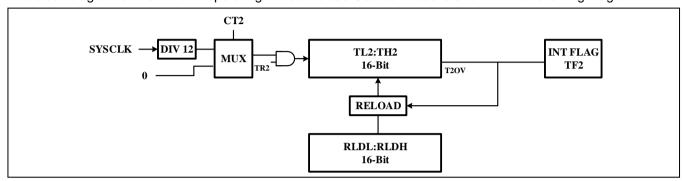

- Three 16-bit Timers, T0/T1 and T2. TCON, RLDL, RLDH, TL2, TH2, and T2CON registers

- I2C Master Controller. I2CMSA, I2CMCR, I2CMBUF, and I2CMTP register

- SPI Master Controller

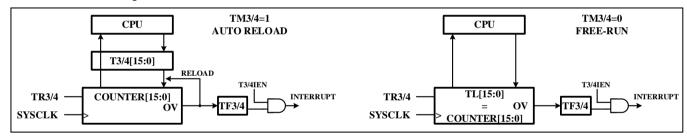

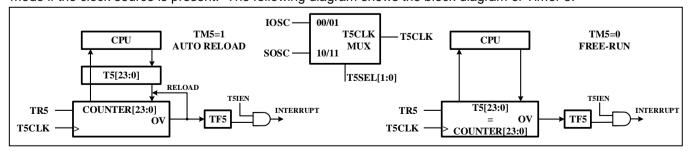

- Two 16-bit Timers T3/T4 and one 24-bit Timer T5

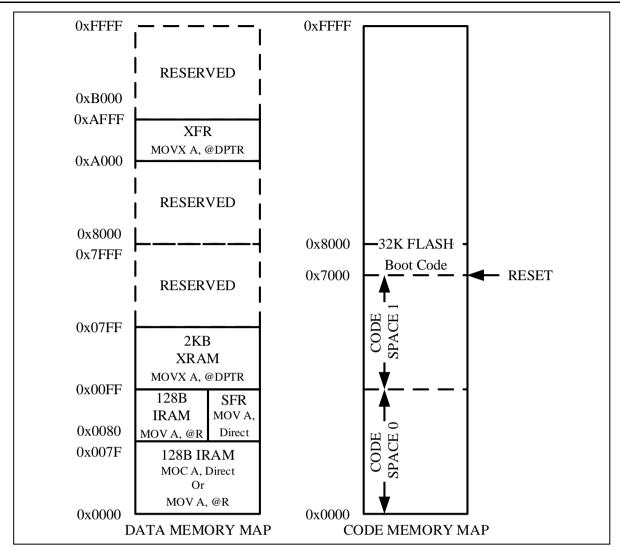

#### **MEMORY MAP**

The following chart shows the memory mapping of IS32LT3183A. On the right, it shows the flash memory space. IS32LT3183A has a 32KB embedded flash, which is organized as 64 pages and each page has storage space of 512 byte. Boot code is stored between 0x7000H to 0x7FFFH, from page 56 to 63. Page 0 is reserved for Interrupt, while page 55 is reserved for protected key (from 0x6FF8 to 0x6FFF).

The flash has a separate, independent 128 byte of information block page (IFB). IFB serves two purposes in upper and lower locations. Lower location 0x00 - 0x3F is used for storing manufacturing and calibration parameters in manufacturing tests. IFB upper location 0x40 - 0x7B is used for one-time programmable memory for user program. IFB is protected and cannot be erased by end users. For details of IFB information, please refer to ISSI's customer support.

On the left, it shows the 8051 standard memory mapping. These mapped areas are described in detail in this document, along with the register's associated functions. Assuming readers are familiar with 8051 standard operations and peripherals, the compatible functions are not covered here.

Figure 3 Memory Mapping of IS32LT3183A

#### REGISTER MAP: SFR (0x80 - 0xFF) and XFR (0xA000 - 0xAFFF)

The SFR address map maintains maximum compatibilities to most commonly used 8051 like MCU. The following table shows the SFR address map. Since SFR can be accessed by direct addressing mode, registers of built-in peripherals that require fast access are mostly located in SFR. XFR is mainly used for on-chip peripheral control and configurations.

REGISTER MAP: SFR (0x80 - 0xFF)

| Address                      | 0                                    | 1                                | 2                           | 3                            | 4                       | 5                        | 6                            | 7                        |

|------------------------------|--------------------------------------|----------------------------------|-----------------------------|------------------------------|-------------------------|--------------------------|------------------------------|--------------------------|

| 0XF0                         | В                                    | -                                | -                           | -                            | I2CMSA                  | I2CMCR                   | I2CMBUF                      | I2CMTP                   |

| 0XE0                         | ACC                                  | -                                | -                           | -                            | -                       | -                        | -                            | -                        |

| 0XD0                         | PSW                                  | -                                | -                           | -                            | -                       | -                        | -                            | -                        |

| 0XC0                         | SCON1                                | SBUF1                            | SCON2                       | I2CMTO                       | PMR                     | STATUS                   | MCON                         | TA                       |

| 0XB0                         | P3                                   | -                                | CCAPM0                      | CCAPM1                       | CCAPM2                  | ССАРМ3                   | CCAPM4                       | CCAPM5                   |

| 0XA0                         | P2                                   | SPICR                            | SPIMR                       | SPIST                        | SPIDATA                 | SFIFO2                   | SBUF2                        | SINT2                    |

| 0X90                         | P1                                   | EXIF                             | WTST                        | DPX                          | CMPST                   | DPX1                     | -                            | -                        |

| 0X80                         | P0                                   | SP                               | DPL                         | DPH                          | DPL1                    | DPH1                     | DPS                          | PCON                     |

|                              | 8                                    | 9                                | Α                           | В                            | С                       | D                        | Е                            | _                        |

|                              | U                                    | 9                                | <b>A</b>                    | ь                            | C                       | U                        |                              | F                        |

| 0XF8                         | EXIP                                 | MD0                              | MD1                         | MD2                          | MD3                     | MD4                      | MD5                          | ARCON                    |

| 0XF8<br>0XE8                 | _                                    | -                                |                             |                              | _                       | _                        |                              |                          |

|                              | EXIP                                 | MD0                              | MD1                         |                              | _                       | _                        |                              | ARCON                    |

| 0XE8                         | EXIP<br>EXIE                         | MD0<br>CH                        | MD1<br>MXAX                 | MD2                          | MD3                     | MD4                      | MD5                          | ARCON<br>P4              |

| 0XE8<br>0XD8                 | EXIP<br>EXIE<br>WDCON                | MD0<br>CH<br>CL                  | MD1<br>MXAX<br>DPXR         | MD2<br>-<br>I2CSCON2         | MD3<br>-<br>I2CSST2     | MD4<br>-<br>I2CSADR2     | MD5<br>-<br>I2CSDAT2         | ARCON<br>P4<br>P5        |

| 0XE8<br>0XD8<br>0XC8         | EXIP<br>EXIE<br>WDCON<br>T2CON       | MD0<br>CH<br>CL<br>TB            | MD1<br>MXAX<br>DPXR<br>RLDL | MD2<br>-<br>I2CSCON2<br>RLDH | MD3 - I2CSST2 TL2       | MD4 - I2CSADR2 TH2       | MD5 - I2CSDAT2 ADCCFG3       | ARCON P4 P5 T34CON       |

| 0XE8<br>0XD8<br>0XC8<br>0XB8 | EXIP<br>EXIE<br>WDCON<br>T2CON<br>IP | MD0<br>CH<br>CL<br>TB<br>ADCCFG1 | MD1 MXAX DPXR RLDL ADCAL    | MD2 - I2CSCON2 RLDH ADCAH    | MD3 - I2CSST2 TL2 ADCBL | MD4 - I2CSADR2 TH2 ADCBH | MD5 - I2CSDAT2 ADCCFG3 ADCCL | ARCON P4 P5 T34CON ADCCH |

**REGISTER MAP: XFR (0xA000 - 0xAFFF)**

| INCOICTER WATER |          | (0242-1000 | ., .,    |          |          |          |          |          |

|-----------------|----------|------------|----------|----------|----------|----------|----------|----------|

| Address         | 0 1      |            | 2        | 3        | 4        | 5        | 6        | 7        |

| A000            | -        | -          | -        | T5CON    | TL5      | TH5      | TT5      | -        |

| A010            | -        | -          | FLSHSPRT | FLSHCPRT | -        | -        | -        | -        |

| A020            | FLSHCMD  | FLSHDAT    | FLSHADH  | FLSHADL  | ISPCLKF  | ECCSTA   | ECCCFG   | -        |

| A030            | -        | -          | -        | -        | -        | -        | -        | -        |

| A040            | HVIOCFA0 | HVIOCFB0   | HVIOCFC0 | HVIOCFD0 | HVIOCFA1 | HVIOCFB1 | HVIOCFC1 | -        |

| A050            | HVIOINT0 | HVIOINT1   | HVIOINT2 | HVIOINT3 | -        | -        | -        | -        |

|                 | 8        | 9          | Α        | В        | С        | D        | E        | F        |

| A008            | REGTRIM  | REFTRIM    | REFILED  | REFGLED  | REF2MA   | UVOVTRIM | BTTRIM   | PWRINT   |

| A018            | IOSCFTRM | -          | -        | -        | -        | -        | -        | -        |

| A048            | HVIOCFA2 | HVIOCFB2   | HVIOCFC2 | -        | HVIOCFA3 | HVIOCFB3 | HVIOCFC3 | HFFILTER |

| A058            | HVIODBN0 | HVIODBN1   | HVIODBN2 | HVIODBN3 | -        | -        | -        | -        |

| Address | 0       | 1        | 2        | 3       | 4       | 5       | 6        | 7       |

|---------|---------|----------|----------|---------|---------|---------|----------|---------|

| A080    | PWMHRL  | PWMHRH   | PWMHGL   | PWMHGH  | PWMHBL  | PWMHBH  | PWMHWL   | PWMHWH  |

| A090    | LINCTRL | LINCNTRH | LINCNTRL | LINSBRH | LINSBRL | LININT  | LININTEN | -       |

| A0A0    | LINTCON | TXDTOL   | TXDTOH   | RXDTOL  | RXDTOH  | BSDCLR  | BSDCLRH  | BSDWKC  |

|         | 8       | 9        | Α        | В       | С       | D       | E        | F       |

| A088    | -       | PWMHUPD  | PWMHOSC  | OSDLY   | PWMHTRG | PWMINTE | PWMHCFG  | PWMHINT |

| A098    | -       | •        | •        | -       | -       | -       | R2MACFG  | SSCCFG  |

| A0A8    | BSDACT  | -        | XCVRCFG  | SNPDCFG | SNPDINT | -       | -        | -       |

#### **CPU REGISTERS**

| ACC | Accu | mulator  |          | R/W |   |   |   |   |  |

|-----|------|----------|----------|-----|---|---|---|---|--|

| Bit | 7    | 6        | 5        | 4   | 3 | 2 | 1 | 0 |  |

| RD  |      |          | ACC[7:0] |     |   |   |   |   |  |

| WR  |      | ACC[7:0] |          |     |   |   |   |   |  |

SFR Address: 0xE0 Default: 0b00000000

ACC is the CPU accumulator register and is involved in direct operations of many instructions. ACC is bit addressable.

| В   | B Re   | gister |        | R/W |   |   |   |   |

|-----|--------|--------|--------|-----|---|---|---|---|

| Bit | 7      | 6      | 5      | 4   | 3 | 2 | 1 | 0 |

| RD  |        |        | B[7:0] |     |   |   |   |   |

| WR  | B[7:0] |        |        |     |   |   |   |   |

SFR Address: 0xF0 Default: 0b00000000

B register is used in standard 8051 multiply and divide instructions and also used as an auxiliary register for temporary storage. B is also bit addressable.

| PSW Program Status Word R/W |     |    |    |    |     |     |    |    |   |

|-----------------------------|-----|----|----|----|-----|-----|----|----|---|

|                             | Bit | 7  | 6  | 5  | 4   | 3   | 2  | 1  | 0 |

|                             | RD  | CY | AC | FO | RS1 | RS0 | OV | UD | Р |

|                             | WR  | CY | AC | FO | RS1 | RS0 | OV | UD | Р |

SFR Address: 0xD0 Default: 0b00000000

CY Carry Flag

AC Auxiliary Carry Flag (BCD Operations)

FO General Purpose

RS1, RS0 Register Bank Select

OV Overflow Flag

UD User Defined (reserved)

P Parity Flag

| SP  | Stack | k Pointer |         | R/W |   |   |   |   |  |

|-----|-------|-----------|---------|-----|---|---|---|---|--|

| Bit | 7     | 6         | 5       | 4   | 3 | 2 | 1 | 0 |  |

| RD  |       |           | SP[7:0] |     |   |   |   |   |  |

| WR  |       | SP[7:0]   |         |     |   |   |   |   |  |

SFR Address: 0x81 Default: 0b00000000

PUSH will result ACC to be written to SP+1 address. POP will load ACC from IRAM with the address of SP.

| ESP | Exter | nded Stack P | ointer | R/W |   |   |   |   |  |

|-----|-------|--------------|--------|-----|---|---|---|---|--|

| Bit | 7     | 6            | 5      | 4   | 3 | 2 | 1 | 0 |  |

| RD  |       | ESP[7:0]     |        |     |   |   |   |   |  |

| WR  |       | ESP[7:0]     |        |     |   |   |   |   |  |

SFR Address: 0x9B Default: 0b00000000

In FLAT address mode, ESP and SP together form a 16-bit address for stack pointer. ESP holds the higher byte of the 16-bit address.

| STATUS | ATUS Program Status Word |     | Vord | RO |       |       |       |       |

|--------|--------------------------|-----|------|----|-------|-------|-------|-------|

| Bit    | 7                        | 6   | 5    | 4  | 3     | 2     | 1     | 0     |

| RD     | -                        | HIP | LIP  | -  | SPTA1 | SPRA1 | SPTA0 | SPRA0 |

| WR     | -                        | -   | -    | -  | -     | -     | -     | -     |

SFR Address: 0xC5 Default: 0b00000000

| HIP | High Priority (HP) Interrupt Status |

|-----|-------------------------------------|

|     | THE STATE OF THE STATE OF           |

HIP=0 indicates no HP Interrupt

HIP=1 indicates HP Interrupt progressing

LIP Low Priority (LP) Interrupt Status

LIP=0 indicates no LP Interrupt LIP=1 indicates LP Interrupt progressing

SPTA1 **UART1 Transmit Activity Status**

SPTA1=0 indicates no UART1 transmit activity

SPTA1=1 indicates UART1 transmit active

SPRA1 **UART1** Receive Activity Status

SPRA1=0 indicates no UART1 receive activity

SPRA1=1 indicates UART1 receive active

SPTA0 **UARTO Transmit Activity Status**

> SPTA0=0 indicates no UART0 transmit activity SPTA0=1 indicates UART0 transmit active

SPRA0 **UARTO Receive Activity Status**

> SPRA0=0 indicates no UART0 receive activity SPRA0=1 indicates UART0 receive active

The program should check status conditions before entering SLEEP, STOP, IDLE, or PMM modes to prevent loss of intended functions from delayed entry until these events are finished.

#### **Addressing Timing and Memory Modes**

The clock speed of an MCU with embedded flash memory is usually limited by the access time of on-chip flash memory. While in modern process technology, the CPU can operate faster, the access time of flash memory is usually around 40 nanoseconds, which becomes a bottleneck for CPU performance. To mitigate this problem, a programmable wait state function is incorporated to allow faster CPU clock rate to access slower embedded flash memory. The wait state is controlled by WTST register as shown in the following.

| WTST | TA | Protected | F | R/W |       |       |       |       |

|------|----|-----------|---|-----|-------|-------|-------|-------|

| Bit  | 7  | 6         | 5 | 4   | 3     | 2     | 1     | 0     |

| RD   | -  | -         | - | -   | WTST3 | WTST2 | WTST1 | WTST0 |

| WR   | -  | -         | - | -   | WTST3 | WTST2 | WTST1 | WTST0 |

SFR Address: 0x92 Default: 0b00000111

WTST[3:0] Wait State Control register. WTST sets the wait state in CPU clock period

| WTST3 | WTST2 | WTST1 | WTST0 | Wait State Cycle |

|-------|-------|-------|-------|------------------|

| 0     | 0     | 0     | 0     | 0                |

| 0     | 0     | 0     | 1     | 1                |

| 0     | 0     | 1     | 0     | 2                |

| 0     | 0     | 1     | 1     | 3                |

| 0     | 1     | 0     | 0     | 4                |

| 0     | 1     | 0     | 1     | 5                |

| 0     | 1     | 1     | 0     | 6                |

| 0     | 1     | 1     | 1     | 7                |

| 1     | 0     | 0     | 0     | 8                |

| 1     | 0     | 0     | 1     | 9                |

| 1     | 0     | 1     | 0     | 10               |

| 1     | 0     | 1     | 1     | 11               |

| 1     | 1     | 0     | 0     | 12               |

| 1     | 1     | 0     | 1     | 13               |

| 1     | 1     | 1     | 0     | 14               |

| 1     | 1     | 1     | 1     | 15               |

The default setting of the program wait state register after reset is 0x07 and the software must initialize the setting to change the wait state setting. If ISOCDIV=0, then WTST should be set higher than 1 to allow enough read access time, others can set WTST to minimum.

| MCC | N  | XRAN      | // Relocation | Register | R/W TA Pr | otected |   |   |   |  |

|-----|----|-----------|---------------|----------|-----------|---------|---|---|---|--|

| Bi  | it | 7         | 6             | 5        | 4         | 3       | 2 | 1 | 0 |  |

| RI  | 0  | MCON[7:0] |               |          |           |         |   |   |   |  |

| W   | R  | MCON[7:0] |               |          |           |         |   |   |   |  |

SFR Address: 0xC6 Default: 0b00000000

MCON holds the starting address of XRAM in 4KB steps. For example, if MCON[7:0]=0x01, the starting address is 0x001000. MCON is not meaningful in IS32LT3183A because it only contains on-chip XRAM and MCON should not be modified from 0x00.

The LARGE mode, addressing mode is compatible with standard 8051 in 16-bit address. FLAT mode extends the program address to 20-bit and expands the stack space to 16-bit data space. The data space is always 16-bit in either LARGE or FLAT mode.

| ACON |   |   |         | R/W TAF | Protected |    |     |     |

|------|---|---|---------|---------|-----------|----|-----|-----|

| Bit  | 7 | 6 | 5       | 4       | 3         | 2  | 1   | 0   |

| RD   | - | - | IVECSEL | -       | DPXREN    | SA | AM1 | AM0 |

| WR   | - | - | IVECSEL | -       | DPXREN    | SA | AM1 | AM0 |

SFR Address: 0x9D Default: 0b00000000

ACON is addressing mode control register.

**IVECSEL** Interrupt Vector Selection

INTVSEC=1 maps the Interrupt vector to 0x7000 space.

INTVSEC=0 maps to normal 0x0000 space

**DPXREN** DPXR Register Control Bit.

If DPXREN is 0, "MOVX, @Ri" instruction uses P2 (0xA0) register and XRAM Address [15:8]. If

DPXREN is 1, DPXR (0xDA) register and XRAM Address [15:8] is used.

SA Extended Stack Address Mode Indicator. This bit is read-only.

0 – 8051 standard stack mode where stack resides in internal 256-byte memory

1 – Extended stack mode. Stack pointer is ESP:SP in 16-bit addressing to data space.

AM1, AM0 AM1 and AM0 Address Mode Control Bits

00 - LARGE address mode in 16-bit

1x - FLAT address mode with 20-bit program address

#### MOVX A, @Ri Instructions

| DPXR |   |           |   | R/W |   |   |   |   |  |

|------|---|-----------|---|-----|---|---|---|---|--|

| Bit  | 7 | 6         | 5 | 4   | 3 | 2 | 1 | 0 |  |

| RD   |   | DPXR[7:0] |   |     |   |   |   |   |  |

| WR   |   | DPXR[7:0] |   |     |   |   |   |   |  |

SFR Address: 0xDA Default: 0b000000000

DPXR is used to replace P2[7:0] for high byte of XRAM address bit[15:8] for "MOVX, @Ri" instructions only if DPXREN=1.

MXAX MOVX Extended Address Register R/W

| Bit | 7 | 6         | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-----|---|-----------|---|---|---|---|---|---|--|--|

| RD  |   | MXAX[7:0] |   |   |   |   |   |   |  |  |

| WR  |   | MXAX[7:0] |   |   |   |   |   |   |  |  |

SFR Address: 0xEA Default: 0b00000000

MXAX is used to provide top 8-bit address for "MOVX @Ri" instructions only. MXAX does not affect other MOVX instructions.

When accessing XRAM using "MOVX, @DPTR" instruction, the address of XRAM access is formed by DPHi:DPLi depending on which data pointer is selected. Another form of MOVX instruction is "MOVX, @Ri". This instruction provides an efficient programming method to move content within a 256-byte data block. In "@RI" instruction, the XRAM address [15:8] can be derived from two sources. If ACON.DPXREN = 0, the high order address [15:8] is from P2 (0xA0), if ACON.DPXREN = 1, the high order address is from DPXR (0xDA) register.

The maximum addressing space of XRAM is up to 16MB thus requiring 24-bit address. For "MOVX, @DPTR", the XRAMADDR [23:16] is from either DPX (0x93) or DPX1 (0x95) depending on which data pointer is selected. For "MOVX, @Ri", the XRAMUADDR [23:16] is from MXAX (0xEA) register.

#### **Dual Data Pointers And MOVX Operations**

In standard 8051, there is only one data pointers DPH:DPL to perform MOVX. The enhanced CPU provides 2<sup>nd</sup> data pointer DPH1:DPL1 to speed up the movement, or copying of data block. The active DPTR is selected by setting DPS (Data Pointer Select) register. Through the control DPS, efficient programming can be achieved.

| DPS | Data | Pointer Selec | t   | R/W |   |   |   |     |

|-----|------|---------------|-----|-----|---|---|---|-----|

| Bit | 7    | 6             | 5   | 4   | 3 | 2 | 1 | 0   |

| RD  | ID1  | ID0           | TSL | -   | - | - | - | SEL |

| WR  | ID1  | ID0           | TSL | -   | - | - | - | SEL |

SFR Address: 0x86 Default: 0b00000000

ID[1:0] Define the operation of Increment Instruction of DPTR, "INC DPTR". Standard 8051 only have increment DPTR instruction. ID[1:0] changes the definitions of "INC DPTR" instruction and allows flexible modifications of DPTR when "INC DPTR" instructions is executed.

| ID1 | ID0 | SEL=0    | SEL=1     |

|-----|-----|----------|-----------|

| 0   | 0   | INC DPTR | INC DPTR1 |

| 0   | 1   | DEC DPTR | INC DPTR1 |

| 1   | 0   | INC DPTR | DEC DPTR1 |

| 1   | 1   | DEC DPTR | DEC DPTR1 |

TSL

Enable toggling selection of DPTR selection. When this bit is set, the selection of DPTR is toggled when DPTR is used in an instruction and executed.

SEL

DPTR selection bit. Set to select DPTR1, and clear to select DPTR. SEL is also affected by the state of ID[1:0] and TSL after DPTR is used in an instruction. When read, SEL reflects the current selection of command.

| DPL | Data Pointer | Low      | R/W |   |   |   |   |   |  |

|-----|--------------|----------|-----|---|---|---|---|---|--|

| Bit | 7            | 6        | 5   | 4 | 3 | 2 | 1 | 0 |  |

| RD  |              | DPL[7:0] |     |   |   |   |   |   |  |

| WR  |              | DPL[7:0] |     |   |   |   |   |   |  |

SFR Address: 0x82 Default: 0b00000000

DPL register holds the low byte of data pointer, DPTR.

DPH **Data Pointer High** R/W

| Bit | 7 | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-----|---|----------|---|---|---|---|---|---|--|--|

| RD  |   | DPH[7:0] |   |   |   |   |   |   |  |  |

| WR  |   | DPH[7:0] |   |   |   |   |   |   |  |  |

SFR Address: 0x83 Default: 0b00000000

DPH register holds the high byte of data pointer, DPTR.

**DPL1** Extended Data Pointer Low R/W

| Bit | 7 | 6         | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-----|---|-----------|---|---|---|---|---|---|--|

| RD  |   | DPL1[7:0] |   |   |   |   |   |   |  |

| WR  |   | DPL1[7:0] |   |   |   |   |   |   |  |

SFR Address: 0x84 Default: 0b00000000

DPL1 register holds the low byte of extended data pointer 1, DPTR1.

DPH1 Extended Data Pointer High

| <u> </u> | Exteriaca Ba | ta i Oilitoi ili | j |        |      |   |   |   |  |

|----------|--------------|------------------|---|--------|------|---|---|---|--|

| Bit      | 7            | 6                | 5 | 4      | 3    | 2 | 1 | 0 |  |

| RD       |              | DPH1[7:0]        |   |        |      |   |   |   |  |

| WR       |              |                  |   | DPH1[7 | 7:0] |   |   |   |  |

SFR Address: 0x85 Default: 0b00000000

DPH1 register holds the high byte of extended data pointer 1, DPTR1.

| DPX           | Data Pointer Top    | R/W  |

|---------------|---------------------|------|

| <b>D</b> : /\ | Data i Gilitor i Op | 1471 |

|    |    |          | · |   |   | ı | 1 |   |   |  |

|----|----|----------|---|---|---|---|---|---|---|--|

| Bi | it | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| RI | D  | DPX[7:0] |   |   |   |   |   |   |   |  |

| W  | R  | DPX[7:0] |   |   |   |   |   |   |   |  |

SFR Address: 0x93 Default: 0b00000000

DPX is used to provide top 8-bit address of DPTR when address above 64KB. The lower 16-bit address is formed by DPH and DPL.DPX is not affected in Large mode, and will form full 24-bit address in Flat mode, meaning auto increment and decrement when DPTR is changed. Since IS32LT3183A only has on-chip data space, DPX value has no effect.

| Bit | 7         | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-----|-----------|---|---|---|---|---|---|---|--|

| RD  | DPX1[7:0] |   |   |   |   |   |   |   |  |

| WR  | DPX1[7:0] |   |   |   |   |   |   |   |  |

SFR Address: 0x95 Default: 0b000000000

DPX1 is used to provide top 8-bit address of DPTR when address above 64KB. The lower 16-bit address is formed by DPH1 and DP1L.DPX1 is not affected in Large mode, and will form full 24-bit address in Flat mode, meaning auto increment and decrement when DPTR is changed. Since 3183A only has on-chip data space, DPX1 value has no effect.

#### **INTERRUPT SYSTEM**

The CPU implements an enhanced Interrupt Control that allows total 15 Interrupt sources and each with two programmable priority levels. The Interrupts are sampled at rising edge of SYSCLK. If Interrupts are present and enabled, the CPU enters Interrupt service routine by vectoring to the highest priority Interrupt. Of the 15 Interrupt sources, 7 of them are from CPU internal integrated peripherals, 6 of them are for on-chip external peripherals, and 2 of them are used for external pin Interrupt expansion. When an Interrupt is shared, the Interrupt service routine must determine which source is requesting the Interrupt by examining the corresponding Interrupt flags of sharing peripherals.

The following table shows the Interrupt sources and corresponding Interrupt vectors. The Flag Reset column shows whether the corresponding Interrupt flag is cleared by hardware (self-cleared) or software. Please note the software can only clear the Interrupt flag but not set the Interrupt flag. The Natural Priority column shows the inherent priority if more than one Interrupts are assigned to the same priority level. Please note that the Interrupts assigned with higher priority levels always get serviced first compared with Interrupts assigned with lower priority levels regardless of the natural priority sequence.

| Interrupt | Peripheral Source Description      | Vectors<br>IVECSEL=0/1 | FLAG RESET | Natural Priority |

|-----------|------------------------------------|------------------------|------------|------------------|

| PINT0     | Expanded Pin INT0.x                | 0x0003/0x7003          | Software   | 1                |

| TF0       | Timer 0                            | 0x000B/0x700B          | Hardware   | 2                |

| PINT1     | Expanded Pin INT1.x                | 0x0013/0x7013          | Software   | 3                |

| TF1       | Timer 1                            | 0x001B/0x701B          | Hardware   | 4                |

| TF2       | Timer 2                            | 0x002B/0x702B          | Software   | 6                |

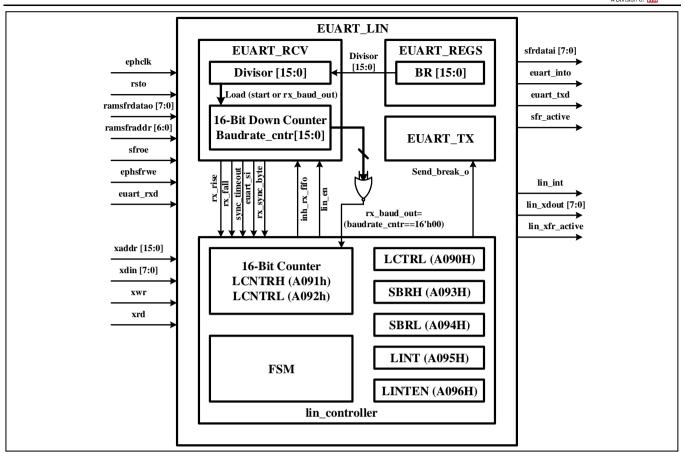

| TI2/RI2   | EUART2/LIN/LIN_FAULT               | 0x0033/0x7033          | Software   | 7                |

| I2CM      | I <sup>2</sup> C Master            | 0x003B/0x703B          | Software   | 8                |

| INT2      | PWMH/HV Fault                      | 0x0043/0x7043          | Software   | 9                |

| INT3      | Power Supply and Thermal Shut Down | 0x004B/0x704B          | Software   | 10               |

| INT4      | ADC                                | 0x0053/0x7053          | Software   | 11               |

| WDIF      | Watchdog                           | 0x005B/0x705B          | Software   | 12               |

| INT7      | SPI/ECC                            | 0x006B/0x706B          | Software   | 14               |

| INT8      | T3/T4/T5                           | 0x0073/0x7073          | Software   | 15               |

The Interrupt related registers are listed in the following. Each Interrupt can be individually enabled or disabled by setting or clearing corresponding bits in IE, EXIE and integrated peripherals' control registers.

| <u>IE</u> | Interrupt Enable Register |     | F   | R/W |     |         |     |         |

|-----------|---------------------------|-----|-----|-----|-----|---------|-----|---------|

| Bit       | 7                         | 6   | 5   | 4   | 3   | 2       | 1   | 0       |

| RD        | EA                        | ES2 | ET2 | -   | ET1 | PINT1EN | ET0 | PINT0EN |

| WR        | EA                        | ES2 | ET2 | -   | ET1 | PINT1EN | ET0 | PINT0EN |

SFR Address: 0xA8 Default: 0b00000000

EA Global Interrupt Enable bit.

ES2 LIN-capable16550-like UART2 Interrupt Enable bit.

ET2 Timer 2 Interrupt Enable bit.

ET1 Timer 1 Interrupt Enable bit.

PINT1EN PINT1.x Interrupt Enable bit.

ET0 Timer 0 Interrupt Enable bit.

PINT0EN Pin PINT0.x Interrupt Enable bit.

EXIE Extended Interrupt Enable Register R/W

| Bit | 7     | 6     | 5     | 4    | 3     | 2     | 1     | 0     |

|-----|-------|-------|-------|------|-------|-------|-------|-------|

| RD  | EINT8 | EINT7 | EINT6 | EWDI | EINT4 | EINT3 | EINT2 | EI2CM |

| WR  | EINT8 | EINT7 | EINT6 | EWDI | EINT4 | EINT3 | EINT2 | EI2CM |

SFR Address: 0xE8 Default: 0b000000000

EINT8 Timer 3/4/5 Interrupt Enable bit.

EINT7 SPI, ECC Interrupt Enable bit.

EWD1 Watchdog Timer Interrupt Enable bit.

EINT4 ADC Interrupt Enable bit.

EINT3 Power Supply and Thermal Shut Down Interrupt Enable bit.

EINT2 PWMH and HV Fault Detection Interrupt Enable bit.

EI2CM I2C Master Interrupt Enable bit.

Each Interrupt can be individually assigned to either high or low. When the corresponding bit is set to 1, it indicates it is of high priority.

| IP | Interrupt Priority Register | R/W |

|----|-----------------------------|-----|

|    |                             |     |

| Bit | 7 | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|---|-----|-----|-----|-----|-----|-----|-----|

| RD  | - | PS2 | PT2 | PS0 | PT1 | PX1 | PT0 | PX0 |

| WR  | - | PS2 | PT2 | PS0 | PT1 | PX1 | PT0 | PX0 |

SFR Address: 0xB8 Default: 0b00000000

PS2 LIN-capable 16550-like UART2 Priority bit.

PT2 Timer 2 Priority bit. PT1 Timer 1 Priority bit.

PX1 Pin Interrupt INT1 Priority bit.

PT0 Timer 0 Priority bit.

PX0 Pin Interrupt INT0 Priority bit.

#### **EXIP** Extended Interrupt Priority Register R/W

| Bit | 7     | 6     | 5     | 4    | 3     | 2     | 1     | 0     |

|-----|-------|-------|-------|------|-------|-------|-------|-------|

| RD  | EINT8 | EINT7 | EINT6 | EWDI | EINT4 | EINT3 | EINT2 | EI2CM |

| WR  | EINT8 | EINT7 | EINT6 | EWDI | EINT4 | EINT3 | EINT2 | EI2CM |

SFR Address: 0xF8 Default: 0b00000000

EINT8 INT8 Timer 3/4/5 Priority bit.

EINT7 INT7 SPI/ECC Priority bit.

EWDI Watchdog Priority bit.

EINT4 INT4 ADC Priority bit.

EINT3 INT3 Power Supply and Thermal Shut Down Priority bit.

EINT2 INT2 PWMH and HV Fault Detection Priority bit.

EI2CM I2C Master Priority bit.

EXIF Extended Interrupt Flag R/W

| Bit | 7     | 6     | 5     | 4 | 3     | 2     | 1     | 0      |

|-----|-------|-------|-------|---|-------|-------|-------|--------|

| RD  | INT8F | INT7F | INT6F | - | INT4F | INT3F | INT2F | I2CMIF |

| WR  | -     | -     | -     | - | -     | -     | -     | I2CMIF |

SFR Address: 0x91 Default: 0b00000000

INT8F INT8 Timer 3/4/5 Interrupt Flag bit INT7F INT7 SPI, ECC Interrupt Flag bit INT4F INT4 ADC Interrupt Flag bit

INT3F INT3 Power Supply and Thermal Shut Down Interrupt Flag bit

INT2F INT2 PWMH and HV Fault Detection Interrupt Flag bit

12CMIF I2C Master Interrupt Flag bit. This bit must be cleared by software

Writing to INT2F to INT8F has no effect.

The Interrupt flag of internal peripherals are stored in the corresponding flag registers in the peripheral and EXIF registers. These peripherals include T0, T1, T2, and WDT. Therefore, to clear the Interrupt flags, the software needs to clear the corresponding flags located in the peripherals (for T0, T1, and T2, and WDT). For I2CM, the Interrupt flag is located in the EXIF register bit I2CMIF. This needs to be cleared by software.

INT2 to INT8 are used to connect to the external peripherals. INT2F to INT8F are direct equivalents of the Interrupt flags from the corresponding peripherals. These peripherals include ECC, I2Cs, PWM, ADC, etc.

HVIO are used for external GPIO pin Interrupts. All GPIO pin can be enabled to generate the HVIO depending on its IO configured registers setting. Each GPIO pin also contains the rising/falling edge detections and either or both edges can be used for Interrupt triggering. The same signaling can be used for generating wake-up.

TCON R/W

| Bit | 7   | 6   | 5   | 4   | 3      | 2 | 1      | 0 |

|-----|-----|-----|-----|-----|--------|---|--------|---|

| RD  | TF1 | TR1 | TF0 | TR0 | PINT1F | - | PINT0F | - |

| WR  | -   | TR1 | -   | TR0 | PINT1F | - | PINT0F | - |

SFR Address: 0x88 Default: 0b00000000

TF1 Timer 1 Interrupt Flag bit. TF1 is cleared by hardware when entering the Interrupt routine.

TR1 Timer 1 Run Control bit. Set to enable Timer 1.

TF0 Timer 0 Interrupt Flag. TF0 is cleared by hardware when entering the Interrupt routine.

TR0 Timer 0 Run Control bit. Set to enable Timer 0.

PINT1F Pin INT1 Interrupt Flag bit.

PINT0F Pin INT0 Interrupt Flag bit.

#### **REGISTER ACCESS CONTROL**

One important aspect of the embedded MCU is its reliable operations under a harsh environment. Many system failures result from the accidental loss of data or changes of critical registers that may lead to catastrophic effects. The CPU provides several protection mechanisms, which are described in this section.

| TA | Time Access A Control Reg | ister2 WO |

|----|---------------------------|-----------|

|    |                           |           |

|     |   | no Accesso A Control Register 1 |   |   |   |   |   |        |  |  |

|-----|---|---------------------------------|---|---|---|---|---|--------|--|--|

| Bit | 7 | 6                               | 5 | 4 | 3 | 2 | 1 | 0      |  |  |

| RD  | - | -                               | - | - | - | - | - | TASTAT |  |  |

| WR  |   | TA Register                     |   |   |   |   |   |        |  |  |

SFR Address: 0xC7 Default: 0b00000000

TA access control emulates a ticket that must be purchased before modifying a critical register. To modify or write into a TA protected register, TA must be accessed in a predefined sequence to obtain the ticket. The ticket is used when an intended modification operation is done to the TA protected register. To obtain the next access a new ticket must be obtained again by performing the same predefined sequence on TA. TA does not limit the read access of the TA protect registers. The TA protected register includes WDCON (0xD8), MCON (0xC6), and ACON (0x9D) registers. The following predefined sequence is required to modify the content of MCON.

MOV TA, #0xAA;

MOV TA, #0x55;

MOV MCON, #0x01;

Once the access is granted, there is no time limitation of the access. The access is voided if any operation is performed in TA address. When read, the bit of TA indicates whether TA is locked or not (1 indicates "unlock" and 0 indicates "lock").

TB Time Access B Control Register2 R/W

| Bit | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0      |

|-----|-------------|---|---|---|---|---|---|--------|

| RD  | -           | - | - | - | - | - | - | TBSTAT |

| WR  | TB Register |   |   |   |   |   |   |        |

SFR Address: 0xC9 Default: 0b00000000

TB access control functions are similar to TA control, except the ticket is for multiple uses with a time limit. Once access is granted, the access is open for 256 clock periods and then expires. The software can also read TB address to obtain the current TB status. The TB protected registers include two SFR registers, CKSEL (0x8F) and WKMASK (0x9F), and twelve XFR registers lodging FLSHCMD (0xA020), FLSHDAT (0xA021), FLSHADL (0xA023), FLSHADH (0xA022), ISPCLKF (0xA024), FLSHSPRT (0xA012), FLSHCPRT (0xA013). To modify registers with TB protection, the following procedure must be performed.

MOV TB, #0xAA

MOV TB, #0x55

This action creates a timed window of 256 SYSCLK periods to allow write access of these TB protected registers. If any above-mentioned sequences are repeated before the 128 cycles expires, a new 128 cycles is extended. The current 256 cycles can be terminated immediately by writing #0x00 to TB registers, such as

MOV TB, #0x00

It is recommended to terminate the TB access window once the user program finishes the modifications of TB protected registers.

Because TA and TB are critical reassurance of the reliable operation of the MCU that prevents accidental hazardous uncontrollable modifications of critical registers, the operation of these two registers should bear extreme cautions. It is strongly advised that these two registers should be turned on only when needed.Both registers use synchronous CPU clock, therefore it is imperative that any running tasks of TA and TB should be terminated before entering Idle mode or Stop mode. Both modes turn off the CPU clock and if TA and TB are enabled, they stay enabled until the CPU clock resumes thus may create vulnerabilities for critical registers.

Another reliability concern of embedded Flash MCU is that the important content on the Flash can be accidentally erased. This concern is addressed by the content protection in the Flash controller.

#### **CLOCK CONTROL AND POWER MANAGEMENT MODES**

This section describes the clock control and power saving modes of the CPU and its integrated peripherals. The settings are controlled by PCON (0x87) and PMR (0xC4) registers. The register description is defined as following.

| PCON |   |   |   | R/W |   |       |      | _    |

|------|---|---|---|-----|---|-------|------|------|

| Bit  | 7 | 6 | 5 | 4   | 3 | 2     | 1    | 0    |

| RD   | - | - | - | -   | - | -     | -    | -    |

| WR   | - | - | - | -   | - | SLEEP | STOP | IDLE |

SFR Address: 0x87 Default: 0b00000000

SLEEP

Sleep mode control bit. When this bit and the STOP bit are set to 1, the clock of the CPU and all peripherals is disabled and enters Sleep mode. The Sleep mode exits when non-clocked Interrupts or resets occur. Upon exiting Sleep mode. SLEEP bit and STOP bit in PCON is automatically cleared. In terms of power consumption, the following relationship applies: Idle mode > Stop mode > Sleep mode. Sleep mode is the same as Stop mode, except it also turns off the band gap and the regulator. It uses a very low power back-up regulator (< 5µA). When waking up from Sleep mode, it takes longer time (< 64 IOSC clock cycles, compared with Stop mode) because the regulator requires more time to stabilize.

**STOP**

Stop mode control bit. The clock of the CPU and all peripherals is disabled and enters Stop mode if the SLEEP bit is in the reset state. The Stop mode can only be terminated by nonclocked Interrupts or resets. Upon exiting Stop mode, STOP bit in PCON is automatically

**IDLE**

Idle mode control bit. If the IDLE bit is set, the system goes into Idle mode. In Idle mode, CPU clock becomes inactive and the CPU and its integrated peripherals such as WDT, T0/T1/T2, and UART0 are reset. But the clocks of external peripherals and CPU like PCA, ADC, LINcapable16550-like UART2, SPI, T3, I2C slave and the others are still active. This allows the Interrupts generated by these peripherals and external Interrupts to wake the CPU. The exit mechanism of Idle mode is the same as Stop mode. IDLE bit is automatically cleared at the exit of the Idle mode.

| PMR |     |     |     | R/W |   |   |   |   |

|-----|-----|-----|-----|-----|---|---|---|---|

| Bit | 7   | 6   | 5   | 4   | 3 | 2 | 1 | 0 |

| RD  | CD1 | CD0 | SWB | -   | - | - | - | - |

| WR  | -   | CD0 | SWB | -   | - | - | - | - |

SFR Address: 0xC4 Default: 0b010xxxxx

CD1, CD0

Clock Divider Control bit. These two bits control the entry of PMM mode. When CD0=1, and CD1=0, full speed operation is in effect. When CD0=1, and CD1=1, the CPU enters PMM mode where CPU and its integrated peripherals operate at a clock rate divided by 257. Note that in PMM mode, all integrated peripherals such as UART0, LIN-capable 16550-like UART2, WDT, and T0/T1/T2 run at this reduced rate, thus may not function properly. All external peripherals to CPU still operate at full speed in PMM mode.

NOTE:

CD1 is internally hardwired to 0. This implementation does not support PMM mode.

**SWB**

Switch Back Control bit. Setting this bit allows the actions to occur in integrated peripherals to

automatically switch back to normal operation mode.