# RENESAS

## ISL15110 PLC MIMO Line Driver

# DATASHEET

FN8282 Rev 1.00 Apr 6, 2018

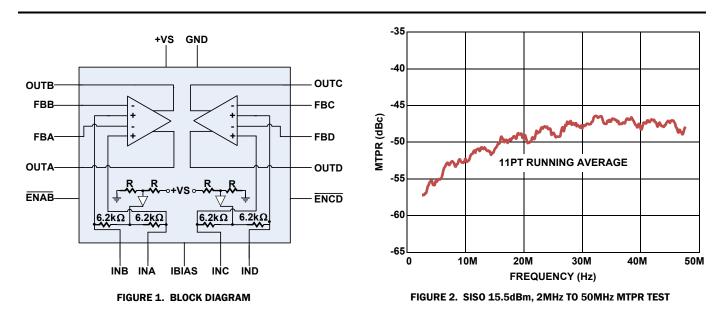

The <u>ISL15110</u> is a dual port differential line driver developed for Power Line Communication (PLC) Multi Input Multi Output (MIMO) applications. MIMO PLC requires transmission on one or two pairs of Phase, Neutral, and Ground wires. The device is designed to drive heavy line loads while maintaining a high level of linearity required in OFDM PLC modem links. With 15.5dBm of total MIMO transmit signal power (12.5dBm per each pair) into a 50 $\Omega$  line load, the drivers deliver -50dB average MTPR distortion across the output spectrum.

Each of the two differential drivers has a control pin to enable and disable its differential output. These controls allow for independent TDM operation of the two differential drivers, as required in ITU-T MIMO G.hn and related standard based PLC applications. In disable mode, the line driver output maintains a high impedance characteristic to preserve TDM receive signal integrity.

The ISL15110 includes an external IBIAS pin for quiescent current flexibility. Grounding the pin in single supply designs gives the nominal currents in the "Electrical Specifications" table starting on page 5, while inserting a resistor from pin to ground can be used to scale down the quiescent current for both ports.

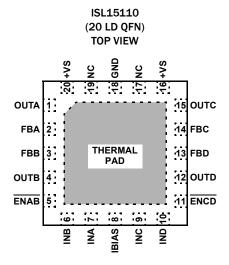

The ISL15110 is available in the thermally-enhanced 20 Ld QFN and is specified for operation across the full -40  $^{\circ}$ C to +85  $^{\circ}$ C temperature range.

## **Related Literature**

For a full list of related documents, visit our website

• ISL15110 product page

### **Features**

- Dual differential drivers

- 50MHz broadband PLC G.hn

- Enable/disable control pins for TDM operation

- -50dBc average MTPR distortion

- Single supply +12V nominal operation

- · Enhanced surge current handling capability

- Thermally enhanced 20 Ld QFN package

- Enable port control voltage <0.7V

- Disable port control voltage >1.7V

### Applications

- · Home networking over power lines

- ITU-T G.hn (G.9963) MIMO PLC

## **Typical Application Circuit**

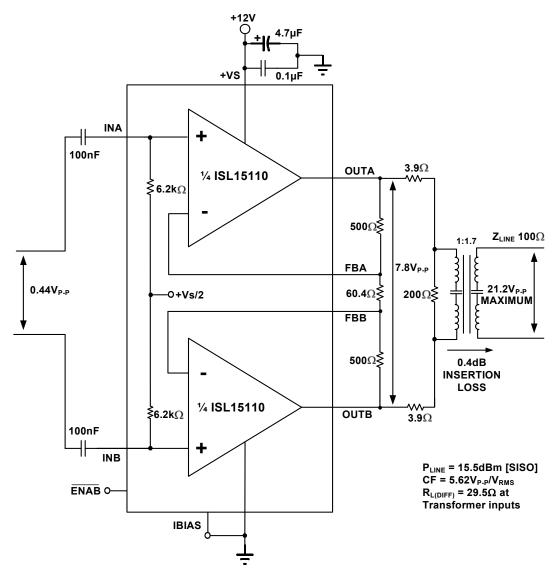

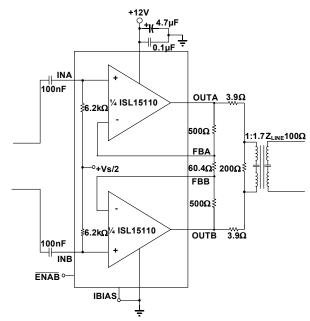

FIGURE 3. TYPICAL APPLICATION CIRCUIT (1 of 2 PORTS)

## **Pin Configuration**

THERMAL PAD CONNECTS TO GND

## **Pin Descriptions**

| PIN NUMBER | PIN NAME    | FUNCTION                                |

|------------|-------------|-----------------------------------------|

| 0          | THERMAL PAD | Connects to GND                         |

| 1          | OUTA        | Amplifier A output                      |

| 2          | FBA         | Amplifier A inverting input             |

| 3          | FBB         | Amplifier B inverting input             |

| 4          | OUTB        | Amplifier B output                      |

| 5          | ENAB        | Port 1 enable/disable control           |

| 6          | INB         | Amplifier B non-inverting input         |

| 7          | INA         | Amplifier A non-inverting input         |

| 8          | IBIAS       | Ports 1 and 2 quiescent current control |

| 9          | INC         | Amplifier C non-inverting input         |

| 10         | IND         | Amplifier D non-inverting input         |

| 11         | ENCD        | Port 2 enable/disable control           |

| 12         | OUTD        | Amplifier D output                      |

| 13         | FBD         | Amplifier D inverting input             |

| 14         | FBC         | Amplifier C inverting input             |

| 15         | OUTC        | Amplifier C output                      |

| 16, 20     | +VS         | Voltage supply                          |

| 17, 19     | NC          | No connect                              |

| 18         | GND         | Ground                                  |

## **Ordering Information**

| PART NUMBER<br>( <u>Notes 2, 3</u> ) | PART<br>MARKING | TEMP RANGE<br>(°C) | TAPE AND REEL<br>(UNITS) ( <u>Note 1</u> ) | PACKAGE<br>(RoHS COMPLIANT) | PKG.<br>DWG. # |

|--------------------------------------|-----------------|--------------------|--------------------------------------------|-----------------------------|----------------|

| ISL15110IRZ                          | 151 10IRZ       | -40 to +85         | -                                          | 20 Ld QFN                   | L20.4x4C       |

| ISL15110IRZ-T7                       | 151 10IRZ       | -40 to +85         | 1k                                         | 20 Ld QFN                   | L20.4x4C       |

| ISL15110IRZ-T13                      | 151 10IRZ       | -40 to +85         | 6k                                         | 20 Ld QFN                   | L20.4x4C       |

NOTES:

1. Refer to TB347 for details about reel specifications.

2. These Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

3. For Moisture Sensitivity Level (MSL), refer to the ISL15110 product information page. For more information about MSL, refer to TB363.

#### Absolute Maximum Ratings (T<sub>A</sub> = +25°C)

| V <sub>S</sub> + Voltage to GND<br>Driver V <sub>IN</sub> + Voltage<br>V <sub>CM</sub> Voltage to GND | $\dots$ .GND to V <sub>S</sub> + |

|-------------------------------------------------------------------------------------------------------|----------------------------------|

| Current Into Any input                                                                                | •                                |

| Continuous Output Current for Long Term Reliability                                                   |                                  |

| ESD Rating                                                                                            |                                  |

| Human Body Model (Tested per JESD22-A114F)                                                            | 4kV                              |

| Machine Model (Tested per JESD22-A115C)                                                               |                                  |

| Charge Device Model (Tested per JESD22-C101E)                                                         | <b>1</b> .5kV                    |

|                                                                                                       |                                  |

### **Thermal Information**

| Thermal Resistance (Typical)              | θ <b>j</b> (°C/W)  | θ <b>JC</b> (°C/W)     |

|-------------------------------------------|--------------------|------------------------|

| 20 Ld QFN Package ( <u>Notes 4, 5</u> )   | 43                 | 6.5                    |

| Thermal Characteristics (Typical)         | ψ <b>JI</b> (°C/W) | Ψ <sub>JB</sub> (°C/W) |

| 20 Ld QFN Package                         | 4                  | 18                     |

| Maximum Junction Temperature (Plastic Pac | kage)              | +150°C                 |

| Power Dissipation                         |                    | see <u>page 14</u>     |

| Storage Temperature Range                 |                    | 40°C to +150°C         |

| Pb-Free Reflow Profile                    |                    | see <u>TB493</u>       |

### **Operating Conditions**

| Ambient Temperature Range  | 40°C to +85°C  |

|----------------------------|----------------|

| Junction Temperature Range | 40°C to +150°C |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 4.  $\theta_{JA}$  is measured in free air with the component mounted on a high-effective thermal conductivity test board with "direct attach" features. See TB379.

- 5. For  $\theta_{JC}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

## **Electrical Specifications** $V_S = +12V$ , Gain = 17.6V/V, $R_f = 500\Omega$ , $R_{L-DIFF} = 29.5\Omega$ differential, $I_{BIAS} = GND$ , $T_A = +25$ °C. Ports are tested separately unless otherwise indicated (see Figure 3).

| PARAMETER                                                                               | SYMBOL               | CONDITIONS                                                                                                                                | MIN<br>(Note 6) | ТҮР  | MAX<br>(Note 6) | UNITS  |

|-----------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|-----------------|--------|

| AC PERFORMANCE                                                                          | U.                   |                                                                                                                                           | 1               |      |                 |        |

| -3dB Bandwidth                                                                          | BW                   | $A_V = 12$ dB, [5V/V]                                                                                                                     |                 | 120  |                 | MHz    |

|                                                                                         |                      | A <sub>V</sub> = 25dB, [17.6V/V]                                                                                                          |                 | 80   |                 | MHz    |

| Passband Ripple (f < 50MHz)                                                             | RIP                  |                                                                                                                                           |                 | 1    |                 | dB     |

| Slew Rate                                                                               | SR                   | Differential V <sub>OUT</sub> from -6V to +6V                                                                                             |                 | 1600 |                 | V/µs   |

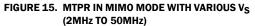

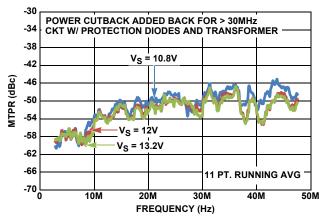

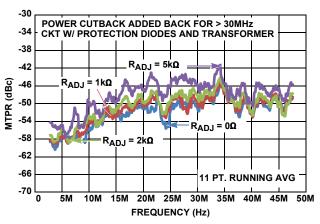

| Multi-Tone Power Ratio<br>(Power Cutback Added Back For<br>Frequency > 30MHz)           | MTPR                 | 2MHz to 50MHz, 25kHz Tone Spacing,<br>$P_{LINE} = 15.5dBm$ , CF = 15dB, V <sub>S</sub> = 10.8V,<br>$T_A = 0$ °C to +85 °C                 | -43             |      |                 | dBc    |

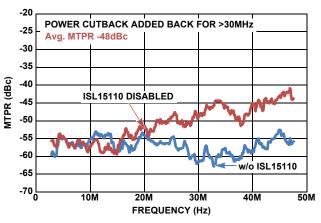

| Off State Multi-Tone Power Ratio<br>(Power Cutback Added Back For<br>Frequency > 30MHz) | MTPR OFF             | 2MHz to 50MHz, 25kHz Tone Spacing,<br>P <sub>LINE</sub> = 15.5dBm, CF = 15dB                                                              |                 | -48  |                 | dBc    |

| Non-Inverting Input Voltage Noise                                                       | eN                   | f = 1MHz                                                                                                                                  |                 | 6    |                 | nV/√Hz |

| Non-Inverting Input Current Noise                                                       | iN+                  | f = 1MHz                                                                                                                                  |                 | 13   |                 | pA/√Hz |

| Inverting Input Current Noise                                                           | iN-                  | f = 1MHz                                                                                                                                  |                 | 50   |                 | pA/√Hz |

| POWER CONTROL FEATURES                                                                  |                      |                                                                                                                                           |                 |      |                 |        |

| Logic High Current for ENAB, ENCD                                                       | IIHAB, IIHCD         | ENAB, ENCD = 3.3V                                                                                                                         | 70              | 98   | 115             | μA     |

| Logic Low Current for ENAB, ENCD                                                        | IILAB, IILCD         | ENAB, ENCD = OV                                                                                                                           | -5              | -2   | 0               | μA     |

| Logic High Voltage for ENAB, ENCD                                                       | VIHAB, VIHCD         | ENAB and ENCD Inputs [Port Disable]                                                                                                       | 1.7             |      |                 | v      |

| Logic Low Voltage for ENAB, ENCD                                                        | VILAB, VILCD         | ENAB and ENCD Inputs [Port Enable]                                                                                                        |                 |      | 0.7             | v      |

| SUPPLY CHARACTERISTICS                                                                  |                      |                                                                                                                                           |                 |      |                 |        |

| Supply Voltage Range                                                                    | ٧ <sub>S</sub>       | Single Supply                                                                                                                             | 10.8            | 12   | 13.2            | v      |

| Supply Current - MIMO [Dual Port Operation]                                             | I <sub>S</sub> -MIMO | ENAB, ENCD = OV                                                                                                                           | 44.5            | 50   | 56.5            | mA     |

| Supply Current - SISO [Single Port Operation]                                           | I <sub>S</sub> -SISO | $\overline{\text{ENAB}}$ = 3.3V and $\overline{\text{ENCD}}$ = 0V or $\overline{\text{ENAB}}$ = 0V<br>and $\overline{\text{ENCD}}$ = 3.3V | 26.5            | 30   | 33              | mA     |

**Electrical Specifications**  $V_S = +12V$ , Gain = 17.6V/V,  $R_f = 500\Omega$ ,  $R_{L-DIFF} = 29.5\Omega$  differential,  $I_{BIAS} = GND$ ,  $T_A = +25$ °C. Ports are tested separately unless otherwise indicated (see Figure 3). (Continued)

| PARAMETER                                                            | SYMBOL                       | CONDITIONS                                                                                                                                      | MIN<br>(Note 6) | ТҮР  | MAX<br>(Note 6) | UNITS |

|----------------------------------------------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|-----------------|-------|

| Supply Current - Power Down [For Two Ports]                          | IS OFF                       | ENAB, ENCD = 3.3V                                                                                                                               | 7.4             | 8.0  | 9.5             | mA    |

| Maximum Power Consumption - MIMO<br>[Dual Port Operation]            | P-MIMO                       | $\overline{\text{ENAB}} = \overline{\text{ENCD}} = 0$ V, P <sub>L</sub> = 12.5dBm per channel                                                   |                 | 1040 | 1090            | mW    |

|                                                                      |                              | V <sub>S</sub> = 13.2V                                                                                                                          |                 | 1145 | 1200            | mW    |

| Maximum Power Consumption - SISO<br>[Single Port Operation]          | P-SIS0                       | $\overline{ENAB} = 0V, \overline{ENCD} = 3.3V, P_{LA} = 15.5dBm \text{ or}$<br>$\overline{ENAB} = 3.3V, \overline{ENCD} = 0V, P_{LB} = 15.5dBm$ |                 | 590  | 720             | mW    |

|                                                                      |                              | V <sub>S</sub> = 13.2V                                                                                                                          |                 | 650  | 790             | mW    |

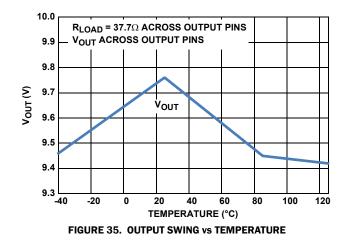

| OUTPUT CHARACTERISTICS                                               |                              |                                                                                                                                                 |                 |      |                 |       |

| Loaded Output Swing (Single-ended)                                   | V <sub>OUT</sub> HI          | $R_L = 37.3\Omega$ across output pins                                                                                                           | 10.7            | 10.8 |                 | v     |

|                                                                      | V <sub>OUT</sub> LO          | $R_L = 37.3\Omega$ across output pins                                                                                                           |                 | 1.2  | 1.6             | v     |

| Output Offset Voltage Differential Mode                              | V <sub>OS-DM</sub><br>Output | (OUTA - OUTB) or (OUTC - OUTD)                                                                                                                  | -100            |      | 100             | mV    |

| Output Offset Voltage Common Mode                                    | V <sub>OS-CM</sub><br>Output | Delta to +V <sub>S</sub> /2                                                                                                                     | -75             |      | 125             | mV    |

| Output Short Circuit Current                                         | I <sub>SC</sub>              | $R_L = 0\Omega$                                                                                                                                 |                 | 2000 |                 | mA    |

| INPUT CHARACTERISTICS                                                |                              |                                                                                                                                                 | 1               | 1    | 1 1             |       |

| Input Offset Voltage Differential Mode                               | V <sub>OS-DM</sub>           | (INA - INB) or (INC - IND)                                                                                                                      | -6              | 0    | +6              | mV    |

| Input Offset Voltage Common Mode                                     | V <sub>OS-CM</sub>           | Delta to +V <sub>S</sub> /2                                                                                                                     | -50             | -18  | 0               | mV    |

| Non-Inverting Input Bias Current                                     | +IB                          |                                                                                                                                                 | -14             | -3   | +12             | μA    |

| Non-Inverting Input Bias Current Differential Mode                   | +IB <sub>DM</sub>            | $(+IB_A - +IB_B)$ or $(+IB_C - +IB_D)$                                                                                                          | -2              | 0    | +2              | μA    |

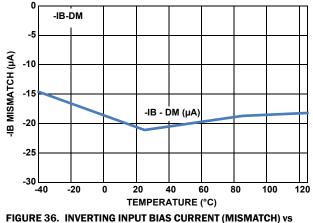

| Inverting Input Bias Current Differential Mode<br>(Mismatch)         | -IB <sub>DM</sub>            | (-IB <sub>A</sub> IB <sub>B</sub> ) or (-IB <sub>C</sub> IB <sub>D</sub> )                                                                      | -50             | ±20  | +50             | μA    |

| Common Mode Input Range at each of the 4<br>Non-Inverting Input Pins | CMIR                         | Delta to +V <sub>S</sub> /2                                                                                                                     | -3              | ±3.5 | +3              | v     |

| Common Mode Rejections for each Port                                 | CMRR                         | V <sub>CM</sub> to Differential Mode Output                                                                                                     | 48              | 60   |                 | dB    |

| $V_{CM} = -3V$ to $+3V$                                              |                              | V <sub>CM</sub> to Common Mode Output                                                                                                           | 45              | 50   |                 | dB    |

| Power Supply Rejection for each Port                                 | PSRR                         | PSRR to Differential Mode Input<br>+V <sub>S</sub> = +10.8V to +13.2V, GND = 0V, DC                                                             | 73              | 90   |                 | dB    |

|                                                                      |                              | PSRR to Common Mode Output Balanced shift in $\pm V_S$ [bipolar supply]                                                                         | 42              | 60   |                 | dB    |

| Differential Input Impedance                                         | Z <sub>IN-DIFF</sub>         |                                                                                                                                                 | 10              | 12.4 | 14              | kΩ    |

NOTE:

6. Compliance to datasheet limits is assured by one or more methods: production test, characterization, and/or design.

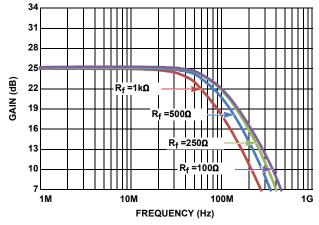

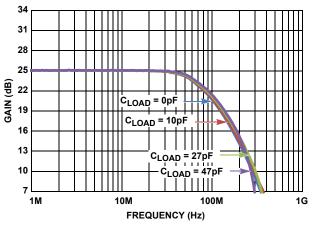

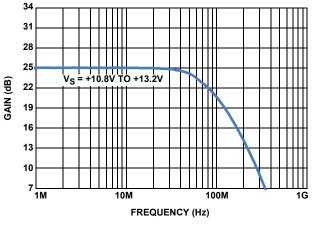

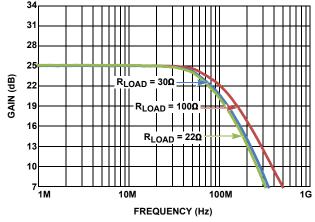

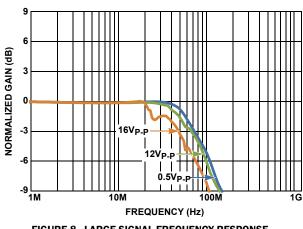

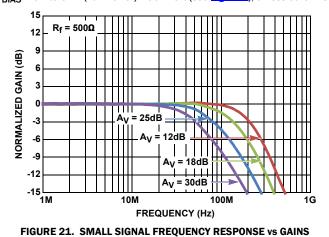

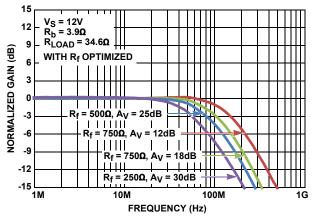

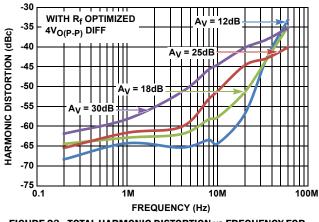

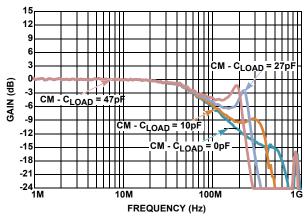

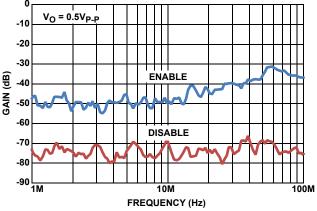

# **Typical Performance Curves** $V_{CC} = \pm 12V$ , Gain = 17.6V/V (Differential), $R_f = 500\Omega$ , $R_{LOAD} = 29.5\Omega$ , $T_A = \pm 25^{\circ}C$ , $I_{BIAS} = 0\Omega$ to GND (Full Power). Each Port (see Figure 3), unless otherwise noted.

FIGURE 4. SMALL SIGNAL FREQUENCY RESPONSE vs R<sub>f</sub>

FIGURE 5. SMALL SIGNAL FREQUENCY RESPONSE vs CLOAD

FIGURE 6. SMALL SIGNAL BW vs SUPPLY VOLTAGE

FIGURE 7. SMALL SIGNAL FREQUENCY RESPONSE vs RLOAD

FIGURE 8. LARGE SIGNAL FREQUENCY RESPONSE

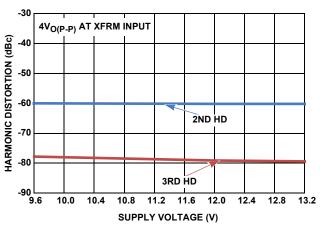

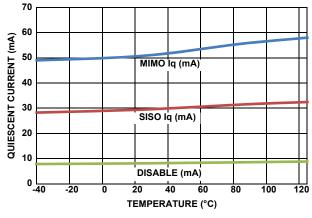

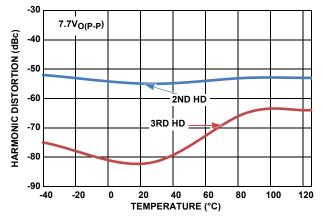

## **Typical Performance Curves** $v_{CC} = +12V$ , Gain = 17.6V/V (Differential), $R_f = 500\Omega$ , $R_{LOAD} = 29.5\Omega$ , $T_A = +25$ °C,

$I_{BIAS}$  = 0Ω to GND (Full Power). Each Port (see <u>Figure 3</u>), unless otherwise noted. (Continued)

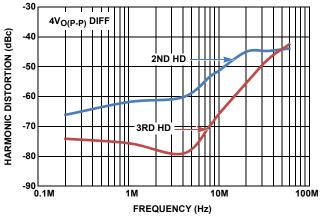

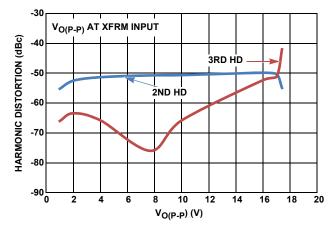

FIGURE 9. HARMONIC DISTORTION vs FREQUENCY

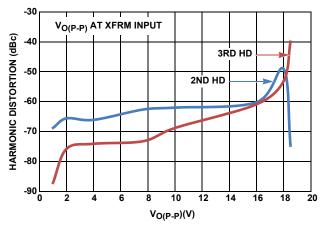

FIGURE 10. 200kHz HARMONIC DISTORTION vs OUTPUT VOLTAGE

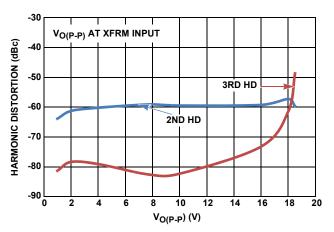

FIGURE 11. 4MHz HARMONIC DISTORTION vs OUTPUT VOLTAGE

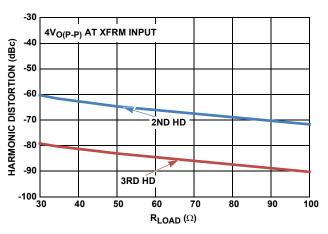

FIGURE 13. 4MHz HARMONIC DISTORTION vs RLOAD

FIGURE 12. 10MHz HARMONIC DISTORTION vs OUTPUT VOLTAGE

**Typical Performance Curves**  $v_{CC} = +12V$ , Gain = 17.6V/V (Differential),  $R_f = 500\Omega$ ,  $R_{LOAD} = 29.5\Omega$ ,  $T_A = +25$ °C,  $I_{BIAS} = 0\Omega$  to GND (Full Power). Each Port (see Figure 3), unless otherwise noted. (Continued)

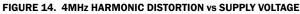

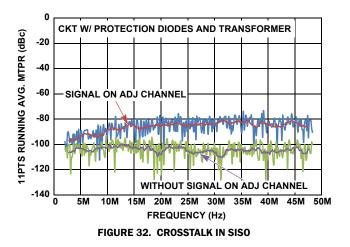

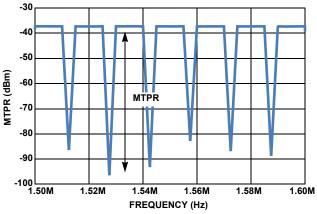

FIGURE 16. MTPR IN SISO MODE WITH VARIOUS VS (2MHz TO 50MHz)

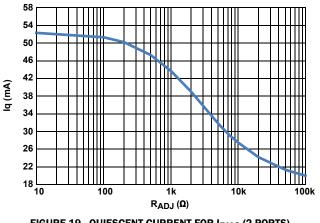

FIGURE 19. QUIESCENT CURRENT FOR IBIAS (2 PORTS)

FIGURE 18. MTPR IN SISO MODE WITH VARIOUS RADJ (2MHz TO 50MHz)

# **Typical Performance Curves** $v_{CC} = \pm 12V$ , Gain = 17.6V/V (Differential), $R_f = 500\Omega$ , $R_{LOAD} = 29.5\Omega$ , $T_A = \pm 25^{\circ}C$ , $I_{BIAS} = 0\Omega$ to GND (Full Power). Each Port (see Figure 3), unless otherwise noted. (Continued)

FIGURE 22. SMALL SIGNAL FREQUENCY RESPONSE vs GAINS

FIGURE 23. TOTAL HARMONIC DISTORTION vs FREQUENCY FOR VARIOUS GAINS

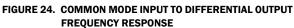

FIGURE 25. COMMON MODE SMALL SIGNAL FREQUENCY RESPONSE WITH VARIOUS  $\mathsf{C}_{\mathsf{LOADS}}$

FIGURE 26. SMALL STEP RESPONSE

# **Typical Performance Curves** $v_{CC} = +12V$ , Gain = 17.6V/V (Differential), $R_f = 500\Omega$ , $R_{LOAD} = 29.5\Omega$ , $T_A = +25$ °C, $I_{BIAS} = 0\Omega$ to GND (Full Power). Each Port (see Figure 3), unless otherwise noted. **(Continued)**

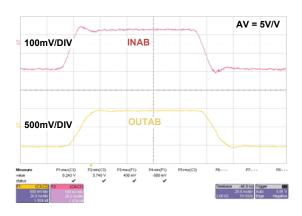

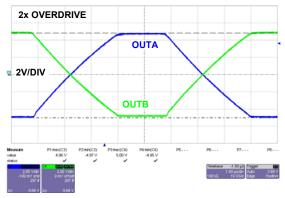

FIGURE 27. LARGE STEP RESPONSE

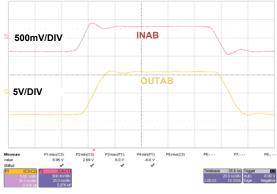

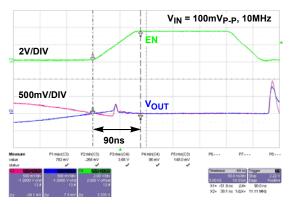

FIGURE 28. POWER ON TIME (ton)

FIGURE 29. POWER OFF TIME (t<sub>OFF</sub>)

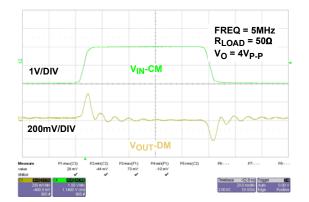

#### FIGURE 31. COMMON MODE INPUT TO DIFFERENTIAL OUTPUT STEP RESPONSE

## **Typical Performance Curves** $v_{CC} = +12V$ , Gain = 17.6V/V (Differential), $R_f = 500\Omega$ , $R_{LOAD} = 29.5\Omega$ , $T_A = +25$ °C,

$I_{BIAS} = 0\Omega$  to GND (Full Power). Each Port (see <u>Figure 3</u>), unless otherwise noted. (Continued)

FIGURE 33. QUIESCENT CURRENT vs TEMPERATURE

FIGURE 34. 4MHz HARMONIC DISTORTION vs TEMPERATURE

TEMPERATURE

## **Operation**

FIGURE 37. APPLICATION CIRCUIT (1 of 2 PORTS)

The ISL15110 consists of two pairs of Current Feedback Amplifiers (CFA): those used in power line communication and those used in (PLC) MIMO applications. The ISL15110 is well suited to the requirements of high output power, high full power bandwidth, and high output impedance in disable mode.

The AC characteristics are set by the  $500\Omega$  feedback resistors, as shown in Figure 37. The effects of increasing or decreasing the feedback resistors is shown in Figure 4. The ISL15110 shows a good flat response with smooth roll off with various feedback resistances. CFAs will generally roll off sooner with the increase in feedback resistance, and decreasing the feedback will peak the frequency response up and extend the bandwidth.

With the bandwidth fixed requirement by the feedback resistors, the gain can be adjusted by changing the 60.4 $\Omega$  in Figure 37. The Figure 37 example sets the differential gain across OUTA, OUTB to:

$$\frac{OUTA}{INA} = \frac{500}{(60.4/2)} + 1 = 17.6 \left(\frac{V}{V}\right)$$

(EQ. 1)

To get the gain to the input of the transformer in Figure 37, the attenuation of the resistor divider [ $3.9\Omega$  and ( $200\Omega$ | $34.6\Omega$ )] is added to Equation 1, in which the  $34.6\Omega$  is the input referred load of  $100\Omega$  through the turns ratio squared.

### **Input Biasing and Input Impedance**

The ISL15110 has integrated resistors at the inputs for mid rail biasing, as shown in Figures 1 and 3. The inputs require only external AC coupling capacitors. With a 100nF coupling capacitor and an input impedance of  $6.2k\Omega$  typical, the first order high pass cut off frequency is 257Hz.

### **Power Control Function**

Each pair of drivers can be enabled and disabled by pulling low and high, respectively, on the EN pin. Putting 1.7V and greater on the EN pin will disable the differential driver, while putting 0.8V and less on the EN pin will enable the driver.

The ISL15110 includes an external IBIAS pin for biasing the quiescent current. Grounding the pin in single supply designs gives the nominal quiescent current shown in the "Electrical Specifications" table starting on page 5, while inserting a resistor from pin to ground will scale down the quiescent current for both drivers, as shown in Figure 19 on page 9.

### Multi Tone Power Ratio (MTPR)

G.hn PLC uses OFDM modulation to digitally encode data for communication. A carrier spacing of 24.41kHz is used in power lines, and 48.82kHz is used in phone lines.

In multi-tone signaling, linearity is shown in the MTPR measurement. MTPR measures the difference in power of a carrier tone vs a missing tone.

FIGURE 38. 2MHz TO 50MHz PLC SIGNAL WITH 25kHz SPACING

Figure 38 shows the ISL15110MTPR in SISO mode. The curve shows an MTPR average of five symbols with an additional 11pt running average of that average. A -45dBc worst case MTPR is measured with a -50dBc, which is the typical number across the 2MHz to 50MHz transmit band.

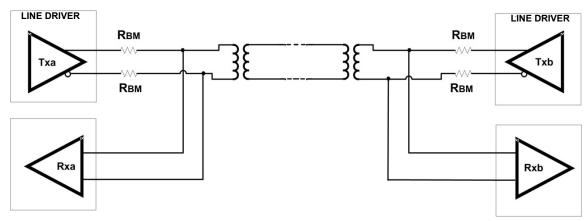

### **Disable Linearity**

Unlike DSL, communication in a PLC system is half duplex, meaning one device can transmit at a time. When the line driver is not transmitting, the line driver is disabled with the receiver ready to receive. Figure 39 on page 14 shows the shared transmit and receive signal path of two ends. RBMs are resistors to limit fault currents and provide a driving impedance to the transformer, thus setting its frequency span. Their values are typically low (<10 $\Omega$ ). When Txa is transmitting, optimal MTPR can be received by Rxb if Txb is removed. Because Txb is present, the ideal output of the line driver is to behave at high impedance when disabled. Figure 20 on page 9 shows the linearity at the outputs with the ISL15110 disabled. An average MTPR of -48dBc is achieved.

FIGURE 39. Tx and Rx SIGNAL PATH. CASE1: [Txa: ON, Rxa: OFF, Txb: OFF, Rxb: ON]. CASE2: [Txa: OFF, Rxa: ON, Txb: ON, Rxb: OFF]

### **Board Design Recommendation**

To minimize parasitic capacitance in the ISL15110 design, lay out short output traces and select low capacitance protection devices and line transformers with low interwinding capacitance in the signal path.

The supply decoupling capacitors are also placed close to the supply pins to minimize parasitic inductance in the supply path. High frequency load currents are typically pulled through these capacitors, so close placement of the  $0.1\mu$ F capacitors on the supply pin will improve dynamic performance. The higher  $4.7\mu$ F value capacitors can be placed farther from the supply pins because they provide low frequency decoupling.

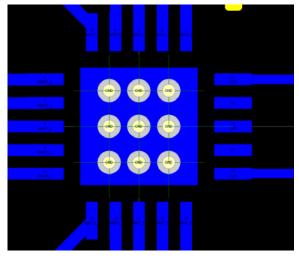

The thermal pad for the ISL15110 should be connected to ground in single supply applications. For good thermal control, run vias to a bottom pad to help dissipate heat away from the package. The ISL15110 evaluation board uses nine 20mil diameter vias with 10mil holes.

FIGURE 40. ISL15110 EVALUATION BOARD

#### **Thermal Resistance and Power Dissipation**

Thermal resistance for junction to ambient,  $T_{JA}$ , is +43°C/W. The maximum power dissipation for MIMO at the 13.2V supply is 1200mW. The ambient temperature allowed given the maximum junction temperature of +150°C is:

$$\begin{split} T_{A} &= T_{J} - \theta_{JA} \times Pd \\ T_{A} &= +150^{\circ}C - 43^{\circ}(C/W)^{*}1.2 = +98.4^{\circ}C \end{split} \tag{EQ. 2}$$

# **Revision History** The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please visit our website to make sure you have the latest revision.

| DATE         | REVISION | CHANGE                                                                                                                                                                                                        |

|--------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Apr 6, 2018  | FN8282.1 | Added Related Literature section to page 1.<br>Updated Ordering information table by adding tape and reel quantity column.<br>Updated Note 3.<br>Removed About Intersil section and added Renesas disclaimer. |

| Jan 31, 2013 | FN8282.0 | Initial release                                                                                                                                                                                               |

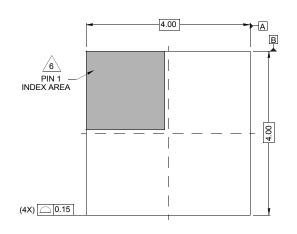

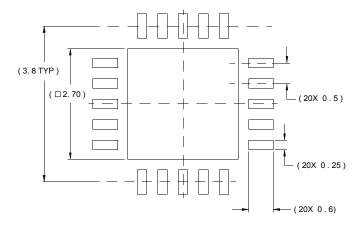

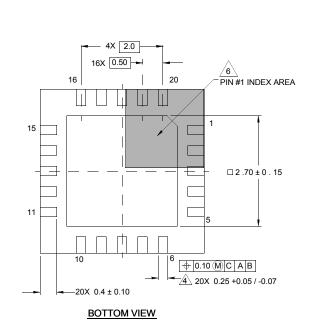

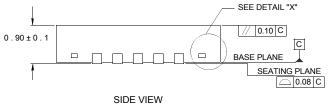

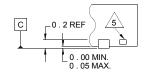

## **Package Outline Drawing**

L20.4x4C

20 LEAD QUAD FLAT NO-LEAD PLASTIC PACKAGE Rev 0, 11/06

TOP VIEW

#### TYPICAL RECOMMENDED LAND PATTERN

DETAIL "X"

#### NOTES:

- 1. Dimensions are in millimeters. Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

- 4. Dimension b applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- 6. The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 indentifier may be either a mold or mark feature.

For the most recent package outline drawing, see <u>L20.4x4C</u>.