# ISL6269B

High-Performance Notebook PWM Controller With Audio-Frequency Clamp

FN6280 Rev 3.00 November 17, 2014

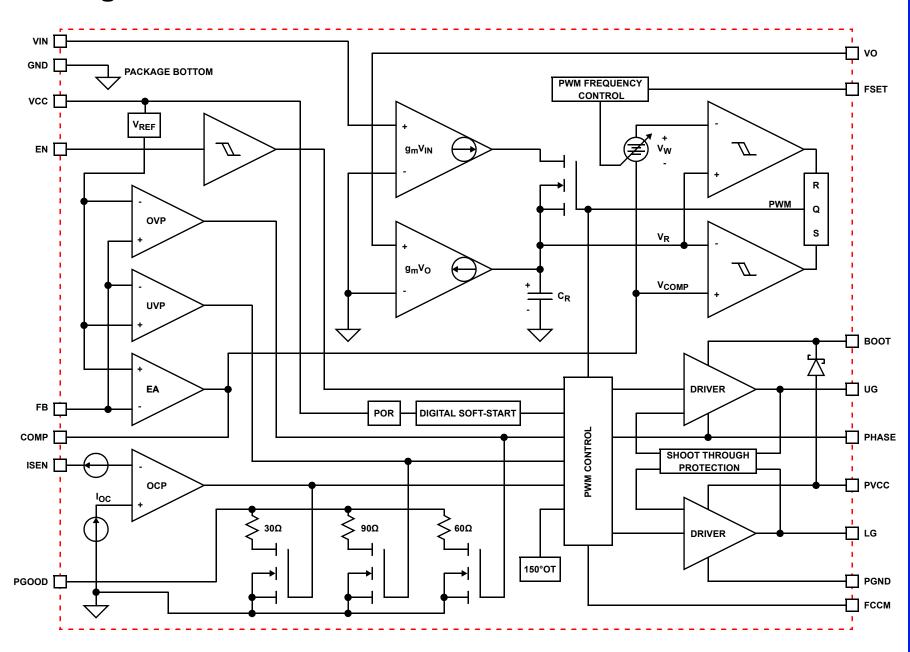

The ISL6269B IC is a Single-phase Synchronous-Buck PWM controller featuring Intersil's Robust Ripple Regulator R3™ Technology that delivers truly superior dynamic response to input voltage and output load transients. Integrated MOSFET drivers and bootstrap diode result in fewer components and smaller implementation area.

Intersil's R3<sup>TM</sup> Technology combines the best features of fixed-frequency PWM and hysteretic PWM while eliminating many of their shortcomings. R3<sup>TM</sup> Technology employs an innovative modulator that synthesizes an AC ripple voltage signal  $V_R$ , analogous to the output inductor ripple current. The AC signal  $V_R$  enters a window comparator where the lower threshold is the error amplifier output  $V_{COMP}$  and the upper threshold is a programmable voltage reference  $V_W$ , resulting in generation of the PWM signal. The voltage reference  $V_W$  sets the steady-state PWM frequency. Both edges of the PWM can be modulated in response to input voltage transients and output load transients, much faster than conventional fixed-frequency PWM controllers. Unlike a conventional hysteretic converter, the ISL6269B has an error amplifier that provides  $\pm 1\%$  voltage regulation at the FB pin.

The ISL6269B has a 1.5ms digital soft-start and can be started into a pre-biased output voltage. A resistor divider is used to program the output voltage setpoint. The ISL6269B can be configured to operate in Continuous Conduction Mode (CCM) or Diode Emulation Mode (DEM), which improves light-load efficiency. In CCM the controller always operates as a synchronous rectifier, however when DEM is enabled, the low-side MOSFET is permitted to stay off, blocking negative current flow into the low-side MOSFET from the output inductor.

# **Features**

- High performance R3™ Technology

- · Fast transient response

- ±1% regulation accuracy: -10°C to +100°C and -40° to +100°C

- Wide input voltage range: +5V to +25V

- Output voltage range: +0.6V to +3.3V

- · Wide output load range: 0A to 25A

- Selectable diode emulation mode for increased light load efficiency

- Programmable PWM frequency: 200kHz to 600kHz

- · Pre-biased output start-up capability

- · Integrated MOSFET drivers and bootstrap diode

- · Internal digital soft-start

- · Power-good monitor

- · PWM minimum frequency above audible spectrum

- · Fault protection

- Undervoltage protection

- Soft crowbar overvoltage protection

- Low-side MOSFET r<sub>DS(ON)</sub> overcurrent protection

- Over-temperature protection

- Fault identification by PGOOD pull-down resistance

- · Pb-free (RoHS compliant)

# **Applications**

- · PCI express graphical processing unit

- · Auxiliary power rail

- VRM

- Network adapter

# **Ordering Information**

| PART NUMBER<br>(Notes 1, 2, 3) | PART<br>MARKING | TEMP RANGE<br>(°C) | PACKAGE<br>(RoHS Compliant) | PKG. DWG. # |  |

|--------------------------------|-----------------|--------------------|-----------------------------|-------------|--|

| ISL6269BCRZ                    | 62 69BCRZ       | -10 to +100        | 16 Ld 4x4 QFN               | L16.4x4     |  |

| ISL6269BIRZ                    | 62 69BIRZ       | -40 to +100        | 16 Ld 4x4 QFN               | L16.4x4     |  |

#### NOTES:

- 1. Add "-T\*" suffix for tape and reel. Please refer to TB347 for details on reel specifications.

- These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials and 100% matte tin

plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free

products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. For Moisture Sensitivity Level (MSL), please see product information page for ISL6269B. For more information on MSL, please see tech brief TB363.

# **Pin Configuration**

# **Functional Pin Descriptions**

## **GND (Bottom Pad)**

Signal common of the IC. Unless otherwise stated, signals are referenced to the GND pin, not the PGND pin.

# VIN (Pin 1)

The VIN pin measures the converter input voltage which is a required input to the R3™ PWM modulator. Connect across the drain of the high-side MOSFET to the GND pin.

# VCC (Pin 2)

The VCC pin is the input bias voltage for the IC. Connect +5V from the VCC pin to the GND pin. Decouple with at least  $1\mu F$  of a MLCC capacitor from the VCC pin to the GND pin.

## FCCM (Pin 3)

The FCCM pin configures the controller to operate in Forced Continuous Conduction Mode (FCCM) or Diode Emulation Mode (DEM.) DEM is disabled when the FCCM pin is pulled above the rising threshold voltage  $V_{\mbox{FCCMTHR}}$ , conversely DEM is enabled when the FCCM pin is pulled below the falling threshold voltage  $V_{\mbox{FCCMTHF}}$ .

### **EN (Pin 4)**

The EN pin is the on/off switch of the IC. The soft-start sequence begins when the EN pin is pulled above the rising threshold voltage  $V_{\mbox{\footnotesize ENTHR}}$  and  $V_{\mbox{\footnotesize VCC}}$  is above the power-on reset (POR) rising threshold voltage  $V_{\mbox{\footnotesize VCC\_THR}}.$  When the EN pin is pulled below the falling threshold voltage  $V_{\mbox{\footnotesize ENTHF}}$  PWM immediately stops.

## COMP (Pin 5)

The COMP pin is the output of the control-loop error amplifier. Compensation components for the control-loop connect across the COMP and FB pins.

## FB (Pin 6)

The FB pin is the inverting input of the control-loop error amplifier. The converter output voltage regulates to 600mV from the FB pin to the GND pin. Program the desired output voltage with a resistor network connected across the VO, FB and GND pins. Select the resistor values such that FB to GND is 600mV when the converter output voltage is at the programmed regulation value.

#### FSET (Pin 7)

The FSET pin programs the PWM switching frequency. Program the desired PWM frequency with a resistor and a capacitor connected across the FSET and GND pins.

### **VO (Pin 8)**

The VO pin measures the converter output voltage and is used exclusively as an input to the R3™ PWM modulator. Connect at the physical location where the best output voltage regulation is desired.

# ISEN (Pin 9)

The ISEN pin programs the threshold of the OCP overcurrent fault protection. Program the desired OCP threshold with a resistor connected across the ISEN and PHASE pins. The OCP threshold is programmed to detect the peak current of the output inductor. The peak current is the sum of the DC and AC components of the inductor current.

#### PGND (Pin 10)

The PGND pin conducts the turn-off transient current through the LG gate driver. The PGND pin must be connected to complete the pull-down circuit of the LG gate driver. The PGND pin should be connected to the source of the low-side MOSFET through a low impedance path, preferably in parallel with the trace connecting the LG pin to the gate of the low-side MOSFET. The adaptive shoot-through protection circuit, measures the low-side MOSFET gate-source voltage from the LG pin to the PGND pin.

#### **LG (Pin 11)**

The LG pin is the output of the low-side MOSFET gate driver. Connect to the gate of the low-side MOSFET.

# **PVCC (Pin 12)**

The PVCC pin is the input voltage bias for the LG low-side MOSFET gate driver. Connect +5V from the PVCC pin to the PGND pin. Decouple with at least  $1\mu F$  of an MLCC capacitor across the PVCC and PGND pins.

# **BOOT (Pin 13)**

The BOOT pin stores the input voltage for the UG high-side MOSFET gate driver. Connect an MLCC capacitor across the BOOT and PHASE pins. The boot capacitor is charged through an internal boot diode connected from the PVCC pin to the BOOT pin, each time the PHASE pin drops below PVCC minus the voltage dropped across the internal boot diode.

#### **UG (Pin 14)**

The UG pin is the output of the high-side MOSFET gate driver. Connect to the gate of the high-side MOSFET.

## PHASE (Pin 15)

The PHASE pin detects the voltage polarity of the PHASE node and is also the current return path for the UG high-side MOSFET gate driver. Connect the PHASE pin to the node consisting of the high-side MOSFET source, the low-side MOSFET drain and the output inductor.

# **PGOOD (Pin 16)**

The PGOOD pin is an open-drain output that indicates when the converter is able to supply regulated voltage. Connect the PGOOD pin to +5V through a pull-up resistor.

# **Block Diagram**

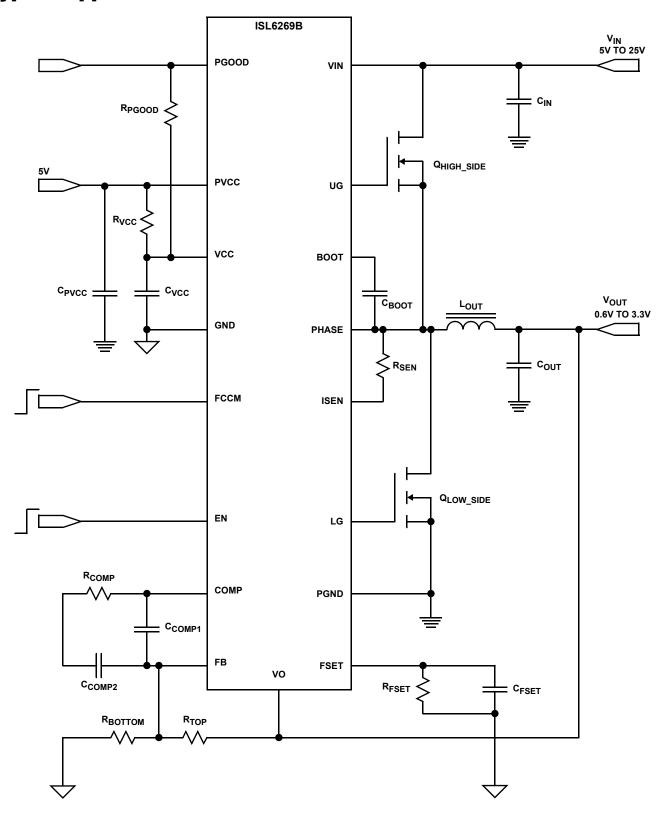

# **Typical Application**

# **Absolute Maximum Ratings**

| A-11 1/11 A-15             | 0.014                     |

|----------------------------|---------------------------|

| SEN, VIN to GND            | 0.3V to +28V              |

| VCC, PGOOD to GND          | 0.3V to +7.0V             |

| •                          |                           |

| PVCC to PGND               |                           |

| GND to PGND                | 0.3V to +0.3V             |

| EN, FCCM                   | 0.3V to GND, VCC +3.3V    |

| VO, FB, COMP, FSET         | 0.3V to GND, VCC +0.3V    |

| PHASE to GND (DC)          | 0.3V to +28V              |

| (<100ns Pulse Width, 10µJ) | 5.0V                      |

| BOOT to GND, or PGND       | 0.3V to +33V              |

| BOOT to PHASE              | 0.3V to +7V               |

| UG (DC)                    | 0.3V to PHASE, BOOT +0.3V |

| (<200ns Pulse Width, 20µJ) | 4.0V                      |

| LG (DC)                    | 0.3V to PGND, PVCC +0.3V  |

| (<100ns Pulse Width, 4µJ)  | 2.0V                      |

| Thermal Resistance (Typical, Notes 4, 5) | θ <sub>JA</sub> (°C/W) | θ <b>JC</b> (°C/W) |

|------------------------------------------|------------------------|--------------------|

| QFN Package                              | 48                     | 11.5               |

| Junction Temperature Range               | 5                      | 55°C to +150°C     |

| Operating Temperature Range              |                        |                    |

| ISL6269BCRZ                              | 10                     | 0°C to +100°C      |

| ISL6269BIRZ                              | 40                     | 0°C to +100°C      |

| Storage Temperature                      | <del>.</del> 6         | 55°C to +150°C     |

| Pb-Free Reflow Profile                   |                        | see TB493          |

|                                          |                        |                    |

# **Recommended Operating Conditions**

**Thermal Information**

| Ambient Temperature Range   |                |

|-----------------------------|----------------|

| ISL6269BCRZ                 | 10°C to +100°C |

| ISL6269BIRZ                 | 40°C to +100°C |

| Supply Voltage (VIN to GND) | 5V to 25V      |

| VCC to GND                  | 5V ±5%         |

| PVCC to PGND                | 5V ±5%         |

# **Recommended Operating Conditions**

Temperature .....-40 °C to +85 °C Supply Voltage .....2.7V to 5.5V

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES

- θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 5. For  $\theta_{JC}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

**Electrical Specifications** These specifications apply for  $T_A = -40 \,^{\circ}\text{C}$  to  $+100 \,^{\circ}\text{C}$ , unless otherwise stated. All typical specifications  $T_A = +25 \,^{\circ}\text{C}$ ,  $V_{CC} = 5V$ ,  $V_{IN} = 15V$

| PARAMETER                                     | SYMBOL                 | TEST CONDITIONS                                | MIN      | TYP  | MAX  | UNIT |

|-----------------------------------------------|------------------------|------------------------------------------------|----------|------|------|------|

| V <sub>IN</sub>                               |                        |                                                |          |      |      | •    |

| V Innut Biog Current                          | I <sub>VIN</sub>       | EN = 5V, V <sub>IN</sub> = 5V                  |          | 6.5  | 10   | μΑ   |

| V <sub>IN</sub> Input Bias Current            |                        | EN = 5V, V <sub>IN</sub> = 25V                 |          | 26   | 35   | μΑ   |

| V <sub>IN</sub> Shutdown Current              | I <sub>VIN_SHDN</sub>  | EN = GND, V <sub>IN</sub> = 25V                |          | 0.1  | 1.0  | μΑ   |

| V <sub>CC</sub> and PVCC                      | ,                      |                                                | ,        |      |      |      |

| V <sub>CC</sub> Input Bias Current            | I <sub>vcc</sub>       | EN = 5V, FCCM = GND, FB = 0.65V                |          | 1.7  | 2.5  | mA   |

| V <sub>CC</sub> Shutdown Current              | lvcc_shdn              | EN = GND, VCC = 5V                             |          | 0.1  | 1.0  | μΑ   |

| PVCC Shutdown Current                         | I <sub>PVCC_SHDN</sub> | EN = GND, PVCC = 5V                            |          | 0.1  | 1.0  | μΑ   |

| V <sub>CC</sub> POR THRESHOLD                 | <u> </u>               |                                                | "        |      |      |      |

| Rising V <sub>CC</sub> POR Threshold Voltage  | V <sub>VCC_THR</sub>   | T <sub>A</sub> = -10°C to +100°C               | 4.35     | 4.45 | 4.55 | V    |

|                                               |                        |                                                | 4.33     | 4.45 | 4.55 | ٧    |

| Falling V <sub>CC</sub> POR Threshold Voltage | V <sub>VCC_THF</sub>   | T <sub>A</sub> = -10°C to +100°C               | 4.10     | 4.20 | 4.30 | ٧    |

|                                               |                        |                                                | 4.08     | 4.20 | 4.30 | ٧    |

| REGULATION                                    | ,                      |                                                | ,        |      |      |      |

| Reference Voltage                             | V <sub>REF</sub>       |                                                |          | 0.6  |      | V    |

| Regulation Accuracy                           |                        | FB connected to COMP                           | -1       |      | +1   | %    |

| PWM                                           |                        |                                                | <u> </u> | II.  | 1    |      |

| Frequency Range                               | f <sub>SW</sub>        | FCCM = 5V                                      | 200      |      | 600  | kHz  |

|                                               | f <sub>AUDIO</sub>     | FCCM = GND, T <sub>A</sub> = -10 °C to +100 °C | 19       | 28   |      | kHz  |

|                                               |                        | FCCM = GND                                     | 18       | 28   |      | kHz  |

| Frequency-Set Accuracy                        |                        | f <sub>SW</sub> = 300kHz                       | -12      |      | +12  | %    |

| VO Range                                      | V <sub>VO</sub>        |                                                | 0.60     |      | 3.30 | ٧    |

**Electrical Specifications** These specifications apply for  $T_A = -40 \,^{\circ}\text{C}$  to  $+100 \,^{\circ}\text{C}$ , unless otherwise stated. All typical specifications  $T_A = +25 \,^{\circ}\text{C}$ ,  $V_{CC} = 5V$ ,  $V_{IN} = 15V$  (Continued)

| PARAMETER                           | SYMBOL                | TEST CONDITIONS                                           | MIN  | TYP  | MAX  | UNIT |

|-------------------------------------|-----------------------|-----------------------------------------------------------|------|------|------|------|

| VO Input Leakage                    | Ivo                   | VO = 0.6V                                                 |      | 1.3  |      | μΑ   |

|                                     |                       | VO = 3.30V                                                |      | 7.0  |      | μΑ   |

| ERROR AMPLIFIER                     |                       |                                                           |      |      |      |      |

| FB Input Bias Current               | I <sub>FB</sub>       | FB = 0.6V                                                 | -0.5 |      | +0.5 | μΑ   |

| COMP Source Current                 | I <sub>COMP_SRC</sub> | FB = 0.40V, COMP = 3.20V                                  |      | 2.5  |      | mA   |

| COMP Sink Current                   | I <sub>COMP_SNK</sub> | FB = 0.80V, COMP = 0.30V                                  |      | 0.3  |      | mA   |

| COMP High Clamp Voltage             | V <sub>COMP_HC</sub>  | FB = 0.40V, Sink 5μA                                      | 3.10 | 3.40 | 3.65 | V    |

| COMP Low Clamp Voltage              | V <sub>COMP_LC</sub>  | FB = 0.80V, Source 50μA                                   | 0.09 | 0.15 | 0.21 | V    |

| POWER-GOOD                          |                       |                                                           | •    |      |      | •    |

| PGOOD Pull-down Impedance           | R <sub>PG_SS</sub>    | PGOOD = 5mA Sink, T <sub>A</sub> = -10°C to +100°C        | 75   | 95   | 125  | Ω    |

|                                     |                       | PGOOD = 5mA Sink                                          | 67   | 95   | 125  | Ω    |

|                                     | R <sub>PG_UV</sub>    | PGOOD = 5mA Sink, T <sub>A</sub> = -10°C to +100°C        | 75   | 95   | 125  | Ω    |

|                                     |                       | PGOOD = 5mA Sink                                          | 67   | 95   | 125  | Ω    |

|                                     | R <sub>PG_OV</sub>    | PGOOD = 5mA Sink, T <sub>A</sub> = -10°C to +100°C        | 50   | 63   | 85   | Ω    |

|                                     |                       | PGOOD = 5mA Sink                                          | 45   | 63   | 85   | Ω    |

|                                     | R <sub>PG_OC</sub>    | PGOOD = 5mA Sink, T <sub>A</sub> = -10 °C to +100 °C      | 25   | 32   | 45   | Ω    |

|                                     |                       | PGOOD = 5mA Sink                                          | 22   | 32   | 45   | Ω    |

| PGOOD Leakage Current               | I <sub>PGOOD</sub>    | PGOOD = 5V                                                |      | 0.1  | 1.0  | μΑ   |

| PGOOD Maximum Sink Current (Note 6) |                       |                                                           |      | 5.0  |      | mA   |

| PGOOD Soft-start Delay              | t <sub>SS</sub>       | EN High to PGOOD High, T <sub>A</sub> = -10 °C to +100 °C | 2.20 | 2.75 | 3.30 | ms   |

|                                     |                       | EN High to PGOOD High                                     | 2.20 | 2.75 | 3.50 | ms   |

| GATE DRIVER                         |                       |                                                           | l l  |      |      |      |

| UG Pull-Up Resistance               | R <sub>UGPU</sub>     | 200mA Source Current                                      |      | 1.0  | 1.5  | Ω    |

| UG Source Current (Note 6)          | lugsrc                | UG - PHASE = 2.5V                                         |      | 2.0  |      | Α    |

| UG Sink Resistance                  | R <sub>UGPD</sub>     | 250mA Sink Current                                        |      | 1.0  | 1.5  | Ω    |

| UG Sink Current (Note 6)            | lugsnk                | UG - PHASE = 2.5V                                         |      | 2.0  |      | Α    |

| LG Pull-Up Resistance               | R <sub>LGPU</sub>     | 250mA Source Current                                      |      | 1.0  | 1.5  | Ω    |

| LG Source Current (Note 6)          | I <sub>LGSRC</sub>    | LG - PGND = 2.5V                                          |      | 2.0  |      | Α    |

| LG Sink Resistance                  | R <sub>LGPD</sub>     | 250mA Sink Current                                        |      | 0.5  | 0.9  | Ω    |

| LG Sink Current (Note 6)            | I <sub>LGSNK</sub>    | LG - PGND = 2.5V                                          |      | 4.0  |      | Α    |

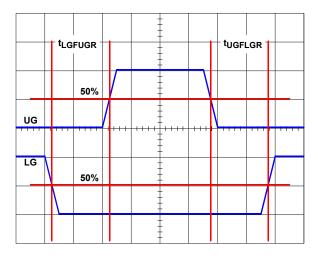

| UG to LG Deadtime                   | tugflgr               | UG falling to LG rising, no load                          |      | 21   |      | ns   |

| LG to UG Deadtime                   | tLGFUGR               | LG falling to UG rising, no load                          |      | 14   |      | ns   |

| BOOTSTRAP DIODE                     |                       | 1                                                         |      |      |      |      |

| Forward Voltage                     | V <sub>F</sub>        | PVCC = 5V, I <sub>F</sub> = 2mA                           |      | 0.58 |      | V    |

| Reverse Leakage                     | I <sub>R</sub>        | V <sub>R</sub> = 25V                                      |      | 0.2  |      | μΑ   |

| CONTROL INPUTS                      |                       |                                                           |      | 1    |      |      |

| EN High Threshold                   | V <sub>ENTHR</sub>    |                                                           | 2.0  |      |      | V    |

| EN Low Threshold                    | V <sub>ENTHF</sub>    |                                                           |      |      | 1.0  | V    |

| FCCM High Threshold                 | V <sub>FCCMTHR</sub>  |                                                           | 2.0  |      |      | V    |

| FCCM Low Threshold                  | V <sub>FCCMTHF</sub>  |                                                           |      |      | 1.0  | V    |

| EN Leakage                          | I <sub>ENL</sub>      | EN = OV                                                   |      | 0.1  | 1.0  | μA   |

| Č                                   | I <sub>ENH</sub>      | EN = 5V                                                   |      | 0.1  | 1.0  | μA   |

# **Electrical Specifications** These specifications apply for $T_A = -40 \,^{\circ}\text{C}$ to $+100 \,^{\circ}\text{C}$ , unless otherwise stated. All typical specifications $T_A = +25 \,^{\circ}\text{C}$ , $V_{CC} = 5V$ , $V_{IN} = 15V$ (Continued)

| PARAMETER                     | SYMBOL             | TEST CONDITIONS                                   | MIN | TYP | MAX | UNIT |

|-------------------------------|--------------------|---------------------------------------------------|-----|-----|-----|------|

| FCCM Leakage                  | IFCCML             | FCCM = OV                                         |     | 0.1 | 1.0 | μΑ   |

|                               | I <sub>FCCMH</sub> | FCCM = 5V                                         |     | 2.0 |     | μA   |

| PROTECTION                    |                    |                                                   |     |     |     |      |

| ISEN OCP Threshold            | loc                | ISEN sourcing, T <sub>A</sub> = -10 °C to +100 °C | 19  | 26  | 33  | μΑ   |

|                               |                    | ISEN sourcing                                     | 17  | 26  | 33  | μΑ   |

| ISEN Short-Circuit Threshold  | I <sub>sc</sub>    | ISEN sourcing                                     |     | 50  |     | μΑ   |

| UVP Threshold                 | V <sub>UV</sub>    |                                                   | 81  | 84  | 87  | %    |

| OVP Rising Threshold          | V <sub>OVR</sub>   |                                                   | 113 | 116 | 119 | %    |

| OVP Falling Threshold         | V <sub>OVF</sub>   |                                                   | 100 | 103 | 106 | %    |

| OTP Rising Threshold (Note 6) | T <sub>OTR</sub>   |                                                   |     | 150 |     | °C   |

| OTP Hysteresis (Note 6)       | T <sub>OTHYS</sub> |                                                   |     | 25  |     | °C   |

#### NOTE:

<sup>6.</sup> Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

# **Theory of Operation**

#### **Modulator**

The ISL6269B is a hybrid of fixed frequency PWM control and variable frequency hysteretic control. Intersil's R3TM Technology can simultaneously affect the PWM switching frequency and PWM duty cycle in response to input voltage and output load transients. The term "Ripple" in the name "Robust Ripple Regulator" refers to the converter output inductor ripple current, not the converter output ripple voltage. The R3TM Modulator synthesizes an AC signal  $V_R,$  which is an ideal representation of the output inductor ripple current. The duty-cycle of  $V_R$  is the result of charge and discharge current through a ripple capacitor  $C_R$ . The current through  $C_R$  is provided by a transconductance amplifier  $g_m$  that measures the VIN and VO pin voltages. The positive slope of  $V_R$  can be written as:

$$V_{RPOS} = (g_m) \cdot (V_{IN} - V_{OUT})$$

(EQ. 1)

The negative slope of V<sub>R</sub> can be written as:

$$V_{RNEG} = g_{m} \cdot V_{OUT}$$

(EQ. 2)

Where g<sub>m</sub> is the gain of the transconductance amplifier.

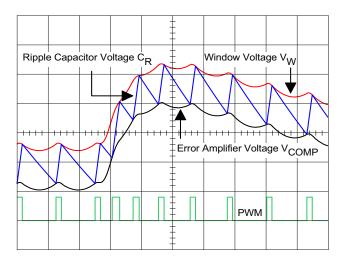

A window voltage  $V_W$  is referenced with respect to the error amplifier output voltage  $V_{COMP}$ , creating an envelope into which the ripple voltage  $V_R$  is compared. The amplitude of  $V_W$  is set by a resistor connected across the FSET and GND pins. The  $V_R$ ,  $V_{COMP}$  and  $V_W$  signals feed into a window comparator in which  $V_{COMP}$  is the lower threshold voltage and  $V_W$  is the higher threshold voltage. Figure 1 shows PWM pulses being generated as  $V_R$  traverses the  $V_W$  and  $V_{COMP}$  thresholds. The PWM switching frequency is proportional to the slew rates of the positive and negative slopes of  $V_R$ ; the PWM switching frequency is inversely proportional to the voltage between  $V_W$  and  $V_{COMP}$ .

FIGURE 1. MODULATOR WAVEFORMS DURING LOAD TRANSIENT

#### **Power-On Reset**

The ISL6269B is disabled until the voltage  $V_{VCC}$  has increased above the rising power-on reset (POR)  $V_{VCC\_THR}$  threshold voltage. The controller will become once again disabled when the voltage  $V_{VCC}$  decreases below the falling POR  $V_{VCC\_THF}$  threshold voltage.

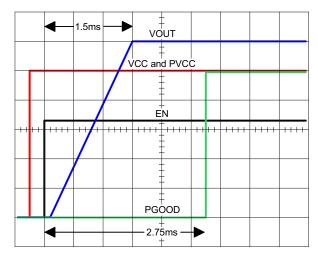

## **EN, Soft-Start and PGOOD**

The ISL6269B uses a digital soft-start circuit to ramp the output voltage of the converter to the programmed regulation setpoint at a predictable slew rate. The slew rate of the soft-start sequence has been selected to limit the in-rush current through the output capacitors as they charge to the desired regulation voltage. When the EN pin is pulled above the rising EN threshold voltage  $V_{\mbox{\footnotesize{ENTHR}}}$  the PGOOD soft-start delay  $t_{\mbox{\footnotesize{SS}}}$  begins and the output voltage begins to rise. The output voltage enters regulation in approximately 1.5ms and the PGOOD pin goes to high impedance once  $t_{\mbox{\footnotesize{SS}}}$  has elapsed.

FIGURE 2. SOFT-START SEQUENCE

The PGOOD pin indicates when the converter is capable of supplying regulated voltage. The PGOOD pin is an undefined impedance if  $V_{VCC}$  has not reached the rising POR threshold  $V_{VCC\_THR}$ , or if  $V_{VCC}$  is below the falling POR threshold  $V_{VCC\_THF}$ . The ISL6269B features a unique fault-identification capability that can drastically reduce troubleshooting time and effort. The pull-down resistance of the PGOOD pin corresponds to the fault status of the controller. During soft-start or if an undervoltage fault occurs, the PGOOD pull-down resistance is  $95\Omega$ , or  $30\Omega$  for an overcurrent fault, or  $60\Omega$  for an overvoltage fault.

**TABLE 1. PGOOD PULL-DOWN RESISTANCE**

| CONDITION                  | PGOOD RESISTANCE |

|----------------------------|------------------|

| V <sub>CC</sub> Below POR  | Undefined        |

| Soft-start or Undervoltage | 95Ω              |

| Overvoltage                | 60Ω              |

| Overcurrent                | 30Ω              |

# **MOSFET Gate-Drive Outputs LG and UG**

The ISL6269B has internal gate-drivers for the high-side and low-side N-Channel MOSFETs. The LG gate-driver is optimized for low duty-cycle applications where the low-side MOSFET conduction losses are dominant, requiring a low r<sub>DS(ON)</sub> MOSFET. The LG pull-down resistance is small in order to clamp the gate of the MOSFET below the  $V_{\mbox{GS}(\mbox{th})}$  at turnoff. The current transient through the gate at turnoff can be considerable because the switching charge of a low r<sub>DS(ON)</sub> MOSFET can be large. Adaptive shoot-through protection prevents a gate-driver output from turning on until the opposite gate-driver output has fallen below approximately 1V. The dead-time shown in Figure 3 is extended by the additional period that the falling gate voltage stays above the 1V threshold. The high-side gate-driver output voltage is measured across the UG and PHASE pins while the low-side gate-driver output voltage is measured across the LG and PGND pins. The power for the LG gate-driver is sourced directly from the PVCC pin. The power for the UG gate-driver is sourced from a "boot" capacitor connected across the BOOT and PHASE pins. The boot capacitor is charged from a 5V bias supply through a "boot diode" each time the low-side MOSFET turns on, pulling the PHASE pin low. The ISL6269B has an integrated boot diode connected from the PVCC pin to the BOOT pin.

FIGURE 3. LG AND UG DEAD-TIME

#### **Diode Emulation**

The ISL6269B normally operates in Continuous Conduction Mode (CCM), minimizing conduction losses by forcing the low-side MOSFET to operate as a synchronous rectifier. An improvement in light-load efficiency is achieved by allowing the converter to operate in Diode Emulation Mode (DEM), where the low-side MOSFET behaves as a smart-diode, forcing the device to block negative inductor current flow. The ISL6269B can be configured to operate in DEM by setting the FCCM pin low. Setting the FCCM pin high will disable DEM.

Positive-going inductor current flows from either the source of the high-side MOSFET, or the drain of the low-side MOSFET. Negative-going inductor current usually flows into the drain of the low-side MOSFET. When the low-side MOSFET conducts positive inductor current, the phase voltage will be negative with respect to the GND and PGND pins. Conversely, when the low-side

MOSFET conducts negative inductor current, the phase voltage will be positive with respect to the GND and PGND pins. Negative inductor current occurs when the output load current is less than ½ the inductor ripple current. Sinking negative inductor current through the low-side MOSFET lowers efficiency through unnecessary conduction losses. Efficiency can be further improved with a reduction of unnecessary switching losses by reducing the PWM frequency. It is characteristic of the R3™ architecture for the PWM frequency to decrease while in diode emulation. The extent of the frequency reduction is proportional to the reduction of load current. Upon entering DEM, the PWM frequency makes an initial step-reduction because of a 33% step-increase of the window voltage V<sub>W</sub>. The ISL6269B features an audio filter that clamps the minimum PWM frequency to a level beyond human hearing when the output load current becomes low enough.

With FCCM pulled low, the converter will automatically enter DEM after the PHASE pin has detected positive voltage, while the LG gate-driver pin is high for eight consecutive PWM pulses. The converter will return to CCM on the following cycle after the PHASE pin detects negative voltage, indicating that the body diode of the low-side MOSFET is conducting positive inductor current.

#### **Overcurrent and Short-Circuit Protection**

The overcurrent protection (OCP) and short circuit protection (SCP) setpoint is programmed with resistor R<sub>SEN</sub> that is connected across the ISEN and PHASE pins. The PHASE pin is connected to the drain terminal of the low-side MOSFET.

The SCP setpoint is internally set to twice the OCP setpoint. When an OCP or SCP fault is detected, the PGOOD pin will pull down to  $30\Omega$  and latch off the converter. The fault will remain latched until the EN pin has been pulled below the falling EN threshold voltage  $V_{\mbox{ENTHF}}$  or if  $V_{\mbox{VCC}}$  has decayed below the falling POR threshold voltage  $V_{\mbox{VCC}}$  THF:

The OCP circuit does not directly detect the DC load current leaving the converter. The OCP circuit detects the peak of positive-flowing output inductor current. The low-side MOSFET drain current  $I_D$  is assumed to be equal to the positive output inductor current when the high-side MOSFET is off. The inductor current develops a negative voltage across the r<sub>DS(ON)</sub> of the low-side MOSFET that is measured shortly after the LG gate driver output goes high. The ISEN pin sources the OCP sense current I<sub>SEN</sub>, through the OCP programming resistor R<sub>SEN</sub>. forcing the ISEN pin to zero volts with respect to the GND pin. The negative voltage across the PHASE and GND pins is nulled by the voltage dropped across R<sub>SEN</sub> as I<sub>SEN</sub> conducts through it. An OCP fault occurs if I<sub>SFN</sub> rises above the OCP threshold current I<sub>OC</sub> while attempting to null the negative voltage across the PHASE and GND pins. The  $I_{\mbox{\footnotesize{SEN}}}$  must exceed  $I_{\mbox{\footnotesize{OC}}}$  on all the PWM pulses that occur within 20 $\mu s$ . If I<sub>SEN</sub> falls below I<sub>OC</sub> on a PWM pulse before 20 $\mu s$  has elapsed, the timer will be reset. An SCP fault will occur within 10 $\mu$ s when I<sub>SEN</sub> exceeds twice I<sub>OC</sub>. The relationship between  $I_D$  and  $I_{SEN}$  is written as:

$$I_{SEN} \cdot R_{SEN} = I_{D} \cdot r_{DS(ON)}$$

(EQ. 3)

The value of R<sub>SEN</sub> is then written as:

$$R_{SEN} = \frac{\left(I_{FL} + \frac{I_{P-P}}{2}\right) \cdot OC_{SP} \cdot r_{DS(ON)}}{I_{OC}}$$

(EQ. 4)

#### Where:

- $R_{SEN}\left(\Omega\right)$  is the resistor used to program the overcurrent setpoint

- I<sub>SEN</sub> is the current sense current that is sourced from the ISEN pin

- I<sub>OC</sub> is the I<sub>SEN</sub> threshold current sourced from the ISEN pin that will activate the OCP circuit

- IFL is the maximum continuous DC load current

- IP-P is the inductor peak-to-peak ripple current

- OC<sub>SP</sub> is the desired overcurrent setpoint expressed as a multiplier relative to I<sub>FL</sub>

### **Overvoltage Protection**

When an OVP fault is detected, the PGOOD pin will pull down to  $60\Omega$  and latch-off the converter. The OVP fault will remain latched until  $^{\rm V}_{\rm VCC}$  has decayed below the falling POR threshold voltage  $^{\rm V}_{\rm VCC}$  THF.

The OVP fault detection circuit triggers after the voltage across the FB and GND pins has increased above the rising overvoltage threshold  $V_{OVR}.$  Although the converter has latched-off in response to an OVP fault, the LG gate-driver output will retain the ability to toggle the low-side MOSFET on and off, in response to the output voltage transversing the  $V_{OVR}$  and  $V_{OVF}$  thresholds.

# **Undervoltage Protection**

When a UVP fault is detected, the PGOOD pin will pull down to  $95\Omega$  and latch-off the converter. The fault will remain latched until the EN pin has been pulled below the falling EN threshold voltage  $V_{ENTHF}$  or if  $^{V}_{VCC}$  has decayed below the falling POR threshold voltage  $^{V}_{VCC\_THF}.$  The UVP fault detection circuit triggers after the voltage across the FB and GND pins has fallen below the undervoltage threshold  $V_{UV}.$

#### **Over-Temperature**

When the temperature of the ISL6269B increases above the rising threshold temperature TOTR, the IC will enter an OTP state that suspends the PWM, forcing the LG and UG gate-driver outputs low. The status of the PGOOD pin does not change nor does the converter latch-off. The PWM remains suspended until the IC temperature falls below the hysteresis temperature TOTHYS at which time normal PWM operation resumes. The OTP state can be reset if the EN pin is pulled below the falling EN threshold voltage  $\rm V_{ENTHF}$  or if  $\rm ^{V}_{VCC}$  decays below the falling POR threshold voltage V<sub>VCC\_THF</sub>. All other protection circuits function normally during OTP. It is likely that the IC will detect an UVP fault because in the absence of PWM, the output voltage immediately decays below the undervoltage threshold V<sub>UV</sub>; the PGOOD pin will pull down to  $95\Omega$  and latch-off the converter. The UVP fault will remain latched until the EN pin has been pulled below the falling EN threshold voltage V<sub>ENTHF</sub> or if <sup>V</sup><sub>VCC</sub> has decayed below the falling POR threshold voltage V<sub>VCC THF</sub>.

# **Programming the Output Voltage**

When the converter is in regulation there will be 600mV from the FB pin to the GND pin. Connect a two-resistor voltage divider across the VO pin and the GND pin with the output node connected to the FB pin. Scale the voltage-divider network such that the FB pin is 600mV with respect to the GND pin when the converter is regulating at the desired output voltage. The output voltage can be programmed from 600mV to 3.3V.

Programming the output voltage is written as:

$$V_{REF} = V_{OUT} \cdot \frac{R_{BOTTOM}}{R_{TOP} + R_{BOTTOM}}$$

(EQ. 5)

#### Where

- V<sub>OUT</sub> is the desired output voltage of the converter

- V<sub>REF</sub> is the voltage that the converter regulates to between the FB pin and the GND pin

- R<sub>TOP</sub> is the voltage programming resistor that connects from the FB pin to the VO pin. In addition to setting the output voltage, this resistor is part of the loop compensation network

- R<sub>BOTTOM</sub> is the voltage programming resistor that connects from the FB pin to the GND pin

Beginning with  $R_{TOP}$  between  $1k\Omega$  to  $5k\Omega$  , calculating  $R_{BOTTOM}$  is written as:

$$R_{BOTTOM} = \frac{V_{REF} \cdot R_{TOP}}{V_{OUT} - V_{REF}}$$

(EQ. 6)

# **Programming the PWM Switching Frequency**

The ISL6269B does not use a clock signal to produce PWM. The PWM switching frequency f<sub>SW</sub> is programmed by the resistor R<sub>FSET</sub> that is connected from the FSET pin to the GND pin. The approximate PWM switching frequency is written as:

$$f_{SW} = \frac{1}{k \cdot R_{FSET}}$$

(EQ. 7)

Estimating the value of R<sub>FSET</sub> is written as:

$$R_{FSET} = \frac{1}{k \cdot f_{SW}}$$

(EQ. 8)

#### Where:

- f<sub>SW</sub> is the PWM switching frequency

- $R_{\mbox{FSET}}$  is the  $f_{\mbox{SW}}$  programming resistor

- $k = 75 \times 10^{-12}$

It is recommended that whenever the control loop compensation network is modified,  $f_{SW}$  should be checked for the correct frequency and if necessary, adjust  $R_{FSET}$ .

#### **Compensation Design**

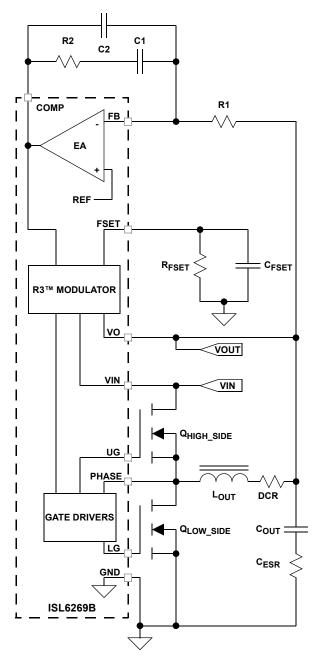

The LC output filter has a double pole at its resonant frequency that causes the phase to abruptly roll downward. The R3™ Modulator used in the ISL6269B, makes the LC output filter resemble a first order system in which the closed loop stability can be achieved with a Type II compensation network.

FIGURE 4. COMPENSATION REFERENCE CIRCUIT

Your local Intersil representative can provide a PC-based tool that can be used to calculate compensation network component values and help simulate the loop frequency response. The compensation network consists of the internal error amplifier of the ISL6269B and the external components R1, R2, C1 and C2 as well as the frequency setting components RFSET and CFSET, are identified in the schematic Figure 4.

# General Application Design Guide

This design guide is intended to provide a high-level explanation of the steps necessary to create a single-phase power converter. It is assumed that the reader is familiar with many of the basic skills and techniques referenced. In addition to this guide, Intersil provides complete reference designs that include schematics, bills of materials and example board layouts.

# **Selecting the LC Output Filter**

The duty cycle of an ideal buck converter is a function of the input and the output voltage. This relationship is written as:

$$D = \frac{V_{OUT}}{V_{IN}}$$

(EQ. 9)

The output inductor peak-to-peak ripple current is written as:

$$I_{p-p} = \frac{V_{OUT} \cdot (1-D)}{f_{SW} \cdot L_{OUT}}$$

(EQ. 10)

A typical step-down DC/DC converter will have an  $I_{P-P}$  of 20% to 40% of the maximum DC output load current. The value of  $I_{P-P}$  is selected based upon several criteria such as MOSFET switching loss, inductor core loss and the resistive loss of the inductor winding. The DC copper loss of the inductor can be estimated by:

$$P_{COPPER} = I_{LOAD}^2 \cdot DCR$$

(EQ. 11)

Where I<sub>LOAD</sub> is the converter output DC current.

The copper loss can be significant so attention has to be given to the DCR selection. Another factor to consider when choosing the inductor is its saturation characteristics at elevated temperature. A saturated inductor could cause destruction of circuit components, as well as nuisance OCP faults.

A DC/DC buck regulator must have output capacitance  $C_{OUT}$  into which ripple current  $I_{P-P}$  can flow. Current  $I_{P-P}$  develops a corresponding ripple voltage  $V_{P-P}$  across  $C_{OUT}$ , which is the sum of the voltage drop across the capacitor ESR and of the voltage change stemming from charge moved in and out of the capacitor. These two voltages are written as:

$$\Delta V_{FSR} = I_{P-P} \cdot ESR$$

(EQ. 12)

and

$$\Delta V_{C} = \frac{I_{P-P}}{8 \cdot C_{OUT} \cdot f_{SW}}$$

(EQ. 13)

If the output of the converter has to support a load with high pulsating current, several capacitors will need to be paralleled to reduce the total ESR until the required  $V_{P,P}$  is achieved. The inductance of the capacitor can cause a brief voltage dip if the load transient has an extremely high slew rate. Low inductance capacitors constructed with reverse package geometry are available. A capacitor dissipates heat as a function of RMS current and frequency. Be sure that  $I_{P,P}$  is shared by a sufficient quantity of paralleled capacitors so that they operate below the maximum rated RMS current at  $f_{\rm SW}$ . Take into account that the rated value of a capacitor can fade as much as 50% as the DC voltage across it increases.

# **Selection of the Input Capacitor**

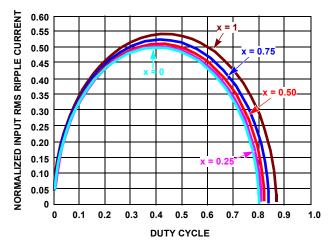

The important parameters for the bulk input capacitance are the voltage rating and the RMS current rating. For reliable operation, select bulk capacitors with voltage and current ratings above the maximum input voltage and capable of supplying the RMS current required by the switching circuit. Their voltage rating should be at least 1.25x greater than the maximum input voltage, while a voltage rating of 1.5x is a preferred rating. Figure 5 is a graph of the input RMS ripple current, normalized relative to output load current, as a function of duty cycle that is adjusted for converter efficiency. The ripple current calculation is written as shown in Equation 14:

$$I_{IN\_RMS} = \frac{\sqrt{(I_{MAX}^2 \cdot (D - D^2)) + (x \cdot I_{MAX}^2 \cdot \frac{D}{12})}}{I_{MAX}}$$

(EQ. 14)

#### Where:

- I<sub>MAX</sub> is the maximum continuous I<sub>LOAD</sub> of the converter

- x is a multiplier (0 to 1) corresponding to the inductor peak-to-peak ripple amplitude expressed as a percentage of  $I_{MAX}$  (0% to 100%)

- D is the duty cycle that is adjusted to take into account the efficiency of the converter which is written as shown in Equation 15:

$$D = \frac{V_{OUT}}{V_{IN} \cdot EFF}$$

(EQ. 15)

In addition to the bulk capacitance, some low ESL ceramic capacitance is recommended to decouple between the drain of the high-side MOSFET and the source of the low-side MOSFET.

FIGURE 5. NORMALIZED RMS INPUT CURRENT FOR x = 0.8

#### **MOSFET Selection and Considerations**

Typically, a MOSFET cannot tolerate even brief excursions beyond their maximum drain-to-source voltage rating. The MOSFETs used in the power stage of the converter should have a maximum  $V_{DS}$  rating that exceeds the sum of the upper voltage tolerance of the input power source and the voltage spike that occurs when the MOSFET switches off.

There are several power MOSFETs readily available that are optimized for DC/DC converter applications. The preferred high-side MOSFET emphasizes low switch charge so that the device spends the least amount of time dissipating power in the linear region. Unlike the low-side MOSFET, which has the drain to source voltage clamped by its body diode during turn off, the high-side MOSFET turns off with  $V_{\text{IN}}$ - $V_{\text{OUT}}$ - $V_{\text{Lacross}}$  it. The preferred low-side MOSFET emphasizes low  $r_{\text{DS}(\text{ON})}$  when fully saturated to minimize conduction loss.

For the low-side MOSFET, (LS), the power loss can be assumed to be conductive only and is written as:

$$P_{CON LS} \approx I_{LOAD}^2 \cdot r_{DS(ON) LS} \cdot (1-D)$$

(EQ. 16)

For the high-side MOSFET, (HS), its conduction loss is written as:

$$P_{CON HS} = I_{LOAD}^{2} \cdot r_{DS(ON) HS} \cdot D$$

(EQ. 17)

For the high-side MOSFET, its switching loss is written as:

$$P_{SW\_HS} = \frac{V_{IN} \cdot I_{VALLEY} \cdot t_{ON} \cdot f_{SW}}{2} + \frac{V_{IN} \cdot I_{PEAK} \cdot t_{OFF} \cdot f_{SW}}{2}$$

(EQ. 18)

#### Where:

- I<sub>VALLEY</sub> is the difference of the DC component of the inductor current minus 1/2 of the inductor ripple current

- I<sub>PEAK</sub> is the sum of the DC component of the inductor current plus 1/2 of the inductor ripple current

- t<sub>ON</sub> is the time required to drive the device into saturation

- t<sub>OFF</sub> is the time required to drive the device into cut-off

### **Selecting The Bootstrap Capacitor**

The selection of the bootstrap capacitor is written as:

$$C_{BOOT} = \frac{Q_g}{\Delta V_{BOOT}}$$

(EQ. 19)

#### Where

- Qg is the total gate charge required to turn on the high-side MOSFFT

- ΔV<sub>BOOT</sub>, is the maximum allowed voltage decay across the boot capacitor each time the high-side MOSFET is switched on

As an example, suppose the high-side MOSFET has a total gate charge  $Q_g$ , of 25nC at  $V_{GS}$  = 5V and a  $\Delta V_{BOOT}$  of 200mV. The calculated bootstrap capacitance is 0.125µF. For a comfortable margin select a capacitor that is double the calculated capacitance, in this example 0.22µF will suffice. Use an X7R or X5R ceramic capacitor.

# **Layout Considerations**

As a general rule, power should be on the bottom layer of the PCB and weak analog or logic signals are on the top layer of the PCB. The ground-plane layer should be adjacent to the top layer to provide shielding. The ground plane layer should have an island located under the IC, the compensation components and the FSET components. The island should be connected to the rest of the ground plane layer at one point.

FIGURE 6. TYPICAL POWER COMPONENT PLACEMENT

# **Signal Ground and Power Ground**

The bottom of the ISL6269B QFN package is the signal ground (GND) terminal for analog and logic signals of the IC. Connect the GND pad of the ISL6269B to the island of ground plane under the top layer using several vias, for a robust thermal and electrical conduction path. Connect the input capacitors, the output capacitors and the source of the lower MOSFETs to the power ground plane.

# PGND (Pin 10)

This is the return path for the pull-down of the LG low-side MOSFET gate driver. Ideally, PGND should be connected to the source of the low-side MOSFET with a low resistance, low inductance path.

#### VIN (PIN 1)

The VIN pin should be connected close to the drain of the high-side MOSFET, using a low resistance and low inductance path.

#### VCC (PIN 2)

For best performance, place the decoupling capacitor very close to the VCC and GND pins.

#### PVCC (PIN 12)

For best performance, place the decoupling capacitor very close to the PVCC and PGND pins, preferably on the same side of the PCB as the ISL6269B IC.

## FCCM (PIN 3), EN (PIN 4), PGOOD (PIN 16)

These are logic inputs that are referenced to the GND pin. Treat as a typical logic signal.

#### COMP (PIN 5), FB (PIN 6) AND VO (PIN 8)

For best results, use an isolated sense line from the output load to the VO pin. The input impedance of the FB pin is high, so place the voltage programming and loop compensation components close to the VO, FB and GND pins keeping the high impedance trace short

#### FSET (PIN 7)

This pin requires a quiet environment. The resistor  $R_{FSET}$  and capacitor  $C_{FSET}$  should be placed directly adjacent to this pin. Keep fast moving nodes away from this pin.

#### ISEN (PIN 9)

Route the connection to the ISEN pin away from the traces and components connected to the FB pin, COMP pin and FSET pin.

#### **LG (PIN 11)**

The signal going through this trace is both high dv/dt and high di/dt with high peak charging and discharging current. Route this trace in parallel with the trace from the PGND pin. These two traces should be short, wide and away from other traces. There should be no other weak signal traces in proximity with these traces on any layer.

#### **BOOT (PIN 13), UG (PIN 14), PHASE (PIN 15)**

The signals going through these traces are both high dv/dt and high di/dt, with high peak charging and discharging current. Route the UG and PHASE pins in parallel with short and wide traces. There should be no other weak signal traces in proximity with these traces on any layer.

# **Copper Size for the Phase Node**

The parasitic capacitance and parasitic inductance of the phase node should be kept very low to minimize ringing. It is best to limit the size of the PHASE node copper in strict accordance with the current and thermal management of the application. An MLCC should be connected directly across the drain of the upper MOSFET and the source of the lower MOSFET to suppress the turn-off voltage spike.

# **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to the web to make sure that you have the latest revision.

| DATE              | REVISION | CHANGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| November 17, 2014 | FN6280.3 | -Updated TemplateUpdated intersil trademark statement at the bottom of page oneOrdering information table on page 2, updated Note 1 from "*Add"-T" suffix for tape and reel" to "Add "-T*" suffix for tape and reel. Please refer to TB347 for details on reel specifications." -Ordering information table on page 2: Added MSL Note 3On page 6, updated Caution statement per legal's new verbiageOn page 8, updated Note 6 from "Guaranteed by characterization." to "Compliance to limits is assured by characterization and design." -Added revision history and about Intersil verbiageUpdated L16.4x4 to new POD format by removing table listing dimensions and moving dimensions onto drawingAdded Typical Recommended Land Pattern. |

# **About Intersil**

Intersil Corporation is a leading provider of innovative power management and precision analog solutions. The company's products address some of the largest markets within the industrial and infrastructure, mobile computing and high-end consumer markets.

For the most updated datasheet, application notes, related documentation and related parts, please see the respective product information page found at <a href="https://www.intersil.com">www.intersil.com</a>.

You may report errors or suggestions for improving this datasheet by visiting www.intersil.com/ask.

Reliability reports are also available from our website at <a href="www.intersil.com/support">www.intersil.com/support</a>

© Copyright Intersil Americas LLC 2006-2014. All Rights Reserved.

All trademarks and registered trademarks are the property of their respective owners.

For additional products, see <a href="https://www.intersil.com/en/products.html">www.intersil.com/en/products.html</a>

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="https://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <a href="https://www.intersil.com">www.intersil.com</a>