### ISL6700

80V/1.25A Peak, Medium Frequency, Low Cost, Half-Bridge Driver

FN9077 Rev.6.00 December 29, 2004

The ISL6700 is an 80V/1.25A peak, medium frequency, low cost, half-bridge driver IC available in 8-lead SOIC and 12-lead QFN plastic packages. The low-side and high-side gate drivers are independently controlled and matched to 25ns. This gives the user maximum flexibility in dead-time selection and driver protocol. Undervoltage protection on both the low-side and high-side supplies force the outputs low. Non-latching, level-shift translation is used to control the upper drive circuit. Unlike some competitors, the high-side output returns to its correct state after a momentary undervoltage of the high-side supply.

### **Ordering Information**

| PART<br>NUMBER           | TEMP. RANGE (°C) PACKAGE |                            | PKG. DWG. # |  |  |

|--------------------------|--------------------------|----------------------------|-------------|--|--|

| ISL6700IB                | -40 to 125               | 8 Ld SOIC                  | M8.15       |  |  |

| ISL6700IBZ<br>(See Note) | -40 to 125               | 8 Ld SOIC<br>(Pb-free)     | M8.15       |  |  |

| ISL6700IR                | -40 to 125               | 12 Ld 4x4 QFN              | L12.4x4     |  |  |

| ISL6700IRZ<br>(See Note) | -40 to 125               | 12 Ld 4x4 QFN<br>(Pb-free) | L12.4x4     |  |  |

Add "-T" suffix to part number for tape and reel packaging.

NOTE: Intersil Pb-free products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

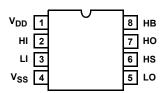

#### **Pinouts**

TOP VIEW

#### Features

- Drives 2 N-Channel MOSFETs in Half-Bridge Configuration

- Space Saving SO8 and Low R<sub>C-S</sub> QFN Packages

- Phase Supply Max Voltage to 80VDC

- · Bootstrap Supply Max Voltage to 96VDC

- Drives 1000pF Load with Rise and Fall Times Typ. 15ns

- TTL/CMOS Compatible Input Thresholds

- Independent Inputs for Non-Half-Bridge Topologies

- · No Start-Up Problems

- · Low Power Consumption

- · Wide Supply Range

- · Supply Undervoltage Protection

- QFN Package

- Compliant to JEDEC PUB95 MO-220 QFN

- Quad Flat No Leads Package Outline

- Pb-Free Available (RoHS Compliant)

### **Applications**

- · Telecom/Datacom Power Supplies

- · Half-Bridge Converters

- · Two-Switch Forward Converters

- Active Clamp Forward Converters

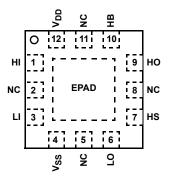

ISL6700IR (QFN) TOP VIEW

NOTE: EPAD = Exposed PAD.

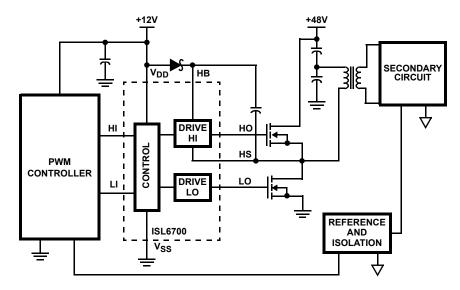

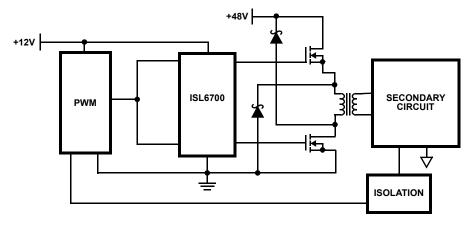

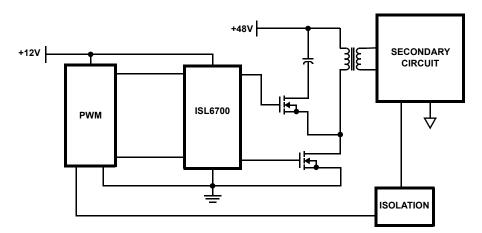

# Application Block Diagram

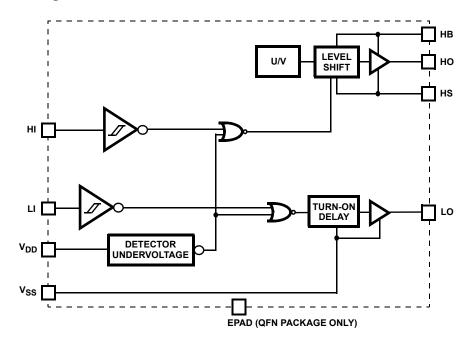

## Functional Block Diagram

FIGURE 1. TWO-SWITCH FORWARD CONVERTER

FIGURE 2. FORWARD CONVERTER WITH AN ACTIVE CLAMP

### **Absolute Maximum Ratings**

| Supply Voltage, V <sub>DD</sub> (Note 1) | 0.3V to 16V                                      |

|------------------------------------------|--------------------------------------------------|

| LI and HI Voltages (Note 1)              | 0.3V to V <sub>DD</sub> +0.3V                    |

| Voltage on HS (Note 1)                   | 0V to 80V                                        |

| Voltage on HB (Note 1)                   | . $V_{HS}$ -0.3V to $V_{HS}$ + $V_{DD}$          |

| Voltage on LO (Note 1)                   | V <sub>SS</sub> -0.3 to V <sub>DD</sub> +0.3V    |

| Voltage on HO (Note 1)                   | . V <sub>HS</sub> -0.3V to V <sub>HB</sub> +0.3V |

| Phase Slew Rate                          |                                                  |

#### **Maximum Recommended Operating Conditions**

| Supply Voltage, V <sub>DD</sub> |                                                           |

|---------------------------------|-----------------------------------------------------------|

| Voltage on HS                   |                                                           |

| Voltage on HS (Note 2)          | (Repetitive Transient) -1V to 80V                         |

| Voltage on HB                   | V <sub>HS</sub> +7.5V to V <sub>HS</sub> +V <sub>DD</sub> |

#### **Thermal Information**

| Thermal Resistance (Typical)              | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|-------------------------------------------|------------------------|------------------------|

| SOIC (Note 3)                             | 95                     | N/A                    |

| QFN (Note 4)                              | 49                     | 7                      |

| Max Power Dissipation at 25°C in Free Air | (SOIC, Note            | 3). 1.316W             |

| Max Power Dissipation at 25°C in Free Air | (QFN, Note             | 4) 2.976W              |

| Maximum Storage Temperature Range         | 65°                    | C to +150°C            |

| Maximum Junction Temperature Range        | 40°                    | C to +150°C            |

| Maximum Lead Temperature (Soldering 10    | Os)                    | +300°C                 |

| (SOIC - Lead Tips Only)                   |                        |                        |

|                                           |                        |                        |

For Recommended soldering conditions see Tech Brief TB389.

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the recommended operating conditions of this specification is not implied.

#### NOTES:

- 1. All voltages referenced to  $V_{\mbox{\footnotesize SS}}$  unless otherwise specified.

- Based on V<sub>DD</sub>=15V. The magnitude of the allowable negative transient on the HS pin is a function of the V<sub>DD</sub> supply voltage. V<sub>HS</sub><15.6V-V<sub>DD</sub>+V<sub>F</sub>, where V<sub>HS</sub> is the magnitude of the allowable negative transient and V<sub>F</sub> is the forward voltage drop of the bootstrap diode.

- 3.  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

- 4. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. θ<sub>JC</sub>, the "case temp" is measured at the center of the exposed metal pad on the package underside. See Tech Brief TB379.

### **Electrical Specifications** $V_{DD} = V_{HB} = 12V$ , $V_{SS} = V_{HS} = 0V$ , No Load on LO or HO, Unless Otherwise Specified

|                                                |                    |                                                 | T <sub>J</sub> = 25°C MIN TYP MAX |      | T <sub>J</sub> = -40°C TO<br>125°C |      |       |    |

|------------------------------------------------|--------------------|-------------------------------------------------|-----------------------------------|------|------------------------------------|------|-------|----|

| PARAMETERS                                     | SYMBOL             | TEST CONDITIONS                                 |                                   |      | MIN                                | MAX  | UNITS |    |

| SUPPLY CURRENTS & UNDERVOLTAGE PROTECTION      |                    |                                                 |                                   |      |                                    |      |       |    |

| V <sub>DD</sub> Quiescent Current              | I <sub>DD</sub>    | LI = 0 or V <sub>DD</sub>                       | -                                 | 1.9  | 2.2                                | -    | 2.4   | mA |

| V <sub>DD</sub> Operating Current              | I <sub>DDO</sub>   | f = 50kHz                                       | -                                 | 2.0  | 2.2                                | -    | 2.5   | mA |

| V <sub>DD</sub> Operating Current              | I <sub>DDO</sub>   | f = 500kHz                                      | -                                 | 2.5  | 3.0                                | -    | 4.0   | mA |

| HB Off Quiescent Current                       | I <sub>HBL</sub>   | HI = 0                                          | -                                 | 1.25 | 1.5                                | -    | 1.8   | mA |

| HB On Quiescent Current                        | I <sub>HBH</sub>   | HI = V <sub>DD</sub>                            | -                                 | 170  | 240                                | -    | 250   | μА |

| HB Operating Current                           | I <sub>HBO</sub>   | f = 50kHz, C <sub>L</sub> = 1000pF              | -                                 | 1.45 | 1.8                                | -    | 2.0   | mA |

| HB Operating Current                           | I <sub>HBO</sub>   | f = 500kHz, C <sub>L</sub> = 1000pF             | -                                 | 2.4  | 2.8                                | -    | 3.0   | mA |

| HS Leakage Current                             | I <sub>HLK</sub>   | V <sub>HS</sub> = 80V<br>V <sub>HB</sub> = 96V  | -                                 | -    | 1                                  | -    | 1     | μА |

| V <sub>DD</sub> Rising Undervoltage Threshold  | V <sub>DDUV+</sub> |                                                 | 6.8                               | 7.6  | 8.25                               | 6.5  | 8.5   | V  |

| V <sub>DD</sub> Falling Undervoltage Threshold | V <sub>DDUV-</sub> |                                                 | 6.5                               | 7.1  | 7.8                                | 6.25 | 8.1   | V  |

| Undervoltage Hysteresis                        | UVHYS              |                                                 | 0.17                              | 0.45 | 0.75                               | 0.15 | 0.90  | V  |

| HB Undervoltage Threshold                      | VHBUV              | Referenced to HS                                | 4.8                               | 5.3  | 6.5                                | 4.0  | 7.5   | V  |

| INPUT PINS: LI and HI                          |                    |                                                 | •                                 |      |                                    |      |       | •  |

| Low Level Input Voltage                        | V <sub>IL</sub>    | Full Operating Conditions                       | 0.8                               | 1.6  | -                                  | 8.0  | -     | V  |

| High Level Input Voltage                       | V <sub>IH</sub>    | Full Operating Conditions                       | -                                 | 1.7  | 2.2                                | -    | 2.2   | V  |

| Input Voltage Hysteresis                       |                    |                                                 | -                                 | 100  | -                                  | -    | -     | mV |

| Low Level Input Current                        | I <sub>IL</sub>    | V <sub>IN</sub> = 0V, Full Operating Conditions | -70                               | -60  | -30                                | -80  | -30   | μА |

| High Level Input Current                       | l <sub>IH</sub>    | V <sub>IN</sub> = 5V, Full Operating Conditions | 30                                | 115  | 130                                | 30   | 145   | μА |

# Electrical Specifications $V_{DD} = V_{HB} = 12V$ , $V_{SS} = V_{HS} = 0V$ , No Load on LO or HO, Unless Otherwise Specified (Continued)

|                                  |                     |                        | T <sub>J</sub> = 25°C |     | T <sub>J</sub> =-40°C TO<br>125°C |     |     |       |

|----------------------------------|---------------------|------------------------|-----------------------|-----|-----------------------------------|-----|-----|-------|

| PARAMETERS                       | SYMBOL              | TEST CONDITIONS        | MIN                   | TYP | MAX                               | MIN | MAX | UNITS |

| GATE DRIVER OUTPUT PINS: LO & HO |                     |                        |                       |     |                                   |     |     |       |

| Low Level Output Voltage         | V <sub>OL</sub>     | I <sub>OUT</sub> = 0A  | -                     | -   | 0.1                               | -   | 0.1 | V     |

| High Level Output Voltage        | $V_{DD}$ - $V_{OH}$ | I <sub>OUT</sub> = 0A  | -                     | -   | 0.1                               | -   | 0.1 | V     |

| Peak Pullup Current              | I <sub>O</sub> +    | V <sub>OUT</sub> = 0V  | -                     | 1.4 | -                                 | -   | -   | Α     |

| Peak Pulldown Current            | I <sub>O</sub> -    | V <sub>OUT</sub> = 12V | -                     | 1.3 | -                                 | -   | -   | Α     |

## **Switching Specifications** $V_{DD} = V_{HB} = 12V$ , $V_{SS} = V_{HS} = 0V$ , No Load on LO or HO, Unless Otherwise Specified

|                                                             |                   | TEST                           | T <sub>J</sub> = 25°C |     | T <sub>J</sub> = -40°C<br>TO 125°C |     |     |       |

|-------------------------------------------------------------|-------------------|--------------------------------|-----------------------|-----|------------------------------------|-----|-----|-------|

| PARAMETERS                                                  | SYMBOL            | CONDITIONS                     | MIN                   | TYP | MAX                                | MIN | MAX | UNITS |

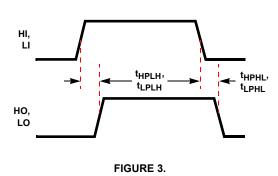

| Lower Turn-off Propagation Delay (LI Falling to LO Falling) | tLPHL             |                                | -                     | 45  | 50                                 | -   | 65  | ns    |

| Upper Turn-off Propagation Delay (HI Falling to HO Falling) | t <sub>HPHL</sub> |                                | -                     | 60  | 75                                 | -   | 90  | ns    |

| Lower Turn-on Propagation Delay (LI Rising to LO Rising)    | t <sub>LPLH</sub> |                                | -                     | 75  | 82                                 | -   | 95  | ns    |

| Upper Turn-on Propagation Delay (HI Rising to HO Rising)    | t <sub>HPLH</sub> |                                | -                     | 70  | 75                                 | -   | 95  | ns    |

| Deadtime, (t <sub>HPLH</sub> - t <sub>LPHL</sub> )          | DHt <sub>ON</sub> | LI, HI switched simultaneously | 0                     | 24  | -                                  | 0   | -   | ns    |

| Deadtime, (t <sub>LPLH</sub> - t <sub>HPHL</sub> )          | DLt <sub>ON</sub> |                                | 0                     | 17  | -                                  | 0   | -   | ns    |

| Rise Time                                                   | t <sub>R</sub>    |                                | ı                     | 5   | 20                                 | ı   | 25  | ns    |

| Fall Time                                                   | t <sub>F</sub>    |                                | -                     | 5   | 20                                 | -   | 25  | ns    |

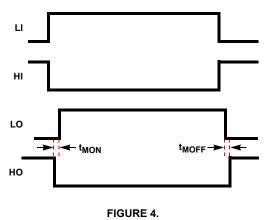

| Delay Matching: Lower Turn-On and Upper Turn-Off            | t <sub>MON</sub>  |                                | -                     | 8   | 20                                 | -   | 25  | ns    |

| Delay Matching: Lower Turn-Off and Upper Turn-On            | t <sub>MOFF</sub> |                                | -                     | -15 | 25                                 | -   | 30  | ns    |

# Pin Descriptions

| SYMBOL          | DESCRIPTION                                                                                                                                                               |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub> | Positive supply to control logic and lower gate drivers. De-couple this pin to V <sub>SS</sub> . Connect anode of bootstrap diode to this pin.                            |

| HI              | Logic level input that controls the HO output.                                                                                                                            |

| LI              | Logic level input that controls the LO output.                                                                                                                            |

| V <sub>SS</sub> | Chip negative supply, generally will be ground.                                                                                                                           |

| LO              | Low-side output. Connect to gate of low-side power MOSFET.                                                                                                                |

| HS              | High-side source connection. Connect to source of high-side power MOSFET. Connect negative side of bootstrap capacitor to this pin.                                       |

| НО              | High-side output. Connect to gate of high-side power MOSFET.                                                                                                              |

| НВ              | High-side bootstrap supply. External bootstrap diode and capacitor are required. Connect cathode of bootstrap diode and positive side of bootstrap capacitor to this pin. |

| EPAD            | Exposed pad. Connect to ground or float. The EPAD is electrically isolated from all other pins.                                                                           |

# Timing Diagrams

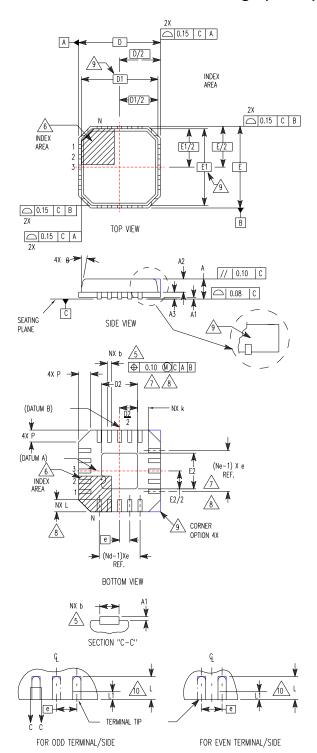

## Quad Flat No-Lead Plastic Package (QFN) Micro Lead Frame Plastic Package (MLFP)

L12.4x4

12 LEAD QUAD FLAT NO-LEAD PLASTIC PACKAGE

(COMPLIANT TO JEDEC MO-220-VGGC ISSUE C)

| SYMBOL | MIN  | NOMINAL MAX |      | NOTES |  |

|--------|------|-------------|------|-------|--|

| Α      | 0.80 | 0.90        | 1.00 | -     |  |

| A1     | -    | -           | 0.05 | -     |  |

| A2     | -    | -           | 1.00 | 9     |  |

| A3     |      | 0.20 REF    |      | 9     |  |

| b      | 0.23 | 0.28        | 0.38 | 5, 8  |  |

| D      |      | 4.00 BSC    |      | -     |  |

| D1     |      | 3.75 BSC    |      | 9     |  |

| D2     | 1.95 | 2.10        | 2.25 | 7, 8  |  |

| Е      |      | 4.00 BSC    |      |       |  |

| E1     |      | 3.75 BSC    | 9    |       |  |

| E2     | 1.95 | 2.10        | 2.25 | 7, 8  |  |

| е      |      | 0.80 BSC    |      | -     |  |

| k      | 0.25 | -           | -    | -     |  |

| L      | 0.35 | 0.60        | 0.75 | 8     |  |

| L1     | -    | -           | 0.15 | 10    |  |

| N      |      | 12          |      | 2     |  |

| Nd     |      | 3           |      |       |  |

| Ne     |      | 3           |      |       |  |

| Р      | -    | -           | 0.60 | 9     |  |

| θ      | -    | -           | 12   | 9     |  |

Rev. 1 5/03

#### NOTES:

- 1. Dimensioning and tolerancing conform to ASME Y14.5-1994.

- 2. N is the number of terminals.

- 3. Nd and Ne refer to the number of terminals on each D and E.

- 4. All dimensions are in millimeters. Angles are in degrees.

- 5. Dimension b applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

- Dimensions D2 and E2 are for the exposed pads which provide improved electrical and thermal performance.

- 8. Nominal dimensions are provided to assist with PCB Land Pattern Design efforts, see Intersil Technical Brief TB389.

- Features and dimensions A2, A3, D1, E1, P & 0 are present when Anvil singulation method is used and not present for saw singulation.

- Depending on the method of lead termination at the edge of the package, a maximum 0.15mm pull back (L1) maybe present. L minus L1 to be equal to or greater than 0.3mm.