# RENESAS

# DATASHEET

# ISL78424, ISL78434, ISL78444

100V Boot, 4A Peak, Half-Bridge Driver with Single PWM Input and Adaptive Dead Time Control

FN9357 Rev.0.00 Sep 10, 2018

The <u>ISL78424</u>, <u>ISL78434</u>, and <u>ISL78444</u> are Automotive Grade (<u>AEC-Q100</u> Grade 1) high voltage, high frequency, half-bridge NMOS FET drivers for driving the gates of up to 70V half-bridge topologies.

The family of half-bridge drivers feature 3A sourcing, 4A sinking peak gate drive current. The ISL78424 and ISL78444 feature a single tri-level PWM input for controlling both gate drivers. The ISL78434 has dual independent inputs for controlling the high-side and low-side driver separately. The ISL78424 and ISL78434 have independent sourcing and sinking pins for each gate driver while ISL78444 has a single combined sourcing/sinking output for each gate driver.

Strong gate drive strength and the Adaptive Dead Time (ADT) feature allow this family of drivers to switch high voltage, low  $r_{DS(ON)}$  power FETs in half-bridge topologies at high operating frequencies while providing shoot-through protection and minimizing dead time switching losses.

The ISL78424, ISL78434, and ISL78444 are offered in a 14 Ld HTSSOP package that complies with 100V conductor spacing per IPC-2221B. The ISL78444 is pin compatible with the ISL78420. All devices are specified across a wide ambient temperature range of -40°C to +140°C.

## **Related Literature**

For a full list of related documents, visit our website:

• ISL78424, ISL78434, ISL78444 product pages

#### Features

- Patented gate-sensed adaptive dead time control provides shoot-through protection and mimized dead time

- Unique tri-level PWM input for integration with Renesas multiphase controllers (for example, ISL78225 and ISL78226)

- 3A sourcing and 4A sinking output current

- On-chip  $3\Omega$  bootsrap FET switch

- Programmable dead time delay with single resistor

- Tri-level PWM input (ISL78424, ISL78444)

- Independent HI/LI inputs (ISL78434)

- Separate source/sink pins at driver outputs (ISL78424, ISL78434)

- Bootstrap and VDD Undervoltage Lockout (UVLO)

- Wide supply range: 8V to 18V

- Bootstrap supply maximum voltage: 100V

- Maximum phase voltage: 86V

- Minimum phase voltage: -10V

#### Applications

- Automotive half-bridge and 3-phase motor driver

- 12V to 24V and 12V to 48V bidirectional DC/DC (with ISL78226, ISL78224 controllers)

- Multi-phase boost (with ISL78220 and ISL78225 controllers)

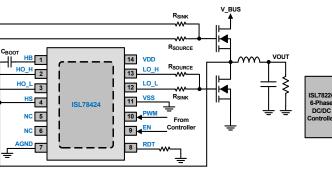

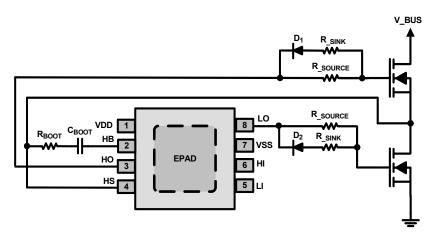

Figure 1. Independent Source and Sink Outputs for Optimizing Gate Drive Current and Adaptive Dead Time Sensing

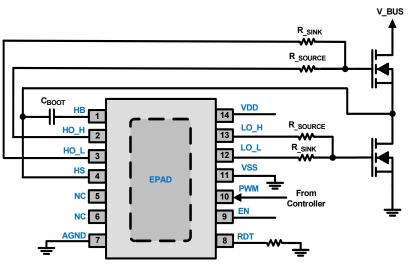

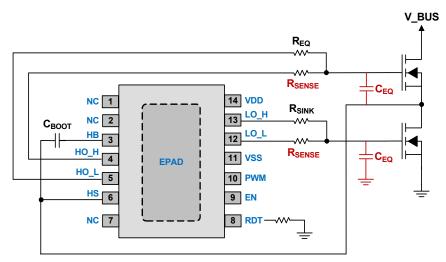

Figure 2. NMOS Half-Bridge Driver for 12V-48V Bi-Directional DC/DC Controller

# Contents

| 1.             | Overview                               | 3  |

|----------------|----------------------------------------|----|

| 1.1            | Block Diagrams                         | 3  |

| 1.2            | Ordering Information                   | 6  |

| 1.3            | Pin Configurations                     | 6  |

| 1.4            | Pin Descriptions                       | 7  |

| 2.             | Specifications                         | 8  |

| 2.1            | Absolute Maximum Ratings               |    |

| 2.2            | Thermal Information.                   |    |

| 2.3            | Recommended Operating Conditions       |    |

| 2.4            | Electrical Specifications              |    |

| 2.5            | Switching Specifications               |    |

| 2.6            | Timing Diagrams                        |    |

| 3.             | Typical Performance Curves.            | 15 |

| 4.             | Product Description.                   | 20 |

| <b></b><br>4.1 | Single PWM or Independent HI/LI Inputs |    |

| 4.2            | ISL78424 and ISL78444 PWM Input.       |    |

| 4.3            | ISL78434 HI/LI Lockout Protection      |    |

| 4.4            | Separate Source and Sink Outputs       |    |

| 4.5            | Peak Gate Drive Currents               |    |

| 4.6            | Shoot-Through Protection               |    |

| 4.7            | Shoot-Through and Dead Time            |    |

| 4.8            | Adaptive Dead Time Control (ADTC).     |    |

| 4.9            | Adaptive Dead Time and Gate Resistors. |    |

| 4.10           | •                                      |    |

| 4.11           |                                        |    |

| 4.12           | Integrated Bootstrap Switch.           | 26 |

| 4.13           | Bootstrap Capacitor                    | 26 |

| 4.14           | EN Pin                                 | 27 |

| 4.15           | UVLO Protection - VDD and Boot         | 27 |

| 5.             | Applications Information.              | 28 |

| 5.1            | Supply Voltage Operating Range         |    |

| 5.2            | Bootstrap Capacitor Design             |    |

| 5.3            | Gate Drive Limiting Resistors          |    |

| 5.4            | Adaptive Dead Time Control             |    |

| 5.5            | Adjustable Dead Time Control           |    |

| 5.6            | Power Dissipation Calculation          | 29 |

| 6.             | PCB Layout Guidelines                  | 31 |

| 7.             | Revision History.                      | 32 |

| 8.             | Package Outline Drawing                | 33 |

# 1. Overview

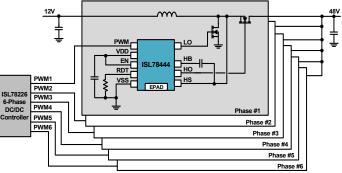

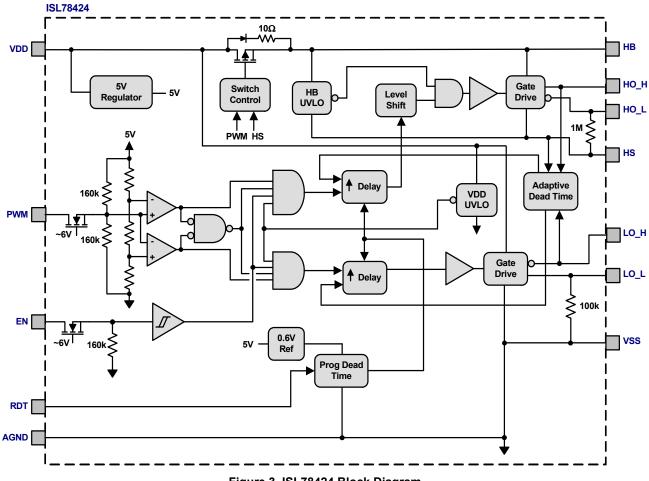

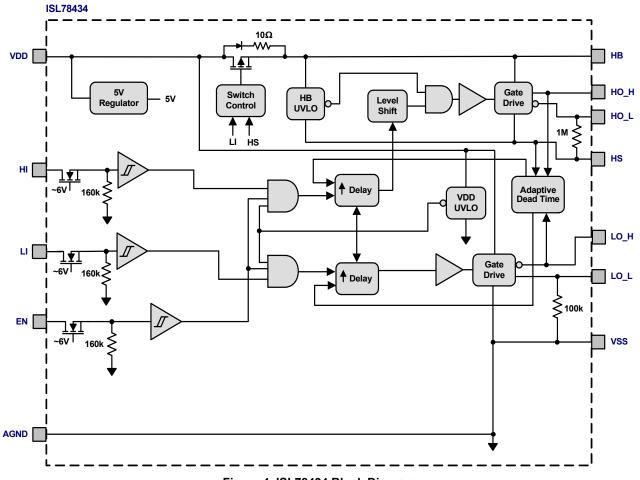

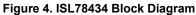

#### 1.1 Block Diagrams

Figure 3. ISL78424 Block Diagram

Figure 5. ISL78444 Block Diagram

#### 1.2 Ordering Information

| Part Number<br>( <u>Notes 2</u> , <u>3</u> ) | Part<br>Marking | Temp Range<br>(°C) | Tape and Reel<br>(Units) ( <u>Note 1</u> ) | Package<br>(RoHS Compliant) | Pkg.<br>Dwg. # |

|----------------------------------------------|-----------------|--------------------|--------------------------------------------|-----------------------------|----------------|

| ISL78424AVEZ                                 | 78424 AVEZ      | -40 to +125        | -                                          | 14 Ld HTSSOP                | M14.173B       |

| ISL78424AVEZ-T                               | 78424 AVEZ      | -40 to +125        | 2.5k                                       | 14 Ld HTSSOP                | M14.173B       |

| ISL78424AVEZ-T7A                             | 78424 AVEZ      | -40 to +125        | 250                                        | 14 Ld HTSSOP                | M14.173B       |

| ISL78434AVEZ                                 | 78434 AVEZ      | -40 to +125        | -                                          | 14 Ld HTSSOP                | M14.173B       |

| ISL78434AVEZ-T                               | 78434 AVEZ      | -40 to +125        | 2.5k                                       | 14 Ld HTSSOP                | M14.173B       |

| ISL78434AVEZ-T7A                             | 78434 AVEZ      | -40 to +125        | 250                                        | 14 Ld HTSSOP                | M14.173B       |

| ISL78444AVEZ                                 | 78444 AVEZ      | -40 to +125        | -                                          | 14 Ld HTSSOP                | M14.173B       |

| ISL78444AVEZ-T                               | 78444 AVEZ      | -40 to +125        | 2.5k                                       | 14 Ld HTSSOP                | M14.173B       |

| ISL78444AVEZ-T7A                             | 78444 AVEZ      | -40 to +125        | 250                                        | 14 Ld HTSSOP                | M14.173B       |

Notes:

1. Refer to <u>TB347</u> for details about reel specifications.

2. These Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

3. For Moisture Sensitivity Level (MSL), refer to the <u>ISL78424</u>, <u>ISL78434</u>, and <u>ISL78444</u> product information pages. For more information about MSL, refer to <u>TB363</u>.

4. These packages are in compliance with 100V conductor spacing guidelines per IPC-2221.

#### Table 1. Key Differences Between Family of Parts

| Part Number | Input | Driver Output Pins                                                   | Adaptive Dead Time Control |

|-------------|-------|----------------------------------------------------------------------|----------------------------|

| ISL78424    | PWM   | HO_H: High-Side Source                                               | Yes                        |

| ISL78434    | HI/LI | HO_L: High-side Sink<br>LO_H: Low-Side Source<br>LO_L: Low-Side Sink | Yes                        |

| ISL78444    | PWM   | HO: High-Side Source and Sink<br>LO: Low-Side Source and Sink        | Yes                        |

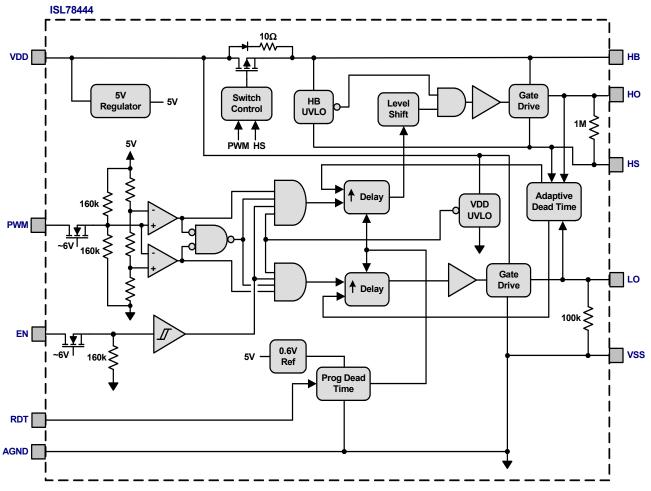

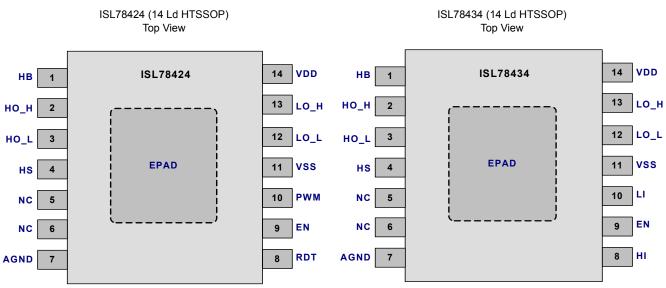

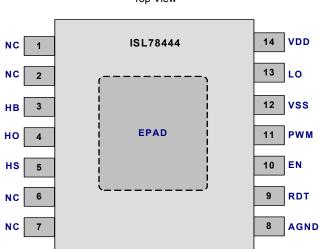

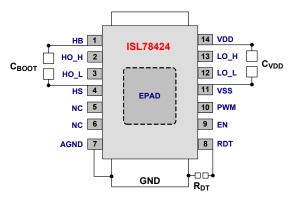

## 1.3 Pin Configurations

# 1.4 Pin Descriptions

| ISL78424 | ISL78434 | ISL78444   | Symbol | Description                                                                                                                                                                                                                                                                                |

|----------|----------|------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | 1        | 3          | HB     | High-side bootstrap supply voltage referenced to HS. Connect boot cap from HB to HS.                                                                                                                                                                                                       |

| -        | -        | 4          | НО     | High-side driver output. Connect to gate of high-side NFET.                                                                                                                                                                                                                                |

| 2        | 2        | -          | НО_Н   | High-side driver source output. Connect to gate of high-side NFET. This pin is also the sense input for high-side adaptive dead time control.                                                                                                                                              |

| 3        | 3        | -          | HO_L   | High-side driver sink output. Connect to gate of high-side NFET.                                                                                                                                                                                                                           |

| 4        | 4        | 5          | HS     | High-side driver reference. Connect to source of high-side NFET.                                                                                                                                                                                                                           |

| 7        | 7        | 8          | AGND   | Analog ground pin. Connect to VSS through EPAD.                                                                                                                                                                                                                                            |

| -        | 8        | -          | HI     | High-side gate driver logic input. 3V and 5V logic compatible.                                                                                                                                                                                                                             |

| 8        | -        | 9          | RDT    | Adjustable dead time delay pin. Connect a resistor to ground to increase the dead time delay in addition to the adaptive dead time control. See <u>"Adjustable Dead Time Delay</u> ( <u>RDT Pin)" on page 25</u> for more information.                                                     |

| 9        | 9        | 10         | EN     | Driver enable. When high, the driver outputs respond to input logic control. When low, the low-side driver sink output is active and the high-side driver sink output has a $1M\Omega$ impedance to HS to keep the half bridge NFETs off.                                                  |

| -        | 10       | -          | LI     | Low-side gate driver logic input. 3V and 5V logic compatible.                                                                                                                                                                                                                              |

| 10       | -        | 11         | PWM    | Tri-Level PWM input for controlling the driver outputs.                                                                                                                                                                                                                                    |

| 11       | 11       | 12         | VSS    | Low-side driver reference. Connect to AGND through EPAD. Connect to source of low-side NFET.                                                                                                                                                                                               |

| -        | -        | 13         | LO     | Low-side driver output. Connect to gate of low-side NFET.                                                                                                                                                                                                                                  |

| 12       | 12       | -          | LO_L   | Low-side driver sink output. Connect to gate of low-side NFET.                                                                                                                                                                                                                             |

| 13       | 13       | -          | LO_H   | Low-side driver source output. Connect to gate of low-side NFET. This pin is also the sense input for the low-side adaptive dead time control.                                                                                                                                             |

| 14       | 14       | 14         | VDD    | Supply voltage for internal bias circuitry and low-side driver source output.                                                                                                                                                                                                              |

| 5, 6     | 5, 6     | 1, 2, 6, 7 | NC     | No connect. This pin is not internally connected.                                                                                                                                                                                                                                          |

| EPAD     |          |            |        | Bottom side thermal pad is not electrically connected internally. Connect VSS and AGND pins together with EPAD on PCB. Connect EPAD PCB to ground plane with as many vias as possible for optimum thermal performance. See <u>"PCB Layout Guidelines" on page 31</u> for more information. |

# 2. Specifications

#### 2.1 Absolute Maximum Ratings

All voltages referenced to  $\mathsf{V}_{\mathsf{SS}}$  unless otherwise specified.

| Parameter                                      | Minimum               | Minimum Maximum       |      |  |

|------------------------------------------------|-----------------------|-----------------------|------|--|

| Supply Voltage, V <sub>DD</sub> , HB-HS        | -0.3                  | -0.3 20               |      |  |

| PWM, HI, LI and EN Voltage                     | -0.3                  | V <sub>DD</sub> + 0.3 | V    |  |

| RDT Voltage                                    | -0.3                  | 5                     | V    |  |

| Voltage on LO                                  | -0.3                  | V <sub>DD</sub> + 0.3 | V    |  |

| Voltage on HO (Referenced to HS)               | V <sub>HS</sub> - 0.3 | V <sub>HB</sub> + 0.3 | V    |  |

| Voltage on HB                                  |                       | 100                   | V    |  |

| Voltage on HS                                  | -1                    | 86                    | V    |  |

| Average Current in VDD to HB FET               |                       | 100                   | mA   |  |

| ESD Rating                                     | Va                    | alue                  | Unit |  |

| Human Body Model (Tested per AEC-Q100-002)     | 2                     | 2.5                   |      |  |

| Charged Device Model (Tested per AEC-Q100-011) |                       | 1                     |      |  |

| Latch-Up (Tested per AEC-A100-004)             | 1                     | 00                    | mA   |  |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

## 2.2 Thermal Information

| Thermal Resistance (Typical)      | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|-----------------------------------|------------------------|------------------------|

| 14 Ld HTSSOP Package (Notes 5, 6) | 35                     | 2.5                    |

Notes:

5. θ<sub>JA</sub> is measured in free air with the component mounted on a high-effective thermal conductivity test board with "direct attach" features. See <u>TB379</u>.

6. For  $\theta_{JC},$  the "case temp" location is the center of the exposed metal pad on the package underside.

| Parameter                                      | Minimum | Maximum        | Unit |

|------------------------------------------------|---------|----------------|------|

| Maximum Power Dissipation at +25°C in Free Air |         | 3.5            | W    |

| Storage Temperature Range                      | -65     | +150           | °C   |

| Junction Temperature Range                     | -55     | +150           | °C   |

| Pb-Free Reflow Profile                         |         | Refer to TB493 |      |

## 2.3 Recommended Operating Conditions

| Parameter                                            | Minimum | Maximum | Unit |

|------------------------------------------------------|---------|---------|------|

| Supply Voltage, V <sub>DD</sub>                      | 8       | 18      | V    |

| Voltage on HS                                        | -0.7    | 70      | V    |

| Voltage on HS (Negative repetitive transient <100ns) |         | -10     | V    |

| Voltage on HB (Referenced to HS)                     | 8       | 18      | V    |

| Voltage on HB (Referenced to VSS)                    |         | 86      | V    |

| HS Slew Rate                                         |         | <50     | V/ns |

| Junction Temperature                                 | -40     | +140    | °C   |

## 2.4 Electrical Specifications

Unless otherwise specified:  $V_{DD}$  = 12V,  $V_{SS}$  = AGND = HS = 0V, HB = HS+VDD, EN = 5V, PWM = 2.5V, HI = LI = 0V, 10k $\Omega$  resistor on RDT pin to AGND. No load on LO or HO. Typical parameters for  $T_J$  = +25°C. Boldface limits apply across the ambient operating temperature range, -40°C to +140°C.

| Parameters                        | Symbol               | Test Conditions                                                                                                                   | Min<br>( <u>Note 7</u> ) | Тур | Max<br>( <u>Note 7</u> ) | Unit |

|-----------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----|--------------------------|------|

| Supply Currents                   |                      | •                                                                                                                                 | •                        |     | •                        |      |

| V <sub>DD</sub> Quiescent Current | I <sub>DD1</sub>     | $R_{DT} = 0\Omega$ to AGND                                                                                                        | -                        | 500 | 800                      | μA   |

|                                   | I <sub>DD2</sub>     | $R_{DT}$ = 10k $\Omega$ to AGND, ISL78424 and ISL78444 only                                                                       | -                        | 650 | 830                      | μA   |

| V <sub>DD</sub> Operating Current | I <sub>DDO1</sub>    | PWM 0V to 5V<br>HI and LI 0V to 5V<br>$f_{PWM}$ = 500kHz, 50% duty cycle<br>$R_{DT}$ = 0Ω to AGND; V <sub>HS</sub> = 5V           | -                        | 6.6 | 11.8                     | mA   |

| ( Dischled Ourset                 | I <sub>DDO2</sub>    | PWM 0V to 5V<br>ISL78424 and ISL78444 only<br>$f_{PWM}$ = 500kHz, 50% duty cycle<br>$R_{DT}$ = 10kΩ to AGND; V <sub>HS</sub> = 5V | -                        | 6.8 | 11.9                     | mA   |

| V <sub>DD</sub> Disabled Current  | I <sub>DDSD</sub>    | EN = 0V                                                                                                                           | -                        | 170 | 360                      | μΑ   |

| HB to HS Quiescent Current        | I <sub>HBQ</sub>     | PWM = 12V; HI = 12V                                                                                                               | -                        | 250 | 320                      | μΑ   |

| HB to HS Operating Current        | І <sub>нво</sub>     | $f_{\text{PWM}} = 500 \text{kHz}, 50\% \text{ duty cycle}$<br>PWM = 2.5V  to  5V<br>$HI \text{ 0V to } 5V; V_{\text{HS}} = 5V$    | -                        | 5.4 | 10                       | mA   |

| HB to $V_{SS}$ Leakage Current    | I <sub>HBSLeak</sub> | V <sub>HB</sub> = V <sub>HS</sub> = 70V                                                                                           | -                        | 50  | 80                       | μA   |

| HB to $V_{SS}$ Bias Current       | I <sub>HBSBias</sub> | $I_{HBSBias} = I_{HB} - I_{HS}$<br>$V_{DD} = 16V; V_{HB} = 86V; V_{HS} = 70V;$<br>PWM = 5V; HI = 5V                               | -                        | 125 | 150                      | μA   |

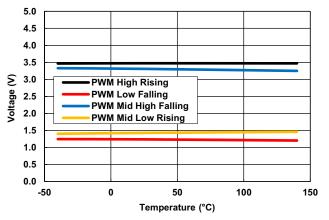

| Tri-Level PWM Input               |                      | ·                                                                                                                                 |                          | •   | •                        |      |

| High Level Rising Threshold       | V <sub>PWMH</sub>    |                                                                                                                                   | -                        | 3.5 | 3.8                      | V    |

| Middle Level Range                | V <sub>MIDH</sub>    | Middle level upper limit                                                                                                          | 3.0                      | 3.3 | -                        | V    |

|                                   | V <sub>MIDL</sub>    | Middle level lower limit                                                                                                          | -                        | 1.5 | 1.65                     | V    |

| Middle Level Hysteresis           |                      |                                                                                                                                   | -                        | 200 | -                        | mV   |

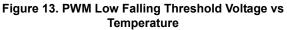

| Low Level Falling Threshold       | V <sub>PWML</sub>    |                                                                                                                                   | 0.8                      | 1.2 | -                        | V    |

| Logic High and Low Input Current  | I <sub>PWM_IH</sub>  | V <sub>PWM</sub> = 5V; Sourcing                                                                                                   | 20                       | 30  | 45                       | μA   |

|                                   | I <sub>PWM_IL</sub>  | V <sub>PWM</sub> = 0V; Sinking                                                                                                    | 10                       | 24  | 35                       | μA   |

| Open Circuit Voltage              | V <sub>float</sub>   | No load on PWM pin                                                                                                                | 2.35                     | 2.5 | 2.55                     | V    |

| PWM Middle Level Resistors        | R <sub>mid</sub>     | Pull-up resistor to internal reference<br>and pull-down resistor to AGND                                                          | -                        | 165 | -                        | kΩ   |

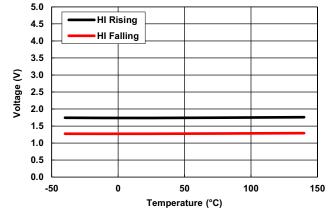

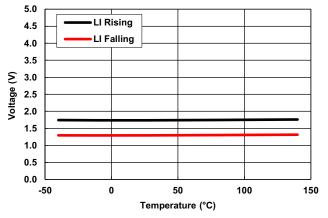

| HI/LI Input                       | -                    |                                                                                                                                   |                          |     |                          |      |

| High Level Threshold              | V <sub>IH</sub>      |                                                                                                                                   | -                        | 1.7 | 2.1                      | V    |

| Low Level Threshold               | V <sub>IL</sub>      |                                                                                                                                   | 1.0                      | 1.3 | -                        | V    |

| Input Hysteresis                  |                      |                                                                                                                                   | -                        | 400 | -                        | mV   |

| HI/LI Pin Pull-Down Resistance    | R <sub>HI_LI</sub>   | HI = LI = 5V                                                                                                                      | 100                      | 175 | 320                      | kΩ   |

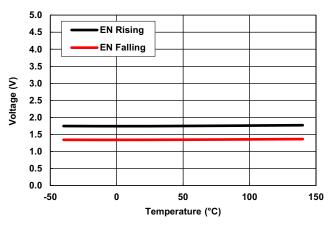

| EN Input                          |                      |                                                                                                                                   |                          |     |                          |      |

| High Level Threshold              | V <sub>ENH</sub>     |                                                                                                                                   | -                        | 1.7 | 2.1                      | V    |

| Low Level Threshold               | V <sub>ENL</sub>     |                                                                                                                                   | 1.0                      | 1.3 | -                        | V    |

| EN Input Hysteresis               |                      |                                                                                                                                   | -                        | 400 | -                        | mV   |

Unless otherwise specified:  $V_{DD}$  = 12V,  $V_{SS}$  = AGND = HS = 0V, HB = HS+VDD, EN = 5V, PWM = 2.5V, HI = LI = 0V, 10k $\Omega$  resistor on RDT pin to AGND. No load on LO or HO. Typical parameters for  $T_J$  = +25°C. Boldface limits apply across the ambient operating temperature range, -40°C to +140°C. (Continued)

| Parameters                       | Symbol               | Test Conditions                                                                                                                                                            | Min<br>( <u>Note 7</u> ) | Тур  | Max<br>( <u>Note 7</u> ) | Unit |

|----------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|--------------------------|------|

| EN Pin Pull-Down Resistor        | R <sub>EN</sub>      | EN = 5V                                                                                                                                                                    | 100                      | 175  | 260                      | kΩ   |

| Enable High Delay                | t <sub>en_h_lo</sub> | From $V_{ENH}$ to transition at LO;<br>PWM = 0V, ISL78424 and ISL78444;<br>LI = 5V, HI = 0V, for ISL78434                                                                  | -                        | 3    | 5.275                    | μs   |

|                                  | t <sub>en_h_ho</sub> | From $V_{ENH}$ to transition at HO;<br>PWM = 5V, ISL78424 and ISL78444;<br>LI = 0V, HI = 5V, for ISL78434                                                                  | -                        | 3    |                          | μs   |

| Enable Low Delay                 | t <sub>en_l_ho</sub> | From $V_{ENL}$ to transition at HO;<br>PWM = 5V, ISL78424 and ISL78444;<br>LI = 0V, HI = 5V, for ISL78434                                                                  | -                        | 0.8  |                          | μs   |

|                                  | t <sub>EN_L_LO</sub> | From $V_{ENL}$ to transition at LO;<br>PWM = 0V, ISL78424 and ISL78444;<br>LI = 5V, HI = 0V, for ISL78434                                                                  | -                        | 0.8  | 1.7                      | μs   |

| V <sub>DD</sub> Start-Up Delay   | t <sub>VDD</sub>     | $\label{eq:entropy} \begin{split} &EN=V_{DD};\\ &ISL78424, ISL78444 \;PWM=0V;\\ &ISL78434 \;HI=0V, LI=V_{DD};\\ &V_{DD} \;crossing \;V_{DDR} \;to\;LO\;rising \end{split}$ | -                        | 20   | -                        | μs   |

| Undervoltage Protection          |                      |                                                                                                                                                                            |                          |      |                          |      |

| V <sub>DD</sub> Rising Threshold | V <sub>DDR</sub>     |                                                                                                                                                                            | 6.8                      | 7.2  | 7.7                      | V    |

| V <sub>DD</sub> UVLO Hysteresis  | V <sub>DDH</sub>     |                                                                                                                                                                            | -                        | 0.7  | -                        | V    |

| HB Rising Threshold              | V <sub>HBR</sub>     |                                                                                                                                                                            | 6                        | 7    | 7.8                      | V    |

| HB UVLO Hysteresis               | V <sub>HBH</sub>     |                                                                                                                                                                            | -                        | 0.5  | -                        | V    |

| Bootstrap FET Switch             | <u>.</u>             |                                                                                                                                                                            |                          |      |                          |      |

| Low Current Forward Voltage      | V <sub>DL</sub>      | Ι <sub>VDD-HB</sub> = 100μΑ                                                                                                                                                | -                        | 1    | -                        | mV   |

| High Current Forward Voltage     | V <sub>DH</sub>      | I <sub>VDD-HB</sub> = 100mA                                                                                                                                                | -                        | 0.3  | 1                        | V    |

| VDD to HB Resistance             | R <sub>BOOT</sub>    | I <sub>BOOT</sub> out of HB pin = 100mA                                                                                                                                    | 1                        | 3    | 6                        | Ω    |

| LO Gate Driver                   |                      |                                                                                                                                                                            |                          |      |                          | •    |

| Output Low Voltage               | V <sub>LOL</sub>     | I <sub>LO</sub> = 100mA sink                                                                                                                                               | -                        | 100  | 225                      | mV   |

| Output High Voltage              | V <sub>LOH</sub>     | $I_{LO}$ = 100mA source;<br>Voltage below V <sub>DD</sub> rail:<br>V <sub>OHL</sub> = V <sub>DD</sub> - V <sub>LO</sub>                                                    | -                        | 170  | 325                      | mV   |

| Peak Pull-Up Current             | I <sub>LOH</sub>     | V <sub>LO</sub> = 0V; T = +25°C                                                                                                                                            | -                        | 4    | -                        | Α    |

|                                  |                      | V <sub>LO</sub> = 0V; T = +85°C                                                                                                                                            | -                        | 3.75 | -                        | Α    |

|                                  |                      | V <sub>LO</sub> = 0V; T = +140°C                                                                                                                                           | -                        | 3.5  | -                        | Α    |

| Peak Pull-Down Current           | I <sub>LOL</sub>     | V <sub>LO</sub> = 12V; T = +25°C                                                                                                                                           | -                        | 4.5  | -                        | Α    |

|                                  |                      | V <sub>LO</sub> = 12V; T = +85°C                                                                                                                                           | -                        | 4    | -                        | Α    |

|                                  |                      | V <sub>LO</sub> = 12V; T = +140°C                                                                                                                                          | -                        | 3.5  | -                        | Α    |

| HO Gate Driver                   |                      | ·                                                                                                                                                                          | •                        |      | •                        | -    |

| Output Low Voltage               | V <sub>HOH</sub>     | I <sub>HO</sub> = 100mA sink                                                                                                                                               | -                        | 100  | 225                      | mV   |

| Output High Voltage              | V <sub>HOL</sub>     | $I_{HO}$ = 100mA source<br>Voltage below V <sub>HB</sub> rail:<br>V <sub>OHH</sub> = V <sub>HB</sub> - V <sub>HO</sub>                                                     | -                        | 170  | 325                      | mV   |

Unless otherwise specified:  $V_{DD}$  = 12V,  $V_{SS}$  = AGND = HS = 0V, HB = HS + VDD, EN = 5V, PWM = 2.5V, HI = LI = 0V, 10k $\Omega$  resistor on RDT pin to AGND. No load on LO or HO. Typical parameters for T<sub>J</sub> = +25°C. Boldface limits apply across the ambient operating temperature range, -40°C to +140°C. (Continued)

| Parameters                                                                  | Symbol               | Test Conditions                                     | Min<br>( <u>Note 7</u> ) | Тур  | Max<br>( <u>Note 7</u> ) | Unit |

|-----------------------------------------------------------------------------|----------------------|-----------------------------------------------------|--------------------------|------|--------------------------|------|

| Peak Pull-Up Current                                                        | I <sub>HOH</sub>     | $V_{LO} = 0V; T = +25^{\circ}C$                     | -                        | 3.75 | -                        | А    |

|                                                                             |                      | V <sub>LO</sub> = 0V; T = +85°C                     | -                        | 3.5  | -                        | А    |

|                                                                             |                      | V <sub>LO</sub> = 0V; T = +140°C                    | -                        | 3.25 | -                        | А    |

| Peak Pull-Down Current                                                      | I <sub>HOL</sub>     | V <sub>LO</sub> = 12V; T = +25°C                    | -                        | 4.5  | -                        | А    |

|                                                                             |                      | V <sub>LO</sub> = 12V; T = +85°C                    | -                        | 4    | -                        | А    |

|                                                                             |                      | V <sub>LO</sub> = 12V; T = +140°C                   | -                        | 3.5  | -                        | А    |

| Adaptive Dead Time Control Threshold Voltage                                |                      |                                                     |                          |      |                          |      |

| LO or LO_H Threshold Voltage Relative to $V_{SS}$                           | V <sub>ADTC_LO</sub> | Falling edge on LO                                  | -                        | 1.3  | -                        | V    |

| HO or HO_H Threshold Voltage Relative to HS (Gate Sense Threshold)          | V <sub>ADTC_HO</sub> | Falling edge on HO                                  | -                        | 1.0  | -                        | V    |

| HS Threshold Voltage Relative to V <sub>SS</sub><br>(Phase Sense Threshold) | V <sub>ADTC_HS</sub> | Falling edge on HS;<br>HO-HS > V <sub>ADTC_HO</sub> | -                        | 0.5  | -                        | V    |

## 2.5 Switching Specifications

Unless otherwise specified:  $V_{DD}$  = 12V,  $V_{SS}$  = AGND = HS = 0V, HB = HS+VDD, PWM = 0V to 5V or HI/LI = 0V to 5V switching. No load on LO or HO. Typical parameters for  $T_J$  = +25°C. Boldface limits apply across the operating temperature range, -40°C to +140°C.

| Parameters                                   | Symbol             | Test Conditions                                                                                                                                               | Min<br>( <u>Note 7</u> ) | Тур | Max<br>( <u>Note 7</u> ) | Unit |

|----------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----|--------------------------|------|

| HO Turn-Off Propagation Delay                | t <sub>PDHO</sub>  | PWM falling to HO falling                                                                                                                                     | 29                       | 45  | 75                       | ns   |

| LO Turn-Off Propagation Delay                | t <sub>PDLO</sub>  | PWM rising to LO falling                                                                                                                                      | 35                       | 45  | 66                       | ns   |

| PWM Propagation Delay Matching               |                    | t <sub>PDHO</sub> - t <sub>PDLO</sub>                                                                                                                         | -10                      | 0   | 10                       | ns   |

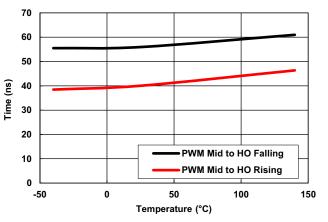

| HO Turn-Off Propagation Delay                | t <sub>PDHO1</sub> | PWM entering mid-level state to HO falling<br>PWM = 5V to 2.5V<br>$R_{DT} = 0\Omega$ to AGND                                                                  | 45                       | 55  | 75                       | ns   |

| HO Turn-On Propagation Delay                 | t <sub>PDHO2</sub> | PWM exiting mid-level state to HO rising<br>PWM = 2.5V to 5V;<br>$R_{DT}$ = 0Ω to AGND                                                                        | 25                       | 40  | 60                       | ns   |

| LO Turn-Off Propagation Delay                | t <sub>PDLO1</sub> | $\begin{array}{l} \mbox{PWM entering mid-level state to LO falling} \\ \mbox{PWM = 0V to 2.5V} \\ \mbox{R}_{\mbox{DT}} = 0\Omega \mbox{ to AGND} \end{array}$ | 50                       | 65  | 80                       | ns   |

| LO Turn-On Propagation Delay                 | t <sub>PDLO2</sub> | PWM exiting mid-level state to LO rising<br>PWM = 2.5V to 0V<br>$R_{DT}$ = 0Ω to AGND                                                                         | 34                       | 45  | 61                       | ns   |

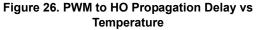

| HO Turn-Off Propagation Delay                | t <sub>PDHI1</sub> | HI falling to HO falling<br>LI = 0V                                                                                                                           | 27                       | 45  | 60                       | ns   |

| LO Turn-Off Propagation Delay                | t <sub>PDLI1</sub> | LI Falling to LO Falling<br>HI = 0V                                                                                                                           | 34                       | 45  | 56                       | ns   |

| HI and LI Falling Propagation Delay Matching |                    | t <sub>PDHI1</sub> - t <sub>PDLI1</sub>                                                                                                                       | -10                      | 0   | 10                       | ns   |

| HO Turn-On Propagation Delay                 | t <sub>PDHI2</sub> | HI rising to HO rising<br>LI = 0V                                                                                                                             | 18                       | 28  | 47                       | ns   |

| LO Turn-On Propagation Delay                 | t <sub>PDLI2</sub> | LI rising to LO rising<br>HI = 0V                                                                                                                             | 27                       | 35  | 51                       | ns   |

| HI and LI Rising Propagation Delay Matching  |                    | t <sub>PDH12</sub> - t <sub>PDL12</sub>                                                                                                                       | -15                      | -7  | -1                       | ns   |

Unless otherwise specified:  $V_{DD}$  = 12V,  $V_{SS}$  = AGND = HS = 0V, HB = HS+VDD, PWM = 0V to 5V or HI/LI = 0V to 5V switching. No load on LO or HO. Typical parameters for  $T_J$  = +25°C. Boldface limits apply across the operating temperature range, -40°C to +140°C. (Continued)

| Parameters                                                                         | Symbol                               | Test Conditions                                                                                                   | Min<br>( <u>Note 7</u> ) | Тур | Max<br>( <u>Note 7</u> ) | Unit |

|------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------|-----|--------------------------|------|

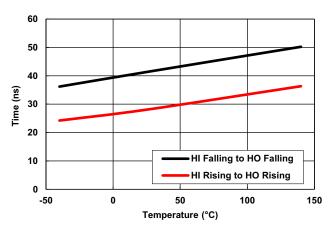

| Minimum Dead Time Delay ( <u>Note 8)</u><br>Includes ISL78434                      | t <sub>DTLHmin</sub><br>(LO Sense)   | LO falling to HO rising $R_{DT} = 0\Omega$ to AGND                                                                | 50                       | 70  | 100                      | ns   |

|                                                                                    | t <sub>DTHLmin</sub><br>(HO Sense)   | HO falling to LO rising HS = 5V, $R_{DT}$ = 0 $\Omega$ to AGND                                                    | 60                       | 85  | 130                      | ns   |

|                                                                                    | t <sub>DTHSmin</sub><br>(HS Sense)   | ISL78424 and ISL78434 only<br>HS falling to LO rising<br>HO_H-HS > $V_{ADTC_HO}$<br>$R_{DT}$ = 0 $\Omega$ to AGND | 150                      | 210 | 325                      | ns   |

| Low Range Resistor Delay ( <u>Note 8</u> )<br>(ISL78424 and ISL78444 only)         | t <sub>DTLH_10k</sub><br>(LO Sense)  | LO falling to HO rising $R_{DT}$ = 10k $\Omega$ to AGND                                                           | 89                       | 110 | 142                      | ns   |

|                                                                                    | t <sub>DTHL_10k</sub><br>(HO Sense)  | HO falling to LO rising<br>HS = 5V<br>R <sub>DT</sub> = 10kΩ to AGND                                              | 108                      | 125 | 150                      | ns   |

|                                                                                    | t <sub>DTHS_10k</sub><br>(HS Sense)  | ISL78424 only<br>HS falling to LO Rising<br>HO_H-HS > V <sub>ADTC_HO</sub><br>R <sub>DT</sub> = 10kΩ to AGND      | 190                      | 250 | 350                      | ns   |

| Mid Range Resistor Delay ( <u>Note 8)</u><br>(ISL78424 and ISL78444 only)          | t <sub>DTLH_65k</sub><br>(LO Sense)  | LO falling to HO rising $R_{DT}$ = 100k $\Omega$ to AGND                                                          | 250                      | 290 | 335                      | ns   |

|                                                                                    | t <sub>DTHL_65k</sub><br>(HO Sense)  | HO falling to LO rising<br>HS = 5V<br>R <sub>DT</sub> = 100kΩ to AGND                                             | 265                      | 300 | 340                      | ns   |

|                                                                                    | t <sub>DTHS_65k</sub><br>(HS Sense)  | ISL78424 only<br>HS falling to LO rising<br>HO_H-HS > $V_{ADTC_HO}$<br>R <sub>DT</sub> = 100kΩ to AGND            | 385                      | 440 | 542                      | ns   |

| High Range Resistor Delay ( <u>Note 8</u> )<br>(ISL78424 and ISL78444 only)        | t <sub>DTLH_100k</sub><br>(LO Sense) | LO falling to HO rising<br>$R_{DT} = 100k\Omega$ to AGND                                                          | -                        | 405 | -                        | ns   |

|                                                                                    | t <sub>DTHL_100k</sub><br>(HO Sense) | HO falling to LO rising<br>HS = 5V<br>R <sub>DT</sub> = 100kΩ to AGND                                             | -                        | 430 | -                        | ns   |

|                                                                                    | t <sub>DTHS_100k</sub><br>(HS Sense) | ISL78424 only<br>HS falling to LO rising<br>HO_H-HS > V <sub>ADTC_HO</sub><br>R <sub>DT</sub> = 100kΩ to AGND     | -                        | 550 | -                        | ns   |

| Dead Time Delay Matching ( <u>Note 8</u> )<br>LO Gate Sense to HO Gate Sense Delay | t <sub>MATCHmin</sub>                | R <sub>DT</sub> = 0Ω to AGND<br>(t <sub>DTHLmin</sub> - t <sub>DTLHmin</sub> )                                    | -38                      | -15 | 15                       | ns   |

| Matching                                                                           | t <sub>MATCH_10k</sub>               | R <sub>DT</sub> = 10kΩ to AGND<br>(t <sub>DTHL_10k</sub> - t <sub>DTLH_10k</sub> )<br>ISL78424 and ISL78444 only  | -38                      | -12 | 13                       | ns   |

|                                                                                    | t <sub>MATCH_65k</sub>               | R <sub>DT</sub> = 65kΩ to AGND<br>(t <sub>DTHL_65k</sub> - t <sub>DTLH_65k</sub> )<br>ISL78424 and ISL78444 only  | -38                      | -13 | 10                       | ns   |

| Either Output Rise/Fall Time<br>(10% to 90%/90% to 10%)                            | t <sub>RC</sub> ,t <sub>FC</sub>     | C <sub>L</sub> = 1nF                                                                                              | -                        | 10  | -                        | ns   |

| Minimum Input Pulse Width for Output to                                            | t <sub>min</sub>                     | ISL78424, ISL78444                                                                                                | -                        | 50  | -                        | ns   |

| Respond                                                                            |                                      | ISL78434                                                                                                          | -                        | 50  | -                        | ns   |

Notes:

7. Compliance to datasheet limits is assured by one or more methods: production test, characterization, and/or design.

8. Dead Time is defined as the period of time between LO falling and HO rising or between HO falling and LO rising.

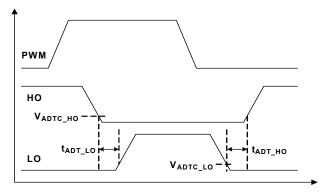

#### 2.6 Timing Diagrams

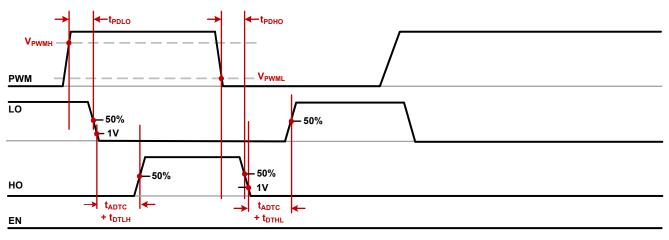

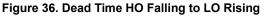

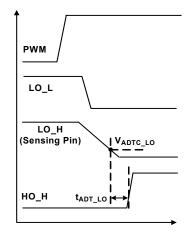

Figure 6. ISL78424, ISL78444

#### Notes:

- 9. Rise and Fall Times on PWM signal are shown exaggerated.

- 10. Timing Diagrams are with HS =  $V_{SS}$  = 0V

- 11. For ISL78424, HO\_H shorted to HO\_L and represented as HO; LO\_H shorted to LO\_L and represented as LO

- 12. t<sub>ADTC</sub>: Adaptive dead time control delay from LO or HO falling below V<sub>ADTC</sub>

- 13. t<sub>DTLH</sub> and t<sub>DTHL</sub> is adjustable dead time delay. See <u>"Adjustable Dead Time Delay (RDT Pin)" on page 25</u> for more information.

- 14. For R<sub>DT</sub> = 0V the adjustable dead time control is disabled and t<sub>DTLH</sub> = t<sub>DTHL</sub> = 0ns

- 15. t<sub>ADTC</sub> + t<sub>DTLH</sub>: Dead time delay from LO falling to HO rising. Measured from 1V on LO to 50% of HO.

- 16. t<sub>ADTC</sub> + t<sub>DTHL</sub>: Dead time delay from HO falling to LO rising. Measured from 1V on HO to 50% of LO.

- 17. t<sub>PDLO</sub>: Propagation delay from PWM rising to LO falling. Measured from PWM = 3.8V to 50% of LO.

- 18. t<sub>PDHO</sub>: Propagation delay from PWM falling to HO falling. Measured from PWM = 0.8V to 50% of HO.

- 19. t<sub>PDL01</sub>: Propagation delay from PWM entering tri-level state to LO falling. Measured from PWM = 1.6V to 50% of LO.

- 20. t<sub>PDLO2</sub>: Propagation delay from PWM exiting tri-level state to LO rising. Measured from PWM = 0.8V to 50% of LO.

- 21. t<sub>PDH01</sub>: Propagation delay from PWM entering tri-level state to HO falling. Measured from PWM = 3.0V to 50% of HO.

- 22. t<sub>PDH02</sub>: Propagation delay from PWM exiting tri-level state to HO rising. Measured from PWM = 3.8V to 50% of HO.

- 23.  $t_{ENL}$ : Disable delay time from EN falling. Measured from V<sub>ENL</sub> to 50% falling on LO with PWM = 0V.

- 24.  $t_{ENH}$ : Enable delay time from EN rising. Measured from  $V_{ENH}$  to 50% rising on LO with PWM = 0V.

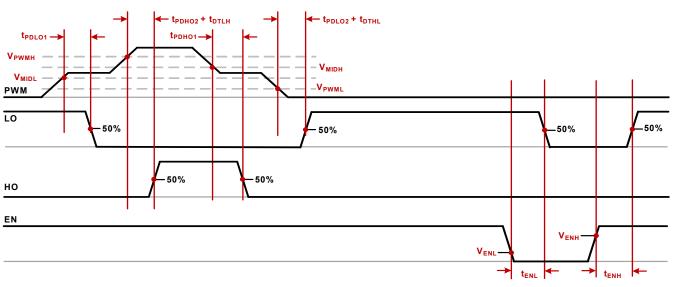

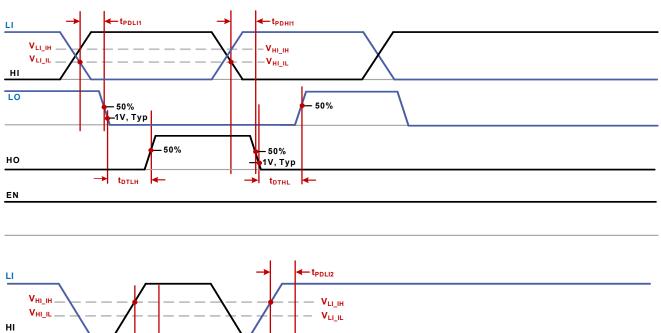

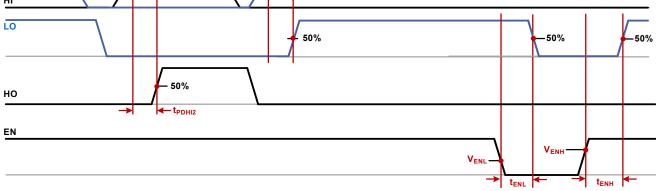

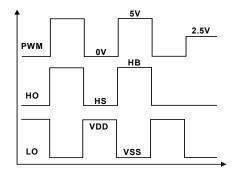

#### Figure 7. ISL78434

Notes:

- 25. Rise and fall times on HI and LI signal are shown exaggerated.

- 26. Timing diagrams are with HS =  $V_{SS}$  = 0V

- 27. For ISL78434, HO\_H shorted to HO\_L and represented as HO; LO\_H shorted to LO\_L and represented as LO

- 28. t<sub>DTLH</sub>: Adaptive dead time delay from LO falling to HO rising. Measured from 1V on LO to 50% of HO.

- 29. t<sub>DTHL</sub>: Adaptive dead time delay from HO falling to LO rising. Measured from 1V on HO to 50% of LO.

- 30. t<sub>PDL11</sub>: Propagation delay from LI falling to LO falling. Measured from LI = 1.0V to 50% of LO.

- 31. t<sub>PDH11</sub>: Propagation delay from HI falling to HO falling. Measured from HI = 1.0V to 50% of HO.

- 32.  $t_{PDLI2}$ : Propagation delay from LI rising to LO rising. Measured from LI = 2.1V to 50% of LO with HI = 0 for >1µs before LI rising.

- 33. t<sub>PDHI2</sub>: Propagation delay from HI rising to HO rising. Measured from HI = 2.1V to 50% of HO with LI = 0 for >1µs before HI rising.

- 34.  $t_{ENL}$ : Disable delay time from EN falling. Measured from V<sub>ENL</sub> to 50% falling on LO with LI = 5V.

- 35.  $t_{ENH}$ : Enable delay time from EN rising. Measured from  $V_{ENH}$  to 50% rising on LO with LI = 5V.

# 3. Typical Performance Curves

Unless otherwise stated, typical performance curves are taken with conditions with respect to its corresponding parameter in the Electrical Specifications table.

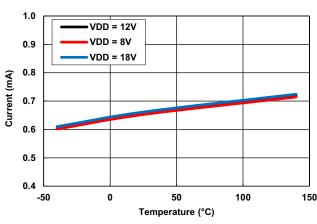

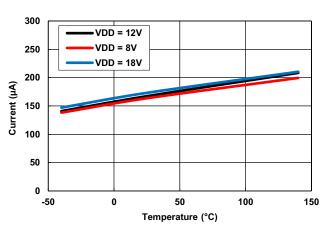

Figure 10. Shutdown Current vs Temperature (ISL78434)

Figure 9. Shutdown Current vs Temperature (ISL78424 and ISL78444)

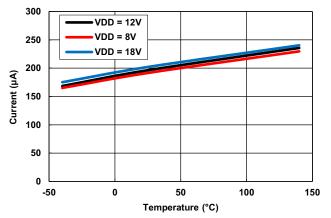

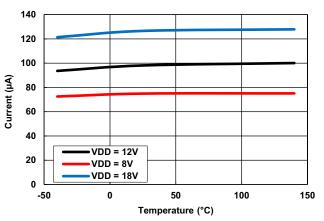

Figure 11. HB to VSS Bias Current vs Temperature

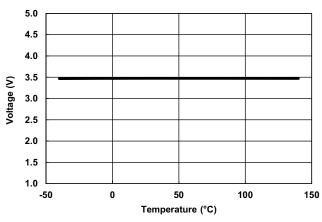

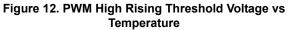

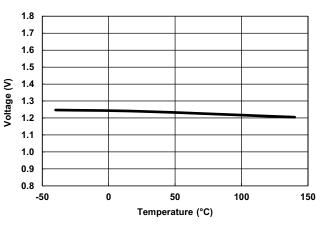

Figure 14. PWM Threshold Voltage vs Temperature

Figure 15. HI Threshold Voltage vs Temperature

Figure 16. LI Threshold Voltage vs Temperature

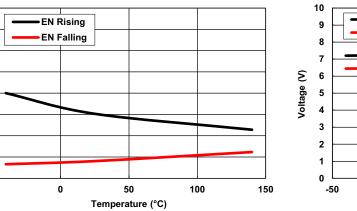

Figure 17. EN Threshold Voltage vs Temperature

Figure 18. EN Delay Time vs Temperature

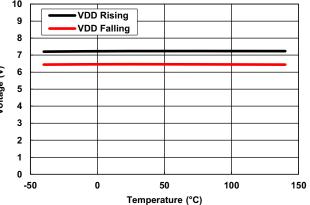

Figure 19. UVLO Threshold Voltage vs Temperature

8

7

6

5

3

2

1

0

-50

Time (µs) 4

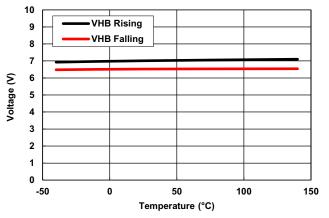

Figure 20. Boot UVLO Threshold Voltage vs Temperature

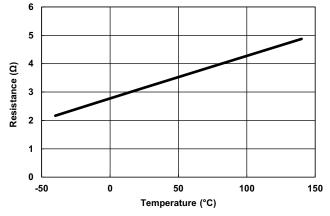

Figure 21. Boot Switch Resistance vs Temperature

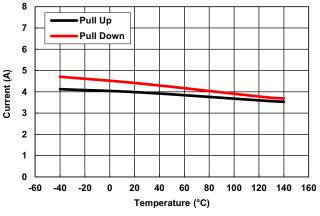

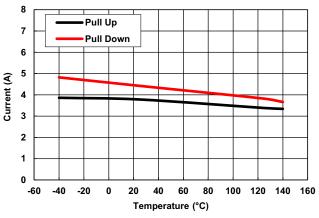

Figure 22. Low-Side Peak Current vs Temperature

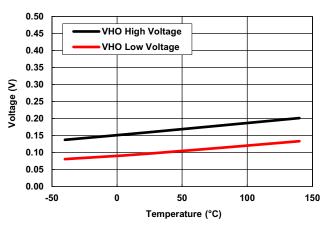

Figure 24. HO Gate Driver Voltage vs Temperature

Figure 23. High-Side Peak Current vs Temperature

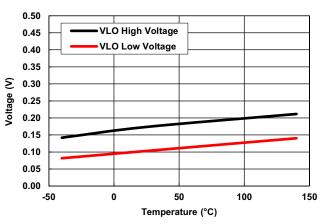

Figure 25. LO Gate Driver Voltage vs Temperature

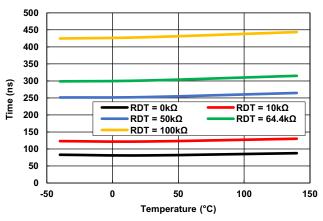

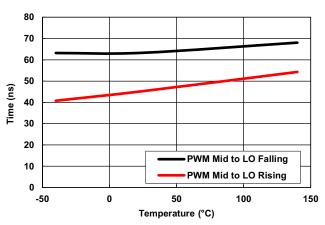

Figure 28. HI Propagation Delay vs Temperature

Figure 29. LI Propagation Delay vs Temperature

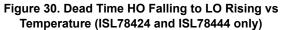

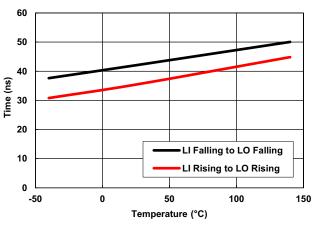

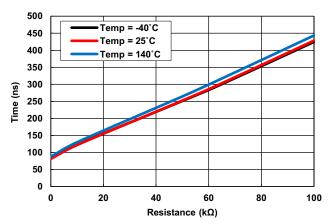

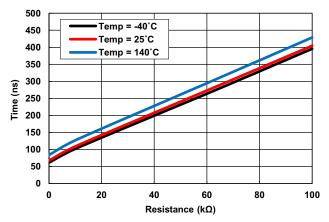

Figure 32. Dead Time HO Falling to LO Rising vs R<sub>DT</sub> Resistance (ISL78424 and ISL78444 only)

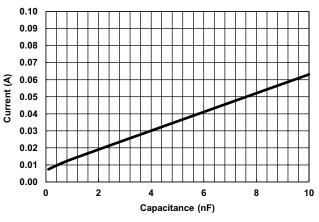

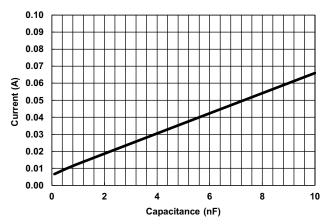

Figure 34. V<sub>DD</sub> Current vs Capacitance on HO, LO

Figure 33. Dead Time LO Falling to HO Rising vs R<sub>DT</sub> Resistance (ISL78424 and ISL78444 only)

Figure 35. HB to HS Current vs Capacitance on HO, LO

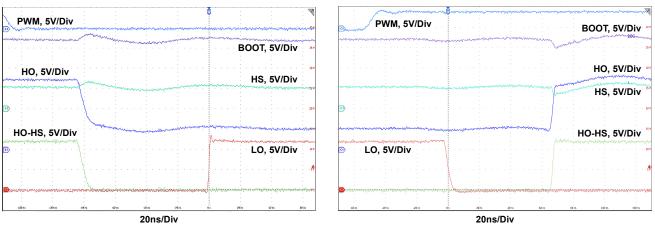

Figure 37. Dead Time LO Falling to HO Rising

# 4. Product Description

The ISL78424, ISL78434, and ISL78444 are Automotive Grade (AEC-Q100 Grade 1) high voltage, high frequency, half-bridge N-MOSFET gate drivers for up to 70V half-bridge topologies. The family of half bridge drivers feature 3A sourcing, 4A sinking peak gate drive current. The ISL78424 and ISL78444 feature a single tri-level PWM input for controlling both gate drivers. The ISL78434 has dual independent inputs for controlling the high and low-side driver separately. Strong gate drive strength and the adaptive dead time feature allow this family of drivers to switch high voltage, low r<sub>ON</sub> power MOSFETs in half bridge topologies at high operating frequencies while providing shoot-through protection and minimizing dead time switching losses. For drivers with single PWM inputs (ISL78424 and ISL78444), when the input is logic high, the high-side driver is on and the low-side driver is off. When the input is a logic low, the low-side driver is on and the high-side driver is off. When the input soft drivers are low to keep the bridge off. The tri-level single PWM input allows the half-bridge to be phase dropped in multi-phase applications. When the enable pin (EN) is low, it takes the bridge driver outputs to a low state to turn off the FETs. When used with the Renesas Multiphase PWM Controllers (ISL78220, ISL78225, ISL78224, and ISL78226) with driver enable output logic, the EN pin prevents false bridge operation during controller start up.

### 4.1 Single PWM or Independent HI/LI Inputs

The ISL78424 and ISL78444 feature a single tri-level PWM input pin to control both the high-side and low-side driver outputs. When PWM is logic high on the ISL78424, the high-side source driver is active and the low-side sink driver is active. When PWM is logic low on the ISL78424, the low-side source driver is active and the high-side sink driver is active. The ISL78444 combines the sinking and sourcing drivers to make one gate drive signal (LO or HO). The gate drive signal is high when the sourcing driver is active, and conversely, the gate drive is low when the sinking driver is active. If the PWM pin is left floating, internal pull-up and pull down resistors bias the PWM pin to the mid-level state. The mid-level state has both high-side and low-side sink drivers active. Alternatively, the PWM pin can be actively driven to the mid-level state.

The single tri-level PWM input is ideal for multi-phase DC/DC converter applications that require phase dropping in light-load conditions. With a single input controlling the high and low-side driver, this reduces the number of controller signals needed by half and simplifies the PCB design, especially in six phase or greater DC/DC converters. The mid-level state puts the half-bridge in high impedance state for phase dropping.

The ISL78434 features independent inputs HI and LI that drive the HO and LO outputs, respectively. The PWM pin is replaced with HI and LI pins. Separate inputs are used in controllers that need to control the upper and lower FET with independent signals.

#### 4.2 ISL78424 and ISL78444 PWM Input

The ISL78424 and ISL78444 single PWM input controls both high and low-side driver with one control signal. When the PWM input is switching between logic high and logic low, the high-side driver output is in phase with the PWM input while the low-side driver is logic inverted from the PWM input. If the PWM is in mid-level (that is, 2.5V) both driver outputs are low. By design, the PWM input prevents a controller from turning both drivers on, providing shoot-through protection against faulted input logic that can occur from a two input driver inadvertently turning both drivers on.

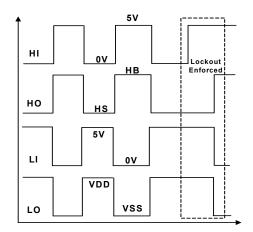

Figure 38. Single PWM Tri-Level Input Control

#### 4.3 ISL78434 HI/LI Lockout Protection

With independent HI and LI inputs being driven by two control signals, dead time is set with the controller by ensuring one control signal is off prior to turning on the other one. There is a possibility the controller outputs are damaged, faulted or from improper dead time programming, causing logic high to both inputs to the driver. The ISL78434 features an input lockout protection to prevent both driver outputs going active high at the same time. Internal logic in the IC senses the HI and LI inputs. The driver locks out any input logic from propagating to that driver output if the other input is already logic high. For example, if HI = 1, LO output does not respond to LI input logic high. If LI = 1, HO output does not respond to HI input logic to propagate to the output. As a further protection against shoot-through, adaptive dead time is enforced when recovering from the lockout function.

Figure 39. HI/LI Input with Lockout Protection

#### 4.4 Separate Source and Sink Outputs

The ISL78424 and ISL78434 feature separate pins for the sourcing and sinking driver outputs. The HO\_H and HO\_L are the high-side sourcing and sinking drivers, respectively. The LO\_H and LO\_L are the low-side sourcing and sinking drivers, respectively. Separate source and sink output pins allow optimizing the FET turn on/off times using gate drive limiting resistors.

The half bridge MOSFET drain-to-source switching dv/dt and di/dt can cause problems when the turn on or turn off occurs too fast (transient overshoot, ringing, and EMI). Many half bridge circuit designs commonly place gate drive limiting resistors in series with the driver output to limit the gate drive current and effectively slow down the turn on and/or turn off of the MOSFET. The turn on and turn off times are typically independently optimized.

A cumbersome solution for single output drivers is to use a series diode + resistor in parallel of a second gate resistor to provide isolation of the sourcing and sinking driver currents (see Figure 40 on page 22). With the diode solution, the gate drive limiting impedance is the parallel resistance in the sinking path and the resistance without the diode in the sourcing path. The drawback of the diode solution is the extra component cost and the parallel resistance requires tuning of both resistors for slew rate control.

Figure 40. Gate Resistors in Standard Bridge Driver

A solution to eliminate the diode and simplify the gate resistance tuning is to provide independent high (sourcing) and low (sinking) driver outputs. This gives flexibility of tuning the source and sink driver impedance to the MOSFET gate without the need of a blocking diode. To separate each output into independent source and sink paths, the half bridge requires an additional pin per driver output (see Figure 41).

Figure 41. Independent Source and Sink Driver Outputs

#### 4.5 **Peak Gate Drive Currents**

The high-side and low-side drivers feature 3A peak sourcing and 4A peak sinking drive capability. Strong gate drive allows fast switching times when low r<sub>DS(ON)</sub>, high voltage power MOSFETs are used. The switching time of the MOSFET translates to the total gate charge of the MOSFET divided by the peak current of the driver.

Example:

$$\begin{array}{l} Q_{GS} = 50nC = 50nA \bullet s \\ I_{SOURCING} = 3A \\ I_{SINKING} = 4A \end{array}$$

$$(EQ. 1) \qquad t_{FET\_ON} = \frac{Q_{GS}}{I_{SOURCING}} = \frac{50nA \bullet s}{3A} = 16.7ns$$

$$(EQ. 2) \qquad t_{FET\_OFF} = \frac{Q_{GS}}{I_{SINKING}} = \frac{50nA \bullet s}{4A} = 12.5ns$$

FN9357 Rev.0.00 Sep 10, 2018

4A

As we can see with the high sourcing and sinking currents of the ISL78424, ISL78434, and ISL78444, the switching times of the MOSFETs are 16.7ns (turn on) and 12.5ns (turn off) for a MOSFET with about 5nF of gate capacitance ( $V_{GS} = 0V$  to 10V). Some bridge drivers offer gate drive capability as low as 500mA, resulting in switching times in the 100ns range for the MOSFET in the example above.

#### 4.6 Shoot-Through Protection

The ISL78424, ISL78434, and ISL78444 feature shoot-through protection of the half bridge by preventing the driver from turning on both FETs at the same time. These drivers integrate Adaptive Dead Time Control (ADTC) that prevents a MOSFET in the bridge from being switched on until the complementary MOSFET has been switched off. The ADTC function seeks to minimize dead time, the time when both MOSFETs are off, while preventing the possibility that both MOSFETs are on at the same time, a condition that could result in shoot-through. ADTC prevents shoot-through while minimizing the higher conduction losses that occur during long dead times.

#### 4.7 Shoot-Through and Dead Time

Shoot-through occurs when both FETs in the half bridge are on at the same time, creating a short-circuit path of the bridge. In a buck regulator, the bus voltage would see a short-circuit to ground causing large current to flow through both FETs. This leads to high power dissipation and can result in FET damage. Dead time is the time when both FETs are off at the same time. Before a FET in the half bridge is turned on, the complementary FET is first switched off, purposefully creating a period of dead time that prevents shoot-through. However, if care is not taken, under some conditions one FET may not be completely off before the complementary FET is turned on. In such a condition, there is no dead time and a transient shoot though condition occurs that results in a momentary short-circuit of the bridge. This fault becomes very serious as the duration when both FETs are on simultaneously is extended and can quickly result in damage of the power FETs due to high power dissipation. ISL78424, ISL78434, and ISL78444 driver includes shoot-through protection to prevent such a condition.

#### 4.8 Adaptive Dead Time Control (ADTC)

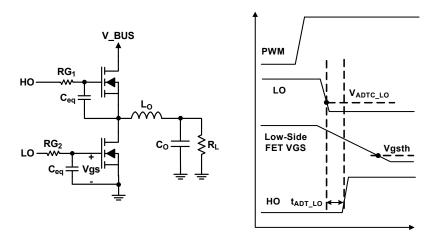

With proper design, shoot-through caused by faulted inputs turning both drivers on are avoided. Other shoot-through conditions occur when there is no dead time on the driver outputs causing a momentary overlap when both FETs are still on. This kind of shoot-through occurs when the gate to source voltage for the top and bottom FET are above the gate threshold voltages, turning both FETs on. Even with proper input logic control, anything that causes the turning off FET to overlap with the turning on FET without dead time causes a transient shoot-through. To prevent against transient shoot-through faults, the ISL78424, ISL78434, and ISL78444 family of drivers implement Adaptive Dead Time Control circuit that prevents a driver output from turning ON until a satisfactory condition is sensed at the turning off FET crosses a falling threshold. This ensures that one FET is completely off before the other FET is turned on with a minimum dead time, minimizing switching losses, and increasing converter efficiency.

Figure 42. Adaptive Dead Time Control

#### 4.9 Adaptive Dead Time and Gate Resistors

To prevent shoot-through, adaptive dead time control senses the voltage at the driver output pins for crossing a falling threshold, at which point the driver considers the FET to be off, before turning the other driver on. With single driver outputs HO and LO, the accuracy of the sense circuit is disrupted when gate resistors are used in series with the driver outputs to slow down the FET turn on/off time because the resistor isolates the driver output from the FET gate. The resistor and FET gate capacitance form an RC low pass filter of the driver output to the FET gate. With the gate voltage lagging behind the driver output voltage, the adaptive dead time control could sense a falling threshold at the driver output but the slower falling gate voltage could still be higher than the gate threshold, resulting in no dead time and causing a momentary shoot-through condition of the bridge.

Figure 43. Adaptive Dead Time Problem with Gate Resistors

The ISL78424 and ISL78434 drivers include a means of using independent source/sink driver outputs to overcome the error that gate resistors typically introduce to adaptive dead time implementations. The driver output sourcing pins (LO\_H and HO\_H) are used as a Kelvin sense when not actively sourcing. When the sinking pins (LO\_L or HO\_L) are active during FET turn off, even with gate resistors between driver output and FET gate, the gate voltage (and not the driver output) is sensed by the LO\_H or HO\_H pin. Adaptive Dead Time Control combined with the gate sensing from separate driver output source and sink pins eliminates the error of inaccurate adaptive dead time sensing when combined with gate resistors.

Figure 44. Adaptive Dead Time with Gate Sensing

Adaptive dead time control minimizes dead time needed to prevent bridge shoot-through. During dead time, the body diode of the synchronous FET conducts, generating conduction losses that exceed those that would occur if the MOSFET itself was conducting. Because conduction losses are higher during dead time than they otherwise would be if the MOSFET were conducting, conversion efficiency is improved as dead time is decreased, so long as

shoot-through does not occur. The lowest adaptive dead time achieved is limited by the propagation delay of the sense circuitry inside the driver. If more dead time is required, the adjustable dead time delay function (ISL78424 and ISL78444 only) further increases the minimum dead time set by the Adaptive dead time control by adjusting the resistor value on RDT pin.

Figure 45. Adaptive Dead Time with Independent Source/Sink for Gate Sensing

#### 4.10 Falling Thresholds for ADTC

The three thresholds for the falling edge detection for Adaptive Dead Time Control - two for the high-side and one for the low-side are summarized in <u>Table 2</u>. For ISL78424 and ISL78434, the detection is sensed at the driver source pins LO\_H (low side) and HO\_H (high side). For ISL78444 where the source and sink driver outputs are on one pin, the detection is done at LO and HO directly, losing the gate sense capability. Additionally, there is a falling edge HS phase sense detector on the high-side driver that turns on the LO output when the high-side gate sense is not detected. This occurs when a large gate resistor slows down the turn off of the high-side FET such that gate voltage is below the Miller voltage but still above the ADTC detection threshold. Here the changing of the HS phase node voltage detects that the high-side FET has turned off.

| Sense Pin | Name                  | Threshold Voltage (Typical) |

|-----------|-----------------------|-----------------------------|

| LO_H      | Low-Side Gate Sense   | 1.0V from LO_H to VSS       |

| HO_H      | High-Side Gate Sense  | 1.3V from HO_H to HS        |

| HS        | High-Side Phase Sense | 0.5V from HS to VSS         |

Table 2. Adaptive Dead Time Falling Edge Thresholds (Note)

Note: This information only applies to the ISL78424 and ISL78434. The ISL78444 uses LO and HO as sense pins.

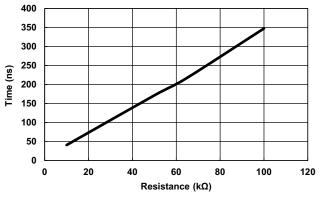

## 4.11 Adjustable Dead Time Delay (RDT Pin)

The minimum dead time due to propagation delays of the adaptive dead time control circuit on this family of bridge drivers can be increased with the adjustable dead time delay feature (ISL78424 and ISL78444). Connect a resistor from the RDT pin to AGND to further increase the dead time set by the ADTC circuit. The adaptive dead time range due to the additional programmed dead time is 30ns to 240ns, from the allowable  $R_{DT}$  resistance values of  $10k\Omega$  to  $100k\Omega$ . This function is useful if the minimum dead time from the adaptive dead time control requires extra margin in the system to prevent shoot-through from occurring.

If adjustable dead time delay is not needed, connect the RDT pin to ground.

A 0.6V reference voltage combined with the resistor on the RDT pin generates a current for an internal oscillator; the current being proportional to the additional dead time delay. The relationship of resistor value on the RDT pin to dead time is shown in Figure 46 on page 26.

Figure 46. Dead Time HO Falling to LO Rising vs  $R_{DT}$  Resistance (ISL78424;  $V_{DD}$  =  $V_{HB}$  -  $V_{HS}$  = 12V;  $V_{HS}$  = 0V)

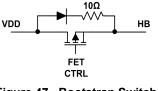

#### 4.12 Integrated Bootstrap Switch

The ISL78424, ISL78434, and ISL78444 family integrates a bootstrap switch internal to the IC. No external boot diode is necessary for the high-side driver bootstrap operation. The advantage of a boot switch compared to a boot diode is that a switch has less voltage drop across it. With a switch the bootstrap voltage at HB can be charged to  $\sim$ VDD while a boot diode has  $\sim$ 0.7V drop at HB. With the boot switch implementation, the low-side and high-side driver outputs can turn on FETs at the V<sub>DD</sub> voltage across gate to source. The boot switch r<sub>ON</sub> is 3 $\Omega$  typical which provides the proper impedance to refresh the boot capacitor in applications up to 500kHz when the proper boot capacitor is selected.

Upon initial enabling of driver, the boot switch is turned on when PWM is logic low for the ISL78424 and ISL78444 (LI is logic high and HI is logic low for the ISL78434) and the HS pin is below 2V. After a subsequent turning on of the high-side driver, PWM is logic high for the ISL78424 and ISL78444 (LI is logic low and HI is logic high for the ISL78434), whenever PWM (HI for the ISL78434) is not logic high and the HS pin is below 2V the boot switch is turned on. When the boot switch FET is not turned on, there is a parallel path of the FET body diode with a  $10\Omega$  series impedance (see Figure 47).

Figure 47. Bootstrap Switch

#### 4.13 Bootstrap Capacitor

To provide the proper gate drive to the high-side FET, the high-side driver bias on this family of drivers is handled with a bootstrap capacitor across the HB and HS pins. The boot bias is recharged whenever the HS pin voltage goes below 2V and the high-side source driver is not commanded by PWM or HI. The internal boot switch from VDD to HB turns on and the bootstrap capacitor is charged by VDD. To maintain operation of the high-side gate drive and at the same time be adequately charged during initial boot up and refreshed in operation requires choosing an appropriate capacitor value. In general, for most applications a  $0.1\mu$ F to  $0.33\mu$ F bootstrap capacitor is a good starting point. For more information on choosing the right bootstrap capacitor, see <u>"Bootstrap Capacitor Design" on page 28</u>.

#### 4.14 EN Pin

The EN pin when placed in logic 0 state places the driver into a low power shutdown state. In shutdown, the driver outputs do not respond to PWM inputs (for ISL78424 and ISL78444) and HI/LI inputs (for ISL78434). The low-side driver sink output is active and the high-side driver sink output has a  $1M\Omega$  impedance to HS to keep the bridge FETs off. The EN pin is used with Renesas analog DC/DC controllers (that is, ISL78220, ISL78225, and ISL78226) to provide a state of non-operation before soft-start of the converter. The Renesas controllers have a driver enable pin that asserts high when soft-start begins to ensure the half bridge is not switching before the controller is properly biased.

The EN pin has an internal  $160k\Omega$  pull-down resistor that disables the driver when the pin is left floating.

#### 4.15 UVLO Protection - VDD and Boot

The driver implements UVLO on both the VDD and HB-HS bootstrap supply. When the voltage on VDD and HB (referenced to HS) is below the UVLO threshold, UVLO protection is active. For the VDD UVLO, both driver sourcing outputs are disabled and the low-side sinking output is active. For boot UVLO, only the high-side driver sourcing output is disable and there is a  $1M\Omega$  impedance on the HO pin relative to HS. The low-side driver continues to respond to driver inputs in Boot UVLO.

When coming out of VDD UVLO, the high-side sourcing driver does not respond to input commands until the low-side sourcing driver is active first. This ensures a boot refresh cycle occurs first to charge the bootstrap capacitor to provide proper bias for the high-side driver.

# 5. Applications Information

#### 5.1 Supply Voltage Operating Range

The recommended operating voltage range on VDD is 8V to 18V. Renesas recommends placing a  $0.1\mu$ F high frequency decoupling capacitor close to the VDD and VSS pin of the IC. A decoupling capacitor of at least 10 times the value of the boot capacitor is recommended to be placed in parallel with the  $0.1\mu$ F at VDD and VSS.

### 5.2 Bootstrap Capacitor Design

ISL78424, ISL78434, and ISL78444 family has an integrated bootstrap switch that charges the external bootstrap capacitor required on the HB to HS pins. To ensure that proper value of the bootstrap capacitance is selected, the minimum  $V_{GS}$  of the FET which is being driven needs to take into account, along with the voltage drop across the bootstrap switch, typically 0.4V.

(EQ. 3)

$$\Delta V_{BOOT} = V_{DD} - V_{DH} - V_{GS}$$

MIN

- $\Delta V_{BOOT}$  = Maximum allowable voltage dip to ensure proper function

- $V_{DD} = V_{BOOT}$  charging supply

- $V_{DH}$  = High current forward voltage

- $V_{GS MIN}$  = Minimum  $V_{GS}$  voltage of FET required to keep FET on

The minimum  $C_{BOOT}$  capacitance required to ensure proper functionality becomes dependent on the total charge required during the on state of the high side when the  $C_{BOOT}$  is not charging, along with the allowable change in voltage of the boot.

(EQ. 4)

$$C_{BOOT} = \frac{Q_{TOTAL}}{\Delta V_{BOOT}}$$

where:

(EQ. 5)  $Q_{TOTAL} = Q_{G MAX} + (I_{GS LKG} + I_{HBQ} + I_{HBSLEAK}) \times t_{ON}$

•  $Q_{G MAX}$  = Maximum gate charge, from FET datasheet

- I<sub>GS LKG</sub> = Maximum FET gate-body leakage current, from FET datasheet

- I<sub>HBO</sub> = Boot quiescent current

- I<sub>HBSLEAK</sub> = Boot leakage current

#### 5.3 Gate Drive Limiting Resistors