# RENESAS

## **USER'S MANUAL**

## ISL8011EVAL1Z

1.2A Integrated FETs, High Efficiency Synchronous Buck Regulator

AN1329 Rev 0.00 June 7, 2007

ISL8011 is an integrated FET, 1.2A synchronous buck regulator for general purpose point-of load applications. It is optimized for generating low output voltages down to 0.8V. The supply voltage range of 2.7V to 5.5V allows the use of common 3.3V or 5V supply rails and Lithium ion battery inputs. It has a guaranteed minimum output current of 1.2A and a 1.5MHz pulse-width modulation (PWM) switching frequency which allows the use of small external components.

The ISL8011 includes a pair of low ON-resistance P-Channel and N-Channel internal MOSFETs to maximize efficiency and minimize external component count. 100% duty-cycle operation allows less than 200mV dropout voltage at 1.2A.

The ISL8011 offers a 200ms Power-On-Reset (POR) timer at power-up. When shut down, the ISL8011 discharges the output capacitor. Other features include internal digital soft-start, enable for power sequence, overcurrent protection, and thermal shut-down.

The ISL8011 is offered in a 10 Ld 3x3mm DFN package with 1mm maximum height. The complete converter occupies less than  $1cm^2$  area.

### **Ordering Information**

| PART NUMBER<br>(Note) | PART<br>MARKING  | TEMP.<br>RANGE<br>(°C) | PACKAGE<br>(Pb-Free)           | PKG.<br>DWG. # |  |

|-----------------------|------------------|------------------------|--------------------------------|----------------|--|

| ISL8011IRZ            | 011Z             | -40 to +85             | 10 Ld 3x3 DFN                  | L10.3x3C       |  |

| ISL8011IRZ-T          | 011Z             | -40 to +85             | 10 Ld 3x3 DFN<br>Tape and Reel | L10.3x3C       |  |

| ISL8011EVAL1Z         | Evaluation Board |                        |                                |                |  |

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

#### Features

- High Efficiency Synchronous Buck Regulator with up to 95% Efficiency

- 2.7V to 5.5V Supply Voltage

- 1.2A Guaranteed Output Current

- 100% Maximum Duty Cycle

- · Peak Current Limiting, Short Circuit Protection

- 200ms Power-On Reset

- 3% Output Accuracy Over Temperature/Load/Line

- Less than 1µA Logic Controlled Shut-down Current

- Internal Loop Compensation

- Internal Digital Soft-Start

- Over-Temperature Protection

- Enable

- Small 10 Ld 3x3mm DFN Package

- Pb-Free Plus Anneal Available (RoHS Compliant)

#### Applications

- DC/DC POL Modules

- μC/μP, FPGA and DSP Power

- Plug-in DC/DC Modules for Routers and Switchers

- Portable Instruments

- · Test and Measurement Systems

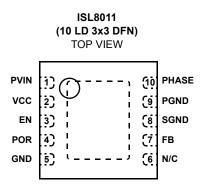

#### Pinout

#### What's inside

The Evaluation Board Kit contains the following materials:

- The ISL8011EVAL1Z Rev A board

- The ISL8011 datasheet

- This EVAL KIT document

#### **Recommended Equipment**

The following materials are recommended to perform testing:

- 0V to 10V power supply with at least 5A source current capability, battery, notebook AC adapter

- Two Electronic Loads capable of sinking current up to 5A

- Digital Multimeters (DMMs)

- 100MHz quad-trace Oscilloscope

- · Signal generator

#### **Quick Setup Guide**

- 1. Ensure that the circuit is correctly connected to the supply and loads prior to applying any power.

- 2. Connect the bias supply to VIN. Plus terminal to (VIN) and negative return to (GND).

- 3. Verify that position is ON for JP1 jumper.

- 4. Turn on the power supply.  $V_{IN}$  = 2.7V to 5.5V.

- 5. Verify the output voltage is 1.6V for  $V_{\mbox{OUT}}$

#### Evaluating the Other Output Voltage

The ISL8011EVAL1Z kit output is preset to 1.6V; however, output voltages can be adjusted from 0.8V to 3.6V by the following equations:

$$VOUT = 0.8 \left(1 + \frac{R2}{R1}\right)$$

(EQ. 1)

Let's set R<sub>2</sub>= 100k $\Omega$

$$R_{1} = \frac{(R_{2})}{\left(\frac{V_{OUT}}{0.8}\right) - 1}$$

(EQ. 2)

where the 0.8V is the reference voltage. To minimize the accuracy impact on the output voltage, select the  $R_1$  and  $R_2$  no larger than 100k $\Omega$ .

| J1 | ENABLE                |                          |

|----|-----------------------|--------------------------|

| 1  | Center post to top    | Enable V <sub>OUT</sub>  |

| 2  | Center post to bottom | Disable V <sub>OUT</sub> |

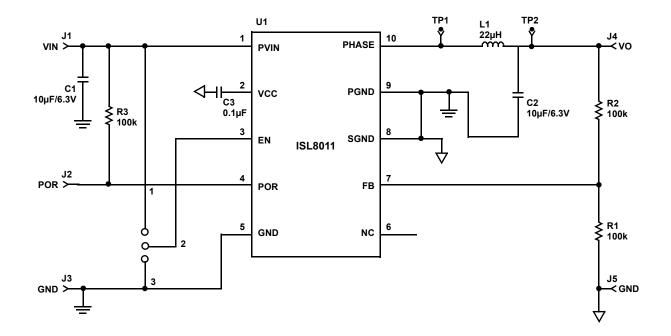

## Schematic

#### TABLE 2. COMPONENT LIST

| REF<br>DES | QTY | VALUE   | TOL. | VOLTAGE | PACKAGE | PART NUMBER    | MANUFACTURER | DESCRIPTION                                   |

|------------|-----|---------|------|---------|---------|----------------|--------------|-----------------------------------------------|

| C3         | 1   | 0.1µF   |      |         | 603     | EMK107BJ104MA  | Taiyo Yuden  | Capacitor                                     |

| L1         | 1   | 2.2µH   |      |         | 4028    | CDRH2D14-2R2   | Sumida       | Inductor                                      |

| C1         | 1   | 10µF    | 20%  | 6.3V    | 805     | C1608X5R0J106M | Panasonic    | CAP, SMD, 0603, 10µF, 6.3V, 20%,<br>X5R, ROHS |

| C2         | 1   | 10µF    | 20%  | 6.3V    | 805     | C1608X5R0J106M | Panasonic    | CAP, SMD, 0603, 10µF, 6.3V, 20%,<br>X5R, ROHS |

| R2         | 1   | 100k    | 1%   | 100V    | 603     | various        |              | RES, SMD, 0603, 100k, 1/10W, 1%,<br>TF, ROHS  |

| R3         | 1   | 100k    | 1%   | 100V    | 603     | various        |              | RES, SMD, 0603, 100k, 1/10W, 1%,<br>TF, ROHS  |

| R1         | 1   | 100k    | 1%   | 100V    | 603     | various        |              | RES, SMD, 0603, 100k, 1/10W, 1%,<br>TF, ROHS  |

| U1         | 1   | ISL8011 |      |         | DFN-10  | ISL8011        | Intersil     |                                               |

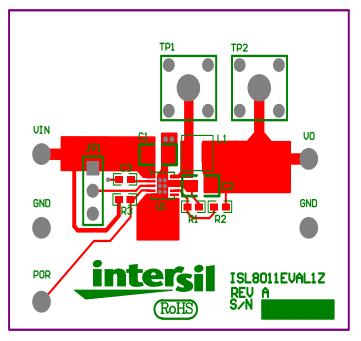

#### ISL8011EVAL1Z Board Layout

FIGURE 1. TOP COMPONENTS

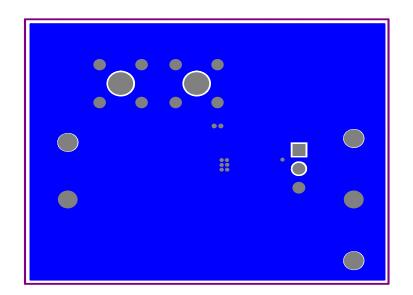

FIGURE 2. BOTTOM LAYER