## ISL8487E, ISL81487L, ISL81487E

±15kV ESD Protected, 1/8 Unit Load, 5V, Low Power, High Speed or Slew Rate Limited RS-485/RS-422 Transceivers

FN6051 Rev.8.00 Sep 20, 2018

The <u>ISL8487E</u>, <u>ISL81487L</u>, and <u>ISL81487E</u> RS-485/RS-422 devices are ESD protected, fractional unit load (UL), BiCMOS, 5V powered, single transceivers that meet both the RS-485 and RS-422 standards for balanced communication. Each driver output/receiver input is protected against ±15kV ESD strikes without latch-up. Unlike competitive devices, this device family is specified for 10% tolerance supplies (4.5V to 5.5V).

All devices present a 1/8 unit load to the RS-485 bus, which allows up to 256 transceivers on the network for large node count systems (for example, process automation and remote meter reading systems). In a remote utility meter reading system, individual utility meter readings (in apartments, for example) are routed to a concentrator with an RS-485 network, so the high allowed node count minimizes the number of repeaters required to network all the meters. Data for all meters is then read out from the concentrator from a single access port or a wireless link.

Slew rate limited drivers on the ISL8487E and ISL81487L reduce EMI and minimize reflections from improperly terminated transmission lines or unterminated stubs in multidrop and multipoint applications. Data rates up to 250kbps are achievable with these devices.

Data rates up to 5Mbps are achievable by using the ISL81487E, which features higher slew rates.

The receiver (Rx) inputs feature a "fail-safe if open" design, which ensures a logic high Rx output if Rx inputs are floating.

The driver (Tx) outputs are short-circuit protected, even for voltages exceeding the power supply voltage. Additionally, on-chip thermal shutdown circuitry disables the Tx outputs to prevent damage if power dissipation becomes excessive.

The half duplex devices multiplex the Rx inputs and Tx outputs to allow transceivers with Rx and Tx disable functions in 8 lead packages.

#### Related Literature

For a full list of related documents, visit our website:

• ISL8487E, ISL81487L, and ISL81487E product pages

#### Features

- RS-485 I/O pin ESD protection . . . . . . ±15kV HBM

Class 3 ESD level on all other pins . . . . . >7kV HBM

- · Fractional unit load allows up to 256 devices on the bus

- Specified for 10% tolerance supplies

- High data rate version (ISL81487E). . . . . . up to 5Mbps

- Slew rate limited versions for error free data transmission (ISL8487E, ISL81487L) . . . . . up to 250kbps

- Low current shutdown mode (except ISL81487E) . . . 0.5μA

- · Low quiescent supply current:

- ISL81487E . . . . . . . . . . . . . 420μA (maximum)

- -7V to +12V common mode input voltage range

- Three state Rx and Tx outputs

- 30ns propagation delays, 5ns skew (ISL81487E)

- · Half duplex pinouts

- Operate from a single +5V supply (10% tolerance)

- Current limiting and thermal shutdown for driver overload protection

- Pin compatible replacements for: MAX487E, (ISL8487E); LTC1487, ADM1487 (ISL81487L); MAX1487E, ST485ER (ISL81487E)

- · Pb-free plus anneal available (RoHS compliant)

## **Applications**

- · High node count networks

- Automated utility meter reading systems

- · Factory automation

- Security networks

- · Building environmental control systems

- Industrial/process control networks

#### **TABLE 1. SUMMARY OF FEATURES**

| PART<br>NUMBER | HALF/FULL<br>DUPLEX | NO. OF DEVICES<br>ALLOWED ON BUS | DATA RATE<br>(Mbps) | SLEW RATE<br>LIMITED? | RECEIVER/<br>DRIVER ENABLE? | QUIESCENT<br>I <sub>CC</sub> (μA) | LOW POWER SHUTDOWN? | PIN<br>COUNT |

|----------------|---------------------|----------------------------------|---------------------|-----------------------|-----------------------------|-----------------------------------|---------------------|--------------|

| ISL8487E       | Half                | 256                              | 0.25                | Yes                   | Yes                         | 120                               | Yes                 | 8            |

| ISL81487L      | Half                | 256                              | 0.25                | Yes                   | Yes                         | 120                               | Yes                 | 8            |

| ISL81487E      | Half                | 256                              | 5                   | No                    | Yes                         | 350                               | No                  | 8            |

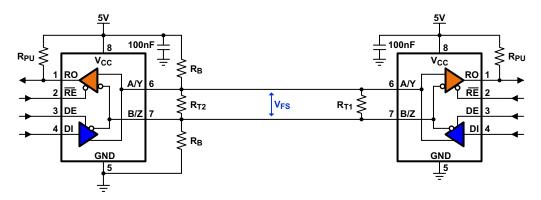

## **Typical Operating Circuits**

To calculate the resistor values, refer to TB509.

## **Ordering Information**

| PART NUMBER ()                                                                               | PART MARKING | TEMP. RANGE (°C) | TAPE AND REEL<br>(UNITS) (Note 1) | PACKAGE                        | PKG. DWG. # |

|----------------------------------------------------------------------------------------------|--------------|------------------|-----------------------------------|--------------------------------|-------------|

| ISL8487EIBZ                                                                                  | 8487EIBZ     | -40 to +85       | -                                 | 8 Ld SOIC<br>(Pb-free)         | M8.15       |

| ISL8487EIBZ-T                                                                                | 8487EIBZ     | -40 to +85       | 2.5k                              | 8 Ld SOIC<br>(Pb-free)         | M8.15       |

| ISL8487EIPZ (not<br>recommended for new designs,<br>recommended replacement<br>ISL81487LIPZ) | 8487EIPZ     | -40 to +85       | -                                 | 8 Ld PDIP<br>(Pb-free, Note 4) | E8.3        |

| ISL81487LIBZ                                                                                 | 81487LIBZ    | -40 to +85       | -                                 | 8 Ld SOIC<br>(Pb-free)         | M8.15       |

| ISL81487LIBZ-T                                                                               | 81487LIBZ    | -40 to +85       | 2.5k                              | 8 Ld SOIC<br>(Pb-free)         | M8.15       |

| ISL81487LIPZ                                                                                 | 81487LIPZ    | -40 to +85       | -                                 | 8 Ld PDIP<br>(Pb-free, Note 4) | E8.3        |

| ISL81487EIBZ                                                                                 | 81487EIBZ    | -40 to +85       | -                                 | 8 Ld SOIC<br>(Pb-free)         | M8.15       |

| ISL81487EIBZ-T                                                                               | 81487EIBZ    | -40 to +85       | 2.5k                              | 8 Ld SOIC<br>(Pb-free)         | M8.15       |

| ISL81487EIPZ                                                                                 | ISL81487EIPZ | -40 to +85       | -                                 | 8 Ld PDIP<br>(Pb-free, Note 4) | E8.3        |

#### NOTES:

- 1. Refer to TB347 for details about reel specifications.

- 2. Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020

- 3. For Moisture Sensitivity Level (MSL), see the <u>ISL8487E</u>, <u>ISL81487L</u>, and <u>ISL81487E</u> product information pages. For more information about MSL, see <u>TB363</u>.

- 4. Pb-free PDIPs can be used for through hole wave solder processing only. They are not intended for use in Reflow solder processing applications.

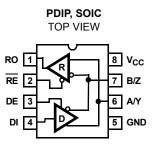

## Pinout

## Pin Descriptions

| PIN             | FUNCTION                                                                                                                                                              |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RO              | Receiver output. RO is high if A > B by at least 0.2V; RO is low if A < B by 0.2V or more; RO is high if A and B are unconnected (floating).                          |

| RE              | Receiver output enable. RO is enabled when $\overline{RE}$ is low; RO is high impedance when $\overline{RE}$ is high.                                                 |

| DE              | Driver output enable. The driver outputs Y and Z are enabled by bringing DE high. They are high impedance when DE is low.                                             |

| DI              | Driver input. A low on DI forces output Y low and output Z high. Similarly, a high on DI forces output Y high and output Z low.                                       |

| GND             | Ground connection.                                                                                                                                                    |

| A/Y             | ±15kV HBM ESD protected, RS-485/422 level, noninverting receiver input and noninverting driver output. Pin is an input (A) if DE = 0; pin is an output (Y) if DE = 1. |

| B/Z             | ±15kV HBM ESD protected, RS-485/422 level, inverting receiver input and inverting driver output. Pin is an input (B) if DE = 0; pin is an output (Z) if DE = 1.       |

| V <sub>CC</sub> | System power supply input (4.5V to 5.5V).                                                                                                                             |

## Truth Tables

| TRANSMITTING |        |         |                     |                     |  |  |  |

|--------------|--------|---------|---------------------|---------------------|--|--|--|

|              | INPUTS | OUTPUTS |                     |                     |  |  |  |

| RE           | DE     | DI      | Z                   | Υ                   |  |  |  |

| Х            | 1      | 1       | 0                   | 1                   |  |  |  |

| Х            | 1      | 0       | 1                   | 0                   |  |  |  |

| 0            | 0      | Х       | High-Z              | High-Z              |  |  |  |

| 1            | 0      | Х       | High-Z<br>(Note 12) | High-Z<br>(Note 12) |  |  |  |

| RECEIVING |        |             |                     |  |  |  |  |

|-----------|--------|-------------|---------------------|--|--|--|--|

|           | OUTPUT |             |                     |  |  |  |  |

| RE        | DE     | A-B         | RO                  |  |  |  |  |

| 0         | Х      | ≥ +0.2V     | 1                   |  |  |  |  |

| 0         | Х      | ≤ -0.2V     | 0                   |  |  |  |  |

| 0         | Х      | Inputs Open | 1                   |  |  |  |  |

| 1         | Х      | Х           | High-Z<br>(Note 12) |  |  |  |  |

| 1         | 0      | Х           | High-Z              |  |  |  |  |

## **Absolute Maximum Ratings**

| V <sub>CC</sub> to Ground | 7V                                     |

|---------------------------|----------------------------------------|

| Input Voltages            |                                        |

| DI, DE, RE                | 0.5V to (V <sub>CC</sub> +0.5V)        |

| Input/Output Voltages     | , 65                                   |

| A/Y, B/Z                  | 8V to +12.5V                           |

| RO                        | 0.5V to (V <sub>CC</sub> +0.5V)        |

| Short-Circuit Duration    |                                        |

| Y, Z                      | Continuous                             |

| ESD Rating                | See <u>"Electrical Specifications"</u> |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 5)           | $\theta_{JA}$ (°C/W) |

|------------------------------------------------|----------------------|

| 8 Ld SOIC Package                              | 170                  |

| 8 Ld PDIP Package (Note 6)                     |                      |

| Maximum Junction Temperature (Plastic Package) | 150°C                |

| Maximum Storage Temperature Range68            | 5°C to 150°C         |

| Maximum Lead Temperature (Soldering 10s)       | 300°C                |

| (SOIC - Lead Tips Only)                        |                      |

#### **Operating Conditions**

| Temperature Range |                  |

|-------------------|------------------|

| ISL8XXXIX         | <br>40°C to 85°C |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" can permanently damage the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

- 5. θ<sub>JA</sub> is measured with the component mounted on a low-effective thermal conductivity test board in free air. See <u>TB379</u> for details.

- 6. Pb-free PDIPs can be used for through hole wave solder processing only. They are not intended for use in Reflow solder processing applications.

## **Electrical Specifications** Test Conditions: V<sub>CC</sub> = 4.5V to 5.5V; Unless Otherwise Specified. Typicals are at V<sub>CC</sub> = 5V, T<sub>A</sub> = +25°C, Note 7

| PARAMETER                                                                                         | SYMBOL           | TEST CONDITIONS                                    |                       | TEMP<br>(°C) | MIN  | TYP  | MAX             | UNIT |

|---------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------|-----------------------|--------------|------|------|-----------------|------|

| DC CHARACTERISTICS                                                                                |                  |                                                    |                       | <u>.</u>     |      |      |                 |      |

| Driver Differential V <sub>OUT</sub> (No Load)                                                    | V <sub>OD1</sub> |                                                    |                       | Full         | -    | -    | V <sub>CC</sub> | V    |

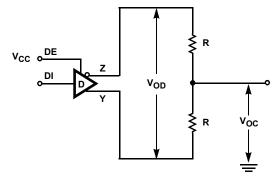

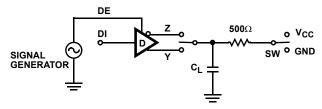

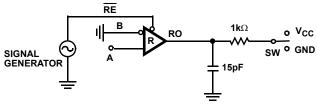

| Driver Differential V <sub>OUT</sub> (with Load)                                                  | V <sub>OD2</sub> | $R = 50\Omega$ (RS-422), ( <u>Figu</u>             | <u>ıre 1</u> )        | Full         | 2    | 3    | -               | V    |

|                                                                                                   |                  | R = 27Ω (RS-485), ( <u>Figu</u>                    | <u>ire 1</u> )        | Full         | 1.5  | 2.3  | 5               | V    |

| Change in Magnitude of Driver<br>Differential V <sub>OUT</sub> for<br>Complementary Output States | ΔV <sub>OD</sub> | R = $27\Omega$ or $50\Omega$ , ( <u>Figure 1</u> ) |                       | Full         | -    | 0.01 | 0.2             | V    |

| Driver Common-Mode V <sub>OUT</sub>                                                               | V <sub>OC</sub>  | R = $27\Omega$ or $50\Omega$ , ( <u>Figure</u>     | <u>1</u> )            | Full         | -    | -    | 3               | V    |

| Change in Magnitude of Driver<br>Common-Mode V <sub>OUT</sub> for<br>Complementary Output States  | ΔV <sub>OC</sub> | R = $27\Omega$ or $50\Omega$ , (Figure 1)          |                       | Full         | -    | 0.01 | 0.2             | V    |

| Logic Input High Voltage                                                                          | V <sub>IH</sub>  | DE, DI, RE                                         |                       | Full         | 2    | -    | -               | V    |

| Logic Input Low Voltage                                                                           | V <sub>IL</sub>  | DE, DI, RE                                         |                       | Full         | -    | -    | 0.8             | V    |

| Logic Input Current                                                                               | I <sub>IN1</sub> | DE, DI, RE                                         |                       | Full         | -2   | -    | 2               | μΑ   |

| Input Current (A/Y, B/Z), (Note 15)                                                               |                  | DE = 0V, V <sub>CC</sub> = 4.5 to 5.5V             | V <sub>IN</sub> = 12V | Full         | -    | -    | 140             | μA   |

|                                                                                                   |                  |                                                    | V <sub>IN</sub> = -7V | Full         | -    | -    | -120            | μΑ   |

|                                                                                                   | I <sub>IN2</sub> | DE = 0V, V <sub>CC</sub> = 0V                      | V <sub>IN</sub> = 12V | Full         | -    | -    | 180             | μA   |

|                                                                                                   |                  |                                                    | V <sub>IN</sub> = -7V | Full         | -    | -    | -100            | μA   |

| Receiver Differential Threshold<br>Voltage                                                        | V <sub>TH</sub>  | $-7V \le V_{CM} \le 12V$                           |                       | Full         | -0.2 | -    | 0.2             | V    |

| Receiver Input Hysteresis                                                                         | $\Delta V_{TH}$  | V <sub>CM</sub> = 0V                               |                       | 25           | -    | 70   | -               | mV   |

| Receiver Output High Voltage                                                                      | V <sub>OH</sub>  | I <sub>O</sub> = -4mA, V <sub>ID</sub> = 200m\     | /                     | Full         | 3.5  | -    | -               | V    |

| Receiver Output Low Voltage                                                                       | V <sub>OL</sub>  | I <sub>O</sub> = -4mA, V <sub>ID</sub> = 200mV     |                       | Full         | -    | -    | 0.4             | V    |

| Three-State (High Impedance)<br>Receiver Output Current                                           | I <sub>OZR</sub> | $0.4V \le V_O \le 2.4V$                            |                       | Full         | -    | -    | ±1              | μA   |

| Receiver Input Resistance                                                                         | R <sub>IN</sub>  | $-7V \le V_{CM} \le 12V$                           |                       | Full         | 96   | -    | -               | kΩ   |

# **Electrical Specifications** Test Conditions: V<sub>CC</sub> = 4.5V to 5.5V; Unless Otherwise Specified. Typicals are at V<sub>CC</sub> = 5V, T<sub>A</sub> = +25°C, Note 7 (Continued)

| Note / (Continued)                                            |                                        |                                                      |                                                                       |      |                 |      |      |         |  |

|---------------------------------------------------------------|----------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------|------|-----------------|------|------|---------|--|

| PARAMETER                                                     | SYMBOL                                 | TEST CON                                             | NDITIONS                                                              | (°C) | (°C) MIN TYP MA |      |      | AX UNIT |  |

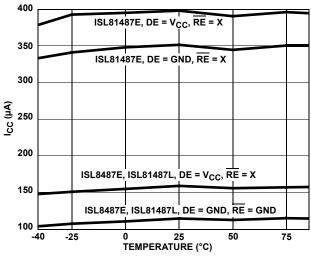

| No-Load Supply Current, (Note 8)                              | I <sub>CC</sub> ISL81487E, DI, RE = 0V |                                                      | DE = V <sub>CC</sub>                                                  | Full | -               | 400  | 500  | μΑ      |  |

|                                                               |                                        | or V <sub>CC</sub>                                   | DE = 0V                                                               | Full | -               | 350  | 420  | μΑ      |  |

|                                                               |                                        | ISL8487E, ISL81487L,                                 | DE = V <sub>CC</sub>                                                  | Full | -               | 160  | 200  | μΑ      |  |

|                                                               |                                        | DI, $\overline{RE} = 0V$ or $V_{CC}$                 | DE = 0V                                                               | Full | -               | 120  | 145  | μA      |  |

| Shutdown Supply Current                                       | I <sub>SHDN</sub>                      | ( <u>Note 12</u> ), DE = 0V, RE =                    | = V <sub>CC</sub> , DI = 0V or V <sub>CC</sub>                        | Full | -               | 0.5  | 8    | μA      |  |

| Driver Short-Circuit Current,<br>V <sub>O</sub> = High or Low | I <sub>OSD1</sub>                      | DE = $V_{CC}$ , -7 $V \le V_Y$ or $V_Y$              | / <sub>Z</sub> ≤ 12V, ( <u>Note 9</u> )                               | Full | 35              | -    | 250  | mA      |  |

| Receiver Short-Circuit Current                                | I <sub>OSR</sub>                       | $0V \leq V_O \leq V_{CC}$                            |                                                                       | Full | 7               | -    | 85   | mA      |  |

| SWITCHING CHARACTERISTICS (                                   | ISL81487E)                             |                                                      |                                                                       | l    |                 |      |      | J       |  |

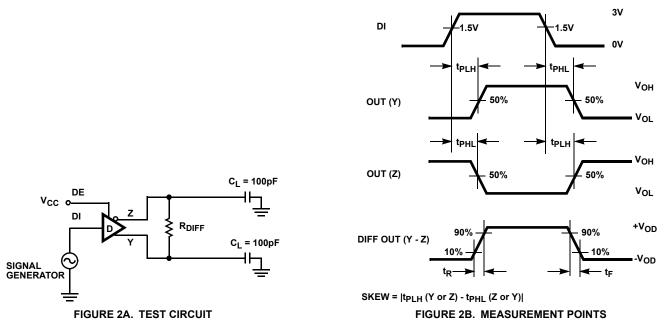

| Driver Input to Output Delay                                  | t <sub>PLH</sub> , t <sub>PHL</sub>    | $R_{DIFF}$ = 54 $\Omega$ , $C_L$ = 100p              | F, ( <u>Figure 2</u> )                                                | Full | 15              | 24   | 50   | ns      |  |

| Driver Output Skew                                            | tskew                                  | R <sub>DIFF</sub> = 54Ω, C <sub>L</sub> = 100p       | F, ( <u>Figure 2</u> )                                                | Full | -               | 3    | 10   | ns      |  |

| Driver Differential Rise or Fall Time                         | t <sub>R</sub> , t <sub>F</sub>        | $R_{DIFF} = 54\Omega$ , $C_L = 100p$                 | F, ( <u>Figure 2</u> )                                                | Full | 3               | 12   | 25   | ns      |  |

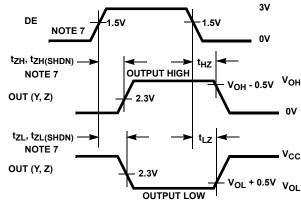

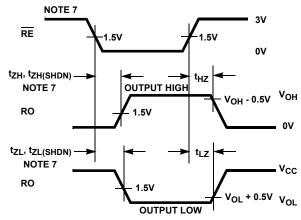

| Driver Enable to Output High                                  | t <sub>ZH</sub>                        | C <sub>L</sub> = 100pF, SW = GND,                    | (Figure 2)                                                            | Full | -               | 14   | 70   | ns      |  |

| Driver Enable to Output Low                                   | t <sub>ZL</sub>                        | C <sub>L</sub> = 100pF, SW = V <sub>CC</sub> ,       | ( <u>Figure 2</u> )                                                   | Full | -               | 14   | 70   | ns      |  |

| Driver Disable from Output High                               | t <sub>HZ</sub>                        | C <sub>L</sub> = 15pF, SW = GND, (                   | Figure 2)                                                             | Full | -               | 44   | 70   | ns      |  |

| Driver Disable from Output Low                                | t <sub>LZ</sub>                        | $C_L = 15pF, SW = V_{CC}, ($                         | Figure 2)                                                             | Full | -               | 21   | 70   | ns      |  |

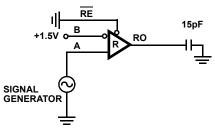

| Receiver Input to Output Delay                                | t <sub>PLH</sub> , t <sub>PHL</sub>    | (Figure 4)                                           |                                                                       | Full | 30              | 90   | 150  | ns      |  |

| Receiver Skew   t <sub>PLH</sub> - t <sub>PHL</sub>           | t <sub>SKD</sub>                       | (Figure 4)                                           |                                                                       | 25   | -               | 5    | -    | ns      |  |

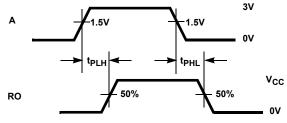

| Receiver Enable to Output High                                | t <sub>ZH</sub>                        | C <sub>L</sub> = 15pF, SW = GND, ( <u>Figure 5</u> ) |                                                                       | Full | -               | 9    | 50   | ns      |  |

| Receiver Enable to Output Low                                 | t <sub>ZL</sub>                        | $C_L = 15pF$ , SW = $V_{CC}$ , (Figure 5)            |                                                                       | Full | -               | 9    | 50   | ns      |  |

| Receiver Disable from Output High                             | t <sub>HZ</sub>                        | C <sub>L</sub> = 15pF, SW = GND, ( <u>Figure 5</u> ) |                                                                       | Full | -               | 9    | 50   | ns      |  |

| Receiver Disable from Output Low                              | t <sub>LZ</sub>                        | $C_L = 15pF$ , SW = $V_{CC}$ , ( <u>Figure 5</u> )   |                                                                       | Full | -               | 9    | 50   | ns      |  |

| Maximum Data Rate                                             | f <sub>MAX</sub>                       |                                                      |                                                                       | Full | 5               | -    | -    | Mbps    |  |

| SWITCHING CHARACTERISTICS (                                   | ISL8487E)                              |                                                      |                                                                       | II.  |                 |      |      |         |  |

| Driver Input to Output Delay                                  | t <sub>PLH</sub> , t <sub>PHL</sub>    | $R_{DIFF} = 54\Omega$ , $C_L = 100p$                 | F, ( <u>Figure 2</u> )                                                | Full | 250             | 650  | 2000 | ns      |  |

| Driver Output Skew                                            | tskew                                  | $R_{DIFF} = 54\Omega$ , $C_L = 100p$                 | F, ( <u>Figure 2</u> )                                                | Full | -               | 160  | 800  | ns      |  |

| Driver Differential Rise or Fall Time                         | t <sub>R</sub> , t <sub>F</sub>        | $R_{DIFF} = 54\Omega$ , $C_L = 100p$                 | F, ( <u>Figure 2</u> )                                                | Full | 250             | 900  | 2000 | ns      |  |

| Driver Enable to Output High                                  | t <sub>ZH</sub>                        | C <sub>L</sub> = 100pF, SW = GND,                    | (Figure 3, Note 10)                                                   | Full | 250             | 1000 | 2000 | ns      |  |

| Driver Enable to Output Low                                   | t <sub>ZL</sub>                        | C <sub>L</sub> = 100pF, SW = V <sub>CC</sub> ,       | (Figure 3, Note 10)                                                   | Full | 250             | 860  | 2000 | ns      |  |

| Driver Disable from Output High                               | t <sub>HZ</sub>                        | C <sub>L</sub> = 15pF, SW = GND, (                   | Figure 3)                                                             | Full | 300             | 660  | 3000 | ns      |  |

| Driver Disable from Output Low                                | t <sub>LZ</sub>                        | $C_L = 15pF, SW = V_{CC}, (I_{CC})$                  | Figure 3)                                                             | Full | 300             | 640  | 3000 | ns      |  |

| Receiver Input to Output Delay                                | t <sub>PLH</sub> , t <sub>PHL</sub>    | (Figure 4)                                           |                                                                       | Full | 250             | 500  | 2000 | ns      |  |

| Receiver Skew   t <sub>PLH</sub> - t <sub>PHL</sub>           | t <sub>SKD</sub>                       | (Figure 4)                                           |                                                                       | 25   | -               | 60   | -    | ns      |  |

| Receiver Enable to Output High                                | tzH                                    | C <sub>L</sub> = 15pF, SW = GND, (                   | C <sub>L</sub> = 15pF, SW = GND, ( <u>Figure 5</u> , <u>Note 11</u> ) |      | -               | 10   | 50   | ns      |  |

| Receiver Enable to Output Low                                 | t <sub>ZL</sub>                        | $C_L = 15pF$ , $SW = V_{CC}$ , (Figure 5, Note 11)   |                                                                       | Full | -               | 10   | 50   | ns      |  |

| Receiver Disable from Output High                             | t <sub>HZ</sub>                        | C <sub>L</sub> = 15pF, SW = GND, ( <u>Figure 5</u> ) |                                                                       | Full | -               | 10   | 50   | ns      |  |

| Receiver Disable from Output Low                              | t <sub>LZ</sub>                        | $C_L = 15pF$ , SW = $V_{CC}$ , (Figure 5)            |                                                                       | Full | -               | 10   | 50   | ns      |  |

| Maximum Data Rate                                             | f <sub>MAX</sub>                       | 2                                                    |                                                                       | Full | 250             | -    | -    | kbps    |  |

| Time to Shutdown                                              | t <sub>SHDN</sub>                      | (Note 12)                                            |                                                                       | Full | 50              | 120  | 600  | ns      |  |

| Driver Enable from Shutdown to Output High                    | tzh(shdn)                              | C <sub>L</sub> = 100pF, SW = GND,<br>13)             | ( <u>Figure 3</u> , <u>Notes 12</u> and                               | Full | -               | 1000 | 2000 | ns      |  |

| Driver Enable from Shutdown to<br>Output Low                  | <sup>t</sup> ZL(SHDN)                  | $C_L = 100pF, SW = V_{CC},$<br>13)                   | ( <u>Figure 3</u> , <u>Notes 12</u> and                               | Full | -               | 1000 | 2000 | ns      |  |

## **Electrical Specifications** Test Conditions: V<sub>CC</sub> = 4.5V to 5.5V; Unless Otherwise Specified. Typicals are at V<sub>CC</sub> = 5V, T<sub>A</sub> = +25°C, Note 7 (Continued)

| PARAMETER SYMBOL TEST CONDITIONS                    |                                     | TEMP<br>(°C)                                                                         | MIN  | TYP | MAX  | UNIT |      |

|-----------------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------|------|-----|------|------|------|

| Receiver Enable from Shutdown to Output High        | <sup>t</sup> ZH(SHDN)               | C <sub>L</sub> = 15pF, SW = GND, ( <u>Figure 5</u> , <u>Notes 12</u> and <u>14</u> ) |      | -   | 800  | 2500 | ns   |

| Receiver Enable from Shutdown to Output Low         | <sup>t</sup> ZL(SHDN)               | $C_L$ = 15pF, SW = $V_{CC}$ , ( <u>Figure 5</u> , <u>Notes 12</u> and <u>14</u> )    | Full | -   | 800  | 2500 | ns   |

| SWITCHING CHARACTERISTICS (                         | ISL81487L)                          |                                                                                      |      |     |      |      |      |

| Driver Input to Output Delay                        | t <sub>PLH</sub> , t <sub>PHL</sub> | $R_{DIFF} = 54\Omega$ , $C_L = 100pF$ , (Figure 2)                                   | Full | 150 | 650  | 1200 | ns   |

| Driver Output Skew                                  | tskew                               | $R_{DIFF} = 54\Omega$ , $C_L = 100pF$ , (Figure 2)                                   | Full | -   | 160  | 600  | ns   |

| Driver Differential Rise or Fall Time               | t <sub>R</sub> , t <sub>F</sub>     | $R_{DIFF} = 54\Omega$ , $C_L = 100pF$ , ( <u>Figure 2</u> )                          | Full | 250 | 900  | 1200 | ns   |

| Driver Enable to Output High                        | t <sub>ZH</sub>                     | C <sub>L</sub> = 100pF, SW = GND, ( <u>Figure 3</u> , <u>Note 10</u> )               | Full | 100 | 1000 | 1500 | ns   |

| Driver Enable to Output Low                         | t <sub>ZL</sub>                     | C <sub>L</sub> = 100pF, SW = V <sub>CC</sub> , ( <u>Figure 3</u> , <u>Note 10</u> )  | Full | 100 | 1000 | 1500 | ns   |

| Driver Disable from Output High                     | t <sub>HZ</sub>                     | C <sub>L</sub> = 15pF, SW = GND, ( <u>Figure 3</u> )                                 | Full | 150 | 750  | 1500 | ns   |

| Driver Disable from Output Low                      | t <sub>LZ</sub>                     | C <sub>L</sub> = 15pF, SW = V <sub>CC</sub> , ( <u>Figure 3</u> )                    | Full | 150 | 750  | 1500 | ns   |

| Receiver Input to Output Delay                      | t <sub>PLH</sub> , t <sub>PHL</sub> | (Figure 4)                                                                           | Full | 30  | 175  | 250  | ns   |

| Receiver Skew   t <sub>PLH</sub> - t <sub>PHL</sub> | t <sub>SKD</sub>                    | ( <u>Figure 4</u> )                                                                  | 25   | -   | 13   | -    | ns   |

| Receiver Enable to Output High                      | t <sub>ZH</sub>                     | C <sub>L</sub> = 15pF, SW = GND, ( <u>Figure 5</u> , <u>Note 11</u> )                |      | -   | 10   | 50   | ns   |

| Receiver Enable to Output Low                       | t <sub>ZL</sub>                     | C <sub>L</sub> = 15pF, SW = V <sub>CC</sub> , ( <u>Figure 5</u> , <u>Note 11</u> )   | Full | -   | 10   | 50   | ns   |

| Receiver Disable from Output High                   | t <sub>HZ</sub>                     | C <sub>L</sub> = 15pF, SW = GND, ( <u>Figure 5</u> )                                 | Full | -   | 10   | 50   | ns   |

| Receiver Disable from Output Low                    | t <sub>LZ</sub>                     | C <sub>L</sub> = 15pF, SW = V <sub>CC</sub> , ( <u>Figure 5</u> )                    | Full | -   | 10   | 50   | ns   |

| Maximum Data Rate                                   | f <sub>MAX</sub>                    |                                                                                      | Full | 250 | -    | -    | kbps |

| Time to Shutdown                                    | t <sub>SHDN</sub>                   | ( <u>Note 12</u> )                                                                   | Full | 50  | 140  | 600  | ns   |

| Driver Enable from Shutdown to Output High          | tzh(shdn)                           | C <sub>L</sub> = 100pF, SW = GND, ( <u>Figure 3, Notes 12</u> and <u>13</u> )        | Full | 1   | 1100 | 2000 | ns   |

| Driver Enable from Shutdown to Output Low           | <sup>t</sup> ZL(SHDN)               | $C_L$ = 100pF, SW = $V_{CC}$ , ( <u>Figure 3</u> , <u>Notes 12</u> and <u>13</u> )   | Full | -   | 1000 | 2000 | ns   |

| Receiver Enable from Shutdown to Output High        | <sup>t</sup> ZH(SHDN)               | C <sub>L</sub> = 15pF, SW = GND, ( <u>Figure 3</u> , <u>Notes 12</u> and <u>14</u> ) |      | -   | 900  | 2000 | ns   |

| Receiver Enable from Shutdown to Output Low         | <sup>t</sup> ZL(SHDN)               | $C_L$ = 15pF, SW = $V_{CC}$ , ( <u>Figure 3</u> , <u>Notes 12</u> and <u>14</u> )    |      | -   | 900  | 2000 | ns   |

| ESD PERFORMANCE                                     |                                     |                                                                                      | ,    |     | ,    | ,    |      |

| RS-485 Pins (A/Y, B/Z)                              |                                     | Human Body Model                                                                     | 25   | -   | ±15  | -    | kV   |

| All Other Pins                                      |                                     |                                                                                      | 25   | -   | >±7  | -    | kV   |

#### NOTES:

- 7. Currents into device pins are positive; currents out of device pins are negative. Voltages are referenced to ground unless otherwise specified.

- 8. Supply current specification is valid for loaded drivers when DE = 0V.

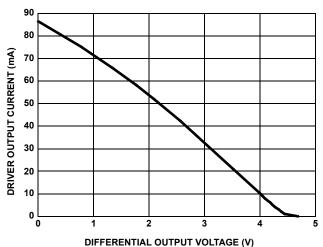

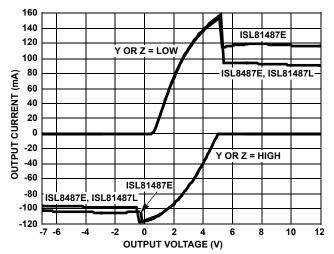

- 9. Applies to peak current. See "Typical Performance Curves" for more information.

- 10. When testing the ISL8487E and ISL81487L, keep  $\overline{RE} = 0$  to prevent the device from entering shutdown (SHDN).

- 11. When testing the ISL8487E and ISL81487L, the RE signal high time must be short enough (typically <200ns) to prevent the device from entering SHDN.

- 12. The ISL8487E and ISL81487L go into SHDN by bringing RE high and DE low. If the inputs are in this state for less than 50ns, the parts are specified not to enter SHDN. If the inputs are in this state for at least 600ns, the parts are specified to enter SHDN. See "Low Power Shutdown Mode (Excluding ISL81487E)" for more information.

- 13. Keep  $\overline{RE} = V_{CC}$  and set the DE signal low time >600ns to ensure that the device enters SHDN.

- 14. Set the RE signal high time >600ns to ensure that the device enters SHDN.

- 15. Devices meeting these limits are denoted as 1/8 unit load (1/8 UL) transceivers. The RS-485 standard allows up to 32 UL on the bus, so there can be 256 1/8 UL devices on a bus.

## **Test Circuits and Waveforms**

FIGURE 1. DRIVER  $V_{\mbox{\scriptsize OD}}$  and  $V_{\mbox{\scriptsize OC}}$

FIGURE 2. DRIVER PROPAGATION DELAY AND DIFFERENTIAL TRANSITION TIMES

## Test Circuits and Waveforms (Continued)

(SHDN) for ISL8487E and ISL81487L only.

| PARAMETER             | OUTPUT | RE                      | DI  | sw              | C <sub>L</sub> (pF) |

|-----------------------|--------|-------------------------|-----|-----------------|---------------------|

| t <sub>HZ</sub>       | Y/Z    | Х                       | 1/0 | GND             | 15                  |

| $t_{LZ}$              | Y/Z    | Х                       | 0/1 | V <sub>CC</sub> | 15                  |

| t <sub>ZH</sub>       | Y/Z    | 0<br>( <u>Note 10</u> ) | 1/0 | GND             | 100                 |

| t <sub>ZL</sub>       | Y/Z    | 0<br>( <u>Note 10</u> ) | 0/1 | V <sub>CC</sub> | 100                 |

| t <sub>ZH(SHDN)</sub> | Y/Z    | 1<br>( <u>Note 12</u> ) | 1/0 | GND             | 100                 |

| <sup>t</sup> ZLSHDN)  | Y/Z    | 1<br>( <u>Note 12</u> ) | 0/1 | V <sub>CC</sub> | 100                 |

FIGURE 3A. TEST CIRCUIT

FIGURE 3B. MEASUREMENT POINTS

FIGURE 3. DRIVER ENABLE AND DISABLE TIMES

FIGURE 4A. TEST CIRCUIT

FIGURE 4B. MEASUREMENT POINTS

FIGURE 4. RECEIVER PROPAGATION DELAY

(SHDN) for ISL8487E and ISL81487L only.

| PARAMETER                       | DE | Α     | SW              |

|---------------------------------|----|-------|-----------------|

| t <sub>HZ</sub>                 | 0  | +1.5V | GND             |

| t <sub>LZ</sub>                 | 0  | -1.5V | V <sub>CC</sub> |

| t <sub>ZH</sub> (Note 11)       | 0  | +1.5V | GND             |

| t <sub>ZL</sub> (Note 11)       | 0  | -1.5V | V <sub>CC</sub> |

| t <sub>ZH(SHDN)</sub> (Note 12) | 0  | +1.5V | GND             |

| t <sub>ZL(SHDN)</sub> (Note 12) | 0  | -1.5V | V <sub>CC</sub> |

FIGURE 5A. TEST CIRCUIT

FIGURE 5B. MEASUREMENT POINTS

FIGURE 5. RECEIVER ENABLE AND DISABLE TIMES

## Application Information

RS-485 and RS-422 are differential (balanced) data transmission standards for use in long haul or noisy environments. RS-422 is a subset of RS-485, so RS-485 transceivers are also RS-422 compliant. RS-422 is a point-to-multipoint (multidrop) standard that allows only one driver and up to 10 receivers on each bus (assuming one unit load devices). RS-485 is a true multipoint standard that allows up to 32 one unit load devices (any combination of drivers and receivers) on each bus. To allow for multipoint operation, the RS-485 specification requires that drivers handle bus contention without sustaining any damage.

An important advantage of RS-485 is the extended Common-Mode Range (CMR), which specifies that the driver outputs and receiver inputs withstand signals ranging from +12V to -7V. RS-422 and RS-485 are intended for runs as long as 4000ft, so the wide CMR is necessary to handle ground potential differences and voltages induced in the cable by external fields.

#### Receiver Features

These devices use a differential input receiver for maximum noise immunity and common-mode rejection. Input sensitivity is  $\pm 200$ mV, as required by the RS-422 and RS-485 specifications.

The receiver input resistance of  $96k\Omega$  surpasses the RS-422 specification of  $4k\Omega$  and is eight times the RS-485 Unit Load (UL) requirement of  $12k\Omega$  minimum. Thus, these products are known as one-eighth UL transceivers. A network can host up to 256 of these devices still complying with the RS-485 loading specification.

The receiver inputs function with common-mode voltages as great as  $\pm 7V$  outside the power supplies (that is, +12V and -7V), making them ideal for long networks in which induced voltages are a realistic concern.

All the receivers include a "fail-safe if open" function that guarantees a high level receiver output if the receiver inputs are unconnected (floating).

Receivers easily meet the data rates supported by the corresponding driver. The receiver outputs are three-statable using the active low  $\overline{\text{RE}}$  input.

#### **Driver Features**

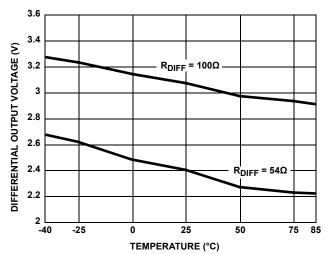

The RS-485/422 driver is a differential output device that delivers at least 1.5V across a  $54\Omega$  load (RS-485) and at least 2V across a  $100\Omega$  load (RS-422). The drivers feature low propagation delay skew to maximize bit width and to minimize EMI.

Driver outputs are three-statable using the active high DE input

The ISL8487E and ISL81487L driver outputs are slew rate limited to minimize EMI and to minimize reflections in unterminated or improperly terminated networks. The

maximum data rate on these slew rate limited versions is 250kbps. The ISL81487E drivers are not limited, so faster output transition times allow data rates of at least 5Mbps.

#### Data Rate, Cables, and Terminations

RS-485/422 are intended for network lengths up to 4000ft, but the maximum system data rate decreases as the transmission length increases. Devices operating at 5Mbps are limited to lengths less than a few hundred feet, while the 250kbps versions can operate at full data rates with lengths in excess of 1000ft.

Twisted pair cable is the cable of choice for RS-485/422 networks. Twisted pair cables tend to pick up noise and other electromagnetically induced voltages as common-mode signals that are effectively rejected by the differential receivers in these ICs.

Proper termination is imperative to minimize reflections when using the 5Mbps device. Short networks using the 250kbps versions do not need to be terminated, but terminations are recommended unless power dissipation is an overriding concern.

In point-to-point or point-to-multipoint (single driver on bus) networks, terminate the main cable in its characteristic impedance (typically  $120\Omega)$  at the end farthest from the driver. In multi-receiver applications, keep stubs connecting receivers to the main cable as short as possible. In multipoint (multi-driver) systems, terminate the main cable in its characteristic impedance at both ends. Keep stubs connecting a transceiver to the main cable as short as possible.

#### **Built-In Driver Overload Protection**

The RS-485 specification requires that drivers survive worst case bus contentions undamaged. These devices meet this requirement with driver output short-circuit current limits and on-chip thermal shutdown circuitry.

The driver output stages incorporate short-circuit current limiting circuitry that ensures the output current never exceeds the RS-485 specification, even at the common-mode voltage range extremes. These devices also use a foldback circuit that reduces the short-circuit current and as a result, the power dissipation when the contending voltage exceeds either supply.

In the event of a major short-circuit condition, the thermal shutdown feature disables the drivers when the die temperature becomes excessive. This eliminates the power dissipation, allowing the die to cool. The drivers automatically re-enable after the die temperature drops about 15°C. If the condition persists, the thermal shutdown/re-enable cycle repeats until the fault is cleared. Receivers stay operational during thermal shutdown.

## Low Power Shutdown Mode (Excluding ISL81487E)

These CMOS transceivers all use a fraction of the power required by their bipolar counterparts, but the ISL8487E and ISL81487L include a shutdown feature that reduces the already low quiescent I $_{CC}$  to a 500nA trickle. They enter shutdown whenever the receiver and driver are simultaneously disabled ( $\overline{RE}$  =  $V_{CC}$  and DE = GND) for a period of at least 600ns. Disabling both the driver and the receiver for less than 50ns guarantees that shutdown is not entered.

Note that receiver and driver enable times increase when enabling from shutdown. Refer to <u>Note 10</u> through <u>14</u> at the end of the <u>"Electrical Specifications"</u> table for more information.

#### **ESD Protection**

All pins on the interface devices include Class 3 Human Body Model (HBM) ESD protection structures, but the RS-485 pins (driver outputs and receiver inputs) incorporate advanced structures allowing them to survive ESD events in excess of  $\pm 15 \text{kV}$  HBM. The RS-485 pins are particularly vulnerable to

ESD damage because they typically connect to an exposed port on the exterior of the finished product. Touching the port pins or connecting a cable can cause an ESD event that destroys unprotected ICs. The ESD structures protect the device whether or not it is powered up, protect without allowing any latchup mechanism to activate, and without degrading the RS-485 common-mode range of -7V to +12V. This built-in ESD protection eliminates the need for board level protection structures (for example, transient suppression diodes), and the associated undesirable capacitive load they present.

#### **Human Body Model Testing**

This test method emulates the ESD event delivered to an IC during human handling. The tester delivers the charge stored on a 100pF capacitor through a 1.5k $\Omega$  current limiting resistor into the pin under test. The HBM method determines an IC's ability to withstand the ESD events typically present during handling and manufacturing. The RS-485 pin survivability on this high ESD family has been characterized to be in excess of  $\pm$ 15kV for discharges to GND.

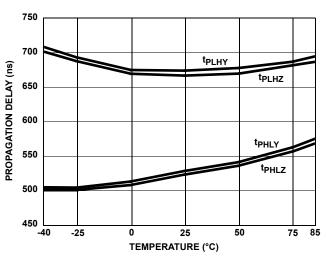

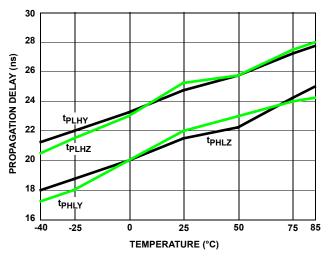

## **Typical Performance Curves** V<sub>CC</sub> = 5V, T<sub>A</sub> = +25°C, ISL8487E, ISL81487L, and ISL81487E; unless otherwise specified

FIGURE 6. DRIVER OUTPUT CURRENT vs DIFFERENTIAL OUTPUT VOLTAGE

FIGURE 7. DRIVER DIFFERENTIAL OUTPUT VOLTAGE vs TEMPERATURE

## Typical Performance Curves V<sub>CC</sub> = 5V, T<sub>A</sub> = +25°C, ISL8487E, ISL81487L, and ISL81487E; unless otherwise specified

FIGURE 8. DRIVER OUTPUT CURRENT vs SHORT-CIRCUIT VOLTAGE

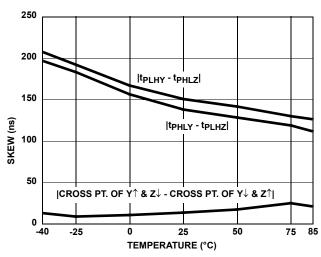

FIGURE 10. DRIVER PROPAGATION DELAY vs TEMPERATURE (ISL8487E and ISL81487L)

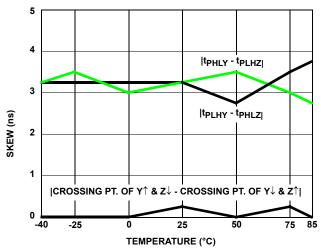

FIGURE 12. DRIVER PROPAGATION DELAY vs TEMPERATURE (ISL81487E)

FIGURE 9. SUPPLY CURRENT vs TEMPERATURE

FIGURE 11. DRIVER SKEW vs TEMPERATURE (ISL8487E and ISL81487L)

FIGURE 13. DRIVER SKEW vs TEMPERATURE (ISL81487E)

## **Typical Performance Curves** V<sub>CC</sub> = 5V, T<sub>A</sub> = +25°C, ISL8487E, ISL81487L, and ISL81487E; unless otherwise specified

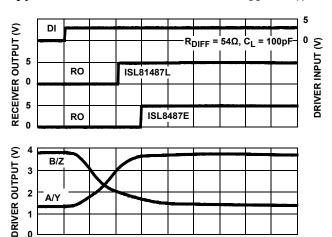

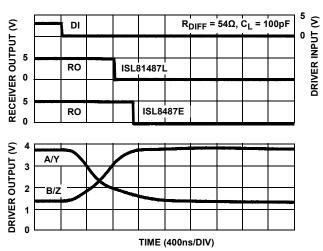

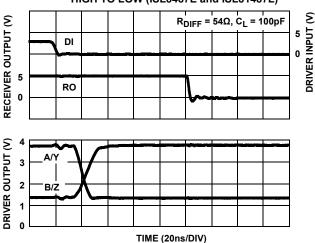

FIGURE 14. DRIVER AND RECEIVER WAVEFORMS, LOW TO HIGH (ISL8487E and ISL81487L)

TIME (400ns/DIV)

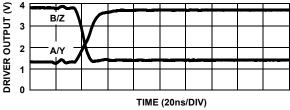

FIGURE 16. DRIVER AND RECEIVER WAVEFORMS, LOW TO HIGH (ISL81487E)

FIGURE 15. DRIVER AND RECEIVER WAVEFORMS, HIGH TO LOW (ISL8487E and ISL81487L)

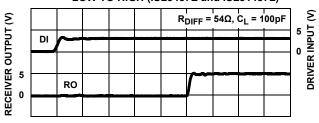

FIGURE 17. DRIVER AND RECEIVER WAVEFORMS, HIGH TO LOW (ISL81487E)

## Die Characteristics

SUBSTRATE POTENTIAL (POWERED UP):

**GND**

TRANSISTOR COUNT:

518

PROCESS:

Si Gate CMOS

**Revision History** The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please visit our website to make sure you have the latest revision.

| DATE         | REVISION | CHANGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

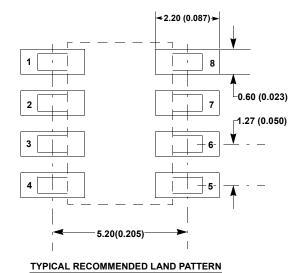

| Sep 20, 2018 | FN6051.8 | Applied Renesas Header/Footer. Added Related Literature section. Updated Ordering Information table by removing retired parts ISL8487EIB, ISL81487LIB, ISL81487LIP, and ISL81487EIP, adding Notes 1 and 3, and adding tape and reel parts and column. Updated the Typical Operating Circuit diagram on page 2. Added Revision History section. Updated POD M8.15 to the latest revision. Changes are as follows: -Revision 1: Initial revision -Revision 1 to revision 2: Updated to new package outline drawing format by removing table, moving dimensions onto drawing, and adding land pattern -Revision 2 to revision 3: Changed the following values in Typical Recommended Landing Pattern: 2.41(0.095) to 2.20 (0.087) 0.76(0.030) to 0.60(0.023) 0.200 to 5.20(0.205) -Revision 3 to revision 4: Changed text in Note 1 from "1982" to "1994" |

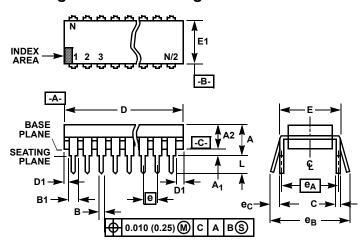

## Package Outline Drawings

#### NOTES:

- Controlling Dimensions: INCH. In case of conflict between English and Metric dimensions, the inch dimensions control.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- 3. Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication No. 95.

- 4. Dimensions A, A1 and L are measured with the package seated in JEDEC seating plane gauge GS-3.

- D, D1, and E1 dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

- E and e<sub>A</sub> are measured with the leads constrained to be perpendicular to datum -C-

- e<sub>B</sub> and e<sub>C</sub> are measured at the lead tips with the leads unconstrained. e<sub>C</sub> must be zero or greater.

- 8. B1 maximum dimensions do not include dambar protrusions. Dambar protrusions shall not exceed 0.010 inch (0.25mm).

- 9. N is the maximum number of terminal positions.

- Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3, E42.6 will have a B1 dimension of 0.030 - 0.045 inch (0.76 - 1.14mm).

### E8.3 (JEDEC MS-001-BA ISSUE D) 8 LEAD DUAL-IN-LINE PLASTIC PACKAGE

|                | INCHES    |       | MILLIMETERS |       |       |

|----------------|-----------|-------|-------------|-------|-------|

| SYMBOL         | MIN       | MAX   | MIN         | MAX   | NOTES |

| Α              | -         | 0.210 | -           | 5.33  | 4     |

| A1             | 0.015     | -     | 0.39        | -     | 4     |

| A2             | 0.115     | 0.195 | 2.93        | 4.95  | -     |

| В              | 0.014     | 0.022 | 0.356       | 0.558 | -     |

| B1             | 0.045     | 0.070 | 1.15        | 1.77  | 8, 10 |

| С              | 0.008     | 0.014 | 0.204       | 0.355 | -     |

| D              | 0.355     | 0.400 | 9.01        | 10.16 | 5     |

| D1             | 0.005     | -     | 0.13        | -     | 5     |

| Е              | 0.300     | 0.325 | 7.62        | 8.25  | 6     |

| E1             | 0.240     | 0.280 | 6.10        | 7.11  | 5     |

| е              | 0.100 BSC |       | 2.54 BSC    |       | -     |

| e <sub>A</sub> | 0.300 BSC |       | 7.62 BSC    |       | 6     |

| e <sub>B</sub> | -         | 0.430 | -           | 10.92 | 7     |

| L              | 0.115     | 0.150 | 2.93        | 3.81  | 4     |

| N              | 8         |       | 8           |       | 9     |

Rev. 0 12/93

For the most recent package outline drawing, see <u>E8.3</u>.

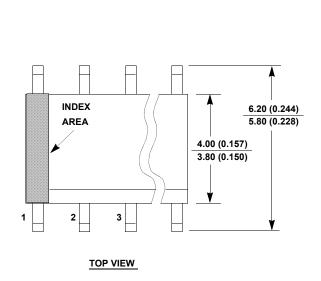

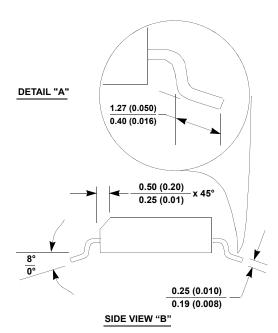

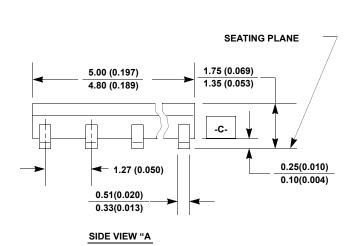

## 8 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE Rev 4, 1/12

#### NOTES:

- 1. Dimensioning and tolerancing per ANSI Y14.5M-1994.

- Package length does not include mold flash, protrusions or gate burrs. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- 3. Package width does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

- The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 5. Terminal numbers are shown for reference only.

- The lead width as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch).

- Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

- 8. This outline conforms to JEDEC publication MS-012-AA ISSUE C.