# RENESAS

# DATASHEET

# ISL91132

High Efficiency 1.8A Boost Regulator with Input-to-Output Bypass

FN8637 Rev.2.00 Dec 20, 2018

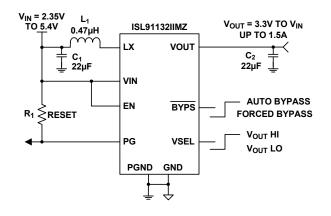

The <u>ISL91132</u> is an integrated boost switching regulator for battery powered applications. The device provides a power supply solution for products using a one cell Li-ion or Li-polymer battery.

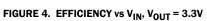

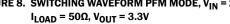

The device is capable of delivering up to 1.8A output current from V<sub>IN</sub> = 2.5V and V<sub>OUT</sub> = 3.3V. The no-load quiescent current is only 108µA in Boost mode and 45µA in Forced Bypass mode, which significantly reduces the standby consumption.

The ISL91132 offers a Bypass mode operation where the output is directly connected to the input through a  $38m\Omega$  MOSFET to allow a significantly lower dropout voltage. The Bypass mode can be entered by an external command, or by auto bypass. The Forced Bypass mode allows the output voltage to operate close to the input voltage and improves the efficiency under these conditions.

The ISL91132 is designed to support six fixed output voltages ranging from 3.15V to 5V. A voltage select pin is available for each output variant to scale up the output voltage by a small offset to compensate the load transient droop.

The ISL91132 requires only an inductor and a few external components to operate. The 2.5MHz switching frequency further reduces the size of external components.

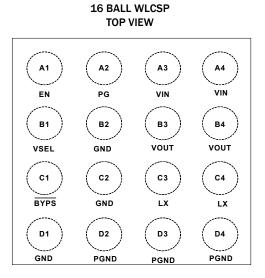

The ISL91132 is available in a 16 bump, 0.4mm pitch, 1.78mmx1.78mm WLCSP.

### **Features**

- Input voltage range: 2.35V to 5.4V

- Output current: up to 1.8A (V<sub>IN</sub> = 2.5V, V<sub>OUT</sub> = 3.3V)

- + Burst current up to 2A (V\_{IN} = 2.5V, V\_{OUT} = 3.3V, t\_{ON} < 600 \mu s, T = 4.6 ms)

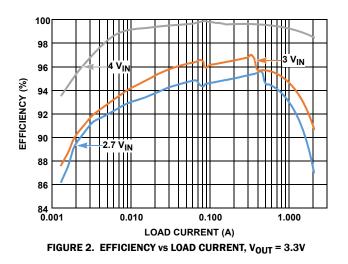

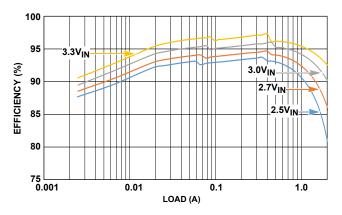

- High efficiency: up to 96%

- 108µA quiescent current minimizes standby consumption in Boost mode, 45µA in Forced Bypass mode

- 2.5MHz switching frequency minimizes external component size

- Forced Bypass or Auto Bypass modes with a  $38 m \Omega$  switch

- PFM mode at light-load currents

- Fully protected for overcurrent, over-temperature, and undervoltage

- Load disconnect when disabled

- Small 1.78mmx1.78mm WLCSP

# **Applications**

- Smartphones and tablet PCs

- Wireless communication devices

- 2G/3G/4G RF power amplifiers

- USB OTG power source

## **Related Literature**

For a full list of related documents, visit our website:

- ISL91132 device page

- AN1942, "ISL91132 Evaluation Board User Guide"

FIGURE 1. TYPICAL APPLICATION

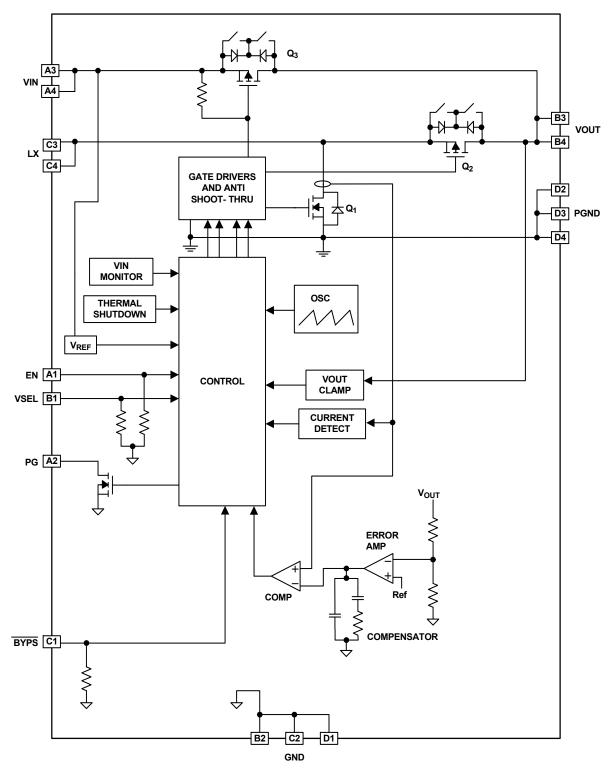

# **Block Diagram**

FIGURE 3. BLOCK DIAGRAM

### **Pin Configuration**

# **Pin Descriptions**

| PIN #         | PIN<br>NAMES | DESCRIPTION                                                                                                                                                                                                 |

|---------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B3, B4        | VOUT         | Boost output; connect a $22\mu F$ capacitor to PGND.                                                                                                                                                        |

| C3, C4        | LX           | Inductor connection                                                                                                                                                                                         |

| D2, D3,<br>D4 | PGND         | Power ground for high switching current.                                                                                                                                                                    |

| A3, A4        | VIN          | Power input; Range: 2.35V to 5.4V. Connect a 22µF capacitor to PGND.                                                                                                                                        |

| B1            | VSEL         | Output selection between LO and HI. While<br>operating in Boost mode, pull this pin HI to select<br>the high output level. To select the low output<br>level, pull this pin to LO.                          |

| A2            | PG           | Open-drain output; provides output power-good status.                                                                                                                                                       |

| A1            | EN           | Logic input; drive HIGH to enable device.                                                                                                                                                                   |

| C1            | BYPS         | Force bypass input; Pull this pin LO to activate<br>Forced Bypass mode, where both $Q_2$ and $Q_3$ are<br>turned on, the rest of the IC is disabled. When this<br>pin is HI, Auto Bypass mode is activated. |

| B2, C2,<br>D1 | GND          | Analog ground pin                                                                                                                                                                                           |

#### PART NUMBER TEMP RANGE TAPE AND REEL PACKAGE PKG. (UNITS) (Note 1) PART MARKING (RoHS Compliant) DWG. # (Notes 2, 3) V<sub>OUT</sub> (V) (°C) ISL91132IILZ-T 132L 3.15/3.3 -40 to +85 3k 16 Ball WLCSP W4x4.16E ISL91132IIMZ-T 132M 3.3/3.5 -40 to +85 16 Ball WLCSP W4x4.16E 3k 132N -40 to +85 ISL91132IINZ-T 3.5/3.7 3k 16 Ball WLCSP W4x4.16E ISL91132II0Z-T 1320 3.7/3.77 -40 to +85 16 Ball WLCSP W4x4.16E 3k ISL91132IIPZ-T 132P 4.5/4.76 -40 to +85 3k 16 Ball WLCSP W4x4.16E ISL91132IIQZ-T -40 to +85 16 Ball WLCSP W4x4.16E 132Q 5.0/5.2 3k ISL91132IIM-EVZ Evaluation Board for ISL91132IIMZ

## **Ordering Information**

NOTES:

1. See <u>TB347</u> for details about reel specifications.

These Pb-free WLCSP packaged products employ special Pb-free material sets; molding compounds/die attach materials and SnAgCu - e1 solder ball terminals, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Pb-free WLCSP packaged products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

3. For Moisture Sensitivity Level (MSL), see the ISL91132 device page. For more information about MSL, see TB363.

#### **Absolute Maximum Ratings**

| VIN                                                    |

|--------------------------------------------------------|

| LX0.3V to 6.5V                                         |

| GND, PGND                                              |

| All Other Pins                                         |

| ESD Rating                                             |

| Human Body Model (Tested per JESD22-A114F) 3kV         |

| Machine Model (Tested per JESD22-A115-C) 225V          |

| Charge Device Model (Tested per JESD22-C101F) 2kV      |

| Latch-Up (Tested per JESD-78D; Class 2, Level A) 100mA |

#### **Thermal Information**

| Thermal Resistance (Typical)                        | $\theta_{JA}$ (°C/W) | θ <sub>JB</sub> (°C/W) |

|-----------------------------------------------------|----------------------|------------------------|

| 16 Ball WLCSP Package ( <u>Notes 4</u> , <u>5</u> ) | 70                   | 14                     |

| Maximum Junction Temperature                        |                      | +125°C                 |

| Storage Temperature Range                           | 6                    | 5°C to +150°C          |

| Pb-Free Reflow Profile                              |                      | see <u>TB493</u>       |

#### **Recommended Operating Conditions**

| Ambient Temperature Range                                                   | 40°C to +85°C    |

|-----------------------------------------------------------------------------|------------------|

| Supply Voltage Range (Boost Only)                                           | 2.35V to 5.5V    |

| Max Load Current (V <sub>IN</sub> = 2.5V V <sub>OUT</sub> = 3.3V)           | 1.8A DC          |

| Max Load Current ( $V_{IN}$ = 2.5V $V_{OUT}$ = 3.3V, $t_{ON}$ = 600 $\mu$ s | s, T = 4.6ms) 2A |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

4.  $\theta_{JA}$  is measured in free air with the component mounted on a high-effective thermal conductivity test board with "direct attach" features. See TB379.

5. For  $\theta_{JB}$ , the board temp is taken on the board near the edge of the package, on a trace at the middle of one side. See <u>TB379</u>.

# **Electrical Specifications** $V_{IN} = V_{EN} = 3V$ , $L_1 = 0.47 \mu$ H, $C_1 = C_2 = 22 \mu$ F, $T_A = +25$ °C. Boldface limits apply across the operating temperature range, -40°C to +85°C.

| PARAMETER                                          | SYMBOL                | TEST CONDITIONS                                 | MIN<br>( <u>Note 6</u> ) | TYP<br>( <u>Note 7</u> ) | MAX<br>( <u>Note 6</u> ) | UNIT |

|----------------------------------------------------|-----------------------|-------------------------------------------------|--------------------------|--------------------------|--------------------------|------|

| POWER SUPPLY                                       |                       |                                                 |                          |                          |                          |      |

| Input Voltage Range                                | V <sub>IN</sub>       |                                                 | 2.35                     |                          | 5.40                     | v    |

| V <sub>IN</sub> Undervoltage Lockout Threshold     | V <sub>UVLO</sub>     | Rising                                          |                          | 2.20                     | 2.35                     | v    |

|                                                    |                       | Falling                                         | 1.9                      | 2.0                      |                          | v    |

| VIN Supply Current in Boost Mode                   | IVIN_BOOST            | PFM mode, no external load on V <sub>OUT</sub>  |                          | 108                      | 180                      | μA   |

| V <sub>IN</sub> Supply Current in Auto Bypass Mode | IVIN_BYP1             | V <sub>IN</sub> = 4.2V, V <sub>OUT</sub> < 4.2V |                          | 80                       | 120                      | μA   |

| VIN Supply in Forced Bypass Mode                   | I <sub>VIN_BYP2</sub> | V <sub>IN</sub> = 3.5V                          |                          | 45                       | 70                       | μA   |

| V <sub>IN</sub> Supply Current, Shutdown           | I <sub>SD</sub>       | EN = GND, V <sub>IN</sub> = 3.6V                |                          | 1.3                      | 5                        | μA   |

| OUTPUT VOLTAGE REGULATION                          |                       | 1                                               |                          |                          |                          |      |

| Output Voltage Range, Boost Mode                   | V <sub>OUT</sub>      | I <sub>OUT</sub> = 100mA                        | 3.15                     |                          | 5.20                     | v    |

| Output Voltage Accuracy                            |                       | V <sub>IN</sub> = 3.6V                          | -2                       |                          | 4                        | %    |

| Output Voltage Clamp                               | V <sub>CLAMP</sub>    | V <sub>OUT</sub> rising                         | 5.4                      |                          | 5.7                      | v    |

| Output Voltage Clamp Hysteresis                    | V <sub>CLAMP_HS</sub> |                                                 |                          | 170                      |                          | mV   |

| INDUCTOR VALLEY CURRENT LIMIT                      |                       | 1                                               |                          |                          |                          |      |

| Inductor Valley Current Limit                      | I <sub>PK_LMT</sub>   | V <sub>IN</sub> = 2.6V                          | 2.78                     | 3.20                     | 3.78                     | Α    |

| During Soft-Start                                  | IPK_LMT_SU            |                                                 |                          | 1.5                      |                          | Α    |

| DC/DC SWITCHING SPECIFICATIONS                     |                       |                                                 | ł                        | 1                        | l                        |      |

| Oscillator Frequency                               | fsw                   |                                                 | 2.1                      | 2.5                      | 2.9                      | MHz  |

| BOOST ON-RESISTANCE                                | <b>I</b>              |                                                 | I                        |                          |                          |      |

| P-Channel MOSFET (Q2) ON-Resistance                | rDSON_P               | V <sub>IN</sub> = 3.5V, I <sub>O</sub> = 200mA  |                          | 0.04                     |                          | Ω    |

| N-Channel MOSFET (Q1) ON-Resistance                | rdson_n               | V <sub>IN</sub> = 3.5V, I <sub>O</sub> = 200mA  |                          | 0.045                    |                          | Ω    |

| PFM/PWM TRANSITION                                 | 1                     | 1                                               |                          | 1                        | 1                        |      |

| Load Current Threshold, PFM to PWM                 |                       | V <sub>IN</sub> = 3.0V, V <sub>OUT</sub> = 3.3V |                          | 500                      |                          | mA   |

| Load Current Threshold, PWM to PFM                 |                       | V <sub>IN</sub> = 3.0V, V <sub>OUT</sub> = 3.3V |                          | 300                      |                          | mA   |

# **Electrical Specifications** $V_{IN} = V_{EN} = 3V$ , $L_1 = 0.47\mu$ H, $C_1 = C_2 = 22\mu$ F, $T_A = +25$ °C. Boldface limits apply across the operating temperature range, -40°C to +85°C. (Continued)

| PARAMETER                                                      | SYMBOL               | TEST CONDITIONS                                                     | MIN<br>( <u>Note 6</u> ) | TYP<br>( <u>Note 7</u> ) | MAX<br>( <u>Note 6</u> ) | UNIT |

|----------------------------------------------------------------|----------------------|---------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|------|

| THERMAL SHUTDOWN                                               |                      | l                                                                   |                          |                          |                          |      |

| Thermal Warning                                                |                      |                                                                     |                          | 120                      |                          | °C   |

| Thermal Shutdown                                               |                      |                                                                     |                          | 150                      |                          | °C   |

| Thermal Shutdown and Thermal Warning<br>Hysteresis             |                      |                                                                     |                          | 20                       |                          | °C   |

| LEAKAGE CURRENT                                                |                      |                                                                     | J                        |                          |                          |      |

| V <sub>OUT</sub> to V <sub>IN</sub> Reverse Leakage            | ILEAK                | V <sub>IN</sub> = 3V, V <sub>OUT</sub> = 5V, EN = 0                 |                          | 0.3                      | 1.0                      | μA   |

| V <sub>IN</sub> to V <sub>OUT</sub> Leakage                    |                      | $V_{IN} = 3V, V_{OUT} = 0V, EN = 0$                                 |                          | 0.05                     | 1.00                     | μA   |

| LX Pin Leakage Current                                         | INFETLEAK            | V <sub>LX</sub> = 5V, EN = 0                                        | -1                       |                          | 1                        | μA   |

| SOFT-START                                                     |                      |                                                                     |                          | 1                        |                          |      |

| Level 1 Linear Start-Up Current, Fast                          | I <sub>LIN1</sub>    | ISL9113211LZ, ISL9113211MZ, ISL9113211NZ,<br>ISL91132110Z           |                          | 1300                     |                          | mA   |

| Level 1 Linear Start-Up Current, Slow                          |                      | ISL91132IIPZ, ISL91132IIQZ                                          |                          | 350                      |                          |      |

| Level 2 Linear Start-Up Current, Fast                          | I <sub>LIN2</sub>    | ISL9113211LZ, ISL9113211MZ, ISL9113211NZ,<br>ISL91132110Z           |                          | 2400                     |                          | mA   |

| Level 1 Linear Start-Up Current, Slow                          |                      | ISL91132IIPZ, ISL91132IIQZ                                          |                          | 700                      |                          |      |

| Soft-Start Time EN Hi to Regulation                            | t <sub>SS</sub>      | ISL91132IILZ, ISL91132IIMZ, ISL91132IINZ,<br>ISL91132IIOZ, 50Ω load |                          | 600                      |                          | μs   |

|                                                                |                      | ISL91132IIPZ, ISL91132IIQZ, 50Ω load                                |                          | 1200                     |                          | μs   |

| BYPASS MODE                                                    |                      |                                                                     |                          | 1                        |                          |      |

| Bypass P-Channel MOSFET (Q <sub>3</sub> )<br>ON-Resistance     | <sup>r</sup> dson_bp | I <sub>OUT</sub> = 600mA, V <sub>IN</sub> = 3.5V                    |                          | 0.038                    |                          | Ω    |

| Auto Bypass Hysteresis                                         | V <sub>BYP_Hys</sub> |                                                                     |                          | 100                      |                          | mV   |

| Bypass Mode Current Limit (for ISL91132IIPZ and ISL91132IIPZ ) | V <sub>OCP_BYP</sub> | $V_{IN} = 5V$ , measured by $V_{IN} - V_{OUT}$                      |                          | 150                      |                          | mV   |

| LOGIC INPUTS/OUTPUT (PG, EN, VSEL, BYPS                        | <u>5</u> )           |                                                                     |                          | 1                        |                          |      |

| Input Leakage, PG                                              | I <sub>PG_LEAK</sub> | PG = HIGH                                                           |                          | 0.05                     | 1                        | μΑ   |

| Input HIGH Voltage, EN, VSEL, BYPS                             | VIH                  |                                                                     | 1.2                      |                          |                          | v    |

| Input LOW Voltage, EN, VSEL, BYPS                              | VIL                  |                                                                     |                          |                          | 0.4                      | v    |

| Pull-Down Resistance, EN, VSEL, BYPS                           | R <sub>PD</sub>      |                                                                     |                          | 1.5                      |                          | MΩ   |

| FAULT Reset Timer                                              | t <sub>FRST</sub>    |                                                                     |                          | 20                       |                          | ms   |

NOTES:

6. Parameters with MIN and/or MAX limits are 100% tested at +25 °C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

7. Typical values are for  $T_A = +25$  °C and  $V_{IN} = 3V$ .

### **Typical Performance Curves**

FIGURE 5. EFFICIENCY vs LOAD CURRENT,  $V_{OUT} = 3.5V$

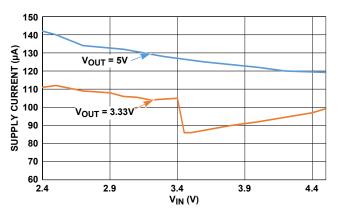

FIGURE 9. SWITCHING WAVEFORM PWM MODE,  $\rm V_{IN}$  = 2.7V,  $\rm I_{OUT}$  = 500mA,  $\rm V_{OUT}$  = 3.3V

# Typical Performance Curves (Continued)

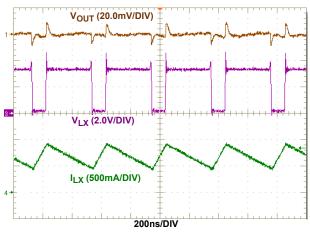

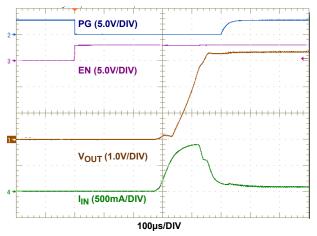

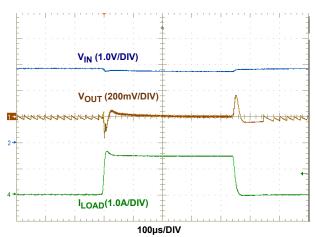

FIGURE 11. LOAD STEP RESPONSE,  $V_{IN} = 2.7V$ ,  $I_{LOAD} = 10mA \rightarrow 1500mA \rightarrow 10mA$

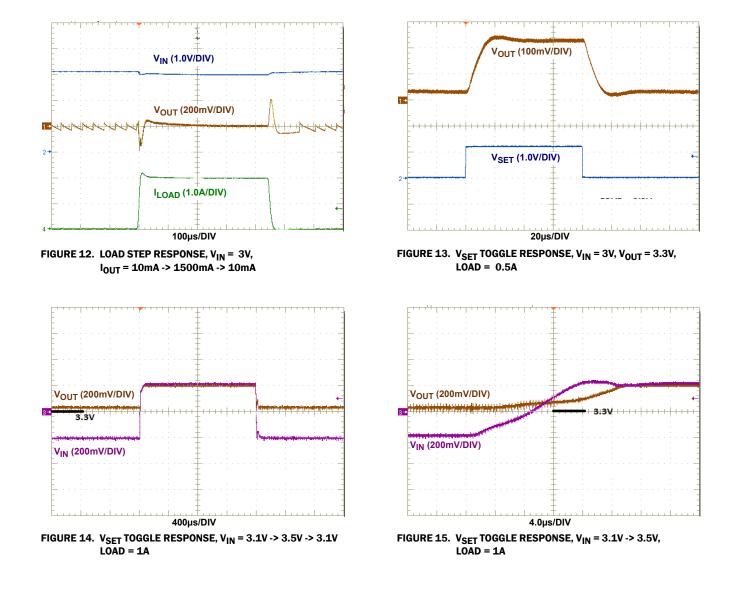

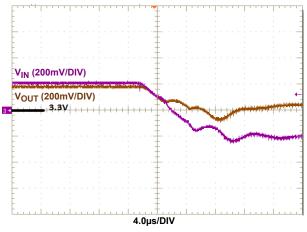

### **Typical Performance Curves** (Continued)

# **Functional Description**

#### **Functional Overview**

The ISL91132 implements a complete boost switching regulator, with PWM controller, internal switches, references, protection circuitry, and bypass control. See the "Block Diagram" on page 2.

#### Internal Supply and References

The ISL91132 provides a power input pin, see "Block Diagram" on page 2. The VIN pin provides an operating voltage source required for stable V<sub>REF</sub> generation. During the Bypass mode, the VIN pin also carries the input power to the output. Separate ground pins (GND and PGND) are provided to avoid problems caused by ground shift due to the high switching currents.

#### **Enable Input**

A master enable pin. EN, allows the device to be enabled. Driving EN low invokes a power-down mode, where most internal device functions, including input and output power-good detection, are disabled.

#### **POR Sequence and Soft-Start**

Bringing the EN pin high allows the device to power up. A number of events occur during the start-up sequence. The internal voltage reference powers up and stabilizes. The device then starts operating.

When the device is enabled, the start-up cycle starts in the Linear mode. During the linear phase, the bypass FET  $Q_3$  is controlled as a constant current source, delivering a fixed current  $\mathsf{I}_{\mathsf{LIN1}}$  as shown in the "Electrical Specifications" table on page 5. If the output voltage has not reached the  $V_{IN}$  - 300mV threshold within the 512 $\mu$ s time interval during the I<sub>LIN1</sub> mode, the ISL91132 enters a Level 2 Linear mode, where the bypass MOSFET Q<sub>3</sub> is controlled as a constant current source, delivering a fixed current ILIN2 as shown in the "Electrical Specifications" table on page 5. If  $V_{OUT}$  still has not reached the  $V_{IN}$  - 300mV threshold within 1024µs in the ILIN2 current, a fault condition is triggered.

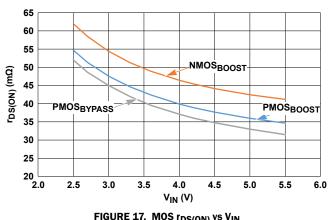

FIGURE 17. MOS rDS(ON) vs VIN

When  $V_{OUT}$  has successfully risen to within 300mV from  $V_{IN}$ within either the  $I_{\mbox{LIN2}}$  or  $I_{\mbox{LIN2}}$  period, the boost operation starts. The boost operation begins with a fixed duty-cycle of 75% with a reduced current limit (IPK LMT SU) as shown in the "Electrical Specifications" on page 4. The fixed duty-cycle operation continues until the output voltage reaches 2.3V, then the closed-loop current mode PWM loop overrides the duty cycle to regulate the output voltage.

If the output has not reached the target regulation voltage after 64µs, a FAULT condition is triggered.

Due to the soft-start current limits and time constraints, it is recommended that the output current be limited to below 500mA at power-up, especially when the output capacitor value is large. If the output current exceeds the start-up capability, a fault condition is triggered. The regulator shuts down for 20ms, then soft-start repeats. This Hiccup mode continues until the output current is reduced to reach the regulated output voltage.

#### **Boost Mode Overcurrent Protection**

When the inductor peak current in the N-channel MOSFET hits the current limit for 16 consecutive switching cycles, the internal protection circuit is triggered, and switching is stopped for approximately 20ms. The device then performs a soft-start cycle. If the external output overcurrent condition exists after the soft-start cycle, the device detects 16 consecutive switching cycles reaching the valley current threshold. The process repeats as long as the external overcurrent condition is present. This behavior is called 'Hiccup mode'.

#### **Short-Circuit Protection**

The ISL91132 provides short-circuit protection by monitoring the output voltage. When output voltage is sensed to be lower than a certain threshold, the PWM oscillator frequency is reduced in order to protect the device from damage. The N-channel MOSFET peak current limit remains active during this state.

#### **Boost Conversion Topology**

The ISL91132 integrates one N-channel MOSFET ( $Q_1$  in the block diagram on page 2) and one P-channel MOSFET ( $Q_2$ ) to implement a synchronous boost converter. A body switch scheme is employed in  $Q_2$  to implement the true shutdown function when the device is disabled. Otherwise, the step-up converter has a conduction path from the input to the output, or from the output to the input, using the body diode of the P-channel MOSFET.

#### **PWM Operation**

The control scheme of the device is based on the valley current mode control, and the control loop is compensated internally. The valley current of the P-channel MOSFET switch is sensed to limit the maximum current flowing through the switch and the inductor. The typical current limit is set to 3A.

The control circuit includes a ramp generator, a slope compensator, an error amplifier, and a PWM comparator. The ramp signal is derived from the inductor current. This ramp signal is then compared to the error amplifier output to generate the PWM gating signals for both the N-channel and the P-channel MOSFETs. The PWM operation is initialized by the clock from the internal oscillator (typical 2.5MHz). The P-channel MOSFET is turned on at the beginning of a PWM cycle, the N-channel MOSFET remains off, and the current starts ramping down. When the sum of the ramp and the slope compensator output reaches the error amplifier output voltage, the PWM comparator outputs a signal to turn off the P-channel MOSFET. At this time, both MOSFETs remain off during the dead-time interval. After the dead time, the N-channel MOSFET is turned on and remains on until the end of this PWM cycle. During this time, the inductor current ramps up until the next clock. Following a short dead time, the P-channel MOSFET is turned on again, repeating as previously described.

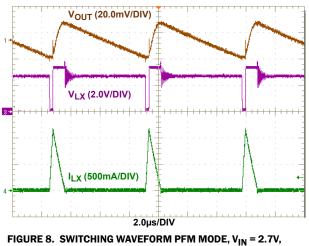

#### **PFM Operation**

The boost converter is capable of operating in two different modes. When the inductor current is sensed to cross zero for eight consecutive times, the converter enters PFM mode. In PFM mode, each pulse cycle is still synchronized by the PWM clock. The N-channel MOSFET is turned on at the rising edge of the clock and turned off when the inductor valley current reaches typically 20% of the current limit. Then the P-channel MOSFET is turned on, and it stays on until its current goes to zero. Subsequently, both N-channel and P-channel MOSFETs are turned off until the next clock cycle starts, at which time the N-channel MOSFET is turned on again. When  $V_{OUT}$  is 1.5% higher than the nominal output voltage, the N-channel MOSFET is immediately turned off and the P-channel MOSFET is turned on until the inductor current goes to zero. The N-channel MOSFET resumes operation when VOUT falls back to its nominal value, repeating the previous operation. The converter returns to 2.5MHz PWM mode operation when V<sub>OUT</sub> drops to 1.5% below its nominal voltage.

Based on this PFM mode algorithm, the average value of the output voltage is approximately 0.75% higher than the nominal output voltage under PWM operation. This positive offset improves the load transient response when switching from Skip mode to PWM mode operation. The ripple on the output voltage is typically 1.5%\*V<sub>OUT</sub> (nominal) when input voltage is sufficiently lower than output voltage, and it increases as input voltage approaches output voltage.

#### **Bypass Operation**

The ISL91132 is designed to allow bypass operation when the input voltage is within a close proximity of the output voltage. The bypass operation is provided by a  $38m\Omega$  P-channel MOSFET  $Q_3$  connecting between VIN and VOUT. In the Bypass mode, Q1 in the boost circuit is turned off and  $Q_2$  is turned on so that the effective bypass resistance is the parallel combination of the  $r_{ON}$  of  $Q_3$  with the series of the inductor DCR and  $r_{ON}$  of  $Q_2$ .

There are two ways to enter Bypass mode: Auto Bypass and Forced Bypass.

#### **AUTO BYPASS**

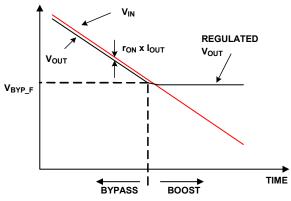

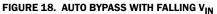

Auto bypass is enabled by pulling the BYPS pin HIGH. When  $V_{IN}$  is 1.5% higher than the target  $V_{OUT}$  regulation and no switching has occurred for 5µs, the device automatically enters the Bypass mode. Figures 18 and 19 illustrate the time sequence of the Auto Bypass mode entry.

#### FORCED BYPASS

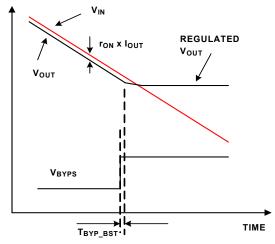

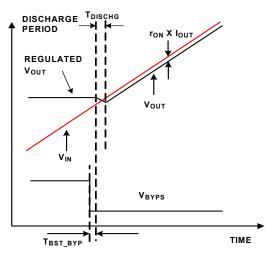

Forced Bypass mode can be activated by pulling the BYPS pin LOW. Figures 20 and 21 illustrate the time sequence of the forced bypass entry. If  $V_{OUT}$  is  $< V_{IN}$  when forced bypass is requested (BYPS is LOW), the bypass MOSFET Q<sub>3</sub> is controlled as a current source to regulate the  $V_{OUT}$ . If  $V_{OUT}$  is  $>V_{IN}$  when bypass is requested (BYPS is LOW), to prevent reverse current flowing from the output to the battery, the ISL91132 first stops the boost operation and activates an internal discharge circuit to discharge the output voltage to the  $V_{IN}$  level before bypass can take place.

FIGURE 20. FORCED MODE, BYPASS TO BOOST

#### Fault Mode

The ISL91132 enters a Fault mode if one of the following conditions are encountered:

- During start-up, V<sub>OUT</sub> does not reach the threshold from Linear mode to Boost mode within the preset time interval.

- In Boost mode, peak current limit is reached for longer than 2ms.

#### **PG Flag**

PG is an open-drain output that provides a flag signal (Hi-Z) to the system when power-up is successful. The PG also provides an early warning flag for overcurrent and over-temperature conditions by turning on the open-drain FET. If a fault condition is encountered, the PG is deasserted.

To summarize, PG is deasserted any of the following conditions are met:

- V<sub>OUT</sub> drops below the PG low threshold (96% of V<sub>OUT</sub>)

- Die temperature has reached the thermal warning threshold (+120°C typical)

- · A fault condition is encountered

#### **Thermal Shutdown**

A built-in thermal protection feature protects the ISL91132, if the die temperature reaches +150°C (typical). At this die temperature, the regulator is completely shut down. The die temperature continues to be monitored in this Thermal Shutdown mode. When the die temperature falls to +120°C (typical), the device resumes normal operation.

## **Applications Information**

#### **Component Selection**

See the typical application circuit in Figure 1 on page 1, and the following sections on component selection.

#### **INDUCTOR SELECTION**

Use an inductor with high frequency core material (for example, ferrite core) to minimize core losses and provide good efficiency. The inductor must be able to handle the peak switching currents without saturating.

A 0.47µH inductor with ≥3A saturation current rating is recommended. Select an inductor with low DCR to provide good efficiency. In applications where radiated noise must be minimized, a toroidal or shielded inductor can be used.

| TABLE 1. INDUCTOR VENDOR INFORMATION | TABLE 1. | INDUCTOR | VENDOR | INFORMATION |

|--------------------------------------|----------|----------|--------|-------------|

|--------------------------------------|----------|----------|--------|-------------|

| MANUFACTURER | SERIES     | INDUCTANCE<br>(µH) | DIMENSION<br>(mm) |

|--------------|------------|--------------------|-------------------|

| ток          | TFM201610A | 0.47               | 2.0x1.6x1.0       |

| токо         | DFE201610R | 0.47               | 2.0x1.6x1.0       |

| CYNTEC       | PIFE32251B | 0.47               | 3.2x2.5x1.2       |

#### $\mathbf{V}_{\text{IN}}$ and $\mathbf{V}_{\text{OUT}}$ capacitor selection

The input and output capacitors should be ceramic X5R type with low ESL and ESR. The recommended input capacitor value is  $22\mu$ F. The recommended V<sub>OUT</sub> capacitor value is  $10\mu$ F to  $22\mu$ F.

| TABLE 2. | CAPACITOR | VENDOR | INFORMATION |

|----------|-----------|--------|-------------|

|          |           |        |             |

| MANUFACTURER | SERIES | WEBSITE         |

|--------------|--------|-----------------|

| AVX          | X5R    | www.avx.com     |

| Murata       | X5R    | www.murata.com  |

| Taiyo Yuden  | X5R    | www.t-yuden.com |

| ток          | X5R    | www.tdk.com     |

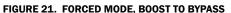

#### **Recommended PCB Layout**

Correct PCB layout is critical for proper operation of the ISL91132. Position the input and output capacitors as close to the IC as possible. Keep the ground connections of the input and output capacitors as short as possible, and on the component layer to avoid problems that are caused by high switching currents flowing through PCB vias.

FIGURE 22. LAYOUT RECOMMENDATION

# **Revision History** The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to web to make sure you have the latest revision.

| DATE         | REVISION | CHANGE                                                                                                                                                              |

|--------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dec 20, 2018 | FN8637.2 | Updated Related Literature<br>Updated Ordering Information table by removing evaluation boards that are not active.<br>Removed About Intersil<br>Updated disclaimer |

| Dec 8, 2016  | FN8637.1 | Updated "Boost Conversion Topology" on page 9.                                                                                                                      |

| Sep 4, 2014  | FN8637.0 | Initial Release                                                                                                                                                     |

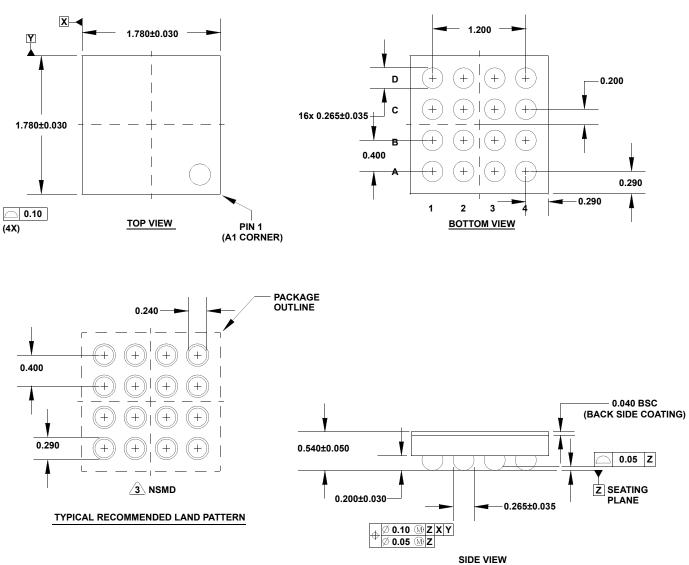

# **Package Outline Drawing**

For the most recent package outline drawing, see W4x4.16E.

W4x4.16E

4X4 ARRAY 16 BALLS WITH 0.40 PITCH WAFER LEVEL CHIP SCALE PACKAGE Rev 0, 2/13

SIDE

#### NOTES:

- 1. All dimensions are in millimeters.

- 2. Dimension and tolerance conform to ASMEY14.5-1994, and JESD 95-1 SPP-010.

- 3. NSMD refers to non-solder mask defined pad design per TB451.