# RENESAS

# DATASHEET

# ISL91302B

Dual/Single Output Power Management IC

The <u>ISL91302B</u> is a highly efficient, dual or single output, synchronous multiphase buck switching regulator that can deliver up to 5A per phase continuous output current. The ISL91302B features four integrated power stages and two controllers. The ISL91302B can assign its power stages and controllers to two dual-phase outputs (2+2) or one three-phase and one-phase output (3+1) or one four-phase output (4+0). This flexibility allows seamless design-in for a wide range of applications in which dual, triple, or quad phase outputs are needed, such as CPU and GPU core power mobile applications.

The ISL91302B integrated low ON-resistance MOSFETs, programmable PWM frequency, and automatic diode emulation, which maximizes efficiency while minimizing the external component count and solution size.

The ISL91302B uses the proprietary Renesas R5 modulator technology to deliver a highly robust power solution capable of ultra-fast transient response, excellent loop stability, and seamless DCM/CCM transitions without requiring external compensation.

The ISL91302B is widely configurable through the factory OTP settings. Available features include:

- SPI and I<sup>2</sup>C interface

- External signal telemetry with an internal ADC

- Dynamic Voltage Scaling (DVS) with selectable slew rate

Contact Renesas support for additional configurations.

### Features

- Dual output 3+1 or 2+2, or single output 4-phase

- 2.5V to 5.5V supply voltage

- 5A per phase output current capability

- Small solution size

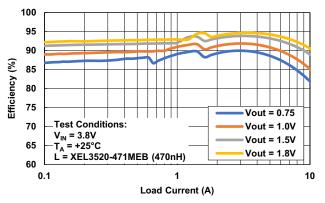

- High efficiency (94.7% peak for 3.8V  $V_{IN}$ , 1.8V  $V_{OUT}$ , L = 470nH)

- Low I<sub>O</sub> in low power mode

- Proprietary control scheme reduces the output capacitor and supports fast load transients (such as 50A/µs per phase)

- Voltage, current, and temperature telemetry through integrated ADC plus auxiliary inputs

- $\pm 0.7\%$  system accuracy with remote voltage sensing

- OTP programmable PWM frequency from 2MHz to 6MHz

- I<sup>2</sup>C and SPI programmable output from 0.3V to 2.0V

- Independent Dynamic Voltage Scaling (DVS) for each output

- Soft-start and fault detection (UV, OV, OC, OT), short-circuit protection

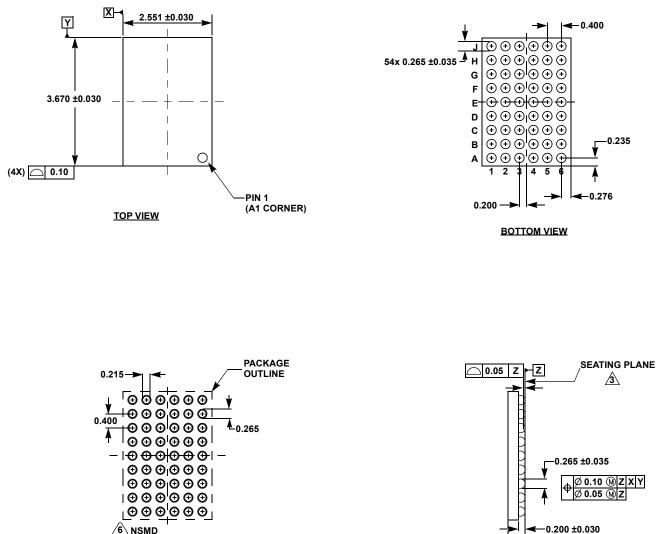

- 2.551mmx 3.670mm 54 ball WLCSP with 0.4mm pin pitch

### Applications

- Smart phones and tablets

- FPGA and ASIC power

- Industrial MPU power

- Human machine interface

FN8828 Rev.3.01 Feb 2, 2022

# Contents

| 1.   | Overview                                      | . 4 |

|------|-----------------------------------------------|-----|

| 1.1  | Typical Application Circuits                  | . 4 |

| 1.2  | Block Diagram                                 | . 6 |

| 1.3  | Ordering Information                          | . 7 |

| 1.4  | Pin Configuration                             | . 8 |

| 1.5  | Pin Descriptions                              | . 9 |

| 2.   | Specifications.                               | 11  |

| 2.1  | Absolute Maximum Ratings                      | 11  |

| 2.2  | Thermal Information                           | 11  |

| 2.3  | Recommended Operation Conditions              | 11  |

| 2.4  | Analog Specifications                         | 12  |

| 3.   | Output Configurations                         | 15  |

| 4.   | Typical Operating Performance                 | 18  |

| 5.   | Applications Information                      | 21  |

| 5.1  | Inductor Selection                            | 21  |

| 5.2  | Output Capacitor Selection                    |     |

| 5.3  | Input Capacitor Selection.                    | 22  |

| 5.4  | ADC Telemetry                                 | 22  |

| 5.5  | Dynamic Voltage Scaling (DVS)                 | 23  |

| 5.6  | Configuring DVS Speed                         | 26  |

| 5.7  | Output Voltage Setting                        | 26  |

| 5.8  | Power Sequencing                              | 26  |

| 5.9  | Watchdog Time (WDOG_RST Pin)                  | 28  |

| 5.10 | ) Interrupt Pin                               | 28  |

| 5.11 | Decay Mode                                    | 29  |

| 6.   | Protection Features (Faults)                  | 30  |

| 6.1  | Over-Temperature Protection                   | 30  |

| 6.2  | Overcurrent Protection Mode                   | 30  |

| 6.3  | Overvoltage (OV)/Undervoltage (UV) Protection | 30  |

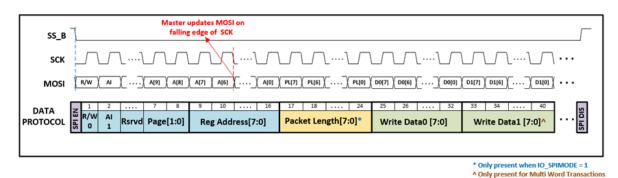

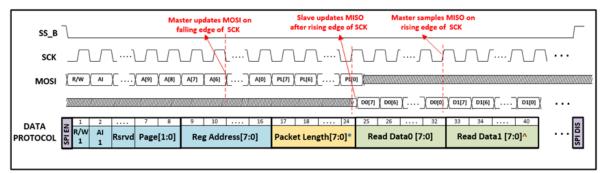

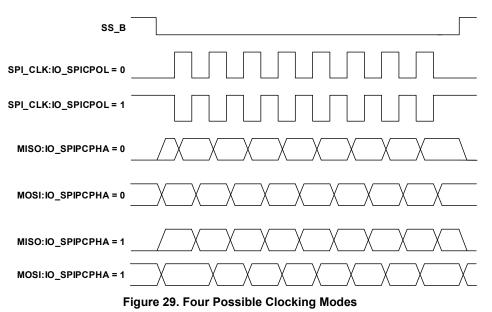

| 7.   | Serial Communication Interface                | 31  |

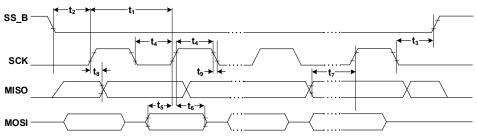

| 7.1  | SPI Serial Interface                          | 31  |

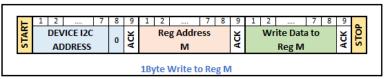

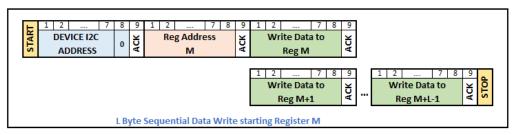

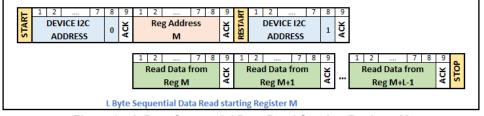

| 7.2  | I <sup>2</sup> C Interface                    | 34  |

| 8.   | Board Layout Recommendations                  | 38  |

| 8.1  | PCB Layout Summary                            | 40  |

| 8.2  | PCB Design for WLCSP Recommendations          |     |

#### ISL91302B

| 9.  | Register Address Map            | 41 |

|-----|---------------------------------|----|

| 10. | Register Description by Address | 42 |

| 11. | Revision History                | 78 |

| 12. | Package Outline Drawing         | 79 |

# 1. Overview

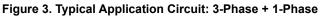

# 1.1 Typical Application Circuits

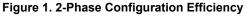

Figure 2. Typical Application 4-Phase Single Output

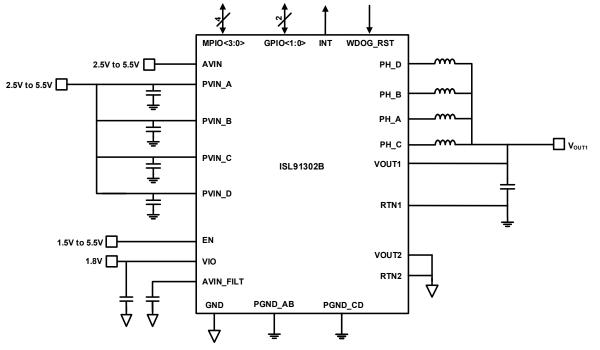

Figure 4. Typical Application Circuit: 2-Phase + 2-Phase

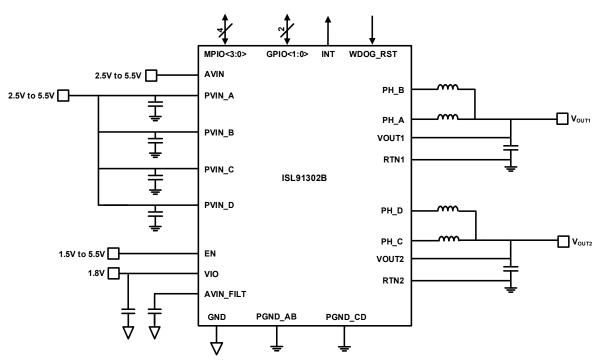

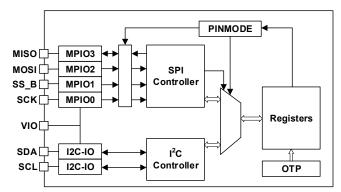

# 1.2 Block Diagram

Figure 5. Block Diagram

# 1.3 Ordering Information

| Part Number<br>( <u>Notes 1</u> , <u>3, 4</u> ) | Part<br>Marking                           | Package Description<br>(RoHS Compliant)                        | Pkg.<br>Dwg. # | Carrier Type<br>( <u>Note 2</u> ) | Temp Range   |  |  |

|-------------------------------------------------|-------------------------------------------|----------------------------------------------------------------|----------------|-----------------------------------|--------------|--|--|

| ISL91302BIIZ-T                                  | 91302B 2.551mmx3.670mm, 54 Ball 6x9 WLCSF |                                                                | W6x9.54        | Reel, 3k                          | -40 to +85°C |  |  |

| ISL91302B22-EVZ                                 | ISL91302B - E                             | ISL91302B - Evaluation board 1, 2+2 PMIC, WLCSP RoHS compliant |                |                                   |              |  |  |

| ISL91302B31-EVZ                                 | ISL91302B - E                             | ISL91302B - Evaluation board 1, 3+1 PMIC, WLCSP RoHS compliant |                |                                   |              |  |  |

| ISL91302B40-EVZ                                 | ISL91302B - E                             | SL91302B - Evaluation board 1, 4+0 PMIC, WLCSP RoHS compliant  |                |                                   |              |  |  |

Notes:

1. For additional part options contact your local sales office.

2. See <u>TB347</u> for details about reel specifications.

3. These Pb-free WLCSP packaged products employ special Pb-free material sets; molding compounds/die attach materials and SnAgCu - e6 solder ball terminals, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Pb-free WLCSP packaged products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J-STD-020.

4. For Moisture Sensitivity Level (MSL), see the ISL91302B device page. For more information about MSL, see TB363.

| Part Number | Pin Configuration | Pitch | Output Configuration        | Maximum Load |

|-------------|-------------------|-------|-----------------------------|--------------|

| ISL91302B   | 54 Ball 6x9 WLCSP | 0.4mm | Single Output (4 + 0 Phase) | 5A           |

|             | 54 Ball 6x9 WLCSP | 0.4mm | Dual Output (3 + 1 Phase)   | 5A           |

|             | 54 Ball 6x9 WLCSP | 0.4mm | Dual Output (2 + 2 Phase)   | 5A           |

| ISL91301A   | 42 Ball 6x7 WLCSP | 0.4mm | Triple Output (2+1+1 Phase) | 4A           |

| ISL91301B   | 42 Ball 6x7 WLCSP | 0.4mm | Quad Output (1+1+1+1 Phase) | 4A           |

| ISL91211A   | 54 Ball 6x9 WLCSP | 0.4mm | Triple Output (2+1+1 Phase) | 5A           |

| ISL91211B   | 54 Ball 6x9 WLCSP | 0.4mm | Quad Output (1+1+1+1 Phase) | 5A           |

Table 1. Key Differences Between Family of Parts

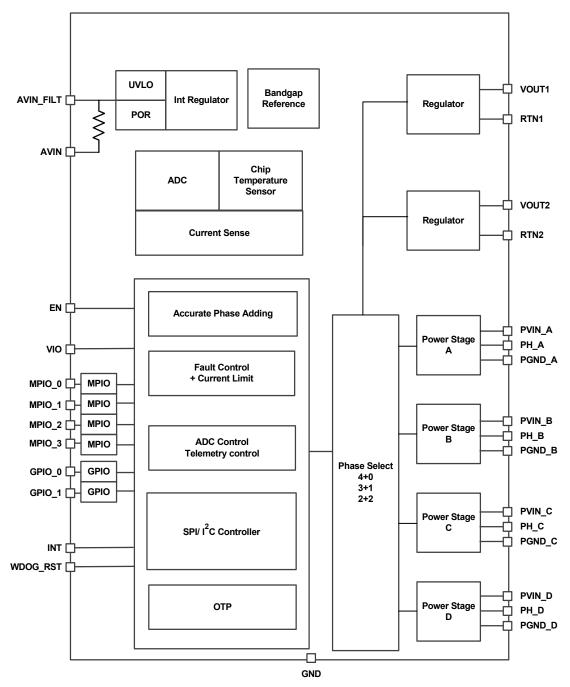

# 1.4 Pin Configuration

54 Bump 6x9 WLCSP

# 1.5 Pin Descriptions

| Pin Number                   | Pin Name  | Туре         | Description                                                                                |

|------------------------------|-----------|--------------|--------------------------------------------------------------------------------------------|

| A1, B1                       | PVIN_A    | Input        | Power supply for Power Stage A.                                                            |

| A2, B2, C2                   | PH_A      | Output       | Switching node for Power Stage A.                                                          |

| A3, B3, C3                   | PGND_A    | Input        | Ground connection for Power Stage A.                                                       |

| A4, B4, C4                   | PGND_B    | Input        | Ground connection for Power Stage B.                                                       |

| A5, B5, C5                   | PH_B      | Input        | Switching node for Power Stage B.                                                          |

| A6, B6                       | PVIN_B    | Input        | Power supply for Power Stage B.                                                            |

| C1                           | GPIO0     | Input/Output | General purpose I/O pin, see <u>Table 2</u> .                                              |

| C6                           | WDOG_RST  | Input        | Digital input, resets the bucks to default output voltage.                                 |

| D1                           | EN        | Input        | Master chip enable input, NMOS logic threshold.                                            |

| D2                           | GPIO1     | Input/Output | General purpose I/O pin, see <u>Table 2</u> .                                              |

| D3                           | INT       | Output       | Interrupt line.                                                                            |

| D4, D5,<br>E2, E3,<br>E4, E5 | GND       | Input        | Analog chip ground. Ensure a low impedance connection to the internal ground layer.        |

| D6                           | RTN1      | Input        | Remote ground voltage sense for Buck #1.                                                   |

| E1                           | VOUT2     | Input        | Remote output voltage sense for Buck #2.                                                   |

| E6                           | VOUT1     | Input        | Remote output voltage sense for Buck #1.                                                   |

| F1                           | RTN2      | Input        | Remote ground voltage sense for Buck #2.                                                   |

| F2                           | AVIN_FILT | Output       | Filtered analog supply voltage, 2.5 to 5.5V. Place a decoupling capacitor close to the IC. |

| F3                           | VIO       | Input        | I/O supply voltage for digital communications. Normally connected to 1.8V supply.          |

| F4                           | MPIO0     | Input/Output | Multipurpose I/O, see <u>Table 2</u> .                                                     |

| F5                           | MPIO1     |              |                                                                                            |

| F6                           | MPIO2     |              |                                                                                            |

| G1                           | AVIN      | Input        | Analog supply voltage, 2.5V to 5.5V.                                                       |

| G2, H2, J2                   | PH_C      | Output       | Switching node for Power Stage C.                                                          |

| G3, H3, J3                   | PGND_C    | Input        | Ground connection for Power Stage C.                                                       |

| G4, H4, J4                   | PGND_D    | Input        | Ground connection for Power Stage D.                                                       |

| G5, H5, J5                   | PH_D      | Output       | Switching node for Power Stage D.                                                          |

| G6                           | MPIO3     | Input/Output | Multipurpose I/O, see <u>Table 2</u> .                                                     |

| H1, J1                       | PVIN_C    | Input        | Power supply connection for Power Stage C.                                                 |

| H6, J6                       | PVIN_D    | Input        | Power supply connection for Power Stage D.                                                 |

#### Table 2. I/O Pin Configuration

| IO_PINMODE | MPIO0    | MPIO1    | MPIO2    | MPIO3    | GPIO0    | GPIO1    | Description                                                  |

|------------|----------|----------|----------|----------|----------|----------|--------------------------------------------------------------|

| 0x0        | SCK      | SS_B     | MOSI     | MISO     | SCL      | SDA      | I <sup>2</sup> C/SPI both available                          |

| 0x1        | SCK      | SS_B     | MOSI     | MISO     | EN_A     | EN_B     | SPI mode with hardware buck enable pins                      |

| 0x2        | Reserved                                                     |

| 0x3        | SCK      | SS_B     | MOSI     | MISO     | DVS1_0   | DVS2_0   | SPI with hardware DVS pins                                   |

| 0x4        | DVS_PIN1 | DVS_PIN0 | PGOOD1   | PGOOD2   | SCL      | SDA      | I <sup>2</sup> C with global DVS mode with PGOOD1 and PGOOD2 |

| IO_PINMODE | MPIO0    | MPIO1    | MPIO2    | MPIO3    | GPIO0    | GPIO1    | Description                                                          |

|------------|----------|----------|----------|----------|----------|----------|----------------------------------------------------------------------|

| 0x5        | DVS1_0   | DVS1_1   | DVS2_0   | DVS2_1   | SCL      | SDA      | I <sup>2</sup> C with full pin controlled DVS for<br>Buck1 and Buck2 |

| 0x6        | DVS1_0   | DVS2_0   | PGOOD1   | PGOOD2   | SCL      | SDA      | I <sup>2</sup> C with DVS and PGOOD for<br>Buck1 and Buck2           |

| 0x7- 0xC   | Reserved                                                             |

| 0xD        | ADC_IN0  | ADC_IN1  | PGOOD1   | PGOOD2   | SCL      | SDA      | I <sup>2</sup> C with ADC input and PGOOD for<br>Buck1 and Buck2     |

| 0xE        | ADC_IN0  | ADC_IN1  | DVS_PIN1 | DVS_PIN0 | SCL      | SDA      | I <sup>2</sup> C with ADC input and global DVS                       |

| 0xF        | Reserved                                                             |

#### Table 2. I/O Pin Configuration (Continued)

#### Table 3. Pin Mode Name Description

| Name               | Definition                                                                            |

|--------------------|---------------------------------------------------------------------------------------|

| SCK                | SPI clock.                                                                            |

| SS_B               | SPI slave select (must be pulled to VIO when using I <sup>2</sup> C in Pin Mode 0x0)  |

| MOSI               | SPI master out slave in.                                                              |

| MISO               | SPI master in slave out.                                                              |

| SCL                | I <sup>2</sup> C clock.                                                               |

| SDA                | I <sup>2</sup> C data.                                                                |

| PGOOD1, PGOOD2     | Power-good output pins.                                                               |

| EN_A, EN_B         | Buck enable input pins.                                                               |

| DVS_PIN1, DVS_PIN0 | Global DVS logic pins which references a look-up table to allow complete DVS control. |

| DVS1_0, DVS1_1     | DVS input logic pins for Buck1.                                                       |

| DVS2_0, DVS2_1     | DVS input logic pins for Buck2.                                                       |

| ADC_IN0, ADC_IN1   | Input pins for auxiliary ADC.                                                         |

# 2. Specifications

# 2.1 Absolute Maximum Ratings

| Parameter                                       | Minimum | Maximum     | Unit |

|-------------------------------------------------|---------|-------------|------|

| PVIN and AVIN Pins to PGND                      | -0.3    | +6          | V    |

| VOUT Pin BUCKx_VOUTFBDIV = 0x0                  | -0.3    | +2.0        | V    |

| VOUT Pin BUCKx_VOUTFBDIV = 0x1                  | -0.3    | +2.4        | V    |

| VOUT Pin BUCKx_VOUTFBDIV = 0x2                  | -0.3    | +3.0        | V    |

| PH to PGND                                      | -0.3    | +0.3 + PVIN | V    |

| VIO, EN Pins to GND                             | -0.3    | +0.3 + AVIN | V    |

| RTN, GND to PGND Pins                           | -0.3    | +0.3        | V    |

| INT, WDOG_RST, MPIO, GPIO pins to GND           | -0.3    | +0.3 + VIO  | V    |

| ESD Ratings ( <u>Note 5</u> )                   | N 1     | /alue       | Unit |

| Human Body Model (Tested per JS-001-2014)       |         | 2           | kV   |

| Charged Device Model (Tested per JS-002-2014)   |         | 750         | V    |

| Latch-Up (Tested per JESD78E; Class 2, Level A) |         | 100         | mA   |

Note:

5. ESD ratings apply to external pins only.

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

# 2.2 Thermal Information

| Thermal Resistance (Typical)                        | θ <sub>JA</sub> (°C/W) | ⊕ <sub>JC</sub> (°C/W) |

|-----------------------------------------------------|------------------------|------------------------|

| 54 Ball WLCSP Package ( <u>Notes 6</u> , <u>7</u> ) | 42                     | 0.5                    |

Notes:

θ<sub>JA</sub> is measured in free air with the component mounted on a high-effective thermal conductivity test board with "direct attach" features. See <u>TB379</u>.

7. For  $\theta_{JC},$  the "case temp" location is taken at the package top center.

| Parameter                                      | Minimum | Maximum          | Unit |

|------------------------------------------------|---------|------------------|------|

| Maximum Junction Temperature (T <sub>J</sub> ) |         | +150             | °C   |

| Storage Temperature Range (T <sub>S</sub> )    | -65     | +150             | °C   |

| Pb-Free Reflow Profile                         |         | see <u>TB493</u> |      |

# 2.3 Recommended Operation Conditions

| Parameter                                             | Minimum | Maximum | Unit |

|-------------------------------------------------------|---------|---------|------|

| Ambient Operating Temperature Range (T <sub>A</sub> ) | -40     | +85     | °C   |

| Operating Junction Temperature (T <sub>J</sub> )      | -40     | +125    | °C   |

| Supply Voltage                                        |         |         |      |

| AVIN to GND                                           | 2.5     | 5.5     | V    |

| PVIN to PGND                                          | 2.5     | 5.5     | V    |

| VIO Voltage (VIO to GND)                              | 1.7     | AVIN    | V    |

| INT, WDOG_RST, MPIO, GPIO Pins to GND                 | 0       | VIO     | V    |

# 2.4 Analog Specifications

$AVIN/PVIN = 3.7V, V_{OUT} = 1V, L = 220nH, Frequency = 4MHz, VIO = 1.8V, T_A = +25^{\circ}C.$  Boldface limits apply across the ambient operating temperature range, -40°C to +85°C unless otherwise noted.

| Parameter                                     | Symbol             | Test Conditions                                                                                  | Min<br>( <u>Note 8</u> ) | Тур      | Max<br>( <u>Note 8</u> ) | Unit |

|-----------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------|--------------------------|----------|--------------------------|------|

| Input Supply                                  |                    |                                                                                                  |                          |          |                          |      |

| Supply Voltage                                | AVIN               |                                                                                                  | 2.5                      |          | 5.5                      | V    |

| Supply Voltage                                | PVIN               |                                                                                                  | 2.5                      |          | 5.5                      | V    |

| AVIN Supply Current                           | ا <sub>م</sub>     | EN = 0V                                                                                          |                          | 0.1      | 1                        | μA   |

| AVIN + PVIN Supply Current                    |                    | EN = 0V                                                                                          |                          | <1       | 6                        | μA   |

| AVIN + PVIN Supply Current                    |                    | BUCK1_EN[0] = 0x0 and BUCK2_EN[0] = 0x0                                                          |                          | 22       |                          | μA   |

| EN = AVIN = PVINx = 3.7V                      |                    | 4+0 OTP configuration, not switching<br>BUCK1_EN[0] = 0x1 DCM operation<br>BUCK2_EN[0] = 0x0     |                          | 75       |                          | μA   |

|                                               |                    | 4+0 OTP configuration, not switching<br>BUCK1_EN[0] = 0x1 1PH CCM operation<br>BUCK2_EN[0] = 0x0 |                          | 635      |                          | μA   |

|                                               |                    | 4+0 OTP configuration, not switching<br>BUCK1_EN[0] = 0x1 4PH CCM operation<br>BUCK2_EN[0] = 0x0 |                          | 765      |                          | μA   |

|                                               |                    | 2+2 OTP configuration, not switching<br>BUCK1_EN[0] = 0x0<br>BUCK2_EN[0] = 0x1 DCM operation     |                          | 85       |                          | μA   |

|                                               |                    | 2+2 OTP configuration, not switching<br>BUCK1_EN[0] = 0x0<br>BUCK2_EN[0] = 0x1 1PH CCM operation |                          | 485      |                          | μA   |

|                                               |                    | 2+2 OTP configuration, not switching<br>BUCK1_EN[0] = 0x0<br>BUCK2_EN[0] = 0x1 2PH CCM operation |                          | 560      |                          | μA   |

| UVLO Rising Threshold                         | V <sub>UVLOR</sub> | Rising                                                                                           | 2.52                     | 2.60     | 2.67                     | V    |

| UVLO Falling Threshold                        | V <sub>UVLOF</sub> | Falling                                                                                          | 2.28                     | 2.34     | 2.40                     | V    |

| Buck Regulation                               | I                  |                                                                                                  |                          |          |                          |      |

| Buck Output Voltage Range                     | V <sub>OUT</sub>   | BUCKx_VOUTFBDIV[1:0] = 0x00                                                                      | 0.300                    |          | 1.2                      | V    |

| (Each Output)                                 |                    | BUCKx_VOUTFBDIV[1:0] = 0x01                                                                      | 0.375                    |          | 1.5                      | V    |

|                                               |                    | BUCKx_VOUTFBDIV[1:0] = 0x02                                                                      | 0.500                    |          | 2.0                      | V    |

| Output Voltage Step Size                      | V <sub>STEP</sub>  | 10-bit control, BUCKx_VOUTFBDIV[1:0] = 0x00                                                      |                          | 1.2      |                          | mV   |

|                                               |                    | 10-bit control, BUCKx_VOUTFBDIV[1:0] = 0x01                                                      |                          | 1.5      |                          | mV   |

|                                               |                    | 10-bit control, BUCKx_VOUTFBDIV[1:0] = 0x02                                                      |                          | 2.0      |                          | mV   |

| Output Voltage Accuracy                       | V <sub>ACC</sub>   | CCM, V <sub>OUT</sub> > 0.6V                                                                     | -0.3                     |          | 0.3                      | %    |

| (Note 9)                                      |                    | CCM, V <sub>OUT</sub> > 0.6V<br>T <sub>A</sub> = -10°C to +85°C                                  | -0.7                     |          | 0.7                      | %    |

|                                               |                    | CCM, V <sub>OUT</sub> < 0.6V                                                                     | -4                       |          | 4                        | mV   |

|                                               |                    | CCM, V <sub>OUT</sub> < 0.6V<br>T <sub>A</sub> = -10°C to +85°C                                  | -5.5                     |          | 5.5                      | mV   |

| Current Matching                              | I <sub>MATCH</sub> | I <sub>OUT</sub> = 5A per phase                                                                  |                          | 10       |                          | %    |

| Dynamic Response                              | •                  | · · · · · · · · · · · · · · · · · · ·                                                            |                          | <u> </u> |                          |      |

| Dynamic Voltage Scaling<br>(Output Slew Rate) | V <sub>DVS</sub>   | 2.5V < V <sub>IN</sub> < 5.5V: 3mV/µs                                                            | -15                      |          | 15                       | %    |

$AVIN/PVIN = 3.7V, V_{OUT} = 1V, L = 220nH, Frequency = 4MHz, VIO = 1.8V, T_A = +25^{\circ}C.$  Boldface limits apply across the ambient operating temperature range, -40°C to +85°C unless otherwise noted. (Continued)

| Parameter                                  | Symbol                    | Test Conditions                                                                                                                                                                                                                        | Min<br>( <u>Note 8</u> ) | Тур  | Max<br>( <u>Note 8</u> ) | Unit |

|--------------------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|--------------------------|------|

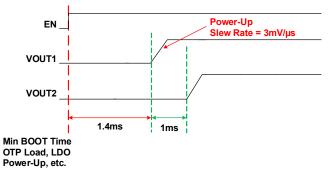

| Boot-Up Time                               | V <sub>BT</sub>           | Delay from when PVIN, AVIN, and EN are<br>asserted to when the first Buck's reference<br>starts ramping. This time includes internal<br>reference startup, OTP load, and buck<br>controller calibration time.<br>BUCKx_EN_DELAY = 0x00 |                          | 1.4  |                          | ms   |

| Frequency                                  |                           |                                                                                                                                                                                                                                        |                          |      |                          |      |

| CCM Frequency Tolerance                    | f <sub>SW_TOL</sub>       | 4MHz                                                                                                                                                                                                                                   | -15                      |      | 15                       | %    |

| Power Stage                                |                           |                                                                                                                                                                                                                                        |                          |      |                          |      |

| Buck Output Current (Each<br>Phase)        |                           | 2.5V < V <sub>IN</sub> < 5.5V                                                                                                                                                                                                          |                          |      | 5                        | A    |

| High-Side Switch<br>ON-Resistance          | HS r <sub>DS(ON)</sub>    | Conditions: PVIN = 3.7V, current = 300mA                                                                                                                                                                                               |                          | 23   |                          | mΩ   |

| Low-Side Switch<br>ON-Resistance           | LS r <sub>DS(ON)</sub>    | Conditions: PVIN = 3.7V, current = 300mA                                                                                                                                                                                               |                          | 9    |                          | mΩ   |

| Protection                                 |                           |                                                                                                                                                                                                                                        |                          |      |                          |      |

| HSD Current Limit (WOC)                    | I <sub>LIMIT</sub>        | 2.5V < V <sub>IN</sub> < 5.5V<br>Phase count = 2 or more; WOC = 11.35A                                                                                                                                                                 | -10                      |      | 10                       | %    |

|                                            |                           | 2.5V < V <sub>IN</sub> < 5.5V<br>Phase count = 1; WOC = 8.38A                                                                                                                                                                          | -10                      |      | 10                       |      |

| Thermal Shutdown Accuracy                  | T <sub>SPS</sub>          | 2.5V < V <sub>IN</sub> < 5.5V, factory default = +140°C                                                                                                                                                                                | -10                      |      | 10                       | %    |

| Thermal Shutdown Hysteresis                | T <sub>SPS_HYS</sub>      | 2.5V < V <sub>IN</sub> < 5.5V, factory default = +60°C                                                                                                                                                                                 | -10                      |      | 10                       | %    |

| Thermal Warning Alert                      | T <sub>ALERT</sub>        | 2.5V < V <sub>IN</sub> < 5.5V, factory default = +85°C                                                                                                                                                                                 | -10                      |      | 10                       | %    |

| Thermal Warning Hysteresis                 | T <sub>ALERT_HYS</sub>    | 2.5V < V <sub>IN</sub> < 5.5V, factory default = +12°C                                                                                                                                                                                 | -10                      |      | 10                       | %    |

| Output OVP Threshold<br>Accuracy           | V <sub>OVP</sub>          | Threshold: +250mV                                                                                                                                                                                                                      | -35                      |      | 35                       | mV   |

| Output UVP Threshold<br>Accuracy           | V <sub>UVP</sub>          | Threshold: -250mV                                                                                                                                                                                                                      | -35                      |      | 35                       | mV   |

| ADC                                        |                           |                                                                                                                                                                                                                                        |                          |      |                          |      |

| Output Current Sense Offset                | I <sub>SENSE_OFFSET</sub> |                                                                                                                                                                                                                                        | -75                      |      | 75                       | mA   |

| Output Current Sense                       | I <sub>SENSE_ADC</sub>    | I <sub>LOAD</sub> = 500mA (minus offset)                                                                                                                                                                                               | -10                      |      | 10                       | %    |

| Accuracy                                   |                           | $3.0V < V_{IN} < 5.0V I_{LOAD} = 500mA (minus offset)$                                                                                                                                                                                 | -15                      |      | 15                       | %    |

| MPIO/GPIO Operating Condition              | ions                      |                                                                                                                                                                                                                                        |                          |      |                          |      |

| Allowable Range of Supply for<br>Operation | VIO                       |                                                                                                                                                                                                                                        | 1.70                     | 1.80 | AVIN                     | V    |

| Chip Enable Logic Threshold                | Level                     |                                                                                                                                                                                                                                        |                          |      |                          |      |

| Low-Level Input Voltage                    | V <sub>IL</sub>           |                                                                                                                                                                                                                                        |                          |      | 0.5                      | V    |

| High-Level Input Voltage                   | V <sub>IH</sub>           |                                                                                                                                                                                                                                        | 1.35                     |      |                          | V    |

| Serial Interfaces                          | •                         | ·                                                                                                                                                                                                                                      |                          |      | •                        | -    |

| I <sup>2</sup> C Frequency Capability      | f <sub>I2C</sub>          |                                                                                                                                                                                                                                        |                          |      | 3.4                      | MHz  |

| SPI Frequency Capability                   | f <sub>SPI</sub>          |                                                                                                                                                                                                                                        |                          | 26   |                          | MHz  |

| MPIO/GPIO Logic Threshold I                | _evels                    |                                                                                                                                                                                                                                        |                          |      |                          | •    |

| Low Level Input Voltage                    | V <sub>IL</sub>           |                                                                                                                                                                                                                                        |                          |      | 0.25 x VIO               | V    |

| High Level Input Voltage                   | V <sub>IH</sub>           |                                                                                                                                                                                                                                        | 0.75 x VIO               |      |                          | V    |

$AVIN/PVIN = 3.7V, V_{OUT} = 1V, L = 220nH, Frequency = 4MHz, VIO = 1.8V, T_A = +25^{\circ}C.$  Boldface limits apply across the ambient operating temperature range, -40°C to +85°C unless otherwise noted. (Continued)

| Parameter           | Symbol           | Test Conditions                         | Min<br>( <u>Note 8</u> ) | Тур | Max<br>( <u>Note 8</u> ) | Unit |

|---------------------|------------------|-----------------------------------------|--------------------------|-----|--------------------------|------|

| Hysteresis on Input | V <sub>HYS</sub> |                                         | 0.1 x VIO                |     |                          | V    |

| Low Level Output    | V <sub>OL</sub>  | 1mA                                     |                          |     | 0.4                      | V    |

| High Level Output   | V <sub>OH</sub>  | 1mA (250µA for 20% drive configuration) | VIO - 0.4                |     |                          | V    |

Notes:

8. Compliance to datasheet limits is assured by one or more methods: production test, characterization, and/or design.

V<sub>OUT</sub> feedback divider ratio equals 1 (BUCKx\_VOUTFBDIV[1:0] = 0x00).

As per <u>"Thermal Information" on page 11</u>, operating beyond thermal limits can cause permanent damage.

# 3. Output Configurations

| Output<br>Configuration                                  | Power Stage<br>Assignment   | Diagram           |

|----------------------------------------------------------|-----------------------------|-------------------|

| 4-Phase                                                  | 4-Phase: Buck #1<br>(VOUT1) | 4+0 Configuration |

| 4-Phase<br>Connect<br>VOUT2 and<br>RTN2 to<br>PGND Plane |                             | 4+0 Configuration |

|                                                          |                             |                   |

### Table 4. Output Configurations

| Output<br>Configuration | Power Stage<br>Assignment                                        |            | Diagran                                                                                                                                                                                                                                                                                                                  | n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|-------------------------|------------------------------------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 3-Phase +<br>1-Phase    | 3+1 Configuration:<br>• 3-phase: Buck #1<br>(VOUT1)<br>Ph1: PH_A |            | 3+1 Configuration                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                         | <ul> <li>3-phase: Buck #1</li> </ul>                             |            | $(PVIN_A) (PH_A) (PGND_A)$ $(PVIN_A) (PH_A) (PGND_A)$ $(GPIOD) (PH_A) (PGND_A)$ $(GPIOD) (PH_A) (PGND_A)$ $(EN) (GPIOI) (INT)$ $(VOUT2) (GND) (GND)$ $(VOUT2) (GND) (GND)$ $(RTN2) (AVIN_A) (PH_C) (PGND_A)$ $(AVIN_A) (PH_C) (PGND_A)$ $(AVIN_A) (PH_C) (PGND_A)$ $(PVIN_C) (PH_C) (PGND_A)$ $(PVIN_C) (PH_C) (PGND_A)$ | $\begin{pmatrix} PGND_{-} \\ B \end{pmatrix} \begin{pmatrix} PH \\ B \end{pmatrix} \begin{pmatrix} PH \\ B \end{pmatrix} \begin{pmatrix} PVIN \\ B \end{pmatrix} \begin{pmatrix} PH \\ B \end{pmatrix} \begin{pmatrix} PVIN \\ B \end{pmatrix} \begin{pmatrix} PH \\ B \end{pmatrix} \begin{pmatrix} PH \\ B \end{pmatrix} \begin{pmatrix} PVIN \\ B \end{pmatrix} \begin{pmatrix} PH \\ PH \end{pmatrix} \begin{pmatrix} PH \\ PH$ |  |  |  |

|                         |                                                                  | 8 PH2 8 PH |                                                                                                                                                                                                                                                                                                                          | В РНЗ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

#### Table 4. Output Configurations (Continued)

| Output<br>Configuration | Power Stage<br>Assignment               | Diagram           |  |  |  |  |  |

|-------------------------|-----------------------------------------|-------------------|--|--|--|--|--|

| 2-Phase +<br>2-Phase    | 2+2 Configuration<br>• 2-phase: Buck #1 | 2+2 Configuration |  |  |  |  |  |

|                         |                                         | 2+2 Configuration |  |  |  |  |  |

#### Table 4. Output Configurations (Continued)

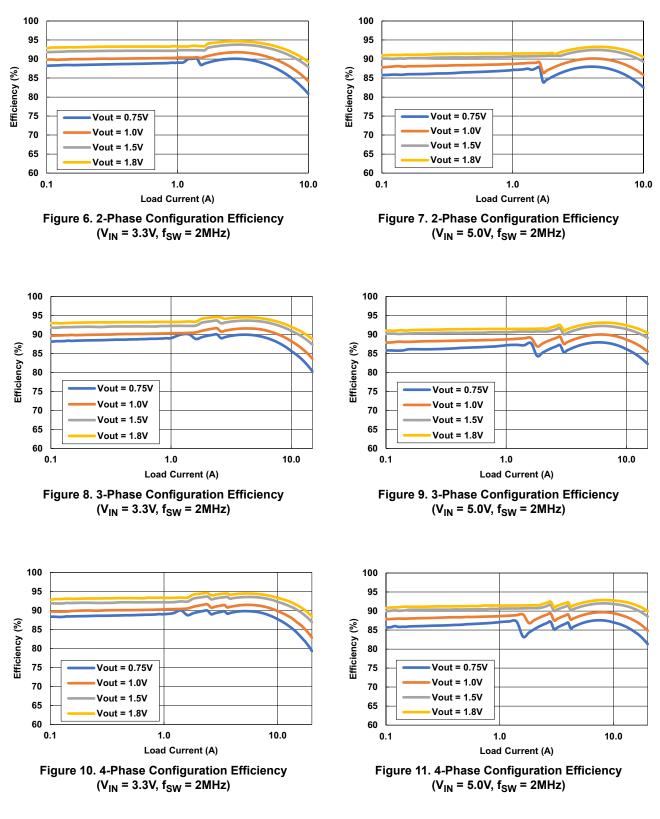

# 4. Typical Operating Performance

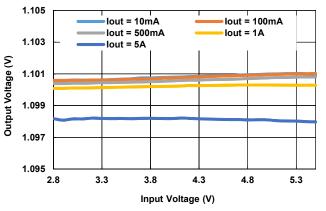

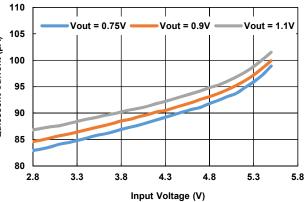

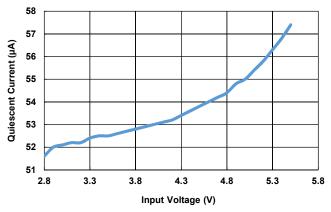

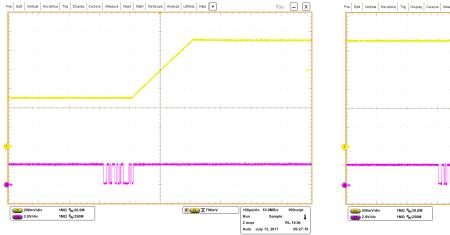

Unless otherwise noted, operating conditions are:  $V_{IN}$  = 3.8V,  $V_{OUT}$  = 1.1V, VIO and Enable = 1.8V,  $T_A$  = +25°C,  $f_{SW}$  = 4MHz, 2-phase operation, L = 220nH,  $C_{OUT}$  = 5x22µF + 8x4.3µF.

FN8828 Rev.3.01 Feb 2, 2022

#### ISL91302B

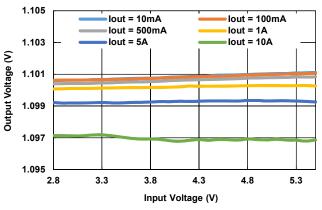

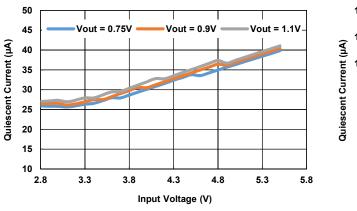

Unless otherwise noted, operating conditions are:  $V_{IN} = 3.8V$ ,  $V_{OUT} = 1.1V$ , VIO and Enable = 1.8V,  $T_A = +25^{\circ}C$ ,  $f_{SW} = 4MHz$ , 2-phase operation, L = 220nH,  $C_{OUT} = 5x22\mu$ F + 8x4.3 $\mu$ F. (Continued)

Figure 12. 2-Phase  $V_{OUT}$  vs  $V_{IN}$  (10mA to 10A)

Figure 13. Single-Phase  $V_{OUT}$  vs  $V_{IN}$  (10mA to 5A)

Figure 15. PVIN Quiescent Current (PWM Mode)

Figure 16. PVIN Quiescent Current (No Switching)

#### ISL91302B

Unless otherwise noted, operating conditions are:  $V_{IN}$  = 3.8V,  $V_{OUT}$  = 1.1V, VIO and Enable = 1.8V,  $T_A$  = +25°C,  $f_{SW}$  = 4MHz, 2-phase operation, L = 220nH,  $C_{OUT}$  = 5x22µF + 8x4.3µF. (Continued)

Figure 17. 0.5V to 1.1V DVS; Load = 5A, Slew Rate = 3mV/µs

Figure 18. 1.1V to 0.5V DVS; Load = 5A, Slew Rate = 3mV/µs

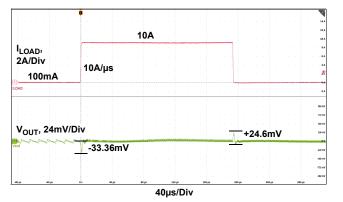

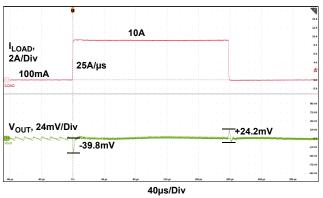

Figure 20. Dual-Phase Transient, C<sub>OUT</sub> =  $9x22\mu$ F and L = 220nH/Phase

# 5. Applications Information

# 5.1 Inductor Selection

The ISL91302B is a high efficiency, high performance, dual output multiphase/single-phase synchronous buck converter that can deliver up to 5A of continuous current per phase at 0.3V to 2.0V regulated voltage from a single Li-Ion battery to power portable and handheld devices. The ISL91302B is designed to provide one or two output voltage rails with operational modes setup to 4+0, 3+1, and 2+2 at a nominal switching frequency of 2MHz~4MHz. Contact <u>support</u> for questions relating to switching frequency of 6MHz. Switching MOSFETs are fully integrated and no additional external MOSFETs or diodes are needed. Each phase requires an equal external inductor that can deliver the maximum load current divided by the number of phases used.

| Manufacturer | Part Number   | L x W x H (mm) | Value (nH) | DCR mΩ (Typ) | I <sub>SAT</sub> (Тур) |

|--------------|---------------|----------------|------------|--------------|------------------------|

| Cyntec       | HMLB25201T    | 2.5x2.0x1.0    | 220        | 9.4          | 7.0                    |

| Taiyo Yuden  | MAKK2520HR22M | 2.5x2.0x1.0    | 220        | 16           | 8.5                    |

| Cyntec       | HTTN2016T     | 2.0x1.6x1.0    | 220        | 13           | 7.2                    |

| Murata       | DFE2016E      | 2.0x1.6x1.0    | 240        | 16           | 7.0                    |

| Murata       | DFE252012F    | 2.5x2.0x1.2    | 470        | 23           | 6.7                    |

Table 5. Recommended Output Inductors

# 5.2 Output Capacitor Selection

Output capacitors are needed to provide filtering of square voltage at the phase node into a regulated output voltage. The amount of output capacitance required is based on the parameters of the maximum load step, the slew rate of the load step, and the maximum allowable voltage regulation tolerance during the transient. The amount of ripple voltage at the output capacitor is also a design constraint; the total peak-to-peak ripple voltages produced from the output capacitor is equal to its ESR multiplied by the worst case inductor ripple current.

Make sure to select X7R or X5R type capacitors and consider for DC bias effects. A wide range of output capacitor values can be used.

| Manufacturer | Part Number         | Case Size | Value (µF) | Voltage Rating (V) |

|--------------|---------------------|-----------|------------|--------------------|

| TDK          | C1608X5R1A226M080AC | 0603      | 22         | 10                 |

| TDK          | C0510X6S0G105M030AC | 0204      | 1          | 4                  |

| Murata       | LLD154R60G435ME01   | 0402      | 4.3        | 4                  |

| Murata       | LLL1U4R60G435ME22   | 0204      | 4.3        | 4                  |

Table 6. Recommended Output Capacitors

# 5.3 Input Capacitor Selection

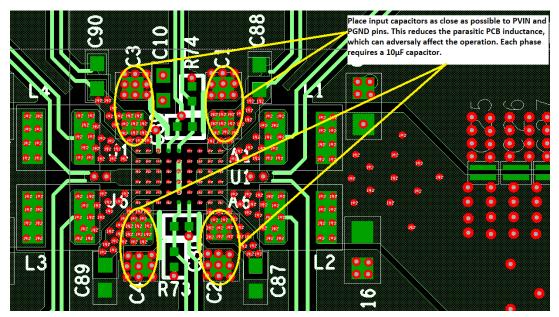

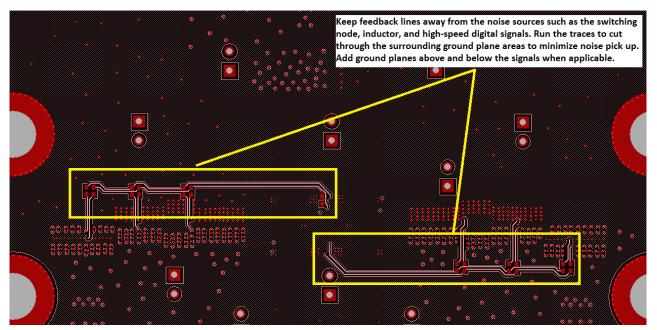

Ceramic input capacitors source the AC component of the input current flowing into the high-side MOSFETs. Place them as close to the IC as possible. If long wires are used to bring power to the IC, use additional bulk capacitors between  $C_{IN}$  and the battery/power supply to dampen ringing and overshoot at startup.

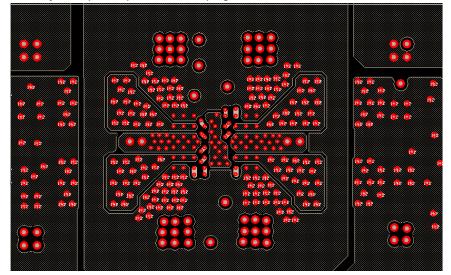

Internal analog reference circuits also require additional filtering at the AVIN\_FLTR pin. A 10 $\mu$ F local decoupling capacitor is recommended for each phase on PVIN.

| Manufacturer | Part Number          | Case Size | Value (µF) | Volt (V) | Input |

|--------------|----------------------|-----------|------------|----------|-------|

| TDK Corp     | CGB2A1X5R1A105M033BC | 0402      | 1          | 10       | AVIN  |

| Kemet        | C0402C104K8RACTU     | 0402      | 0.1        | 10       | AVIN  |

| Samsung      | CL05A10MP5NUNC       | 0402      | 10         | 10       | PVIN  |

| Murata       | GRM188R61A106MAAL    | 0603      | 10         | 10       | PVIN  |

| Table 7. Recommended | Input | Capacitors |

|----------------------|-------|------------|

|----------------------|-------|------------|

### 5.4 ADC Telemetry

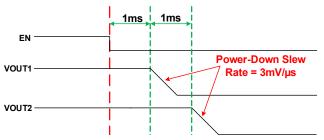

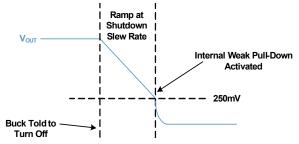

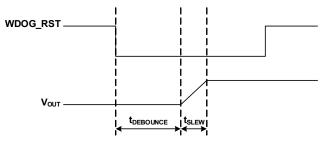

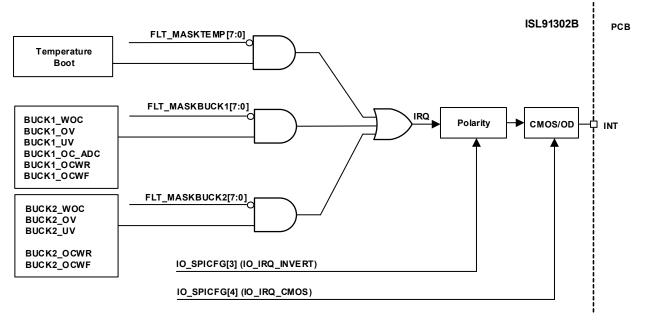

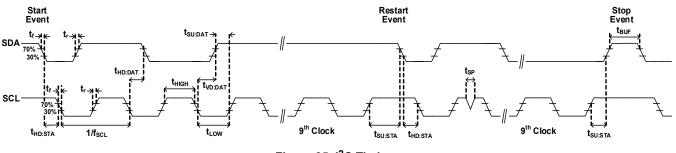

The device features a 12-bit (effective) SAR ADC telemetry function that supports internal silicon temperature, individual phase current, total buck output current, output voltage, and input voltage measurements. Two additional channels provide additional internal or external monitoring. Using these channels requires OTP programming from the factory. The ADC is OTP programmed to be turned off during Discontinuous Conduction mode to save current and improve light-load efficiency. The ADC supports two operating modes: Continuous Mode, and Non-continuous (or Single-shot or One-shot) Mode.