# KIT33907LAEEVB and KIT33908LAEEVB Evaluation Board

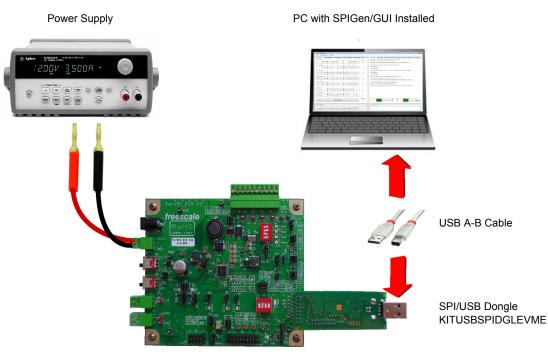

Figure 1. KIT33907LAEEVB and KIT33908LAEEVB Board

## Contents

| 1 Important Notice                |                       | 3  |

|-----------------------------------|-----------------------|----|

| 2 Getting Started                 |                       | 4  |

| 3 Terms                           |                       | 5  |

| 4 Getting to Know the Hardware    |                       | 6  |

| 5 Accessory Interface Board       |                       | 20 |

| 6 Installing the Software and Set | tting up the Hardware | 22 |

| 8 Graphical User Interface        |                       | 24 |

| 9 Schematic                       |                       | 29 |

| 10 Board Layout                   |                       | 30 |

| 11 References                     |                       | 35 |

| 12 Revision History               |                       | 36 |

### 1

## **Important Notice**

Freescale provides the enclosed product(s) under the following conditions:

This evaluation kit is intended for use of ENGINEERING DEVELOPMENT OR EVALUATION PURPOSES ONLY. It is provided as a sample IC pre-soldered to a printed circuit board to make it easier to access inputs, outputs, and supply terminals. This evaluation kit may be used with any development system or other source of I/O signals by simply connecting it to the host MCU or computer board via off-the-shelf cables. Final device in an application will be heavily dependent on proper printed circuit board layout and heat sinking design as well as attention to supply filtering, transient suppression, and I/O signal quality.

The goods provided may not be complete in terms of required design, marketing, and or manufacturing related protective considerations, including product safety measures typically found in the end product incorporating the goods. Due to the open construction of the product, it is the user's responsibility to take any and all appropriate precautions with regard to electrostatic discharge. In order to minimize risks associated with the customers applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards. For any safety concerns, contact Freescale sales and technical support services.

Should this evaluation kit not meet the specifications indicated in the kit, it may be returned within 30 days from the date of delivery and will be replaced by a new kit.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typical", must be validated for each customer application by customer's technical experts.

Freescale does not convey any license under its patent rights nor the rights of others. Freescale products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale product could create a situation where personal injury or death may occur.

Should the Buyer purchase or use Freescale products for any such unintended or unauthorized application, the Buyer shall indemnify and hold Freescale and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale was negligent regarding the design or manufacture of the part. Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2015

## 2 Getting Started

## 2.1 Kit Contents/Packing List

The KIT33907LAEEVB and KIT33908LAEEVB contents include:

- Assembled and tested evaluation board/module in anti-static bag

- Warranty card

## 2.2 Jump Start

Freescale's analog product development boards help to easily evaluate Freescale products. These tools support analog mixed signal and power solutions including monolithic ICs using proven high-volume SMARTMOS mixed signal technology, and system-in-package devices utilizing power, SMARTMOS and MCU dies. Freescale products enable longer battery life, smaller form factor, component count reduction, ease of design, lower system cost and improved performance in powering state of the art systems.

- Go to www.freescale.com/analogtools

- Locate your kit

- Review your Tool Summary Page

- Look for

• Download documents, software, and other information

Once the files are downloaded, review the user guide in the bundle. The user guide includes setup instructions, BOM and schematics. Jump start bundles are available on each tool summary page with the most relevant and current information. The information includes everything needed for design.

## 2.3 Required Equipment and Software

To use this kit, you need

• 2.7 V to 40 V power supply, 3.0 A capability

Notes: When not connected to an MCU, the KITUSBSPIDGLVME can be used for register setting. In this case, the SPIGen dongle and USB cable are required. For more information, see the "SPIGen 7 User Guide".

## 2.4 System Requirements

The kit requires the following:

USB-enabled PC with Windows<sup>®</sup> XP or higher

## 3 Terms

| Part Number or<br>Parameter | Definition                                                                                                            |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------|

| CAN_5V                      | 5.0 V CAN voltage                                                                                                     |

| EVB                         | Evaluation Board                                                                                                      |

| FCCU                        | Fault Collection and Control Unit                                                                                     |

| FS0B                        | Fail-safe Output Number 0                                                                                             |

| INTB                        | Interrupt                                                                                                             |

| Ю                           | Input/Output                                                                                                          |

| LDO                         | Low-dropout Regulator                                                                                                 |

| RSTB                        | Reset                                                                                                                 |

| SMPS                        | Switching Mode Power Supply                                                                                           |

| SPIGen                      | Software utility (installed on a PC) provides communication functions between the PC and a Freescale evaluation board |

| V <sub>AUX</sub>            | Auxiliary power supply                                                                                                |

| V <sub>CCA</sub>            | Power supply for ADC                                                                                                  |

| V <sub>PRE</sub>            | Pre-regulator voltage                                                                                                 |

| WD                          | Watchdog                                                                                                              |

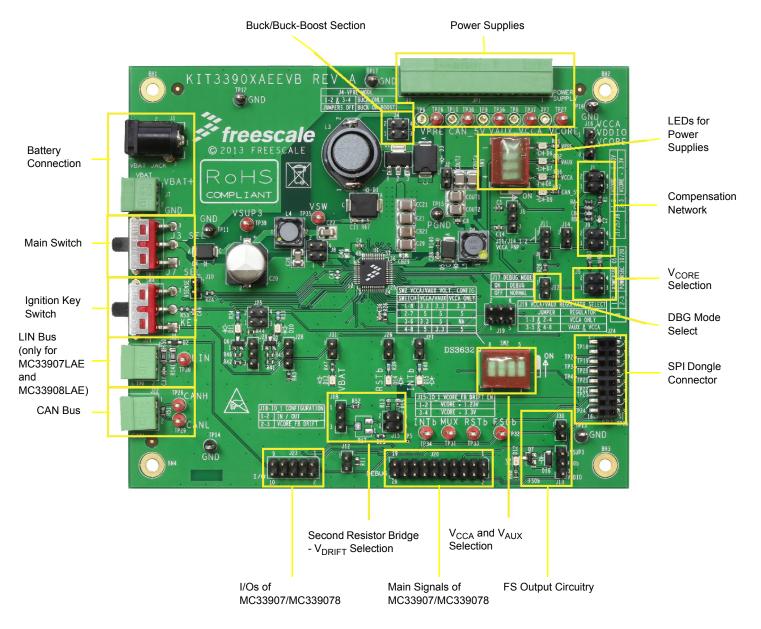

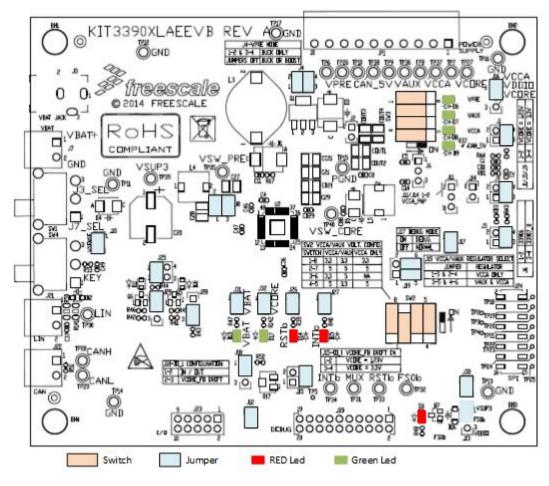

## 4 Getting to Know the Hardware

## 4.1 Board Overview

KIT33907LAEEVB and KIT33908LAEEVB evaluation boards demonstrate the functionality of the SMARTMOS MC33907 and MC33908 power system basis chips, respectively. These ICs are equipped with an intelligent power management system including safety features targeting the latest ISO26262 automotive functional safety standard. The EVB is a standalone board that can be used either with a compatible microcontroller or with a PC. In the latter case, it is necessary to use an KITUSBSPIDGLEVME accessory interface board. See section "Required Equipment and Software".

## 4.2 Board Features

This EVB comes mounted with either an MC33907or an MC33908 IC. The main features of the board are as follows:

- V<sub>BAT</sub> power supply either through power jack (2.0 mm) or phoenix connector

- V<sub>CORE</sub> configuration:1.23 V or 3.3 V

- V<sub>CCA</sub> configuration:

- 5.0 V/3.3 V

- Internal transistor or external PNP

- V<sub>AUX</sub> configuration:

- 3.3 V or 5.0 V

- Enabled or disabled at startup

- Ignition key switch

- LIN bus

- CAN bus

- IO connector (IO\_0 to IO\_5)

- Debug connector (SPI bus, CAN digital, LIN digital, RSTB, FS0B, INTB, Debug, MUX\_OUT)

- Signalling LED to give state of signals or regulators

### 4.3 MC33907 and MC33908 Device Features

The MC33907 and the MC33908 are multi-output ICs, with power supply and HSCAN transceiver. These devices have been designed specifically with the automotive market in mind. The MC33907 is designed to support up 800 mA on  $V_{CORE}$ , while MC33908 supports up to 1.5 A on  $V_{CORE}$ . All other features are the same. Both devices support following functions:

#### Table 1. Device Features

| Device           | Description                                                                  | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MC33907/ MC33908 | Power system<br>basis chip with<br>high-speed CAN<br>and LIN<br>transceivers | <ul> <li>Highly flexible SMPS pre-regulator, allowing two topologies: non-inverting buck-boost or standard buck</li> <li>Switching mode power supply (SMPS) dedicated to MCU core supply: 1.2 V or 3.3 V, delivering up to 1.5 A for the MC33908 and up to 800 mA for the MC33907</li> <li>Linear voltage regulator dedicated to MCU A/D reference voltage or I/Os supply (VCCA): 5.0 V or 3.3 V</li> <li>Linear voltage regulator dedicated to auxiliary functions or to a sensor supply (VCCA tracker or independent 5.0 V/3.3 V)</li> <li>Multiple wake-up sources in Low-power mode: CAN and/or IOs</li> <li>Battery voltage sensing and multiplexer output terminal (various signal monitoring)</li> <li>Enhanced safety block associated with fail-safe outputs</li> <li>Six configurable I/Os</li> <li>ISO11898 high-speed CAN interface compatibility for baud rates of 40 kB/s to 1.0 MB/s</li> <li>High EMC immunity and ESD robustness</li> </ul> |

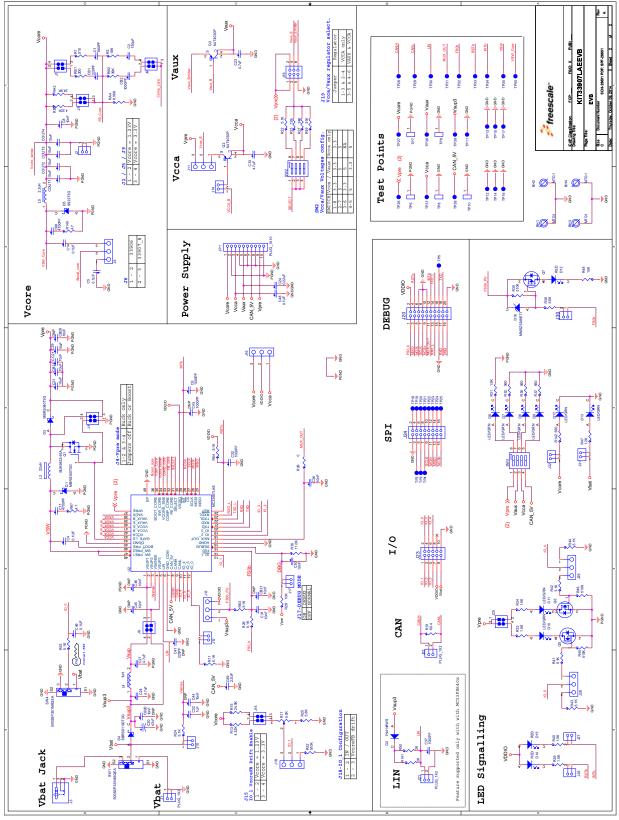

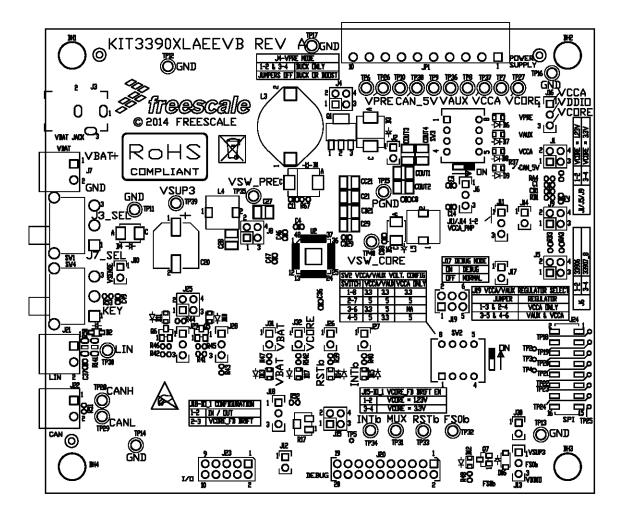

### 4.4 Board Description

The EVB comes with either a Freescale MC33907 or MC33908 IC mounted on it. Below is a board-level logic diagram.

#### Table 2. Board Description

| Name                    | Description                                                                          |

|-------------------------|--------------------------------------------------------------------------------------|

| Buck/Buck-Boost Section | VPRE DC/DC selection mode, either Boost or Buck                                      |

| Battery Connection      | Battery voltage input, either on Jack (black connector) or Phoenix (green) connector |

| Main Switch             | Battery voltage ON/OFF                                                               |

| Ignition Key Switch     | Simulate ignition key. Connected to IO_0                                             |

#### Table 2. Board Description (continued)

| Name                                                  | Description                                                                                                                                                                     |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LIN Bus                                               | LIN bus as a master                                                                                                                                                             |

| CAN Bus                                               | CANH and CANL differential pair                                                                                                                                                 |

| I/Os of MC33907_8                                     | All IOs, VDDIO and GND available                                                                                                                                                |

| Second Resistor Bridge - V <sub>DRIFT</sub> Selection | Bridge resistor for V <sub>CORE</sub> redundant check                                                                                                                           |

| Main Signals of MC33907_8                             | • SPI, VDDIO, fail-safe pin, CAN and LIN digital, MUXOUT, INTB and RSTB available                                                                                               |

| V <sub>CCA</sub> and V <sub>AUX</sub> Selection       | V <sub>CCA</sub> and V <sub>AUX</sub> voltage selection                                                                                                                         |

| FS Output Circuitry                                   | FS0B configuration                                                                                                                                                              |

| SPI Dongel Connector                                  | Connector with SPI bus. Compliant to SPIGen Freescale board                                                                                                                     |

| DBG Mode Select                                       | Controls Debug or Normal mode entering at boot up                                                                                                                               |

| V <sub>CORE</sub> Selection                           | V <sub>CORE</sub> voltage selection                                                                                                                                             |

| Compensation Network                                  | Compensation network selection                                                                                                                                                  |

| LEDs for Power Supplies                               | Switches for ON/OFF on LEDs                                                                                                                                                     |

| Power Supplies                                        | <ul> <li>MC33907LAE or MC33908LAE output power supply (V<sub>PRE</sub>, V<sub>CORE</sub>, V<sub>AUX</sub>, V<sub>CCA</sub>)<br/>(only for MC33907LAE and MC33908LAE)</li> </ul> |

#### 4.5 **Evaluation Board Configuration**

Figure 3 shows a configuration example for the EVB, which enables:

- V<sub>CORE</sub> 3.3 V ٠

- Compensation network for MPC5643L •

- $V_{CCA}$  and  $V_{AUX}$  = 5.0 V •

- V<sub>CCA</sub> with external PNP •

- Debug mode •

- V<sub>PRE</sub> in Buck mode •

- •

- $V_{DDIO}$  tied to  $V_{CCA}$  Various signalling LEDs enabled •

- IO1 configured as IN/OUT •

Figure 3. Default Board Configuration

## 4.6 LED Definitions

The following table lists the LEDs used as visual output devices on the EVB:

### Table 3. LEDs

| Schematic<br>Label | Name               | Description                                         |

|--------------------|--------------------|-----------------------------------------------------|

| D6                 | V <sub>PRE</sub>   | Indicator of pre-regulator voltage                  |

| D7                 | V <sub>AUX</sub>   | Indicator of auxiliary power supply                 |

| D8                 | V <sub>CCA</sub>   | Indicator of ADC power supply                       |

| D9                 | CAN_5V             | Indicator of 5.0 V CAN voltage                      |

| D10                | IO_5               | Indicator of IO_5 state                             |

| D11                | IO_4               | Indicator of IO_4 state                             |

| D12                | FS0B               | Indicator for fail-safe output number 0             |

| D13                | V <sub>BAT_P</sub> | Indicator of battery voltage after protection diode |

| D14                | RSTB               | Indicator of a reset                                |

| D15                | INTB               | Indicator of an interrupt                           |

| D17                | V <sub>CORE</sub>  | Indicator of V <sub>CORE</sub> power supply         |

## 4.7 Test Point Definitions

The following test-point jumpers provide access to signals on the MC33907 or MC33908 IC:

### Table 4. Test Points

| Schematic Label | Signal Name | Description  |

|-----------------|-------------|--------------|

| TP2             | J24.3       | -            |

| TP3             | J24.5       | -            |

| TP4             | J24.7       | -            |

| TP5             | J20.16      | -            |

| TP6             | PGND        | Power ground |

| TP7             | PGND        | Power ground |

| TP8             | GND         | Ground       |

| TP9             | GND         | Ground       |

| TP10            | GND         | Ground       |

| TP11            | GND         | Ground       |

| TP12            | GND         | Ground       |

| TP13            | GND         | Ground       |

| TP14            | GND         | Ground       |

| TP15            | GND         | Ground       |

#### Table 4. Test Points (continued)

| Schematic Label | Signal Name       | Description                        |

|-----------------|-------------------|------------------------------------|

| TP16            | GND               | Ground                             |

| TP17            | GND               | Ground                             |

| TP18            | J24.2             | -                                  |

| TP19            | J24.4             | -                                  |

| TP20            | J24.6             | -                                  |

| TP21            | J24.8             | -                                  |

| TP22            | J24.10            | -                                  |

| TP23            | J24.12            | -                                  |

| TP24            | J24.14            | -                                  |

| TP25            | J24.16            | -                                  |

| TP26            | V <sub>PRE</sub>  | Pre-regulator voltage              |

| TP27            | V <sub>CORE</sub> | Core voltage for the MCU           |

| TP28            | CANH              | -                                  |

| TP29            | CANL              | -                                  |

| TP30            | LIN               | LIN bus                            |

| TP31            | MUX_OUT           | Output from the analog multiplexer |

| TP32            | FS0B              | Fail-safe output                   |

| TP33            | RSTB              | Reset signal                       |

| TP34            | INTB              | Interrupt output                   |

| TP35            | $V_{SW}$          | V <sub>PRE</sub> Switching voltage |

| TP36            | V <sub>AUX</sub>  | Auxiliary power supply             |

| TP37            | V <sub>CCA</sub>  | ADC power supply                   |

| TP38            | CAN_5V            | CAN power supply                   |

| TP39            | V <sub>SUP3</sub> | Supply voltage                     |

| TP40            | VSW_Core          | V <sub>CORE</sub> supply voltage   |

## 4.8 Connector and Jumper Definitions

### Table 5. Main Power Supply Connector

| JP1 Pin Number | Name of Power Rail | Description              |

|----------------|--------------------|--------------------------|

| 1              | V <sub>CORE</sub>  | Core voltage for the MCU |

| 2              | PGND               | Power ground             |

| 3              | V <sub>CCA</sub>   | ADC power supply         |

| 4              | GND                | Ground                   |

| 5              | V <sub>AUX</sub>   | Auxiliary power supply   |

| 6              | GND                | Ground                   |

| 7              | CAN_5V             | CAN power supply         |

| 8              | GND                | Ground                   |

| 9              | V <sub>PRE</sub>   | Pre-regulator voltage    |

| 10             | PGND               | Power ground             |

#### Table 6. Jumpers J1 through J31 (Including Connectors)

| Schematic<br>Label | Pin Number                                                                                                                     | Pin Name | Jumper/Pin Function        |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------|

| J1                 | Compensation network for FB_core – part 1                                                                                      |          |                            |

|                    | 1-2                                                                                                                            |          | V <sub>CORE</sub> = 1.23 V |

|                    | 3-4                                                                                                                            |          | V <sub>CORE</sub> = 3.3 V  |

| J2                 | C_OUT – selection of output capacitance for $V_{CORE}$<br>If connected, output capacitance is 40 $\mu$ F, 20 $\mu$ F otherwise |          |                            |

|                    | No jumper                                                                                                                      |          | C <sub>OUT</sub> = 20 μF   |

|                    | 1-2                                                                                                                            |          | C <sub>OUT</sub> = 40 μF   |

| J3                 | Power supply DC 12 V                                                                                                           |          |                            |

| J4                 | Buck-boost/standard buck mode configuration                                                                                    |          |                            |

|                    | 1-2                                                                                                                            |          | Buck-boost configuration   |

|                    | 3-4                                                                                                                            |          |                            |

|                    | No jumper                                                                                                                      |          | Buck only configuration    |

| J5                 | V <sub>CORE</sub> selection                                                                                                    |          |                            |

|                    | 1-2                                                                                                                            |          | V <sub>CORE</sub> = 1.23 V |

|                    | 3-4                                                                                                                            |          | V <sub>CORE</sub> = 3.3 V  |

| Schematic<br>Label | Pin Number                                                                                                                                                                                                                                                  | Pin Name                                                             | Jumper/Pin Function                                                                                          |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| J6                 | Configuration for Boots_core pin                                                                                                                                                                                                                            |                                                                      |                                                                                                              |

|                    | 1-2                                                                                                                                                                                                                                                         |                                                                      | Boots_core pin connected to GND – used for devices with linear voltage regulator on $V_{\mbox{CORE}}$        |

|                    | 2-3                                                                                                                                                                                                                                                         |                                                                      | Boots_core pin connected to SW_core – used for devices with switching mode power supply on V <sub>CORE</sub> |

| J7                 |                                                                                                                                                                                                                                                             | nax. voltage = 40<br>should be used to                               | V)<br>o supply EVB from protected voltage source                                                             |

|                    | 1                                                                                                                                                                                                                                                           | VBAT                                                                 | Positive supply                                                                                              |

|                    | 2                                                                                                                                                                                                                                                           | GND                                                                  | Ground                                                                                                       |

| J8                 | Power supply fo<br>Allows disconne<br>Normally (no me                                                                                                                                                                                                       | cting of all three                                                   | supply pins for current measurements<br>pers should be connected                                             |

|                    | 1-2                                                                                                                                                                                                                                                         |                                                                      | Enables power supply (V <sub>BAT_P</sub> ) for VSUP3 pin of MC33907 (or MC33908)                             |

|                    | 3-4                                                                                                                                                                                                                                                         |                                                                      | Enables power supply ( $V_{SUP}$ ) for VSUP1 and VSUP2 pins of MC33907 (or MC33908)                          |

| J9                 | Compensation r                                                                                                                                                                                                                                              | network for FB_co                                                    | bre – part 2                                                                                                 |

|                    | 1-2                                                                                                                                                                                                                                                         |                                                                      | V <sub>CORE</sub> = 1.23 V                                                                                   |

|                    | 3-4                                                                                                                                                                                                                                                         |                                                                      | V <sub>CORE</sub> = 3.3 V                                                                                    |

| J10                | V <sub>SNS</sub> EN – con                                                                                                                                                                                                                                   | IS_EN – connects battery voltage before filter to V <sub>SENSE</sub> |                                                                                                              |

| J11                | External transist                                                                                                                                                                                                                                           | or for V <sub>CCA</sub>                                              |                                                                                                              |

|                    | 1-2                                                                                                                                                                                                                                                         |                                                                      | Emitter of Q2 connected to VCCA_E                                                                            |

|                    | 2-3                                                                                                                                                                                                                                                         |                                                                      | External transistor Q2 is not used                                                                           |

| J12                | IO_0_PD – pulls down IO_0                                                                                                                                                                                                                                   |                                                                      |                                                                                                              |

| J13                | FS0B pull-up connection                                                                                                                                                                                                                                     |                                                                      |                                                                                                              |

|                    | 1-2                                                                                                                                                                                                                                                         |                                                                      | FS0B pull-up is supplied from V <sub>SUP3</sub>                                                              |

|                    | 2-3                                                                                                                                                                                                                                                         |                                                                      | FS0B pull-up is supplied from V <sub>DDIO</sub>                                                              |

| J14                | Connects base of the transistor Q2 to the VCCA_B pin                                                                                                                                                                                                        |                                                                      |                                                                                                              |

| J15                | External resistor bridge monitoring (for future use)<br>Used in conjunction with J18<br>Resistor bridge has to be in same configuration as J5<br>Voltage on this voltage divider has to be adjusted to same level as for first bridge using potentiometer F |                                                                      | e configuration as J5                                                                                        |

|                    | 1-2                                                                                                                                                                                                                                                         |                                                                      | V <sub>CORE</sub> = 1.23 V                                                                                   |

|                    | 3-4                                                                                                                                                                                                                                                         |                                                                      | V <sub>CORE</sub> = 3.3 V                                                                                    |

| J16                | V <sub>DDIO</sub> tracking                                                                                                                                                                                                                                  | 1                                                                    |                                                                                                              |

|                    | 1-2                                                                                                                                                                                                                                                         |                                                                      | V <sub>DDIO</sub> tracks V <sub>CCA</sub>                                                                    |

|                    | 2-3                                                                                                                                                                                                                                                         |                                                                      | V <sub>DDIO</sub> tracks V <sub>CORE</sub>                                                                   |

| Schematic<br>Label | Pin Number                              | Pin Name           | Jumper/Pin Function                                                |

|--------------------|-----------------------------------------|--------------------|--------------------------------------------------------------------|

| J17                | DBG_EN - enables debug mode             |                    |                                                                    |

|                    | No jumper                               |                    | Normal mode                                                        |

|                    | 1-2                                     |                    | Debug mode                                                         |

| J18                | DRIFT_MONIT                             | - External resisto | br bridge monitoring                                               |

|                    | 1-2                                     |                    | Second resistor bridge on IO_1 is disabled                         |

|                    | 2-3                                     |                    | Reserved for future use                                            |

| J19                | V <sub>CCA</sub> /V <sub>AUX</sub> regu | lator selection    |                                                                    |

|                    | 1-3 and 2-4                             |                    | V <sub>AUX</sub> is disabled                                       |

|                    | 3-5 and 4-6                             |                    | V <sub>AUX</sub> is enabled                                        |

| J20                | Additional Inputs                       | s/Output           |                                                                    |

|                    | 1                                       | FS0B               | Fail-safe output                                                   |

|                    | 2                                       | VDDIO              | V <sub>DDIO</sub> voltage                                          |

|                    | 3                                       | MISO               | SPI – Master Input Slave Output                                    |

|                    | 4                                       | RSTB               | Reset pin – connect to the reset line of the MCU                   |

|                    | 5                                       | MOSI               | SPI – Master Output Slave Input                                    |

|                    | 6                                       | GND                | Ground                                                             |

|                    | 7                                       | SCLK               | SPI – clock                                                        |

|                    | 8                                       | GND                | Ground                                                             |

|                    | 9                                       | NCS                | SPI – Chip Select                                                  |

|                    | 10                                      | GND                | Ground                                                             |

|                    | 11                                      | MUX_OUT            | Output from the multiplexer – connect to the MCU's ADC             |

|                    | 12                                      | INTB               | Interrupt pin – connect to the MCU IO with an interrupt capability |

|                    | 13                                      | RXD_L              | LIN receive pin – connect to the MCU                               |

|                    | 14                                      | TXD_L              | LIN transmit pin – connect to the MCU                              |

|                    | 15                                      | GND                | Ground                                                             |

|                    | 16                                      | TP5                | -                                                                  |

|                    | 17                                      | RXD                | CAN receive pin – connect to the MCU                               |

|                    | 18                                      | TXD                | CAN transmit pin – connect to the MCU                              |

|                    | 19                                      | DBG                | Debug pin                                                          |

|                    | 20                                      | GND                | Ground                                                             |

| Schematic<br>Label | Pin Number             | Pin Name | Jumper/Pin Function                              |  |  |  |  |  |

|--------------------|------------------------|----------|--------------------------------------------------|--|--|--|--|--|

| J21                | LIN connector          |          |                                                  |  |  |  |  |  |

|                    | 1                      | LIN      | LIN after transceiver (NOT the MCU side)         |  |  |  |  |  |

|                    | 2                      | GND      | Ground                                           |  |  |  |  |  |

| J22                | CAN connector          |          |                                                  |  |  |  |  |  |

|                    | 1                      | CANH     | CANH signal after transceiver (NOT the MCU side) |  |  |  |  |  |

|                    | 2                      | CANL     | CANL signal after transceiver (NOT the MCU side) |  |  |  |  |  |

| J23                | General Inputs/Outputs |          |                                                  |  |  |  |  |  |

|                    | pin1                   | IO_1     | -                                                |  |  |  |  |  |

|                    | pin2                   | IO_0     | -                                                |  |  |  |  |  |

|                    | pin3                   | IO_3     | -                                                |  |  |  |  |  |

|                    | pin4                   | IO_2     | -                                                |  |  |  |  |  |

|                    | pin5                   | IO_5     | -                                                |  |  |  |  |  |

|                    | pin6                   | IO_4     | -                                                |  |  |  |  |  |

|                    | pin7                   | VDDIO    | -                                                |  |  |  |  |  |

|                    | pin8                   | NC       | -                                                |  |  |  |  |  |

|                    | pin9                   | VBAT     | -                                                |  |  |  |  |  |

|                    | pin10                  | GND      | -                                                |  |  |  |  |  |

| Schematic<br>Label | Pin Number                                                                                   | Pin Name           | Jumper/Pin Function                         |  |  |  |  |  |

|--------------------|----------------------------------------------------------------------------------------------|--------------------|---------------------------------------------|--|--|--|--|--|

| J24                | SPI/USB dongle or MCU connection<br>SPI/USB dongle should be directly connected to this port |                    |                                             |  |  |  |  |  |

|                    | pin1                                                                                         | GND                | Ground                                      |  |  |  |  |  |

|                    | pin2                                                                                         | TP18               | -                                           |  |  |  |  |  |

|                    | pin3                                                                                         | TP2                | -                                           |  |  |  |  |  |

|                    | pin4                                                                                         | TP19               | -                                           |  |  |  |  |  |

|                    | pin5                                                                                         | TP3                | -                                           |  |  |  |  |  |

|                    | pin6                                                                                         | TP20               | -                                           |  |  |  |  |  |

|                    | pin7                                                                                         | TP4                | -                                           |  |  |  |  |  |

|                    | pin8                                                                                         | TP21               | -                                           |  |  |  |  |  |

|                    | pin9                                                                                         | SCLK               | SPI – clock                                 |  |  |  |  |  |

|                    | pin10                                                                                        | TP22               | Not connected                               |  |  |  |  |  |

|                    | pin11                                                                                        | MOSI               | SPI – Master Output Slave Input             |  |  |  |  |  |

|                    | pin12                                                                                        | TP23               | -                                           |  |  |  |  |  |

|                    | pin13                                                                                        | MISO               | SPI – Master Input Slave Output             |  |  |  |  |  |

|                    | pin14                                                                                        | TP24               | -                                           |  |  |  |  |  |

|                    | pin15                                                                                        | NCS                | SPI – Chip Select                           |  |  |  |  |  |

|                    | pin16                                                                                        | TP25               | -                                           |  |  |  |  |  |

| J25                | Power supply for LEDs on IO_4 and IO_5 (D11, D10)                                            |                    |                                             |  |  |  |  |  |

|                    | 1-2                                                                                          |                    | Enables power supply for IO_4 (D11)         |  |  |  |  |  |

|                    | 3-4                                                                                          |                    | Enables power supply for IO_5 (D10)         |  |  |  |  |  |

| J26                | RSTB_LED_EN                                                                                  | – enables LED      | D14 for RSTB output                         |  |  |  |  |  |

| J27                | INTB_LED_EN                                                                                  | – enables LED [    | D15 for INTB output                         |  |  |  |  |  |

| J28                | 105_0UT - 10_                                                                                | 5 output configu   | ration                                      |  |  |  |  |  |

|                    | 1-2                                                                                          |                    | IO_5 connected to LED D10 via transistor Q5 |  |  |  |  |  |

|                    | 2-3                                                                                          |                    | IO_5 pulled down                            |  |  |  |  |  |

| J29                | 104_0UT - 10_4                                                                               | 4 output configu   | ration                                      |  |  |  |  |  |

|                    | 1-2                                                                                          |                    | IO_4 pulled down                            |  |  |  |  |  |

|                    | 2-3                                                                                          |                    | IO_4 connected to LED D11 via transistor Q6 |  |  |  |  |  |

| J30                | Enable LED D12                                                                               | 2 for fail-safe.   | ·                                           |  |  |  |  |  |

| J31                | Enables LED D1                                                                               | 13 as indicator o  | f power supply                              |  |  |  |  |  |

| J32                | Enables LED D1                                                                               | 17 as indicator fo | or V <sub>CORE</sub> power supply           |  |  |  |  |  |

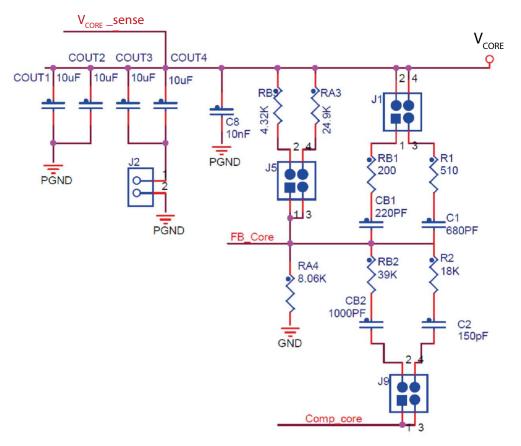

### 4.8.1 Compensation Network

Voltage regulator needs a feedback from the V<sub>CORE</sub> voltage to be able to adjust (control) output voltage. For this reason, two bridges are implemented in the external MC33907 or MC33908 circuitry. Static feedback (steady-state) voltage is defined by a simple resistor bridge (given by RA3/RB3 and RA4). Dynamic behavior of the regulator is controlled by another bridge that is an RC divider (defined by RBx, CBx, R1, C1, R2, C2). Compensation network is shown in the Figure 4. Steady-state voltage can be either 1.23 V or 3.3 V. To tune the dynamic performance, the board is equipped by two different bridges (possible combinations of the jumpers J1 and J9 are shown in Table 7). The combinations shown in Table 7 are chosen to provide an optimal performance for the given output voltage. The real dynamic performance can differ for different applications and can be tuned by changing the compensation network and by adding output capacitors (J2).

| Table 7. Compensation | Network | and V <sub>CORE</sub> | Settings |

|-----------------------|---------|-----------------------|----------|

|                       |         |                       |          |

| V <sub>CORE</sub> | Jumper Settings |                  |     |  |  |  |  |

|-------------------|-----------------|------------------|-----|--|--|--|--|

| (V)               | Static Behavior | Dynamic Behavior |     |  |  |  |  |

|                   | J5              | J1               | J9  |  |  |  |  |

| 1.23              | 3-4             | 3-4              | 3-4 |  |  |  |  |

| 3.3               | 1-2             | 1-2              | 1-2 |  |  |  |  |

Figure 4. Compensation Network and V<sub>CORE</sub> Setup Schematic

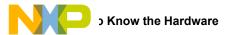

### 4.8.2 Second Resistor Bridge - V<sub>DRIFT</sub> Monitoring

To increase safety level of an application, a second resistor bridge has been added. This bridge generates the same voltage as the bridge connected to FB\_core pin. If difference between voltages is greater than  $V_{DRIFT}$ , then the FS state machine is impacted.

#### Table 8. V<sub>DRIFT</sub> Monitoring Settings

| V <sub>CORE</sub> | Hardware Settings |     |  |  |  |

|-------------------|-------------------|-----|--|--|--|

| (V)               | J15               | J18 |  |  |  |

| 1.23              | 1+2               | 3+4 |  |  |  |

| 3.3               | 3+4               | 1+2 |  |  |  |

To use this functionality, few settings have to be done in the hardware as well as in the software configuration. For the hardware part, the second resistor bridge has to be configured by jumper J18, as shown in the Figure 5, and adjusted by the potentiometer R17 to set the same voltage as on the first bridge. Software sets registers INIT\_Vreg1 (bit Vcore\_FB to 1) and register INIT\_FSSM1 (bit IO\_1\_FS to 1).

Figure 5. Second Resistor Bridge

## 4.9 Switch Definitions

### Table 9. Switches

| Switch Number | Position                                                                 | Function                                                    | Description                                                                                 |  |

|---------------|--------------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|

| SW1           | Power supply select                                                      |                                                             |                                                                                             |  |

|               | 1-2                                                                      | Supply from J7 selected                                     |                                                                                             |  |

|               | 2-3                                                                      | Power jack on J3 selected                                   |                                                                                             |  |

| SW2           | V <sub>CCA</sub> /V <sub>AUX</sub> switch<br>Only one choice is possible | at the same time                                            |                                                                                             |  |

|               | 1                                                                        | 3.3 V / 3.3 V                                               |                                                                                             |  |

|               | 2                                                                        | 5.0 V / 5.0 V                                               |                                                                                             |  |

|               | 3                                                                        | 3.3 V / 5.0 V                                               | This setting is not allowed if $V_{AUX}$ is not used - opt $V_{CCA}$ only (selected by J19) |  |

|               | 4                                                                        | 5.0 V / 3.3 V                                               |                                                                                             |  |

| SW3           | LEDs - indicators for power                                              | supplies                                                    |                                                                                             |  |

|               | 1                                                                        | V <sub>PRE</sub>                                            | Enables LED indicator for pre-regulator                                                     |  |

|               | 2                                                                        | V <sub>AUX</sub>                                            | Enables LED indicator for auxiliary power supply                                            |  |

|               | 3                                                                        | V <sub>CCA</sub>                                            | Enables LED indicator for V <sub>CCA</sub> regulator                                        |  |

|               | 4                                                                        | CAN_5 V                                                     | Enables LED indicator for CAN regulator                                                     |  |

| SW4           | Ignition switch                                                          |                                                             |                                                                                             |  |

|               | 1-2                                                                      | IO_0 connected to V <sub>BAT</sub><br>(ignition key active) |                                                                                             |  |

|               | 2-3                                                                      | No voltage on the IO_0                                      |                                                                                             |  |

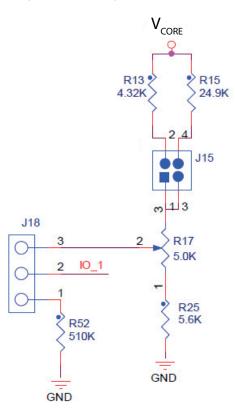

## 5 Accessory Interface Board

The KIT33907LAEEVB or KIT33908LAEEVB is generally used with the KITUSBSPIDGLEVME interface dongle (see Figure 6), which provides a bidirectional SPI/USB conversion. This small board makes use of the USB, SPI, and parallel ports built into Freescale's MC68HC908JW32 microcontroller. The main function provided by this dongle is to allow Freescale evaluation kits that have a parallel port to communicate via a USB port to a PC. For more information regarding KITUSBSPIDGLEVME interface dongle, go to http://www.freescale.com/webapp/sps/site/prod\_summary.jsp?code=KITUSBSPIDGLEVME.

Figure 6. KITUSBSPIDGLEVME Interface Dongle

For information on setting up the dongle with the EVB, see "Connecting the KITUSBSPIDGLEVME Interface Dongle".

## 5.1 Connecting the KITUSBSPIDGLEVME Interface Dongle

A typical connection of KITUSBSPIDGLEVME Interface Dongle (section "Accessory Interface Board") to the KIT33907LAEEVB or KIT33908LAEEVB evaluation board is done through connector J24 (see Figure 7). In this configuration, it is recommended to use the EVB in a debug mode (J17 configured as Debug). In this mode there is no timeout used for the INIT phase, so the initialization commands can be sent anytime. WD refresh is also not mandatory in the debug mode. This means that no action is taken if WD refresh fails (WD window expires, WD refreshed during closed window, wrong WD answer).

KIT33907LAEEVB/KIT33908LAEEVB

#### Figure 7. Connecting KITUSBSPIDGLEVME to the Evaluation Board

## 6 Installing the Software and Setting up the Hardware

## 6.1 Configuring the Hardware

Figure 8 shows the setup required to use KIT33907LAEEVB or KIT33908LAEEVB.

KIT33907LAEEVB/KIT33908LAEEVB Figure 8. Evaluation Board Setup

### 6.2 Step-by-step Instructions for Setting Up the Hardware Using SPIGen

In order to perform the demonstration examples, first set up the EVB hardware and software as follows:

- 1. Ready the computer, install SPIGen.

- 2. Connect SPIGen on J24.

- 3. Connect SPIGen USB cable to the PC.

- 4. Set the EVB jumpers and switches as needed. Refer to Figure 3 for an example.

- 5. Select Debug or Normal mode with J17 (1).

- 6. Attach loads to JP1 as needed.

- 7. Attach DC power supply on J3 or J7 (maximum voltage: 40 V).

- 8. Switch SW1 to supply the board.

- If SW2 switches are ON and V<sub>BAT</sub> is set correctly, then V<sub>PRE</sub>, V<sub>CCA</sub>, V<sub>AUX</sub>, CAN\_5 V LEDs should turn ON. V<sub>BAT</sub> value is dependent on V<sub>PRE</sub> configuration. In Buck mode, it must be 8.2 V min. FS0B LED should turn ON (J13 / J30 must be plugged).

- 10. Launch SPIGen.

- 11. Open the SPIGen configuration file.

- 12. In Debug mode, use the SPIGen batch RST\_counter\_to\_0.spi to reset the error counter. FS0B should turn off (LED D12 turned off).

Note: At this stage, EVB is powered and SPIGen is working. When Normal mode is selected with J17, valid WD must be sent, otherwise the device goes into deep fail-safe.

## 7 Initialization and Configuration Mode

## 7.1 INIT Phase

INIT registers are set after POR (power-on reset) condition with their default values. This default configuration is compatible with the default EVB settings excluding one register - INIT FSSM2. Bit IO\_23\_FS in this register is set by default, which means the fail-safe outputs (FCCU\_x of the MPC5643L or similar device) have to be connected to the IOs 2 and 3 of the MC33907 or MC33908. If MPC5643L (or similar device) is not used, the bit IO\_23\_FS has to be cleared during INIT phase (setting shown in Table 10). INIT phase of the main part is finished after writing to the INIT\_INT register. This command closes access to the INIT registers and device goes in Normal mode. This sequence (INIT\_FSSM2, INIT\_INT) has to be done in the same manner in Debug and also in Standard mode. The only difference is in the timeout constraints used for the Standard mode. In the Standard mode, INIT commands have to be sent before the 256 ms timer (starting from the RST pin release) expires.

### Table 10. INIT FSSM2 Setting

|      | bit15 | bit14 | bit13 | bit12 | bit11 | bit10 | bit9 | bit8 | bit7            | bit6         | bit5 | bit4  | bit3         | bit2         | bit1         | bit0         |

|------|-------|-------|-------|-------|-------|-------|------|------|-----------------|--------------|------|-------|--------------|--------------|--------------|--------------|

| MOSI | 1     | 1     | 0     | 0     | 1     | 0     | 1    | Ρ    | RSTB_<br>err_FS | IO_23_<br>FS | PS   | F_FS1 | Secure<br>_3 | Secure<br>_2 | Secure<br>_1 | Secure<br>_0 |

|      | bit15 | bit14 | bit13 | bit12 | bit11 | bit10 | bit9 | bit8 | bit7            | bit6         | bit5 | bit4  | bit3         | bit2         | bit1         | bit0         |

| MOSI | 1     | 1     | 0     | 0     | 1     | 0     | 1    | 1    | 0               | 0            | 0    | 1     | 1            | 0            | 0            | 0            |

## 7.2 Normal Operation

During normal operation (after INIT phase), in both modes it is possible to send a WD refresh command. In the Debug mode, no action is performed on a bad WD answer. In Normal mode, the KITUSBSPIDGLEVMESPI interface dongle is not able to guarantee WD refresh period (Windows XP, 7 are not real-time operating systems); nevertheless, WD refresh was successfully tested in Standard mode using WD window duration 512 ms (reconfigured in the INIT phase).

## 7.3 Debug Mode

The KIT33907LAEEVB or KIT33908LAEEVB is mainly intended to be used in Debug mode. Use in normal mode requires an MCU to be able to manage the WD. To use the part in Normal mode, it is required to send a good WD answer at startup, in the 256 ms windows after reset release, then to update the WD at the right time. With KIT33907LAEEVB or KIT33908LAEEVB attached to the KITUSBSPIDGLEVME, this can be done only manually, which is not feasible.

## 8 Graphical User Interface

There are two possible interfaces to configure registers:

- SPI generator (SPIGen) allows easy and simple drive, setting registers individually or sending batch of commands.

- MC33907\_8 GUI provides friendly access to registers with a visual environment.

### 8.1 SPIGen

The latest version of SPIGen is designed to run on any Windows 8, Windows 7, Vista or XP-based operating system. To install the software, go to www.freescale.com/analogtools and select your kit. Click on that link to open the corresponding Tool Summary Page. Look for "Jump Start Your Design". Download to your computer desktop the SPIGen software as well as the associated configuration file.

Run the install program from the desktop. The Installation Wizard guides you through the rest of the process.

To use SPIGen, go to the Windows Start menu, then Programs, then SPIGen, and click on the SPIGen icon. The SPIGen Graphic User Interface (GUI) appears. Go to the file menu in the upper left hand corner of the GUI, and select "Open". In the file selection window that appears, set the "Files of type:" drop-down menu to "SPIGen Files (\*.spi)". (In an exceptional case, the file name may have a .txt extension, in which case you should set the menu to "All Files (\*.\*)".) Next, browse for the configuration file you saved on your desktop earlier and select it. Click "Open", and SPIGen creates a specially configured SPI command generator for your EVB.

In order to fill specific need, it is also possible to edit registers with another value and to save it for further use, either as standalone or inside a batch.

Figure 9 shows a batch called "RST\_counter\_to\_0", as an example.

| Commands To Send                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Commands To Send<br>WD_window_DIS_xCD0C<br>INIT_FSSM2_xCB0C<br>INIT_INT_x8C00<br>WD_answer1_xD04D<br>WD_answer2_xD19B<br>WD_answer3_xD137<br>WD_answer4_xD16E<br>WD_answer5_xD10C<br>WD_answer6_xD189<br>WD_answer7_xD072<br>FS_OUT_xD327 |

|                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                           |

| Batch Name                                                                                                                                                                                                                                |

| RST_counter_to_0                                                                                                                                                                                                                          |

Figure 9. RST\_counter\_to\_0 Batch

At startup or when resuming from LPOFF mode the reset error counter starts at level 1 and FS0B is asserted low. To remove activation of FS0B, the RST error counter must go back to value "0" (seven consecutive good WD refresh decreases the reset error counter down to 0) and a right command is sent to FS\_OUT register. This can be demonstrated with this batch running in debug mode.

The batch shown in Figure 9 executes the following action:

- WD\_Window\_DIS\_xCD0C:

- Disables normal WD

- INIT\_FSSM2\_xCB0C:

- IO\_23\_FS bits configured in "NOT SAFETY" mode

- WD\_answer1 to WD\_answer7:

- If the part is in debug mode, this sends the right first WD answer and allows the reset counter to change to 0

- FS\_OUT\_xD327:

- Disables FS0B pin, coming back to high level (D12 turned off)

- INIT\_INT\_x8C00:

- Closes the init phase of the main state machine

- CAN\_MODE\_B0C0:

- Enables CAN transceiver

## 8.2 Working with KIT33907\_8 GUI

The GUI allows the user to program all SPI features by using a friendly interface as well as modifying the register table manually for advance users. Refer to KTMPC5643DBEMOUG for a complete description of the GUI.

1. To launch the MC33907\_8 GUI application, select the application icon from the Freescale folder in the Start menu as it is shown in Figure 10.

Figure 10. Launching MC33907\_8 GUI application

2. Figure 11 shows the status of several registers at startup. In this example, register INIT\_FSSM2 has bit IO\_23\_FS configured as SAFETY CRITICAL.

| PowerSBC GUI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|