# Surge Protected, Single Input, Dual Output Load Switch with OVP

#### **Features**

- Single Input, Dual Output Low On- Resistance Switch

- ► VBUS to OUT: typ. 23mΩ

- ► VBUS to SYS: typ. 30mΩ (Reverse Blocking)

- Wide Input Voltage Range: 2.7V 13.5V

- ▶ VBUS Abs Max: 28V

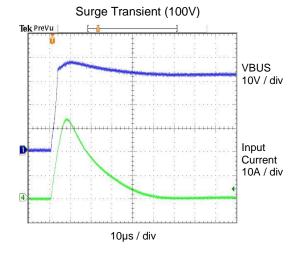

- Surge and ESD Protected Input

- ▶ Surge Protection

- IEC61000-4-5: > ±100V

- ► ESD Protection

- IEC61000-4-2 (Level 4) VBUS

- Contact: ±8kVAir Gap: ±15kVHBM: 2kV All Pins

- Integrated Over-voltage Protection (OVP)

- ▶ VBUS to OUT: 13.9V ±400mV

▶ VBUS to SYS: 5.25V ±250mV

- Maximum Continuous Current

- ► VBUS to OUT: 3.5A ► VBUS to SYS: 6A

- Dual Enable Control with Independent Shutdown Control

- ► Active LOW VBUS to OUT

- ► Active HIGH VBUS to SYS

- ► Active HIGH Shutdown

- VBUS detection LDO

- VBUS to SYS FLAG

- Over Temperature Protection

- Pb-free 28-Bump, WLCSP 2.96mm x 1.67mm

- -40°C to 85°C Operating Temperature Range

### **Brief Description**

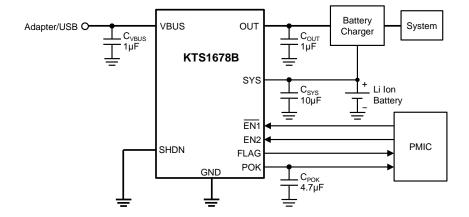

The KTS1678B features two low resistance power switches configured as single input, dual output, change-over switch. The input to both switches is protected against VBUS surge voltages of up to ±100V, and is also protected against over-voltage, with preset trip points on both the VBUS to OUT and VBUS to SYS paths, providing protection to downstream components from abnormal input conditions.

The main switch (VBUS to OUT) features a unidirectional active-LOW enabled 3.5A rated MOSFET, with an OVP trip point of 13.9V ±400mV. The secondary switch (VBUS to SYS) is an active-HIGH enabled, reverse-blocking 6.0A rated MOSFET, with an OVP trip point of 5.25V ±250mV. The input to both switches is rated up to a maximum of 28V.

When VBUS is greater than 2.7V, the POK LDO provides an "always ON" power source, regardless of the OVLO, EN1 and EN2 state, to power downstream components permitting operation without an installed battery.

The KTS1678B also features an active-HIGH SHUTDOWN pin to conserve power, plus over-temperature thermal protection.

The KTS1678B is packaged in advanced, fully "green" compliant, 2.96mm x 1.67mm, Wafer-Level Chip-Scale Package (WLCSP).

## **Applications**

- Smartphones and Tablets

- Mobile Internet Devices

- Wearables

- Portable Devices

## **Typical Application**

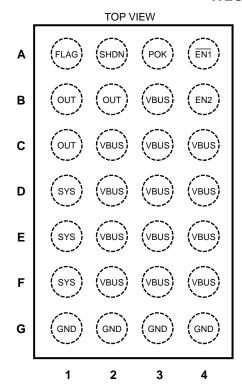

### **Pin Descriptions**

| Pin #                                                    | Name | Function                                                                           |

|----------------------------------------------------------|------|------------------------------------------------------------------------------------|

| A1                                                       | FLAG | Active HIGH CMOS Power good for VBUS to SYS path.                                  |

| A2                                                       | SHDN | Active HIGH input with internal 1MΩ pull-down resistor, for device shutdown.       |

| A3                                                       | POK  | Regulated output whenever VBUS is present                                          |

| A4                                                       | EN1  | Active LOW enable with internal 1MΩ pull-down resistor, for VBUS to OUT path only  |

| B1, B2, C1                                               | OUT  | Power switch output to load                                                        |

| B3, C2, C3, C4, D2, D3,<br>D4, E2, E3, E4, F2, F3,<br>F4 | VBUS | Input to the power switches and device supply                                      |

| B4                                                       | EN2  | Active HIGH enable with internal 1MΩ pull-down resistor, for VBUS to SYS path only |

| D1, E1, F1                                               | SYS  | Power switch output to battery                                                     |

| G1, G2, G3, G4                                           | GND  | Ground                                                                             |

#### WLCSP-28

28-Bump 2.96mm x 1.67mm x 0.620mm WLCSP Package

Top Mark

WW = Device ID Code,

XX = Date Code, YY = Assembly Code

ZZZZ = Serial Number

# Absolute Maximum Ratings<sup>1</sup>

#### $(T_A = 25^{\circ}C \text{ unless otherwise noted})$

| Symbol                       | Description                                      | Value                 | Units |

|------------------------------|--------------------------------------------------|-----------------------|-------|

| VBUS <sup>2</sup>            | VBUS to GND & VBUS to VOUT = GND or Float        | -2 <sup>3</sup> to 28 | V     |

| OUT                          | OUT to GND                                       | -0.3 to<br>VBUS+0.3   | V     |

| SYS                          | SYS to GND                                       | -0.3 to 6             | V     |

| SHDN, EN1, EN2,<br>POK, FLAG | Shutdown, Enable, POK and Flag pins              | -0.3 to 6             | V     |

| VBUS-OUT Current             | VBUS to OUT Continuous Current                   | 3.5                   | Α     |

|                              | VBUS to OUT Peak Current (5ms)                   | 7.0                   | Α     |

| VBUS-SYS Current             | VBUS to SYS Continuous Current                   | 6.0                   | Α     |

| VBUS-SYS Current             | VBUS to SYS Peak Current (5ms)                   | 12.0                  | Α     |

| TJ                           | Operating Temperature Range                      | -40 to 150            | °C    |

| Ts                           | Storage Temperature Range                        | -65 to 150            | °C    |

| T <sub>LEAD</sub>            | Maximum Soldering Temperature (at leads, 10 sec) | 260                   | °C    |

# Thermal Capabilities<sup>4</sup>

| Symbol                          | Description                                 | Value | Units |

|---------------------------------|---------------------------------------------|-------|-------|

| $\Theta_{JA}$                   | Thermal Resistance – Junction to Ambient    | 55    | °C/W  |

| P <sub>D</sub>                  | Maximum Power Dissipation at 25°C           | 2.27  | W     |

| ΔΡ <sub>D</sub> /Δ <sub>T</sub> | Derating Factor Above T <sub>A</sub> = 25°C | -41.3 | mW/°C |

# **Ordering Information**

| Part Number    | Marking                 | Operating<br>Temperature | Package |  |

|----------------|-------------------------|--------------------------|---------|--|

| KTS1678BEUQ-TR | LTXXYYZZZZ <sup>5</sup> | -40°C to +85°C           | WLCSP28 |  |

Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum rating should be applied at any one time.

<sup>2.</sup> Survives burst pulse up to 100V with  $2\Omega$  series impedance.

<sup>3.</sup> Pulsed, 50ms maximum non-repetitive.

<sup>4.</sup> Junction to Ambient thermal resistance is highly dependent on PCB layout. Values are based on thermal properties of the device when soldered to an EV board.

<sup>5.</sup> XX = Date Code, YY = Assembly Code, ZZZZ = Serial Number.

### Electrical Characteristics<sup>6</sup>

Unless otherwise noted, the *Min* and *Max* specs are applied over the full operation temperature range of -40°C to +85°C,  $V_{BUS} = 2.7V$  to 13.5V. Typical values are specified at room temperature (25°C) with  $V_{BUS} = 5V$ ,  $I_{VBUS} \le 2A$ , SHDN =  $\overline{EN1}$  = EN2 = LOW, POK = OPEN,  $C_{IN} = 0.1 \mu F$  and  $T_A = 25$ °C.

| Symbol                | Description                                                           | Conditions                                                                                                                          |                       | Min          | Тур          | Max          | Units |

|-----------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------|--------------|--------------|-------|

| Input                 |                                                                       |                                                                                                                                     |                       | -            |              |              |       |

| IQ                    | Input Quiescent Current                                               | $V_{BUS} = 5V, \overline{EN1} = EN2 = LO$                                                                                           |                       | 139          | 215          | μA           |       |

| I <sub>LK</sub>       | Input Leakage Current                                                 | VBUS = 5V, SHDN = HIGH                                                                                                              |                       |              | 0.7          | μA           |       |

| love o                | Input Supply Current in Over-                                         | $V_{BUS} = 15V$ , OUT = 0V,<br>$\overline{EN1} = EN2 = LOW$                                                                         |                       |              | 165          | 290          | μΑ    |

|                       | voltage mode                                                          | $V_{BUS} = 5.5V$ , SYS = 0V,<br>$\overline{EN1} = EN2 = HIGH$                                                                       |                       |              | 146          | 210          | μΑ    |

| VIN_CLAMP             | Input Clamp Voltage                                                   | I <sub>IN</sub> = 10mA, T <sub>A</sub> = 25°C                                                                                       |                       |              | 32.5         |              | V     |

| V <sub>BUS_UVLO</sub> | Under Voltage Lockout                                                 | V <sub>BUS</sub> Rising                                                                                                             |                       | 2.35<br>2.20 | 2.50<br>2.35 | 2.65<br>2.50 | V     |

| OVD VDII              | IS to OUT                                                             | V <sub>BUS</sub> Falling                                                                                                            |                       | 2.20         | 2.55         | 2.50         |       |

| OVF VBU               | 13 10 001                                                             | \/ 5\/                                                                                                                              | F0C                   | T            | - 00         | 20           | T 0   |

| Ron_out               | ON-Resistance VBUS to OUT                                             | V <sub>BUS</sub> = 5V, I <sub>OUT</sub> = 1A, T <sub>A</sub> = 2<br>V <sub>BUS</sub> = 12V, I <sub>OUT</sub> = 1A, T <sub>A</sub> = |                       |              | 23           | 39<br>39     | mΩ    |

| \ /                   | Own Waltana Tria Laval                                                | V <sub>BUS</sub> Rising                                                                                                             |                       | 13.5         | 13.9         | 14.3         | V     |

| Vout_ovlo             | Over-Voltage Trip Level                                               | V <sub>BUS</sub> Falling                                                                                                            |                       | 13.3         |              |              | V     |

| OVP VBU               | S to SYS                                                              |                                                                                                                                     |                       | •            |              |              | •     |

| Ron_sys               | ON-Resistance VBUS to SYS                                             | V <sub>BUS</sub> = 3V, I <sub>OUT</sub> = 1A, T <sub>A</sub> = 2                                                                    |                       | 30           | 40           | mΩ           |       |

| Vsys_ovlo             | O V II T: 1                                                           | V <sub>BUS</sub> Rising                                                                                                             |                       | 5.00         | 5.25         | 5.50         | V     |

|                       | Over-Voltage Trip Level                                               | V <sub>BUS</sub> Falling                                                                                                            |                       | 4.80         |              |              | V     |

| I <sub>SYS_RB</sub>   | SYS Reverse Current                                                   | V <sub>BUS</sub> = 0V, V <sub>SYS</sub> = 4.4V, T <sub>A</sub> =                                                                    |                       |              | 1            | μA           |       |

| I <sub>VBUS_RB</sub>  | SYS-to-VBUS Reverse<br>Current                                        | Vsys = 4.4V, V <sub>BUS</sub> = 0V, T <sub>A</sub> = 25°C,<br>measured at VBUS, no ambient light                                    |                       |              | 0.05         | 2            | nA    |

| РОК                   |                                                                       | ,                                                                                                                                   | <u> </u>              | •            |              |              |       |

|                       | POK Output Voltage                                                    | V <sub>BUS</sub> = 5V, I <sub>POK</sub> = 0mA                                                                                       |                       | 3.6          | 4.0          | 4.4          | V     |

| 5011                  |                                                                       | V <sub>BUS</sub> = 15V, I <sub>POK</sub> = 0mA                                                                                      |                       | 3.6          | 4.0          | 4.4          | V     |

| POK                   |                                                                       | V <sub>BUS</sub> = 5V, I <sub>POK</sub> = 100mA                                                                                     | T <sub>A</sub> = 25°C | 3.6          | 3.96         | 4.4          | V     |

|                       |                                                                       | V <sub>BUS</sub> = 15V, I <sub>POK</sub> = 100mA                                                                                    |                       | 3.4          | 3.99         | 4.4          | V     |

| I <sub>LK_POK</sub>   | POK-to-GND Leakage Current                                            | $V_{POK} = 5V$ , $V_{BUS} = 0V$ , $T_A = 2$                                                                                         | 25°C                  |              | 0.01         | 1            | μA    |

| I <sub>POK_VBUS</sub> | POK-to-VBUS Leakage<br>Current                                        | V <sub>POK</sub> = 5V, V <sub>BUS</sub> = 0V, T <sub>A</sub> = 25°C,<br>measured at V <sub>BUS</sub> , no ambient light             |                       |              | 0.05         | 2            | nA    |

| DIGITAL               | SIGNALS (FLAG, EN1, EN2)                                              |                                                                                                                                     |                       | •            |              |              |       |

| V <sub>FLAG_</sub> OH | FLAG Output HIGH Voltage                                              | V <sub>BUS</sub> = 5V, EN2 = HIGH                                                                                                   |                       | 1.6          | 1.81         | 2.0          | V     |

| V <sub>FLAG_OL</sub>  | FLAG Output LOW Voltage                                               | V <sub>BUS</sub> = 5V, EN2 = LOW                                                                                                    |                       |              |              | 0.5          | V     |

| V <sub>IH</sub>       | Logic EN1, EN2, SHDN, HIGH<br>Voltage                                 | V <sub>BUS</sub> = 2.7V to 13.5V                                                                                                    |                       | 1.2          |              |              | V     |

| VIL                   | Logic EN1, EN2, SHDN, LOW Voltage                                     |                                                                                                                                     |                       |              |              | 0.35         | V     |

| I <sub>EN_SHDN</sub>  | EN1, Leakage Current                                                  | VBUS = 5V, OUT, SYS = Float                                                                                                         |                       |              | 4.3          | 7            | μΑ    |

| R <sub>PD</sub>       | EN2, SHDN Leakage Current  EN1, EN2, SHDN Internal Pull-down Resistor |                                                                                                                                     |                       | 5.1<br>1     |              | MΩ           |       |

<sup>6.</sup> KTS1678B is guaranteed to meet performance specifications over the  $-40^{\circ}$ C to  $+85^{\circ}$ C operating temperature range by design, characterization and correlation with statistical process controls.

## Electrical Characteristics (continued)<sup>7</sup>

Unless otherwise noted, the *Min* and *Max* specs are applied over the full operation temperature range of -40°C to +85°C,  $V_{BUS} = 2.7V$  to 13.5V. Typical values are specified at room temperature (25°C) with  $V_{BUS} = 5V$ ,  $I_{VBUS} \le 2A$ , SHDN =  $\overline{EN1}$  = EN2 = LOW, POK = OPEN,  $C_{IN} = 0.1 \mu F$  and  $T_A = 25$ °C.

| Symbol                               | Description                             | Conditions                                                                                               | Min | Тур | Max | Units |  |

|--------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|--|

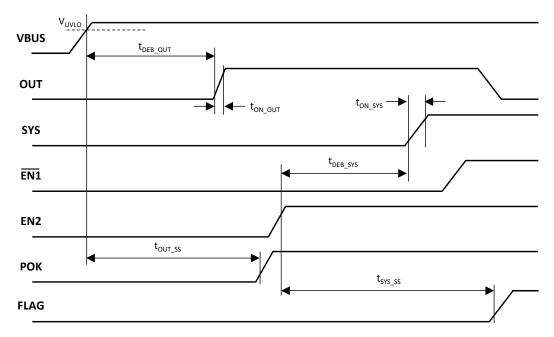

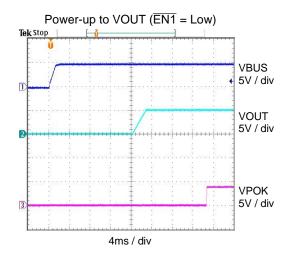

| TIMING CHARACTERISTICS (Figures 1-6) |                                         |                                                                                                          |     |     |     |       |  |

| OUT                                  |                                         |                                                                                                          |     |     |     |       |  |

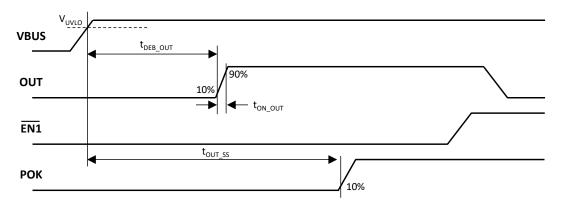

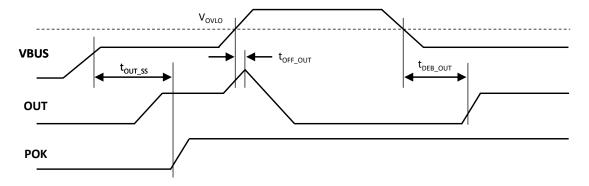

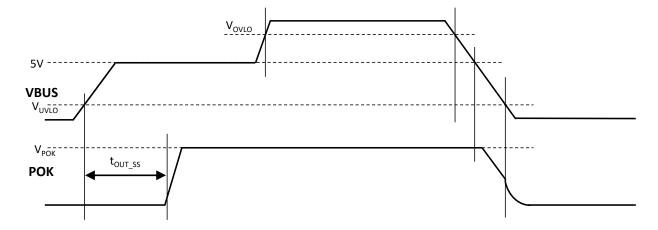

| tout_ss                              | VOUT Soft-Start Time                    | Time from $V_{BUS} = V_{BUS\_UVLO}$ to 10% of POK                                                        |     | 30  |     | ms    |  |

| t <sub>DEB_OUT</sub>                 | OUT Debounce Time                       | Time from V <sub>BUS_UVLO</sub> <v<sub>BUS<vout_ovlo<br>to 10% of V<sub>OUT</sub></vout_ovlo<br></v<sub> |     | 16  |     | ms    |  |

| ton_out                              | OUT Switch Turn-on Time                 | $V_{OUT}$ from 10% of $V_{BUS}$ to 90% of $V_{BUS}$ , $R_L = 100\Omega$ , $C_L = 10\mu F$                |     | 2   |     | ms    |  |

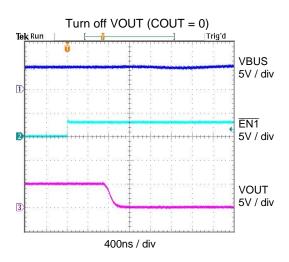

| toff_out                             | OUT Switch Turn-off Time <sup>8</sup>   | $V_{BUS} > V_{OUT\_OVLO}$ to $V_{OUT}$ Stop rising, $R_L = 100\Omega$ , No $C_L$                         |     | 250 |     | ns    |  |

| SYS                                  |                                         |                                                                                                          |     |     |     |       |  |

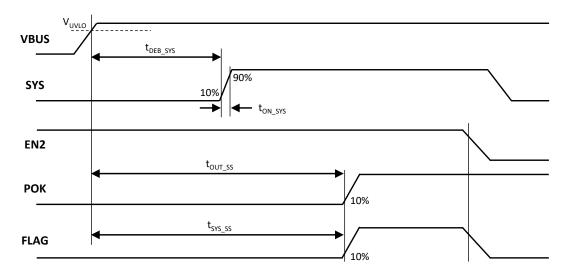

| tsys_ss                              | VSYS Soft-Start Time                    | Time from $V_{BUS} = V_{BUS\_UVLO}$ to 10% of FLAG                                                       |     | 30  |     | ms    |  |

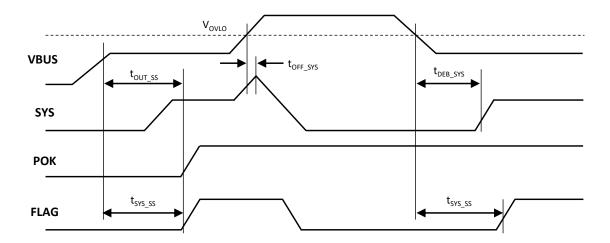

| t <sub>DEB_SYS</sub>                 | SYS Debounce Time                       | Time from V <sub>BUS_UVLO</sub> <v<sub>BUS<vout_ovlo<br>to 10% of V<sub>S</sub>YS</vout_ovlo<br></v<sub> |     | 16  |     | ms    |  |

| ton_sys                              | SYS Switch Turn-on Time                 | $V_{SYS}$ from 10% of $V_{BUS}$ to 90% of $V_{BUS}$ , $R_L = 100\Omega$ , $C_L = 10\mu F$                |     | 2.5 |     | ms    |  |

| toff_sys                             | SYS Switch Turn-off Time <sup>8</sup>   | $V_{BUS} > V_{SYS\_OVLO}$ to $V_{SYS}$ Stop rising, $R_L = 100\Omega$ , No $C_L$                         |     | 400 |     | ns    |  |

| THERMA                               | L SHUTDOWN <sup>8</sup>                 |                                                                                                          |     |     |     |       |  |

|                                      | IC Junction Thermal Shutdown            |                                                                                                          |     | 150 |     | °C    |  |

| t <sub>Ј_ТН</sub>                    | IC Junction Thermal Shutdown Hysteresis |                                                                                                          |     | 20  |     | °C    |  |

| ESD PRO                              | OTECTION <sup>8</sup>                   |                                                                                                          |     |     |     |       |  |

|                                      | Human Body Model (HBM)                  | All pins                                                                                                 |     | ±2  |     | kV    |  |

| $V_{\text{ESD}}$                     | IEC61000-4-2 Contact<br>Discharge       | VBUS Pin                                                                                                 |     | ±8  |     | kV    |  |

|                                      | IEC61000-4-2 Air Discharge              | VBUS Pin                                                                                                 |     | ±15 |     | kV    |  |

August 2020 - Revision 04d Page 5 Company Confidential

<sup>7.</sup> KTS1678B is guaranteed to meet performance specifications over the -40°C to +85°C operating temperature range by design, characterization and correlation with statistical process controls.

<sup>8.</sup> Guaranteed by characterization and design

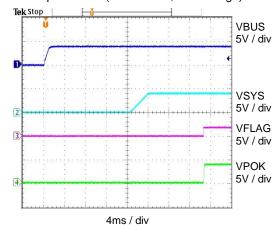

## **Timing Diagrams**

#### **VBUS to OUT**

Figure 1. VBUS to OUT Timing Power Up/Down and Normal Operation

Figure 2. VBUS to OUT Timing OVLO Operation (EN1 = LOW)

Figure 3. POK Always ON Timing ( $\overline{EN1} = X$ , EN2 = X, SHDN = LOW)

August 2020 - Revision 04d Page 6 Company Confidential

#### **VBUS to SYS**

Figure 4. VBUS to SYS Timing Power Up/Down and Normal Operation

Figure 5. VBUS to SYS Timing OVLO Operation (EN2 = HIGH)

August 2020 - Revision 04d Page 7 Company Confidential

Figure 6. ON to OFF Timing Normal Operation (SHDN = LOW)

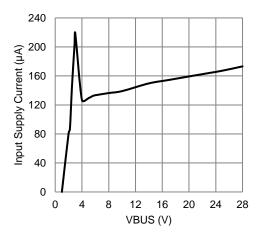

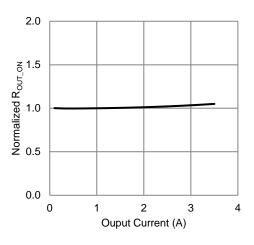

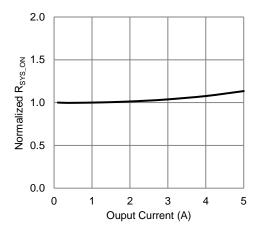

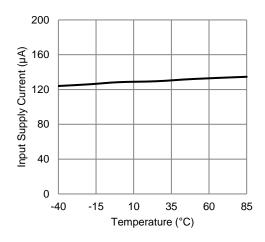

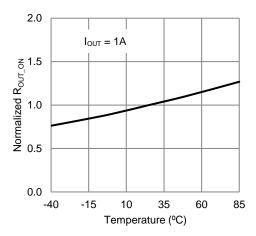

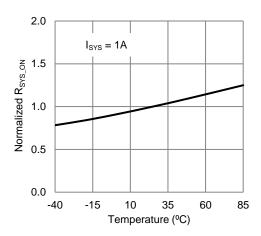

## **Typical Characteristics**

$V_{\text{BUS}} = 5V, \ C_{\text{VBUS}} = 0.1 \mu\text{F}, \ C_{\text{OUT}} = 1 \mu\text{F}, \ C_{\text{SYS}} = 10 \mu\text{F}, \ C_{\text{POK}} = 4.7 \mu\text{F}, \ T_{\text{A}} = 25^{\circ}\text{C} \ unless \ otherwise \ specified.$

Input Supply Current vs. VBUS Voltage (No Load)

Normalized Rout\_on vs Output Current

Normalized R<sub>SYS\_ON</sub> vs Output Current

Input Supply Current vs. Temperature

Normalized Rout\_on vs. Temperature

Normalized  $R_{\text{SYS\_ON}}\,\text{vs.}$  Temperature

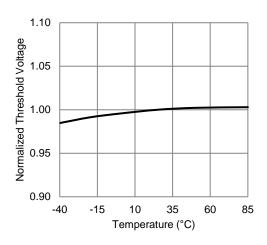

# **Typical Characteristics (continued)**

$V_{BUS} = 5V$ ,  $C_{VBUS} = 0.1 \mu F$ ,  $C_{OUT} = 1 \mu F$ ,  $C_{SYS} = 10 \mu F$ ,  $C_{POK} = 4.7 \mu F$ ,  $T_A = 25 ^{\circ} C$  unless otherwise specified.

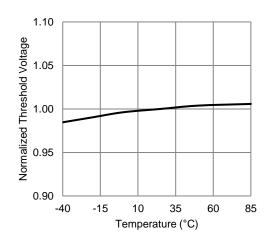

#### Normalized VOUT OVLO vs Temperature

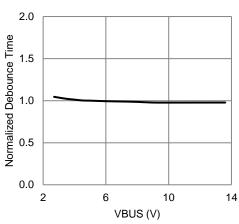

#### Normalized Debounce Time vs. VBUS

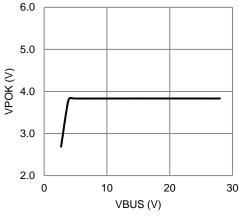

VPOK vs. VBUS

#### Normalized VSYS OVLO Threshold vs Temperature

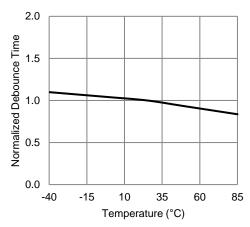

#### Normalized Debounce Time vs. Temperature

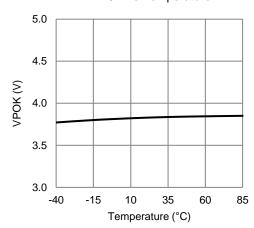

VPOK vs Temperature

# **Typical Characteristics (continued)**

$V_{BUS} = 5V$ ,  $C_{VBUS} = 0.1 \mu F$ ,  $C_{OUT} = 1 \mu F$ ,  $C_{SYS} = 10 \mu F$ ,  $C_{POK} = 4.7 \mu F$ ,  $T_A = 25 ^{\circ}C$  unless otherwise specified.

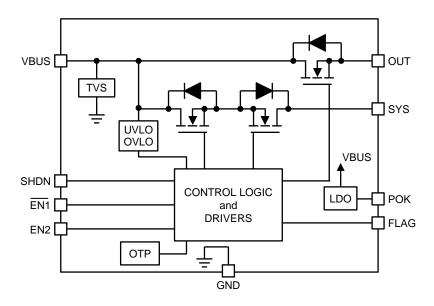

## **Functional Block Diagram**

### **Functional Description**

The KTS1678B features two low resistance power switches configured as single input, dual output, change-over switch. The input to both switches is protected against VBUS surge voltages of up to ±100V, and is also protected against over-voltage, with preset trip points on both the VBUS to OUT and VBUS to SYS paths, providing protection to downstream components from abnormal input conditions.

The main switch (VBUS to OUT) features a unidirectional active–LOW enabled 3.5A rated MOSFET, with an OVP trip point of 13.9V ±400mV. The secondary switch (VBUS to SYS) is an active-HIGH enabled, reverse-blocking 6.0A rated MOSFET, with an OVP trip point of 5.25V ±250mV. The input to both switches is rated up to a maximum of 28V and includes a 15ms debounce time, ensuring that the input VBUS input is stable.

When VBUS is greater than the UVLO of typically 2.7V, the POK LDO provides an "always ON" power source, regulated to typically 4V, regardless of the status of OVLO,  $\overline{\text{EN1}}$  and EN2, to power downstream components permitting operation without an installed battery. The POK LDO is capable of supplying up to 100mA of output current.

The KTS1678B also features an active-HIGH shutdown pin (SHDN) to conserve power, plus over-temperature thermal protection circuitry with hysteresis.

An active HIGH, CMOS FLAG is asserted whenever the SYS switch is active and is in a normal operating mode. The FLAG is deasserted when the SYS switch is OFF due to either EN2 = LOW, VBUS is in UVLO or OVLO, thermal shutdown or SHDN = HIGH.

The truth table for KTS1678B is shown in Table 1 below.

Table 1. KTS1678B Truth Table

| SHDN | (OUT) | EN2 (SYS) | OUT SW | SYS SW | FLAG | POK |

|------|-------|-----------|--------|--------|------|-----|

| 0    | 0     | 0         | ON     | OFF    | LOW  | ON  |

| 0    | 1     | 0         | OFF    | OFF    | LOW  | ON  |

| 0    | 0     | 1         | ON     | ON     | HIGH | ON  |

| 0    | 1     | 1         | OFF    | ON     | HIGH | ON  |

| 1    | x     | х         | OFF    | OFF    | LOW  | OFF |

X = Don't Care

### **Applications Information**

#### **Input Capacitor**

A  $0.1\mu F$  capacitor is typically recommended for  $C_{VBUS}$ .  $C_{VBUS}$  should be located as close to the device VBUS pin as practically possible. 50V rated capacitors are generally good for most OVP applications to support any surge transient voltage.

#### **Output Capacitors**

The soft-start function provides a slow turn-on that allows the KTS1678B to charge large  $C_{SYS}/C_{OUT}$  output capacitors with minimum in-rush current. It is recommended to bypass SYS/OUT/POK outputs with a 1µF minimum ceramic capacitor.

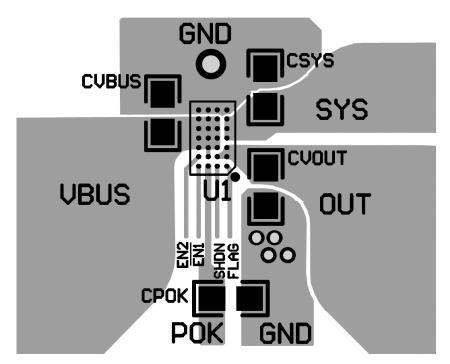

#### **Recommended PCB Layout**

Figure 7. Recommended PCB Layout