# L6985F

Datasheet - production data

# 38 V, 500 mA synchronous step-down switching regulator with 30 µA quiescent current

## Features

- 0.5 A DC output current

- 4 V to 38 V operating input voltage

- Low consumption mode or low noise mode

- 30 μA I<sub>Q</sub> at light-load (LCM V<sub>OUT</sub> = 3.3 V)

- 8 μA <sub>IQ-SHTDWN</sub>

- Output voltage adjustable from 0.85 V to V<sub>IN</sub>

- Adjustable f<sub>SW</sub> (250 kHz 2 MHz)

- Embedded output voltage supervisor

- Synchronization

- Adjustable soft-start time

- Internal current limiting

- Overvoltage protection

- Output voltage sequencing

- Peak current mode architecture

- R<sub>DSON HS</sub> = 360 mΩ, R<sub>DSON LS</sub> = 150 mΩ

- Thermal shutdown

## Applications

- Designed for 12 V and 24 V buses

- Programmable logic controllers (PLCs)

- Decentralized intelligent nodes

- Sensors and low noise applications (LNM)

# Description

The L6985F is a step-down monolithic switching regulator able to deliver up to 0.5 A DC. The output voltage adjustability ranges from 0.85V to VIN. Thanks to the P-channel MOSFET high-side power element, the device features 100% of the duty cycle operation. The wide input voltage range meets the specification for the 5 V, 12 V and 24 V power supplies. The "Low Consumption Mode" (LCM) is designed for applications active during the idle mode, so it maximizes the efficiency at the light-load with the controlled output voltage ripple. The "Low Noise Mode" (LNM) makes the switching frequency constant overload current range, meeting the low noise application specification. The output voltage supervisor manages the reset phase for any digital load (µC, FPGA). The RST open collector output can also implement output voltage sequencing during the power-up phase. The synchronous rectification, designed for high efficiency at the medium - heavy load, and the high switching frequency capability make the size of the application compact. Pulse-by-pulse current sensing on both power elements implements effective constant current protection.

This is information on a product in full production.

# Contents

| 1 | Appl | ication schematic                  |

|---|------|------------------------------------|

| 2 | Pins | settings                           |

|   | 2.1  | Pin connection                     |

|   | 2.2  | Pin description                    |

|   | 2.3  | Maximum ratings                    |

|   | 2.4  | Thermal data                       |

|   | 2.5  | ESD protection                     |

| 3 | Elec | trical characteristics8            |

| 4 | Fund | ctional description                |

|   | 4.1  | Power supply and voltage reference |

|   |      | Switchover feature                 |

|   | 4.2  | Voltages monitor                   |

|   | 4.3  | Soft-start and inhibit 14          |

|   |      | 4.3.1 Ratiometric startup          |

|   |      | 4.3.2 Output voltage sequencing    |

|   | 4.4  | Error amplifier                    |

|   | 4.5  | Light-load operation 23            |

|   |      | 4.5.1 Low noise mode (LNM)         |

|   |      | 4.5.2 Low consumption mode (LCM)   |

|   | 4.6  | Switchover feature                 |

|   |      | 4.6.1 LCM                          |

|   |      | 4.6.2 LNM                          |

|   | 4.7  | Overcurrent protection             |

|   |      | OCP and switchover feature         |

|   | 4.8  | Overvoltage protection             |

|   | 4.9  | Thermal shutdown                   |

|   |      |                                    |

| 5  | Closi  | ng the loop                                             |

|----|--------|---------------------------------------------------------|

|    | 5.1    | G <sub>CO</sub> (s) control to output transfer function |

|    | 5.2    | Error amplifier compensation network                    |

|    | 5.3    | Voltage divider                                         |

|    | 5.4    | Total loop gain                                         |

|    | 5.5    | Compensation network design 42                          |

| 6  | Appli  | cation notes                                            |

|    | 6.1    | Output voltage adjustment                               |

|    | 6.2    | Switching frequency                                     |

|    | 6.3    | MLF pin                                                 |

|    | 6.4    | Voltage supervisor                                      |

|    | 6.5    | Synchronization (LNM)                                   |

|    | 6.6    | Design of the power components 50                       |

|    |        | 6.6.1 Input capacitor selection                         |

|    |        | 6.6.2 Inductor selection                                |

|    |        | 6.6.3 Output capacitor selection                        |

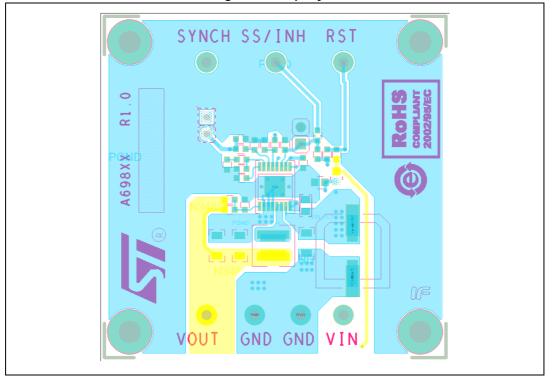

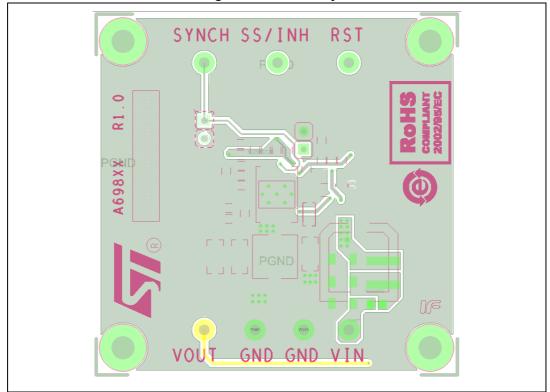

| 7  | Appli  | cation board                                            |

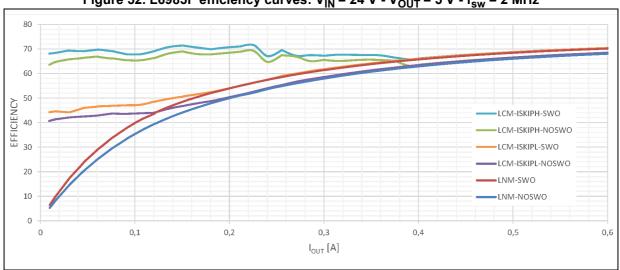

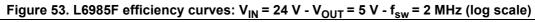

| 8  | Effici | ency curves                                             |

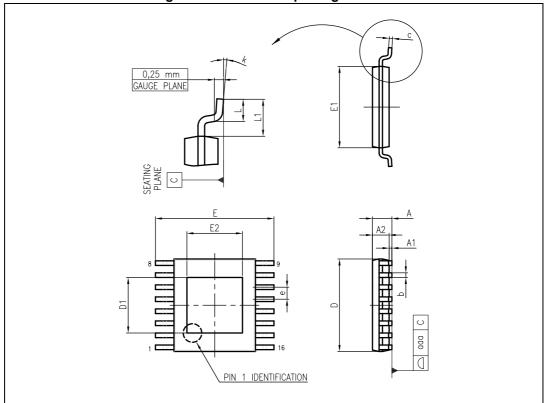

| 9  | Packa  | age information                                         |

|    | 9.1    | HTSSOP16 package information 62                         |

| 10 | Order  | r codes                                                 |

| 11 | Revis  | sion history                                            |

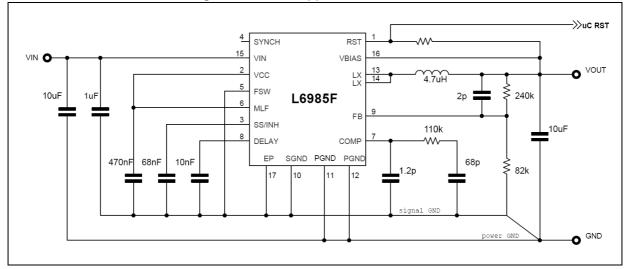

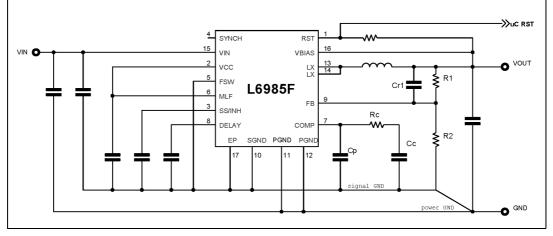

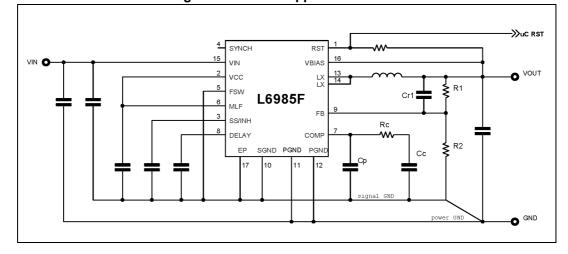

# 1 Application schematic

# 2 Pin settings

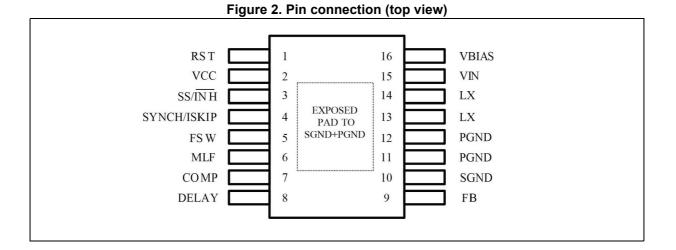

# 2.1 Pin connection

# 2.2 Pin description

#### Table 1. Pin description

| No. | Pin            | Description                                                                                                                                                                                                                           |

|-----|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | RST            | The RST open collector output is driven low when the output voltage is out of regulation. The RST is released after an adjustable time DELAY once the output voltage is over the active delay threshold.                              |

| 2   | VCC            | Connect a ceramic capacitor ( $\geq$ 470 nF) to filter internal voltage reference. This pin supplies the embedded analog circuitry.                                                                                                   |

| 3   | SS/INH         | An open collector stage can disable the device clamping this pin to GND ( $\overline{\text{INH}}$ mode). An internal current generator (4 $\mu$ A typ.) charges the external capacitor to implement the soft-start.                   |

| 4   | SYNCH/<br>ISKP | The pin features Master / Slave synchronization in LNM (see Section 6.5 on page 45) and skip current level selection in LCM (see Section 4.5.2 on page 24).                                                                           |

| 5   | FSW            | A pull-up resistor (E24 series only) to VCC or pull-down to GND selects the switching frequency. Pinstrapping is active only before the soft-start phase to minimize the IC consumption.                                              |

| 6   | MLF            | A pull-up resistor (E24 series only) to VCC or pull-down to GND selects the low noise mode/low consumption mode and the active RST threshold. Pinstrapping is active only before the soft-start phase to minimize the IC consumption. |

| 7   | COMP           | Output of the error amplifier. The designed compensation network is connected at this pin.                                                                                                                                            |

| 8   | DELAY          | An external capacitor connected at this pin sets the time DELAY to assert the rising edge of the RST o. c. after the output voltage is over the reset threshold. If this pin is left floating, RST is like a Power Good.              |

| 9   | FB             | Inverting input of the error amplifier                                                                                                                                                                                                |

| 10  | SGND           | Signal GND                                                                                                                                                                                                                            |

| 11  | PGND           | Power GND                                                                                                                                                                                                                             |

| No. | Pin   | Description                                                                                                                                                                                                       |  |  |  |  |

|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 12  | PGND  | Power GND                                                                                                                                                                                                         |  |  |  |  |

| 13  | LX    | Switching node                                                                                                                                                                                                    |  |  |  |  |

| 14  | LX    | Switching node                                                                                                                                                                                                    |  |  |  |  |

| 15  | VIN   | DC input voltage                                                                                                                                                                                                  |  |  |  |  |

| 16  | VBIAS | Typically connected to the regulated output voltage. An external voltage reference can be used to supply a part of the analog circuitry to increase the efficiency at the light-load. Connect to GND if not used. |  |  |  |  |

| -   | E. p. | Exposed pad must be connected to SGND, PGND.                                                                                                                                                                      |  |  |  |  |

#### Table 1. Pin description (continued)

# 2.3 Maximum ratings

Stressing the device above the rating listed in *Table 2: Absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

| Symbol                            | Description                          | Min.       | Max.                                | Unit |

|-----------------------------------|--------------------------------------|------------|-------------------------------------|------|

| V <sub>IN</sub>                   |                                      | -0.3       | 40                                  | V    |

| DELAY                             |                                      | -0.3       | V <sub>CC</sub> + 0.3               | V    |

| PGND                              |                                      | SGND - 0.3 | SGND + 0.3                          | V    |

| SGND                              |                                      |            |                                     | V    |

| V <sub>CC</sub>                   |                                      | -0.3       | (V <sub>IN</sub> + 0.3) or (max. 4) | V    |

| SS / INH                          |                                      | -0.3       | V <sub>IN</sub> + 0.3               | V    |

| MLF                               | See Table 1                          | -0.3       | V <sub>CC</sub> + 0.3               | V    |

| COMP                              | See Table T                          | -0.3       | V <sub>CC</sub> + 0.3               | V    |

| VOUT                              |                                      | -0.3       | 10                                  | V    |

| FSW                               |                                      | -0.3       | V <sub>CC</sub> + 0.3               | V    |

| SYNCH                             |                                      | -0.3       | V <sub>IN</sub> + 0.3               | V    |

| V <sub>BIAS</sub>                 |                                      | -0.3       | (V <sub>IN</sub> + 0.3) or (max. 6) | V    |

| RST                               |                                      | -0.3       | V <sub>IN</sub> + 0.3               | V    |

| LX                                |                                      | -0.3       | V <sub>IN</sub> + 0.3               | V    |

| ТJ                                | Operating temperature range          | -40        | 150                                 | °C   |

| T <sub>STG</sub>                  | Storage temperature range            |            | -65 to 150                          | °C   |

| T <sub>LEAD</sub>                 | Lead temperature (soldering 10 sec.) |            | 260                                 | °C   |

| I <sub>HS</sub> , I <sub>LS</sub> | High-side / low-side switch current  |            | 2                                   | А    |

| Table 2. | Absolute   | maximum | ratings |

|----------|------------|---------|---------|

|          | / 10001010 |         |         |

DocID027836 Rev 2

# 2.4 Thermal data

| Symbol             | Parameter                                                                                                                     | Value | Unit |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------|-------|------|

| R <sub>th JA</sub> | Thermal resistance junction ambient (device soldered on the STMicroelectronics $^{\mbox{\scriptsize R}}$ demonstration board) | 40    | °C/W |

| R <sub>th JC</sub> | Thermal resistance junction to exposed pad for board design (not suggested to estimate TJ from power losses).                 | 5     | C/W  |

#### Table 3. Thermal data

# 2.5 ESD protection

| Symbol | Test condition | Value | Unit |

|--------|----------------|-------|------|

|        | НВМ            | 2     | kV   |

| ESD    | MM             | 200   | V    |

|        | CDM            | 500   | V    |

#### Table 4. ESD protection

# **3** Electrical characteristics

$T_J$  = 25 °C,  $V_{IN}$  = 12 V unless otherwise specified.

| Symbol               | Parameter                                             | Test condition                                                   | Note | Min.                                   | Тур. | Max. | Unit |

|----------------------|-------------------------------------------------------|------------------------------------------------------------------|------|----------------------------------------|------|------|------|

| V <sub>IN</sub>      | Operating input voltage range                         |                                                                  |      | 4                                      |      | 38   |      |

| V <sub>INH</sub>     | V <sub>CC</sub> UVLO rising threshold                 |                                                                  |      | 2.7                                    |      | 3.5  | V    |

| V <sub>INL</sub>     | V <sub>CC</sub> UVLO falling threshold                |                                                                  |      | 2.4                                    |      | 3.5  |      |

|                      |                                                       | Duty cycle < 20%                                                 |      | 0.8                                    |      |      |      |

| I <sub>PK</sub>      | Peak current limit                                    | Duty cycle = 100%<br>closed loop operation                       |      | 0.65                                   |      |      | A    |

| I <sub>VY</sub>      | Valley current limit                                  |                                                                  |      | 0.9                                    |      |      |      |

| I                    | Ckin ourront limit                                    | LCM, V <sub>SYNCH</sub> = GND                                    | (1)  | 0.15                                   | 0.35 | 0.5  |      |

| I <sub>SKIP</sub>    | Skip current limit                                    | LCM, V <sub>SYNCH</sub> = VCC                                    | (2)  |                                        | 0.1  |      |      |

| I <sub>VY_SNK</sub>  | Reverse current limit                                 | LNM or V <sub>OUT</sub> overvoltage                              |      | 0.5                                    | 1    | 2    |      |

| R <sub>DSON HS</sub> | High-side RDSON                                       | I <sub>SW</sub> = 0.5 A                                          |      |                                        | 0.36 | 0.72 | 0    |

| R <sub>DSON LS</sub> | Low-side RDSON                                        | I <sub>SW</sub> = 0.5 A                                          |      |                                        | 0.15 | 0.30 | Ω    |

| f <sub>SW</sub>      | Selected switching<br>frequency                       | FSW pinstrapping before SS                                       |      | See Table 6: f <sub>SW</sub> selection |      |      |      |

| I <sub>FSW</sub>     | FSW biasing current                                   | SS ended                                                         |      |                                        | 0    | 500  | nA   |

| LCM/LNM              | Low noise mode /<br>Low consumption mode<br>selection | MLF pinstrapping before SS                                       |      | See Table 7 on page 11                 |      |      |      |

| I <sub>MLF</sub>     | MLF biasing current                                   | SS ended                                                         |      |                                        | 0    | 500  | nA   |

| D                    | Duty cycle                                            |                                                                  | (2)  | 0                                      |      | 100  | %    |

| T <sub>ON MIN</sub>  | Minimum On time                                       |                                                                  |      |                                        | 80   |      | ns   |

| VCC regul            | ator                                                  |                                                                  |      |                                        |      |      |      |

| V                    |                                                       | V <sub>BIAS</sub> = GND (no switchover)                          |      | 2.9                                    | 3.3  | 3.6  |      |

| V <sub>CC</sub>      | LDO output voltage                                    | V <sub>BIAS</sub> = 5 V (switchover)                             |      | 2.9                                    | 3.3  | 3.6  |      |

| SWO                  | V <sub>BIAS</sub> threshold                           | Switch internal supply from $V_{\text{IN}}$ to $V_{\text{BIAS}}$ |      | 2.85                                   |      | 3.2  | V    |

| 300                  | (3 V< V <sub>BIAS</sub> < 5.5 V)                      | Switch internal supply from $V_{\text{BIAS}}$ to $V_{\text{IN}}$ |      | 2.78                                   |      | 3.15 |      |

#### Table 5. Electrical characteristics

| Symbol                 | Parameter                                   | Test condition                                                                              | Note | Min.  | Тур. | Max.  | Unit   |

|------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------|------|-------|------|-------|--------|

| Power con              | sumption                                    |                                                                                             |      |       |      |       |        |

| I <sub>SHTDWN</sub>    | Shutdown current from VIN                   | V <sub>SS/INH</sub> = GND                                                                   |      | 4     | 8    | 15    | μA     |

|                        |                                             | <b>LCM - SWO</b><br>$V_{REF} < V_{FB} < V_{OVP}$ (SLEEP)<br>$V_{BIAS}$ = 3.3 V              | (3)  | 4     | 10   | 15    |        |

|                        |                                             | <b>LCM - NO SWO</b><br>$V_{REF} < V_{FB} < V_{OVP}$ (SLEEP)<br>$V_{BIAS}$ = GND             | (3)  | 35    | 70   | 120   | μA     |

| I <sub>Q OPVIN</sub>   | Quiescent current from V <sub>IN</sub>      | LNM - SWO<br>V <sub>FB</sub> = GND (NO SLEEP)<br>V <sub>BIAS</sub> = 3.3 V                  |      | 0.5   | 1.5  | 5     |        |

|                        |                                             | <b>LNM - NO SWO</b><br>V <sub>FB</sub> = GND (NO SLEEP)<br>V <sub>BIAS</sub> = GND          |      | 2     | 2.8  | 6     | mA     |

| I <sub>Q OPVBIAS</sub> | Quiescent current from<br>V <sub>BIAS</sub> | LCM - SWO<br>$V_{REF} < V_{FB} < V_{OVP}$ (SLEEP)<br>$V_{BIAS} = 3.3 V$                     | (3)  | 25    | 50   | 115   | μΑ     |

|                        |                                             | LNM - SWO<br>V <sub>FB</sub> = GND (NO SLEEP)<br>V <sub>BIAS</sub> = 3.3 V                  |      | 0.5   | 1.2  | 5     | mA     |

| Soft-start             |                                             |                                                                                             |      |       |      |       |        |

| V <sub>INH</sub>       | VSS threshold                               | SS rising                                                                                   |      | 200   | 460  | 700   | mV     |

| V <sub>INH HYST</sub>  | VSS hysteresis                              |                                                                                             |      |       | 100  | 140   | IIIV   |

| I <sub>SS CH</sub>     | C <sub>SS</sub> charging current            | $V_{SS} < V_{INH} OR$<br>t < T <sub>SS SETUP</sub> OR<br>V <sub>EA+</sub> > V <sub>FB</sub> | (2)  |       | 1    |       | μΑ     |

|                        |                                             | t > T <sub>SS SETUP</sub> AND<br>V <sub>EA+</sub> < V <sub>FB</sub>                         | (2)  |       | 4    |       | n ** * |

| V <sub>SS START</sub>  | Start of internal error amplifier ramp      |                                                                                             |      | 0.995 | 1.1  | 1.150 | V      |

| SS <sub>GAIN</sub>     | SS/INH to internal error amplifier gain     |                                                                                             |      |       | 3    |       |        |

| Error amp              | lifier                                      |                                                                                             |      |       |      |       |        |

| V <sub>OUT</sub>       | Voltage feedback                            |                                                                                             |      | 0.841 | 0.85 | 0.859 | V      |

| I <sub>VOUT</sub>      | VOUT biasing current                        |                                                                                             |      |       | 50   | 500   | nA     |

| A <sub>V</sub>         | Error amplifier gain                        |                                                                                             | (2)  |       | 100  |       | dB     |

| v                      |                                             |                                                                                             |      |       |      |       |        |

| Table 5. Electrical characteristics (continued) |

|-------------------------------------------------|

|-------------------------------------------------|

| Symbol                            | Parameter                                                                         | Test condition                                                                                | Note | Min.  | Тур.  | Max.     | Unit  |

|-----------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------|-------|-------|----------|-------|

| Inner curre                       | ent loop                                                                          | L                                                                                             |      |       |       |          |       |

| gcs                               | Current sense<br>transconductance (V <sub>COMP</sub> to<br>inductor current gain) | I <sub>PK</sub> = 0.5 A                                                                       | (2)  |       | 1.67  |          | A/V   |

| V <sub>PP</sub> ⋅ g <sub>CS</sub> | Slope compensation                                                                |                                                                                               | (4)  | 0.2   | 0.3   | 0.4      | Α     |

| Overvoltaç                        | ge protection                                                                     |                                                                                               |      |       |       |          |       |

| V <sub>OVP</sub>                  | Overvoltage trip<br>(V <sub>OVP</sub> /V <sub>REF</sub> )                         |                                                                                               |      | 1.15  | 1.2   | 1.25     |       |

| V <sub>OVP</sub><br>HYST          | Overvoltage hysteresis                                                            |                                                                                               |      | 0.5   | 2     | 5        | %     |

| Synchroni                         | zation (fan out: 6 slave device                                                   | es typ.)                                                                                      |      |       |       |          |       |

| f <sub>SYN MIN</sub>              | Synchronization frequency                                                         | LNM; f <sub>SW</sub> = VCC                                                                    |      | 266.5 |       |          | kHz   |

| V <sub>SYN TH</sub>               | SYNCH input threshold                                                             | LNM, SYNCH rising                                                                             |      | 0.70  |       | 1.2      | V     |

| I <sub>SYN</sub>                  | SYNCH pulldown current                                                            | LNM, V <sub>SYN</sub> = 1.2 V                                                                 |      |       | 0.7   |          | mA    |

| V <sub>SYN OUT</sub>              | High level output                                                                 | LNM, 5 mA sinking load                                                                        |      | 1.40  |       |          | V     |

|                                   | Low level output                                                                  | LNM, 0.7 mA sourcing load                                                                     |      |       |       | 0.6      | v     |

| Reset                             |                                                                                   |                                                                                               |      |       |       |          |       |

| V <sub>THR</sub>                  | Selected RST threshold                                                            | MLF pinstrapping before SS                                                                    |      | See   | Table | 7 on pag | ie 11 |

| V <sub>THR HYST</sub>             | RST hysteresis                                                                    |                                                                                               | (2)  |       | 2     |          | %     |

|                                   |                                                                                   | V <sub>IN</sub> > V <sub>INH</sub> AND V <sub>FB</sub> < V <sub>TH</sub><br>4 mA sinking load |      |       |       | 0.4      |       |

| V <sub>RST</sub>                  | RST open collector output                                                         | 2 < V <sub>IN</sub> < V <sub>INH</sub><br>4 mA sinking load                                   |      |       |       | 0.8      | V     |

| Delay                             |                                                                                   |                                                                                               |      |       |       |          |       |

| V <sub>THD</sub>                  | RST open collector released as soon as $V_{DELAY} > V_{THD}$                      | V <sub>FB</sub> > V <sub>THR</sub>                                                            |      | 1.19  | 1.234 | 1.258    | V     |

| I <sub>D CH</sub>                 | C <sub>DELAY</sub> charging current                                               | V <sub>FB</sub> > V <sub>THR</sub>                                                            |      | 1     | 2     | 3        | μA    |

| Thermal sl                        | hutdown                                                                           |                                                                                               |      |       |       |          |       |

| T <sub>SHDWN</sub>                | Thermal shutdown temperature                                                      |                                                                                               | (2)  |       | 165   |          | °C    |

| T <sub>HYS</sub>                  | Thermal shutdown<br>hysteresis                                                    |                                                                                               | (2)  |       | 30    |          | U     |

1. Parameter tested in static condition during the testing phase. Parameter value may change over dynamic application condition.

2. Not tested in production.

3. LCM enables SLEEP mode at the light-load.

4. Measured at  $f_{sw}$  = 250 kHz.

| Symbol          | R <sub>VCC</sub> (E24 series) | R <sub>GND</sub> (E24 series) | Tj  | f <sub>SW</sub> min. | f <sub>SW</sub> typ. | f <sub>SW</sub> max. | Unit |

|-----------------|-------------------------------|-------------------------------|-----|----------------------|----------------------|----------------------|------|

| f <sub>SW</sub> | 0 Ω                           | NC                            |     | 225                  | 250                  | 275                  | kHz  |

|                 | 1.8 kΩ                        | NC                            | (1) |                      | 285                  |                      |      |

|                 | 3.3 kΩ                        | NC                            |     |                      | 330                  |                      |      |

|                 | 5.6 kΩ                        | NC                            |     |                      | 380                  |                      |      |

|                 | 10 kΩ                         | NC                            |     |                      | 435                  |                      |      |

|                 | NC                            | 0 Ω                           |     | 450                  | 500                  | 550                  |      |

|                 | 18 kΩ                         | NC                            | (1) |                      | 575                  |                      |      |

|                 | 33 kΩ                         | NC                            |     |                      | 660                  |                      |      |

|                 | 56 kΩ                         | NC                            |     |                      | 755                  |                      |      |

|                 | NC                            | 1.8 kΩ                        |     |                      | 870                  |                      |      |

|                 | NC                            | 3.3 k $\Omega$                |     | 900                  | 1000                 | 1100                 |      |

|                 | NC                            | 5.6 k $\Omega$                |     |                      | 1150                 |                      |      |

|                 | NC                            | 10 kΩ                         | (1) |                      | 1310                 |                      |      |

|                 | NC                            | 18 kΩ                         |     |                      | 1500 <sup>(2)</sup>  |                      |      |

|                 | NC                            | 33 kΩ                         |     | 1575                 | 1750 <sup>(2)</sup>  | 1925                 |      |

|                 | NC                            | 56 k $\Omega$                 |     | 1800                 | 2000 <sup>(2)</sup>  | 2200                 |      |

$T_J$  = 25 °C,  $V_{IN}$  = 12 V unless otherwise specified.

Table 6. f<sub>SW</sub> selection

1. Not tested in production.

2. No synchronization as slave in LNM.

$T_J$  = 25 °C,  $V_{IN}$  = 12 V unless otherwise specified.

| Symbol           | R <sub>VCC</sub><br>(E24 1%) | R <sub>GND</sub><br>(E24 1%) | Operating<br>mode | V <sub>RST</sub> /V <sub>OUT</sub><br>(tgt. value) | V <sub>RST</sub><br>min. | V <sub>RST</sub><br>typ. | V <sub>RST</sub><br>max. | Unit |

|------------------|------------------------------|------------------------------|-------------------|----------------------------------------------------|--------------------------|--------------------------|--------------------------|------|

| V <sub>RST</sub> | 0 Ω                          | NC                           |                   | 93%                                                | 0.779                    | 0.791                    | 0.802                    |      |

|                  | 8.2 kΩ                       | NC                           | LCM               | 80%                                                | 0.670                    | 0.680                    | 0.690                    |      |

|                  | 18 k $\Omega$                | NC                           |                   | 87%                                                | 0.728                    | 0.740                    | 0.751                    |      |

|                  | 39 kΩ                        | NC                           |                   | 96%                                                | 0.804                    | 0.816                    | 0.828                    | V    |

|                  | NC                           | 0 Ω                          | LNM               | 93%                                                | 0.779                    | 0.791                    | 0.802                    | v    |

|                  | NC                           | 8.2 kΩ                       |                   | 80%                                                | 0.670                    | 0.680                    | 0.690                    |      |

|                  | NC                           | 18 kΩ                        |                   | 87%                                                | 0.728                    | 0.740                    | 0.751                    |      |

|                  | NC                           | 39 kΩ                        |                   | 96%                                                | 0.804                    | 0.816                    | 0.828                    |      |

Table 7. LNM / LCM selection table

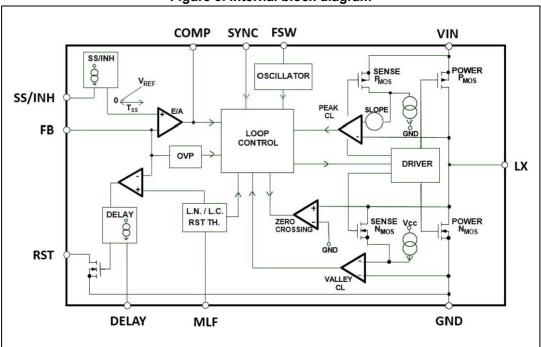

# 4 Functional description

The L6985F device is based on a "peak current mode", constant frequency control. As a consequence, the intersection between the error amplifier output and the sensed inductor current generates the PWM control signal to drive the power switch.

The device features LNM (low noise mode) that is forced PWM control, or LCM (low consumption mode) to increase the efficiency at the light-load.

The main internal blocks shown in the block diagram in *Figure 3* are:

- Embedded power elements. Thanks to the P-channel MOSFET as a high-side switch the device features a low dropout operation

- A fully integrated sawtooth oscillator with adjustable frequency

- A transconductance error amplifier

- The high-side current sense amplifier to sense the inductor current

- A "Pulse Width Modulator" (PWM) comparator and the driving circuitry of the embedded power elements

- The soft-start blocks to ramp the error amplifier reference voltage and so decreases the inrush current at power-up. The SS/INH pin inhibits the device when driven low.

- The switchover capability of the internal regulator to supply a portion of the quiescent current when the V<sub>BIAS</sub> pin is connected to an external output voltage

- The synchronization circuitry to manage a master / slave operation and the synchronization to an external clock

- The current limitation circuit to implement the constant current protection, sensing a pulse-by-pulse high-side / low-side switch current. In case of heavy short-circuit the current protection is fold back to decrease the stress of the external components

- A circuit to implement the thermal protection function

- The OVP circuitry to discharge the output capacitor in case of an overvoltage event

- The MLF pin strapping sets the LNM/LCM mode and the thresholds of the RST comparator

- FSW pinstrapping sets the switching frequency

- The RST open collector output

Figure 3. Internal block diagram

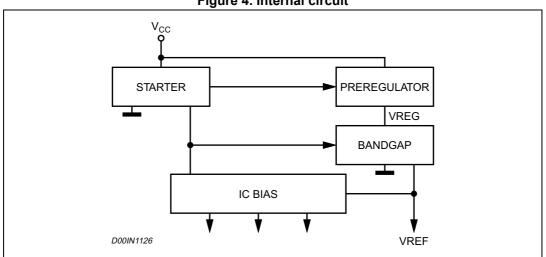

### 4.1 **Power supply and voltage reference**

The internal regulator block consists of a start-up circuit, the voltage pre-regulator that provides the current to all the blocks and the bandgap voltage reference. The starter supplies the startup current when the input voltage goes high and the device is enabled (SS/INH pin over the inhibits threshold).

The pre-regulator block supplies the bandgap cell and the rest of the circuitry with a regulated voltage that has a very low supply voltage noise sensitivity.

#### Switchover feature

The switchover scheme of the pre-regulator block features to derive the main contribution of the supply current for the internal circuitry from an external voltage (3 V <  $V_{BIAS}$  < 5.5 V is typically connected to the regulated output voltage). This helps to decrease the equivalent quiescent current seen at  $V_{IN}$ . (Please refer to *Section 4.6: Switchover feature on page 28*).

## 4.2 Voltages monitor

An internal block continuously senses the V<sub>CC</sub>, V<sub>BIAS</sub> and V<sub>BG</sub>. If the monitored voltages are good, the regulator starts operating. There is also a hysteresis on the V<sub>CC</sub> (UVLO).

Figure 4. Internal circuit

## 4.3 Soft-start and inhibit

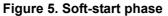

The soft-start and inhibit features are multiplexed on the same pin. An internal current source charges the external soft-start capacitor to implement a voltage ramp on the SS/INH pin. The device is inhibited as long as the SS/INH pin voltage is lower than the V<sub>INH</sub> threshold and the soft-start takes place when the SS/INH pin crosses V<sub>SS START</sub>. (See *Figure 5*).

The internal current generator sources a 1  $\mu$ A typ. current when the voltage of the V<u>CC</u> pin crosses the UVLO threshold. The current increases to 4  $\mu$ A typ. as soon as the SS/INH voltage is higher than the V<sub>INH</sub> threshold. This feature helps to decrease the current consumption in inhibit mode. An external open collector can be used to set the inhibit operation clamping the SS/INH voltage below the V<sub>INH</sub> threshold.

The startup feature minimizes the inrush current and decreases the stress of the power components during the power-up phase. The ramp implemented on the reference of the error amplifier has a gain three times higher (SS<sub>GAIN</sub>) than the external ramp present at the SS/INH pin.

The  $C_{SS}$  is dimensioned accordingly with *Equation 1*:

#### **Equation 1**

$$C_{SS} = SS_{GAIN} \bullet \frac{I_{SSCH} \bullet T_{SS}}{V_{FB}} = 3 \bullet \frac{4\mu A \bullet T_{SS}}{0.85V}$$

where  $T_{SS}$  is the soft-start time,  $I_{SS CH}$  the charging current and  $V_{FB}$  the reference of the error amplifier.

The soft-start block supports the precharged output capacitor.

Figure 6. Soft-start phase with precharged COUT

During the normal operation a new soft-start cycle takes place in case of:

- Thermal shutdown event

- UVLO event

- The device is driven in INH mode

The soft-start capacitor is discharged with a 0.6 mA typ. current capability for 1 msec time max. For complete and proper capacitor discharge in case of fault condition, a maximum  $C_{SS}$  = 67 nF value is suggested.

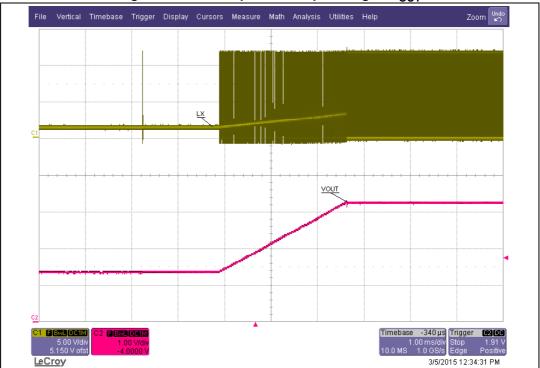

The application example in *Figure* 7 shows how to enable the L6985F and perform the soft-start phase driven by an external voltage step.

Figure 7. Enable the device with external voltage step

The maximum capacitor value has to be limited to guarantee the device can discharge it in case of a thermal shutdown and UVLO events (see Section 4.3.1), so restart the switching activity ramping the error amplifier reference voltage.

#### **Equation 2**

$$C_{SS} < \frac{-1 \text{ msec}}{R_{SS\_EQ} \cdot \ln\left(1 - \frac{V_{SS\_FINAL} - 0.9 \text{ V}}{600 \text{ }\mu\text{A} - R_{SS\_EQ}}\right)}$$

where:

#### **Equation 3**

$$R_{SS\_EQ} = \frac{R_{UP} \cdot R_{DWN}}{R_{UP} + R_{DWN}} \qquad V_{SS\_FINAL} = (V_{STEP} - V_{DIODE}) \cdot \frac{R_{DWN}}{R_{UP} + R_{DWN}}$$

The optional diode prevents to disable the device if the external source drops to ground.

$R_{UP}$  value is selected in order to make the capacitor charge at first approximation independent from the internal current generator (4  $\mu$ A typ. current capability, see *Table 5 on page 8*), so:

#### **Equation 4**

$$\frac{V_{STEP} - V_{DIODE} - V_{SS END}}{R_{UP}} \gg I_{SS CHARGE} \equiv 4 \mu A$$

where:

#### **Equation 5**

$$V_{SS END} = V_{SS START} + \frac{V_{FB}}{SS_{GAIN}}$$

represents the SS/INH voltage correspondent to the end of the ramp on the error amplifier (see *Figure 5*); refer to *Table 5* for  $V_{SS START}$ ,  $V_{FB}$  and  $SS_{GAIN}$  parameters.

As a consequence the voltage across the soft-start capacitor can be written as:

#### **Equation 6**

$$v_{SS}(t) = V_{SS\_FINAL} \cdot \frac{1}{1 - e^{-\frac{t}{C_{SS} \cdot R_{SS\_EQ}}}}$$

$R_{SS\_DOWN}$  is selected to guarantee the device stays in inhibit mode when the internal generator sources 1  $\mu A$  typ. out of the SS/INH pin and  $V_{STEP}$  is not present:

#### **Equation 7**

$$R_{DWN} \cdot I_{SS \text{ INHIBIT}} \equiv R_{DWN} \cdot 1 \ \mu A \ll V_{INH} \equiv 200 \text{ mV}$$

SO:

**Equation 8**

$R_{DWN}$  < 100 k $\Omega$

DocID027836 Rev 2

$\mathsf{R}_{\mathsf{UP}}$  and  $\mathsf{R}_{\mathsf{DWN}}$  are selected to guarantee:

#### **Equation 9**

$$V_{SS FINAL} \cong 2 V > V_{SS END}$$

The time to ramp the internal voltage reference can be calculated from *Equation 10*:

#### **Equation 10**

$$\mathsf{T}_{\mathsf{SS}} = \mathsf{C}_{\mathsf{SS}} \cdot \mathsf{R}_{\mathsf{SS}} \mathsf{_{EQ}} \cdot \mathsf{In} \left( \frac{\mathsf{V}_{\mathsf{SS}} \mathsf{_{\mathsf{FINAL}}} - \mathsf{V}_{\mathsf{SS}} \mathsf{_{\mathsf{START}}}}{\mathsf{V}_{\mathsf{SS}} \mathsf{_{\mathsf{FINAL}}} - \mathsf{V}_{\mathsf{SS}} \mathsf{_{\mathsf{START}}}} \right)$$

that is the equivalent soft-start time to ramp the output voltage.

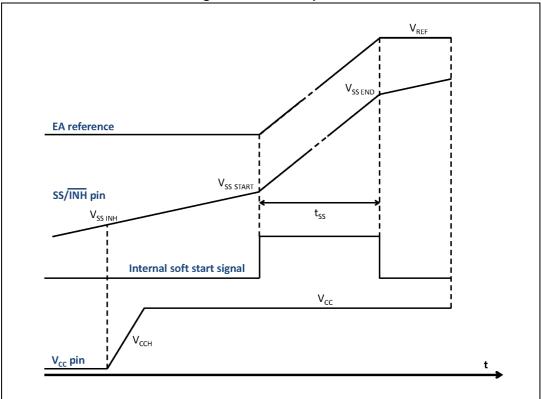

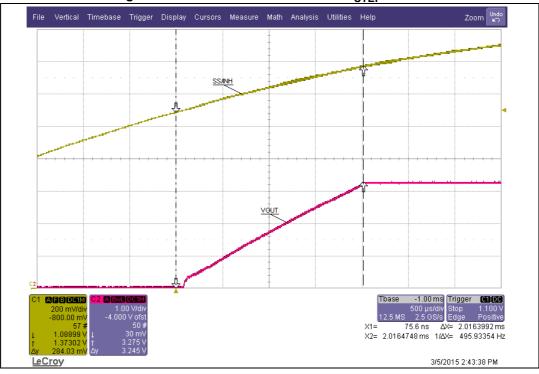

*Figure 8* shows the soft-start phase with the following component selection:  $R_{UP}$  = 180 kΩ,  $R_{DWN}$  = 33 kΩ,  $C_{SS}$  = 200 nF, the 1N4148 is a small signal diode and  $V_{STEP}$  = 13 V.

The circuit in *Figure* 7 introduces a time delay between  $V_{STEP}$  and the switching activity that can be calculated as:

#### **Equation 11**

$$T_{SS \text{ DELAY}} = C_{SS} \cdot R_{SS} \text{ EQ} \cdot ln \left( \frac{V_{SS} \text{ FINAL}}{V_{SS} \text{ FINAL} - V_{SS \text{ START}}} \right)$$

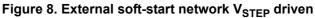

*Figure 9* shows how the device discharges the soft-start capacitor after an UVLO or thermal shutdown event in order to restart the switching activity ramping the error amplifier reference voltage.

Figure 9. External soft-start after UVLO or thermal shutdown

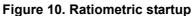

### 4.3.1 Ratiometric startup

The ratiometric startup is implemented sharing the same soft-start capacitor for a set of the L6985F devices.

As a consequence all the internal current generators charge in parallel the external capacitor. The capacitor value is dimensioned accordingly with *Equation 12*:

#### **Equation 12**

$$C_{SS} = n_{L6985F} \bullet SS_{GAIN} \bullet \frac{I_{SSCH} \bullet T_{SS}}{V_{FB}} = n_{L6985F} \bullet 3 \bullet \frac{4\mu A \bullet T_{SS}}{0.85V}$$

where  $n_{L6985F}$  represents the number of devices connected in parallel.

For better tracking of the different output voltages the synchronization of the set of regulators is suggested.

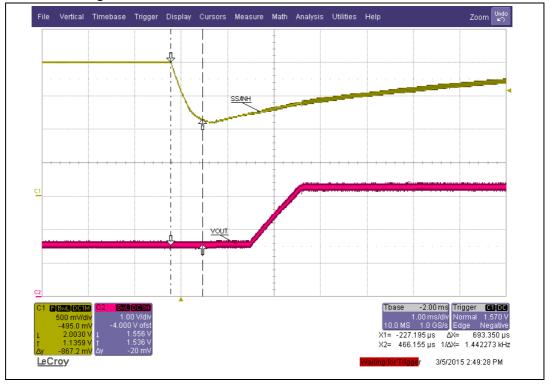

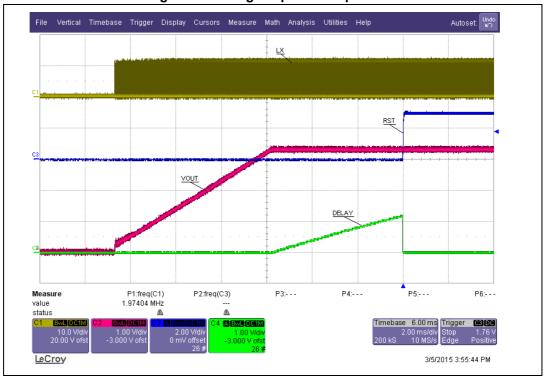

Figure 11. Ratiometric startup operation

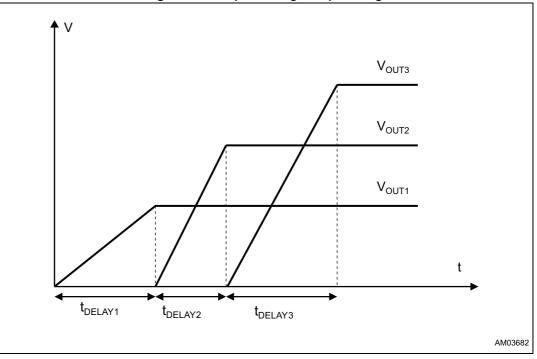

The L6985F device implements sequencing connecting the RST pin of the master device to the SS/INH of the slave. The slave is inhibited as long as the master output voltage is outside of the regulation so implementing the sequencing (see *Figure 12*).

High flexibility is achieved thanks to the programmable RST thresholds (see *Table 7 on page 11*) and programmable delay time. To minimize the component count the DELAY pin capacitor can be also omitted so the pin works as a normal Power Good.

## 4.4 Error amplifier

The voltage error amplifier is the core of the loop regulation. It is a transconductance operational amplifier whose non inverting input is connected to the internal voltage reference (0.85 V), while the inverting input (FB) is connected to the external divider or directly to the output voltage.

| Description        | Values |  |  |  |  |

|--------------------|--------|--|--|--|--|

| Transconductance   | 155 µS |  |  |  |  |

| Low frequency gain | 100 dB |  |  |  |  |

The error amplifier output is compared with the inductor current sense information to perform PWM control. The error amplifier also determines the burst operation at the light-load when the LCM is active.

# 4.5 Light-load operation

The MLF pinstrapping during the power-up phase determines the light-load operation (refer to *Table 7 on page 11*).

### 4.5.1 Low noise mode (LNM)

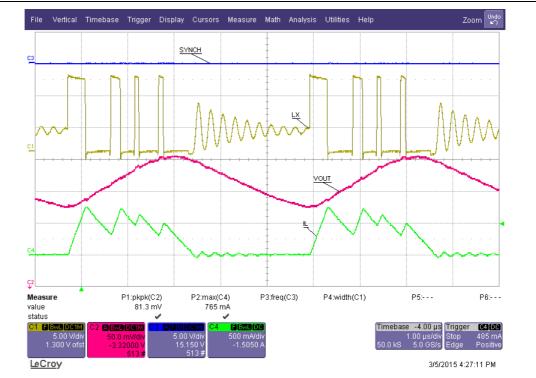

The low noise mode implements a forced PWM operation over the different loading conditions. The LNM features a constant switching frequency to minimize the noise in the final application and a constant voltage ripple at fixed  $V_{IN}$ . The regulator in steady loading condition never skip pulses and it operates in the continuous conduction mode (CCM) over the different loading conditions thus making this operation mode ideal for noise sensitive applications.

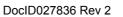

Figure 13. Low noise mode operation

The low consumption mode maximizes the efficiency at the light-load. The regulator prevents the switching activity whenever the switch peak current request is lower than the  $I_{SKIP}$  threshold (350 mA typical). As a consequence the L6985F device works in bursts and it minimizes the quiescent current request in the meantime between the switching operation. In the LCM operation, the pin SYNCH/ISKIP level dynamically defines the  $I_{SKIP}$  current threshold (see *Table 9*).

| SYNCH / ISKIP (pin 4) | I <sub>SKIP</sub> current threshold |  |  |

|-----------------------|-------------------------------------|--|--|

| LOW                   | ISKIP <sub>H</sub> = 0.35 A typical |  |  |

| HIGH                  | ISKIP <sub>L</sub> = 0.1 A typical  |  |  |

| Table | 9. | ISKIP | current | level |

|-------|----|-------|---------|-------|

|-------|----|-------|---------|-------|

The ISKIP programmability helps to optimize the performance in terms of the output voltage ripple or efficiency at the light-load, that are parameters which disagree each other by definition.

A lower skip current level minimizes the voltage ripple but increases the switching activity (time between bursts gets closer) since less energy per burst is transfered to the output voltage at the given load. On the other side, a higher skip level reduces the switching activity and improves the efficiency at the light-load but worsen the voltage ripple.

No difference in terms of the voltage ripple and conversion efficiency for the medium and high load current level, that is when the device operates in the discontinuous or continuous mode (DCM vs. CCM).

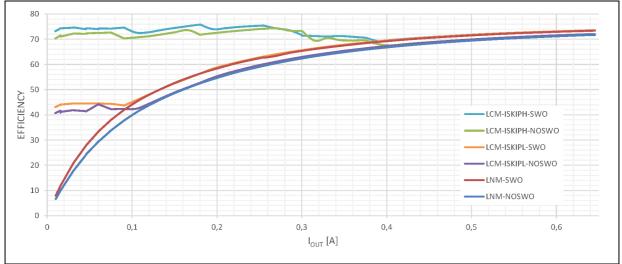

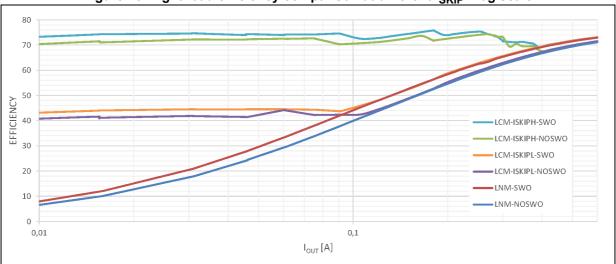

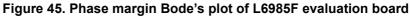

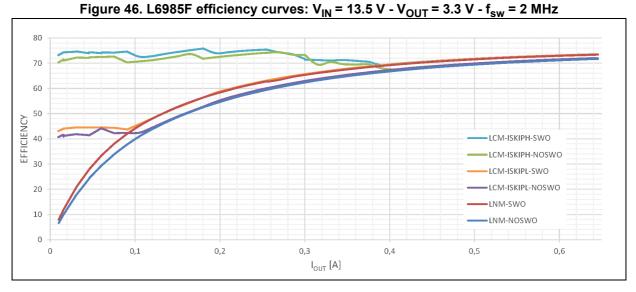

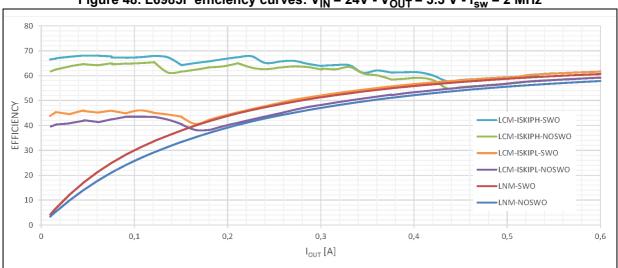

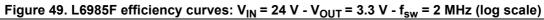

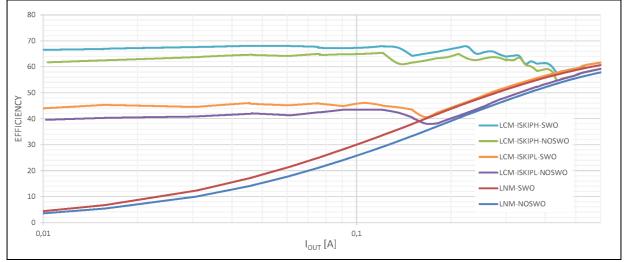

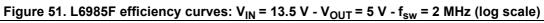

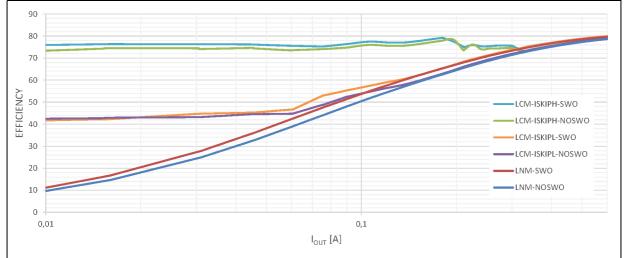

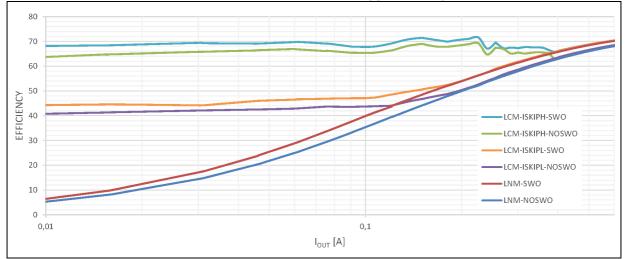

*Figure 14* and *Figure 15* report the efficiency measurements with  $V_{OUT} = 3.3$  V to highlight the ISKIP<sub>H</sub> and ISKIP<sub>L</sub> efficiency gap at the light-load also in comparison with the LNM operation. The same efficiency at the medium / high load is confirmed at different ISKIP levels.

Figure 14. Light-load efficiency comparison at different I<sub>SKIP</sub> - linear scale

Figure 15. Light-load efficiency comparison at different ISKIP - log scale

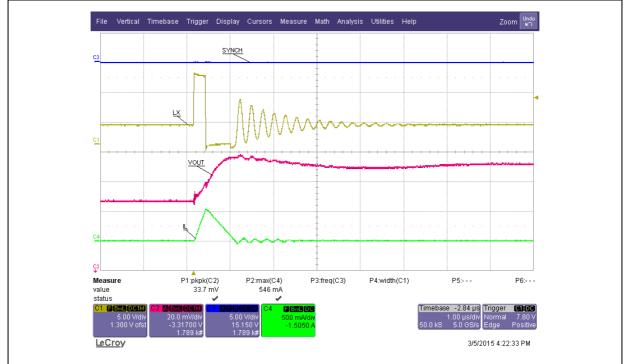

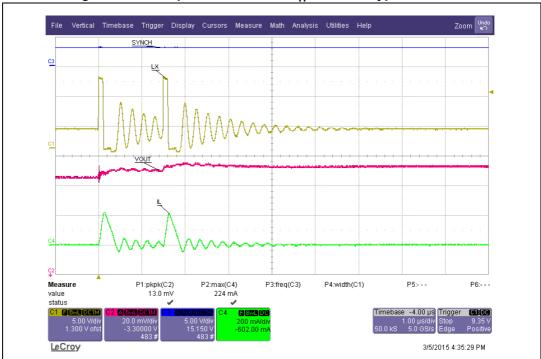

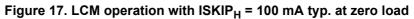

*Figure 16* and *Figure 17* show the LCM operation at the different ISKIP level. *Figure 16* shows the ISKIP<sub>H</sub> = 350 mA typ. and so 34 mV output voltage ripple. *Figure 17* shows the ISKIP<sub>L</sub> = 100 mA typ. and so 13 mV output voltage ripple.

#### Figure 16. LCM operation with ISKIP<sub>H</sub> = 350 mA typ. at zero load

Given the energy stored in the inductor during a burst, the voltage ripple depends on the capacitor value:

#### **Equation 13**

$$V_{\text{OUT RIPPLE}} = \frac{\Delta Q_{\text{IL}}}{C_{\text{OUT}}} = \frac{\int_{0}^{T_{\text{BURST}}} (i_{\text{L}}(t) \cdot dt)}{C_{\text{OUT}}}$$

Figure 18. LCM operation over loading condition (part 1)

Figure 19. LCM operation over loading condition (part 2)

DocID027836 Rev 2

Figure 20. The regulator works in CCM

### 4.6 Switchover feature

The switchover maximizes the efficiency at the light-load that is crucial for LCM applications.

#### 4.6.1 LCM

The LCM operation satisfies the high efficiency requirements of the battery powered applications. In order to minimize the regulator quiescent current request from the input voltage, the V<sub>BIAS</sub> pin can be connected to an external voltage source in the range  $3 \text{ V} < \text{V}_{\text{BIAS}} < 5.5 \text{ V}$  (see Section 4.1: Power supply and voltage reference on page 13).

In case the  $V_{\text{BIAS}}$  pin is connected to the regulated output voltage (V\_{\text{OUT}}), the total current drawn from the input voltage can be calculated as:

#### **Equation 14**

$$I_{QVIN} = I_{QOPVIN} + \frac{1}{\eta_{L6985F}} \bullet \frac{V_{BIAS}}{V_{IN}} \bullet I_{QOPVBIAS}$$

where  $I_{Q OP VIN}$ ,  $I_{Q OP VBIAS}$  are defined in *Table 5: Electrical characteristics on page 8* and  $\eta_{L6985F}$  is the efficiency of the conversion in the working point.

#### 4.6.2 LNM

*Equation 14* is also valid when the device works in LNM and it can increase the efficiency at the medium load since the regulator always operates in the continuous conduction mode.

DocID027836 Rev 2

## 4.7 Overcurrent protection

The current protection circuitry features constant current protection, so the device limits the maximum peak current (see *Table 5: Electrical characteristics on page 8*) in overcurrent condition.

The L6985F device implements a pulse-by-pulse current sensing on both power elements (high-side and low-side switches) for effective current protection over the duty cycle range. The high-side current sensing is called "peak", the low-side sensing "valley".

The internal noise generated during the switching activity makes the current sensing circuitry ineffective for a minimum conduction time of the power element. This time is called "masking time" because the information from the analog circuitry is masked by the logic to prevent erroneous detection of the overcurrent event. As a consequence, the peak current protection is disabled for a masking time after the high-side switch is turned on, the valley for a masking time after the low-side switch is turned on. In other words, the peak current protection can be ineffective at extremely low duty cycles, the valley current protection at extremely high duty cycles.

The L6985F device assures an effective overcurrent protection sensing the current flowing in both power elements. In case one of the two current sensing circuitry is ineffective because of the masking time, the device is protected sensing the current on the opposite switch. Thus, the combination of the "peak" and "valley" current limits assure the effectiveness of the overcurrent protection even in extreme duty cycle conditions.

The valley current threshold is designed higher than the peak to guarantee a proper operation. In case the current diverges because of the high-side masking time, the low-side power element is turned on until the switch current level drops below the valley current sense threshold. The low-side operation is able to prevent the high-side turn on, so the device can skip pulses decreasing the switching frequency.

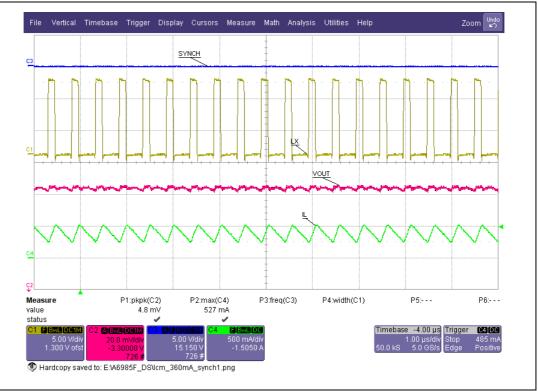

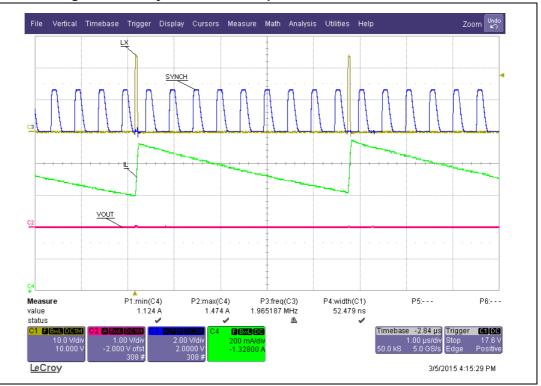

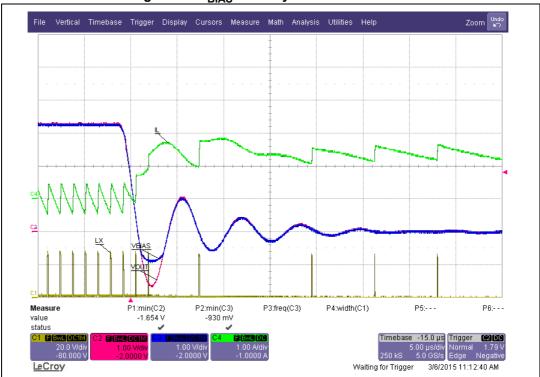

Figure 21. Valley current sense operation in overcurrent condition

*Figure 21* shows the switching frequency reduction during the valley current sense operation in case of an extremely low duty cycle ( $V_{IN}$  = 38 V,  $f_{SW}$  = 2 MHz short-circuit condition).

In a worst case scenario (like in *Figure 21*) of the overcurrent protection the switch current is limited to:

#### **Equation 15**

$$I_{MAX} = I_{VALLEYTH} + \frac{V_{IN} - V_{OUT}}{L} \bullet T_{MASKHS}$$

where  $I_{VALLEY_TH}$  is the current threshold of the valley sensing circuitry (see *Table 5: Electrical characteristics on page 8*) and  $T_{MASK_HS}$  is the masking time of the high-side switch 100 nsec. typ.).

In most of the overcurrent conditions the conduction time of the high-side switch is higher than the masking time and so the peak current protection limits the switch current.

#### **Equation 16**

$$I_{MAX} = I_{PEAK_TH}$$

Figure 22. Peak current sense operation in overcurrent condition

The DC current flowing in the load in overcurrent condition is:

#### **Equation 17**

$$I_{DCOC}(V_{OUT}) = I_{MAX} - \frac{I_{RIPPLE}(V_{OUT})}{2} = I_{MAX} - \left(\frac{V_{IN} - V_{OUT}}{2 \bullet L} \bullet T_{ON}\right)$$

Output capacitor discharging the current flowing to ground during heavy short-circuit events is only limited by parasitic elements like the output capacitor ESR and short-circuit impedance.

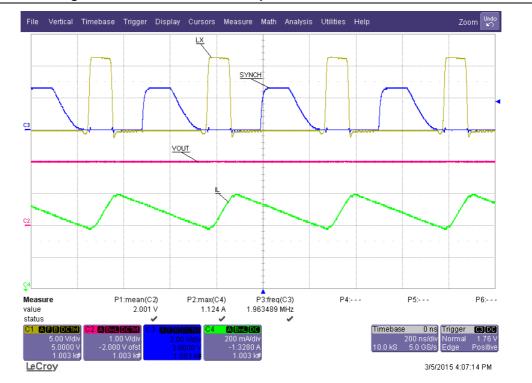

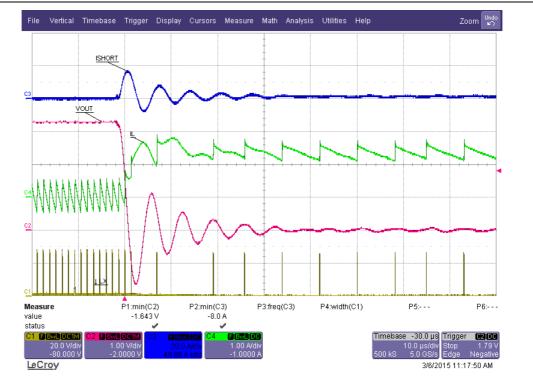

Due to parasitic inductance of the short-circuit impedance, negative output voltage oscillations can be generated with huge discharging current levels (see *Figure 23*).

Figure 23. Output voltage oscillations during heavy short-circuit

Figure 24. Zoomed waveform

The V<sub>BIAS</sub> pin absolute maximum ratings (see *Table 2: Absolute maximum ratings on page 6*) must be satisfied over the different dynamic conditions.

If the  $V_{BIAS}$  is connected to GND there are no issues (see *Figure 23* and *Figure 24*).

A small resistor value (few  $\Omega$ ) in series with the V<sub>BIAS</sub> can help to limit the pin negative voltage (see *Figure 25*) during heavy short-circuit events if it is connected to the regulated output voltage.

Figure 25. V<sub>BIAS</sub> in heavy short-circuit event

# 4.8 Overvoltage protection

The overvoltage protection monitors the FB pin and enables the low-side MOSFET to discharge the output capacitor if the output voltage is 20% over the nominal value.

This is a second level protection and should never be triggered in normal operating conditions if the system is properly dimensioned. In other words, the selection of the external power components and the dynamic performance determined by the compensation network should guarantee an output voltage regulation within the overvoltage threshold even during the worst case scenario in term of load transitions.

The protection is reliable and also able to operate even during normal load transitions for a system whose dynamic performance is not in line with the load dynamic request. As a consequence the output voltage regulation would be affected.

*Figure 26* shows the overvoltage operation during a negative steep load transient for a system designed with huge inductor value and a small output capacitor. The inductor value limits the switch current slew rate and the extra charge flowing into the small capacitor value generates an overvoltage event. This can be considered as an example for a system with a dynamic performance not in line with the load request.

The L6985F device implements a 1 A typ. negative current limitation to limit the maximum reversed switch current during the overvoltage operation.

Figure 26. Overvoltage operation

### 4.9 Thermal shutdown

The shutdown block disables the switching activity if the junction temperature is higher than a fixed internal threshold (165 °C typical). The thermal sensing element is close to the power elements, ensuring fast and accurate temperature detection. A hysteresis of approximately 30 °C prevents the device from turning ON and OFF continuously. When the thermal protection runs away a new soft-start cycle will take place.

# 5 Closing the loop

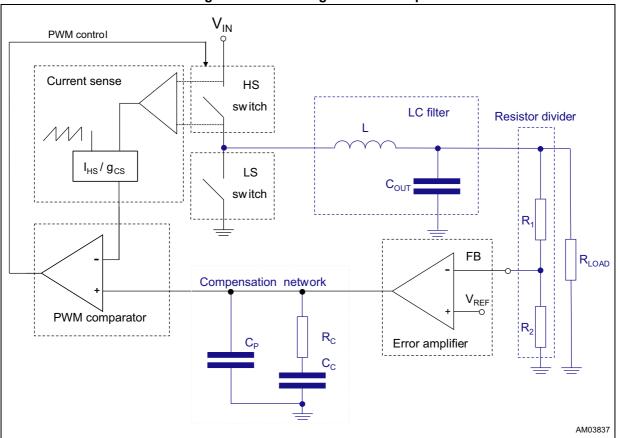

Figure 27. Block diagram of the loop

# 5.1 G<sub>CO</sub>(s) control to output transfer function

The accurate control to output transfer function for a buck peak current mode converter can be written as:

#### **Equation 18**

$$G_{CO(s)} = R_{LOAD} \bullet g_{cs} \bullet \frac{1}{1 + \frac{R_{LOAD} \bullet T_{SW}}{L} \bullet [m_{C} \bullet (1 - D) - 0.5]} \bullet \frac{\left(1 + \frac{s}{\omega_{z}}\right)}{\left(1 + \frac{s}{\omega_{p}}\right)} \bullet F_{H}(s)$$

where  $R_{LOAD}$  represents the load resistance,  $g_{CS}$  the equivalent sensing conductance of the current sense circuitry,  $\omega_p$  the single pole introduced by the power stage and  $\omega_z$  the zero given by the ESR of the output capacitor.

$F_H(s)$  accounts the sampling effect performed by the PWM comparator on the output of the error amplifier that introduces a double pole at one half of the switching frequency.

DocID027836 Rev 2

**Equation 19**

$$\omega_{z} = \frac{1}{\text{ESR} \bullet \text{C}_{\text{OUT}}}$$

**Equation 20**

$$\omega_{p} = \frac{1}{R_{LOAD} \bullet C_{OUT}} + \frac{m_{c} \bullet (1 - D) - 0.5}{L \bullet C_{OUT} \bullet f_{SW}}$$

where:

**Equation 21**

$$\begin{pmatrix} m_{C} = 1 + \frac{S_{e}}{S_{n}} \\ S_{e} = V_{PP} \cdot g_{CS} \cdot f_{SW} \\ S_{n} = \frac{V_{IN} - V_{OUT}}{L} \end{cases}$$

$S_n$  represents the on time slope of the sensed inductor current,  $S_e$  the on time slope of the external ramp (V<sub>PP</sub> peak-to-peak amplitude) that implements the slope compensation to avoid sub-harmonic oscillations at the duty cycle over 50%.

$S_e$  can be calculated from the parameter  $V_{PP}$  ×  $g_{CS}$  given in Table 5 on page 8.

The sampling effect contribution  $\mathsf{F}_{\mathsf{H}}(s)$  is:

#### **Equation 22**

$$\mathsf{F}_{\mathsf{H}}(\mathsf{s}) = \frac{1}{1 + \frac{\mathsf{s}}{\omega_{\mathsf{n}} \bullet \mathsf{Q}_{\mathsf{p}}} + \frac{\mathsf{s}^{2}}{\omega_{\mathsf{n}}^{2}}}$$

where:

**Equation 23**

$$Q_{p} = \frac{1}{\pi \bullet [m_{c} \bullet (1-D) - 0.5]}$$

# 5.2 Error amplifier compensation network

The typical compensation network required to stabilize the system is shown in Figure 28.

$R_C$  and  $C_C$  introduce a pole and a zero in the open loop gain.  $C_P$  does not significantly affect system stability but it is useful to reduce the noise at the output of the error amplifier.

The transfer function of the error amplifier and its compensation network is:

### **Equation 24**

$$A_0(s) = \frac{A_{V0} \bullet (1 + s \bullet R_c \bullet C_c)}{s^2 \bullet R_0 \bullet (C_0 + C_p) \bullet R_c \bullet C_c + s \bullet (R_0 \bullet C_c + R_0 \bullet (C_0 + C_p) + R_c \bullet C_c) + 1}$$

where  $A_{vo} = G_m \cdot R_o$

The poles of this transfer function are (if  $C_c >> C_0 + C_P$ ):

**Equation 25**

$$f_{\mathsf{PLF}} = \frac{1}{2 \bullet \pi \bullet \mathsf{R}_0 \bullet \mathsf{C}_c}$$

### **Equation 26**

whereas the zero is defined as:

$$f_{\mathsf{PHF}} = \frac{1}{2 \bullet \pi \bullet \mathsf{R}_0 \bullet (\mathsf{C}_0 + \mathsf{C}_p)}$$

**Equation 27**

$$f_{Z} = \frac{1}{2 \bullet \pi \bullet R_{c} \bullet C_{c}}$$

### 5.3 Voltage divider

The simple voltage divider contribution is:

#### **Equation 28**

$$G_{DIV}(s) = \frac{R_2}{R_1 + R_2}$$

A small signal capacitor in parallel to the upper resistor (see *Figure 29*) of the voltage divider implements a leading network ( $f_{zero} < f_{pole}$ ), sometimes necessary to improve the system phase margin.

Figure 29. Leading network example

Laplace transformer of the leading network:

#### **Equation 29**

$$G_{\text{DIV}}(s) = \frac{R_2}{R_1 + R_2} \bullet \frac{(1 + s \bullet R_1 \bullet C_{\text{R1}})}{\left(1 + s \bullet \frac{R_1 \bullet R_2}{R_1 + R_2} \bullet C_{\text{R1}}\right)}$$

L6985F

where:

**Equation 30**

$$f_{Z} = \frac{1}{2 \bullet \pi \bullet R_{1} \bullet C_{R1}}$$

$$f_{p} = \frac{1}{2 \bullet \pi \bullet \frac{R_{1} \bullet R_{2}}{R_{1} + R_{2}} \bullet C_{R1}}$$

$$f_{Z} < f_{p}$$

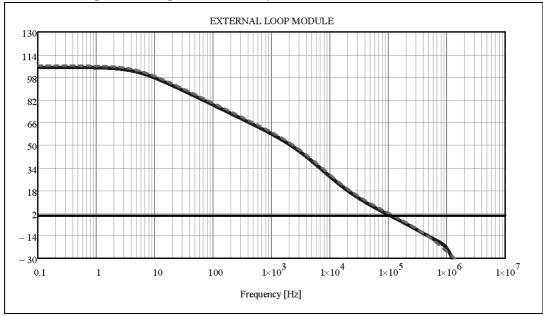

## 5.4 Total loop gain

In summary, the open loop gain can be expressed as:

Equation 31

$$G(s) = G_{DIV}(s) \cdot G_{CO}(s) \cdot A_0(s)$$

#### Example 1

$V_{\text{IN}}$  = 12 V  $V_{\text{OUT}}$  = 3.3 V and  $R_{\text{OUT}}$  = 6.6  $\Omega$

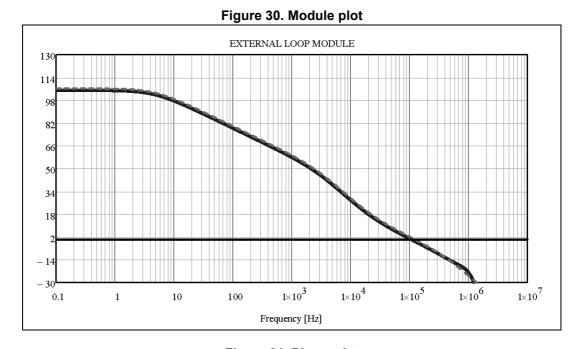

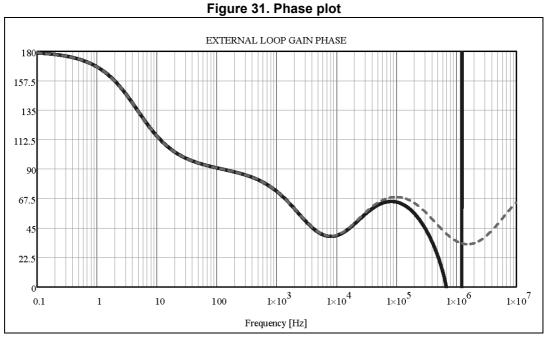

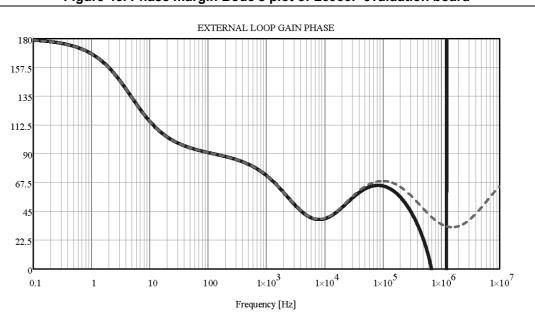

Selecting L = 4.7 $\mu$ H, C<sub>OUT</sub> = 10  $\mu$ F and ESR = 1 m $\Omega$ , R<sub>C</sub>= 110 k $\Omega$ , C<sub>C</sub>= 68 pF, C<sub>P</sub> = 1.2 pF (please refer to *Example 2*), the gain and phase bode diagrams are plotted respectively in *Figure 30* and *Figure 31*.

#### **Equation 32**

$$BW = 108 kHz$$

phase margin = 64<sup>0</sup>

The solid trace represents the transfer function including the sampling effect term (see *Equation 22 on page 37*), the dotted trace neglects the contribution.

## 5.5 Compensation network design

The maximum bandwidth of the system can be designed up to  $f_{SW}/6$  or up to 150 kHz to guarantee a valid small signal model.

#### **Equation 33**

$$\mathsf{BW} = \min\left(\frac{\mathsf{f}_{\mathsf{SW}}}{6}, 150 \mathsf{kHz}\right)$$

**Equation 34**

$$R_{C} = \frac{2 \cdot \pi \cdot BW \cdot C_{OUT} \cdot V_{OUT}}{0.85V \cdot g_{CS} \cdot g_{m TYP}}$$

where  $g_{CS}$  represents the current sense transconductance (see *Table 5: Electrical characteristics on page 8*) and  $g_{m TYP}$  the error amplifier transconductance.

**Equation 35**

$$C_{C} = \frac{5}{2 \cdot \pi \cdot R_{C} \cdot BW}$$

#### Example 2

Considering L6985F,  $V_{IN}$  = 12 V,  $V_{OUT}$  = 3.3 V, L = 4.7  $\mu$ H,  $C_{OUT}$  = 10  $\mu$ F,  $f_{SW}$  = 2 MHz. Assuming to design the compensation network to achieve system bandwidth of 110 kHz:

**Equation 36**

$$f_{POLE} = 2.4 kHz$$

**Equation 37**

$$R_{LOAD} = \frac{V_{OUT}}{I_{OUT}} = 6.6\Omega$$

so accordingly with Equation 34 and Equation 35:

**Equation 38**

$$R_{\rm C} = 107 k\Omega \approx 110 k\Omega$$

**Equation 39**

$$C_C = 66pF \approx 68pF$$

# 6 Application notes

## 6.1 Output voltage adjustment

The internal reference is equal to 0.85 V typical, and the output voltage is adjusted accordingly to *Equation 40* (see *Figure 32*):

#### **Equation 40**

$$V_{OUT} = V_{REF} \bullet \left(1 + \frac{R_1}{R_2}\right) = 0.85 \bullet \left(1 + \frac{R_1}{R_2}\right)$$

where the  $C_{r1}$  capacitor is sometimes useful to increase the small signal phase margin (please refer to Section 5.5: Compensation network design).

Figure 32. L6985F application circuit

## 6.2 Switching frequency

A resistor connected to the FSW pin features the selection of the switching frequency. The pinstrapping is performed at power-up, before the soft-start takes place. The FSW pin is pinstrapped and then driven floating in order to minimize the quiescent current from VIN.

Please refer to *Table 6:*  $f_{SW}$  selection on page 11 to identify the pull-up / pull-down resistor value.  $f_{SW}$  = 250 kHz /  $f_{SW}$  = 500 kHz preferred codifications don't require any external resistor.

## 6.3 MLF pin

A resistor connected to the MLF pin features the selection of the between low noise mode / low consumption mode and the different RST thresholds. The pinstrapping is performed at power-up, before the soft-start takes place. The FSW pin is pinstrapped and then driven floating in order to minimize the quiescent current from VIN.

Please refer to *Table 7 on page 11* to identify the pull-up / pull-down resistor value. (LNM, RST threshold 93%) / (LCM, RST threshold 93%) preferred codifications don't require any external resistor.

## 6.4 Voltage supervisor

The embedded voltage supervisor (composed of the RST and the DELAY pins) monitors the regulated output voltage and keeps the RST open collector output in low impedance as long as the  $V_{OUT}$  is out of regulation. In order to ensure a proper reset of digital devices with a valid power supply, the device can delay the RST assertion with a programmable time.

Figure 33. Voltage supervisor operation

The comparator monitoring the FB voltage has four different programmable thresholds (80%, 87%, 93%, 96% nominal output voltage) for high flexibility (see *Section 6.3: MLF pin* and *Table 7 on page 11*).

When the RST comparator detects the output, voltage is in regulation, a 2  $\mu$ A internal current source starts to charge an external capacitor to implement a voltage ramp on the DELAY pin. The RST open collector is then released as soon as V<sub>DELAY</sub> = 1.234 V (see *Figure 33*).

L6985F

The C<sub>DELAY</sub> is dimensioned accordingly with *Equation 41*:

#### **Equation 41**

$$C_{DELAY} = \frac{I_{SSCH} \bullet T_{DELAY}}{V_{DELAY}} = \frac{2\mu A \bullet T_{DELAY}}{1.234V}$$

The maximum suggested capacitor value is 270 nF.

## 6.5 Synchronization (LNM)

Beating frequency noise is an issue when multiple switching regulators populate the same application board. The L6985F synchronization circuitry features the same switching frequency for a set of regulators simply connecting their SYNCH pin together, so preventing beating noise. The master device provides the synchronization signal to the others since the SYNCH pin is I/O able to deliver or recognize a frequency signal.

For proper synchronization of multiple regulators, all of them have to be configured with the same switching frequency (see *Table 6 on page 11*), so the same resistor connected at the FSW pin.

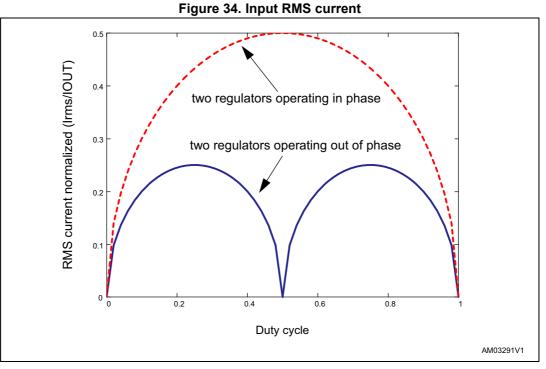

In order to minimize the RMS current flowing through the input filter, the L6985F device provides a phase shift of 180° between the master and the SLAVES. If more than two devices are synchronized, all slaves will have a common 180° phase shift with respect to the master.

Considering two synchronized L6985F devices which regulates the same output voltage (i.e.: operating with the same duty cycle), the input filter RMS current is optimized and is calculated as:

#### **Equation 42**

$$I_{RMS} = \begin{cases} \frac{I_{OUT}}{2} \cdot \sqrt{2D \cdot (1 - 2D)} & \text{if } D < 0.5 \\ \frac{I_{OUT}}{2} \cdot \sqrt{(2D - 1) \cdot (2 - 2D)} & \text{if } D > 0.5 \end{cases}$$

The graphical representation of the input RMS current of the input filter in the case of two devices with a 0° phase shift (synchronized to an external signal) or a 180° phase shift (synchronized connecting their SYNCH pins) regulating the same output voltage is provided in *Figure 34*. To dimension the proper input capacitor please refer to *Section 6.6.1: Input capacitor selection on page 50*.

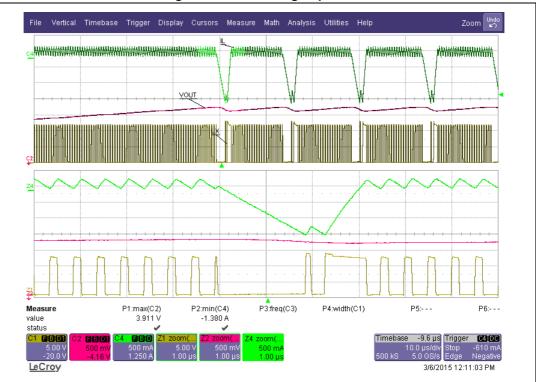

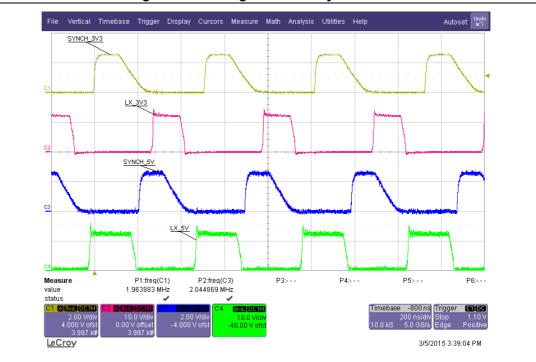

Figure 35 shows two regulators not synchronized.

Figure 35. Two regulators not synchronized

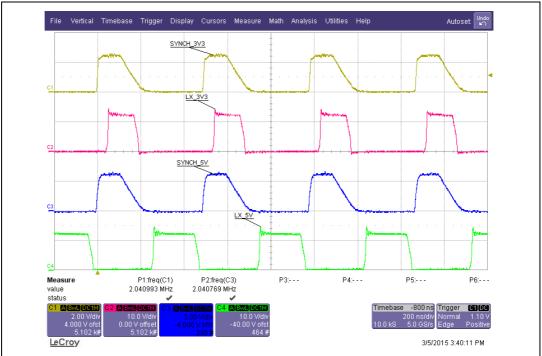

*Figure 36* shows the same regulators working synchronized. The MASTER regulator (LX\_5V trace) delivers the synchronization signal (SYNCH\_3V3, SYNCH\_5V pins are connected together) to the SLAVE device (LX\_3V3). The SLAVE regulator works in phase with the synchronization signal which is out of phase with the MASTER switching operation.

Figure 36. Two regulators synchronized

Multiple L6985F devices can be synchronized to an external frequency signal fed to the SYNCH pin. In this case the regulator set is phased to the reference and all the devices will work with a  $0^{\circ}$  phase shift.

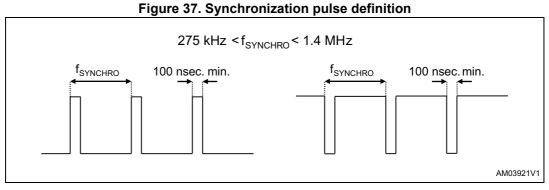

The frequency range of the synchronization signal is 275 kHz - 1.4 MHz and the minimum pulse width is 100 nsec (see *Figure 37*).

Since the slope compensation contribution that is required to prevent subharmonic oscillations in peak current mode architecture depends on the switching frequency, it is important to select the same oscillator frequency for all regulators (all of them operate as SLAVE) as close as possible to the frequency of the reference signal (please refer to *Table 6: f<sub>SW</sub> selection on page 11*). As a consequence all the regulators have the same

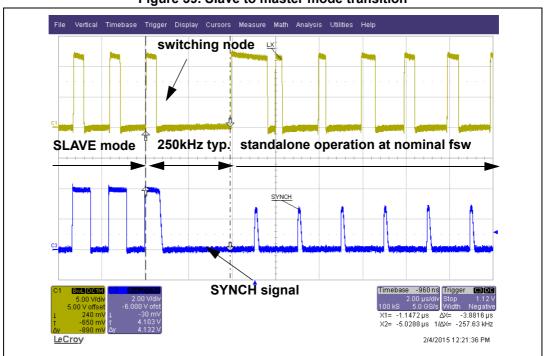

The L6985F normally operates in MASTER mode, driving the SYNCH line at the selected oscillator frequency as shown in *Figure 35* and *Figure 36*.

In SLAVE mode the L6985F sets the internal oscillator at 250 kHz typ. (see *Table 6 on page 11* - first row) and drives the line accordingly.

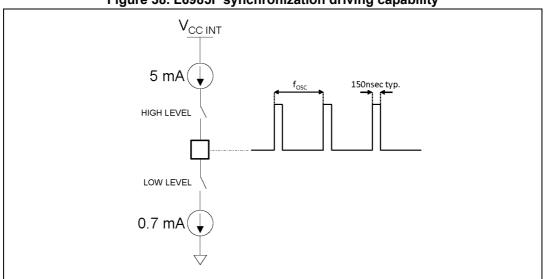

Figure 38. L6985F synchronization driving capability

In order to safely guarantee that each regulator recognizes itself in SLAVE mode during the normal operation, the external master must drive the SYNCH pin with a clock signal frequency higher than the maximum oscillator spread (refer to *Table 6*) for at least 10 internal clock cycles.

#### Example 3

Selecting  $R_{FSW} = 0 \Omega$  to GND.

| Symbol          | R <sub>VCC</sub> (E24 series) | R <sub>GND</sub> (E24 series) | f <sub>SW</sub> min. | f <sub>SW</sub> typ. | f <sub>SW</sub> max. |  |

|-----------------|-------------------------------|-------------------------------|----------------------|----------------------|----------------------|--|

| f <sub>SW</sub> | NC                            | 0 Ω                           | 450                  | 500                  | 550                  |  |

Table 10. Example of oscillator frequency selection from Table 6

The device enters into the slave mode after 10 pulses at frequency higher than 550 kHz and so it is able to synchronize to a clock signal in the range 275 kHz - 1.4 MHz (see *Figure 37*).

Anyway it is suggested to limit the frequency range within  $\pm 20\%$  f<sub>SW</sub> resistor nominal frequency (see details in text below). If a not spread spectrum is required, all the regulators synchronize to a frequency higher to the maximum oscillator spread (550 kHz in *Example 3*).

The device keeps operating in slave mode as far as the master is able to drive the SYNCH pin faster than 275 kHz (maximum oscillator spread for 250 kHz oscillator), otherwise it goes back into MASTER mode at the nominal oscillator frequency after successfully driving one pulse at 250 kHz (see *Figure 39*) in the SYNCH line.

Figure 39. Slave to master mode transition

The external master can force a latched SLAVE mode driving the SYNCH pin low at powerup, before the soft-start starts the switching activity. So the oscillator frequency is 250 kHz typ. fixed until a new UVLO event is triggered regardless FSW resistor value, that otherwise counts to design the slope compensation. The same considerations above are also valid.

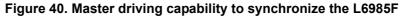

The master driving capability must be able to provide the proper signal levels at the SYNCH pin (see *Table 5 on page 8 - Synchronization* section):

- Low level < V<sub>SYN THL</sub>= 0.7 V sinking 5 mA

- High level > V<sub>SYN THH</sub> = 1.2 V sourcing 0.7 mA

As anticipated above, in the SLAVE mode the internal oscillator operates at 250 kHz typ. but the slope compensation is dimensioned accordingly with FSW resistors so, even if the L6985F supports synchronization over the 275 kHz - 1.4 MHz frequency range, it is important to limit the switching operation around a working point close to the selected frequency (FSW resistor).

As a consequence, to guarantee the full output current capability and to prevent the subharmonic oscillations the master must limit the driving frequency range within  $\pm$  20% of the selected frequency.

A wider frequency range may generate subharmonic oscillation for duty > 50% or limit the peak current capability (see  $I_{PK}$  parameter in *Table 5 on page 8*) since the internal slope compensation signal may be saturated.

In order to guarantee the synchronization as a slave over distribution, temperature and the output load, the external clock frequency must be lower than 1.4 MHz.

### 6.6 Design of the power components

### 6.6.1 Input capacitor selection

The input capacitor voltage rating must be higher than the maximum input operating voltage of the application. During the switching activity a pulsed current flows into the input capacitor and so its RMS current capability must be selected accordingly with the application conditions. Internal losses of the input filter depends on the ESR value so usually low ESR capacitors (like multilayer ceramic capacitors) have a higher RMS current capability. On the other hand, given the RMS current value, lower ESR input filter has lower losses and so contributes to higher conversion efficiency.

The maximum RMS input current flowing through the capacitor can be calculated as:

#### **Equation 43**

$$I_{RMS} = I_{OUT} \bullet \sqrt{\left(1 - \frac{D}{\eta}\right) \bullet \frac{D}{\eta}}$$

Where  $I_{OUT}$  is the maximum DC output current, *D* is the duty cycles,  $\eta$  is the efficiency. This function has a maximum at D = 0.5 and, considering  $\eta$  = 1, it is equal to  $I_{OUT}/2$ .

In a specific application the range of possible duty cycles has to be considered in order to find out the maximum RMS input current. The maximum and minimum duty cycles can be calculated as:

#### **Equation 44**

$$D_{MAX} = \frac{V_{OUT} + \Delta V_{LOWSIDE}}{V_{INMIN} + \Delta V_{LOWSIDE} - \Delta V_{HIGHSIDE}}$$

**Equation 45**

$$D_{MIN} = \frac{V_{OUT} + \Delta V_{LOWSIDE}}{V_{INMAX} + \Delta V_{LOWSIDE} - \Delta V_{HIGHSIDE}}$$

Where  $\Delta V_{HIGH SIDE}$  and  $\Delta V_{LOW SIDE}$  are the voltage drops across the embedded switches.

The peak-to-peak voltage across the input filter can be calculated as:

#### **Equation 46**

$$V_{PP} = \frac{I_{OUT}}{C_{IN} \bullet f_{SW}} \bullet \left(1 - \frac{D}{\eta}\right) \bullet \frac{D}{\eta} + ESR \bullet (I_{OUT} + \Delta I_L)$$

In case of negligible ESR (MLCC capacitor) the equation of  $C_{\rm IN}$  as a function of the target  $V_{\rm PP}$  can be written as follows:

#### **Equation 47**

$$C_{IN} = \frac{I_{OUT}}{V_{PP} \bullet f_{SW}} \bullet \left(1 - \frac{D}{\eta}\right) \bullet \frac{D}{\eta}$$

Considering  $\eta$  = 1 this function has its maximum in D = 0.5:

#### **Equation 48**

$$C_{\text{INMIN}} = \frac{I_{\text{OUT}}}{4 \bullet V_{\text{PPMAX}} \bullet f_{\text{SW}}}$$

Typically C<sub>IN</sub> is dimensioned to keep the maximum peak-to-peak voltage across the input filter in the order of 5% V<sub>IN MAX</sub>.

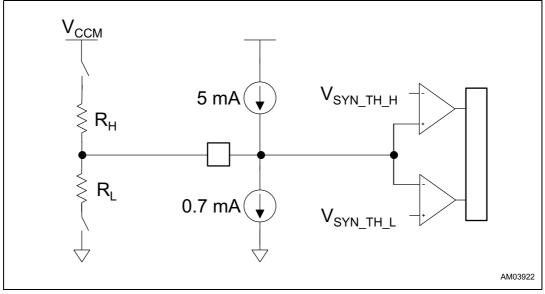

| Manufacturer Series         |                | Size | Cap value (μF) | Rated voltage (V) |