# INEAR SYSTEMS

# LSK489A/B

Over 30 Years of Quality Through Innovation

Low Noise, Monolithic Dual N-Channel JFET Amplifier

### INDUSTRY'S LOWEST INPUT CAPACITANCE MONOLITHIC DUAL N-CHANNEL JFET

| Absolute Maximum Ratings                            |                            |  |  |  |  |

|-----------------------------------------------------|----------------------------|--|--|--|--|

| @ 25 °C (unless otherwise stated)                   |                            |  |  |  |  |

| Maximum Temperatures                                |                            |  |  |  |  |

| Storage Temperature                                 | -55 to +150°C              |  |  |  |  |

| Junction Operating Temperature                      | -55 to +150°C              |  |  |  |  |

| Maximum Power Dissipation, TA = 25°C                |                            |  |  |  |  |

| Continuous Power Dissipation, per side <sup>4</sup> | 300mW                      |  |  |  |  |

| Power Dissipation, total <sup>5</sup>               | 500mW                      |  |  |  |  |

| Maximum Currents                                    |                            |  |  |  |  |

| Gate Forward Current                                | $I_{G(F)} = 10 \text{mA}$  |  |  |  |  |

| Maximum Voltages                                    |                            |  |  |  |  |

| Gate to Source                                      | $V_{GSS} = 60V$            |  |  |  |  |

| Gate to Drain                                       | $V_{GDS} = 60V$            |  |  |  |  |

| Features                                            |                            |  |  |  |  |

| Low Noise (f = 1kHz, NBW = 1Hz)                     | e <sub>n</sub> = 1.8nV/√Hz |  |  |  |  |

| Low Input Capacitance                               | Ciss = 4pF                 |  |  |  |  |

G1 🗗 S2 99 D1 D2 20 D1 []2 D2 SS 6 D2 G1 4 82 SOIC-A SOT-23 TO-71 **Top View Top View Top View** \* For equivalent single version, see LSK189

#### Features

- Low Noise: en = 1.8nV/√Hz (typ), f = 1kHz, NBW = 1Hz

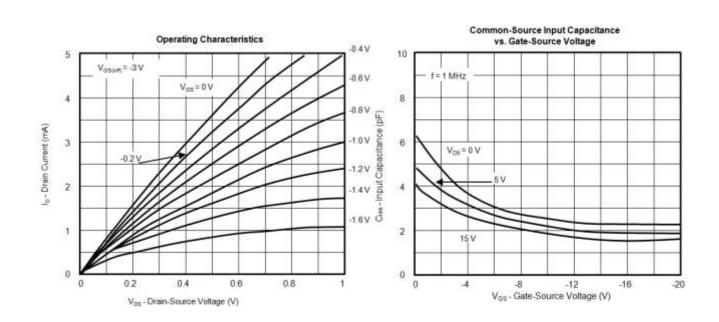

- Very Low Common Source Input Capacitance of C<sub>ISS</sub> = 4pF - typ

- High Slew Rate

- Low Offset/Drift Voltage

- Low Gate Leakage IGSS and IG

- High CMRR 102 dB

#### Benefits

- Tight Differential Voltage Match vs. Current

- Improved Op Amp Speed Settling Time Accuracy

- Minimum Input Error Trimming Error Voltage

- Lower Intermodulation Distortion Due to Low Input Capacitance

#### Applications

- Wideband Differential Amplifiers

- High Speed Temperature Compensated Single Ended Input Amplifier

- High Speed Comparators

- Impedance Converters

- Sonobouys and Hydrophones

- Acoustic Sensors

#### Description

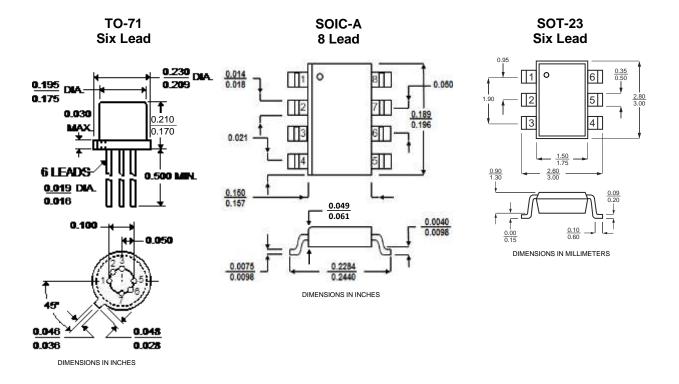

The LSK489 is the industry's lowest input capacitance and low-noise monolithic dual N-Channel JFET. Low input capacitance substantially reduces intermodulation distortion. In addition, these dual JFETs feature tight offset voltage and low drift over temperature range, and are targeted for use in a wide range of precision instrumentation and sensor applications. The LSK489 is available in surface mount plastic SOIC 8L and SOT-23 6L, as well as thru-hole metal TO-71 6L packages. For an equivalent single N-Channel version refer to the LSK189 datasheet. LSK489 TO-71 6L and SOIC 8L are fit, form and pin compatible to the same LSK389 product.

The LSK489 provides a dramatic increase in capabilities for a wide range of low-noise applications. The most significant aspect of the LSK489 is how it combines a noise level nearly as low as the LSK389 while having much lower gate-to-drain capacitance, 4pF versus the 25pF. The slightly higher noise of the LSK489, versus the LSK389, is not significant in most instances, while the much lower capacitance enables designers to produce simpler, more elegant circuit designs with fewer devices that cost less in production. Also notice that the LSK489 and LSK389 TO-71 and SOIC packages are the same and pin compatible, therefore, they can be used interchangeably.

Like the Linear Systems LSK389, the LSK489 features a unique design construction of interleaving both JFETs on the same piece of silicon to provide excellent matching and thermal tracking, as well a low-noise profile having nearly zero popcorn noise. I<sub>DSS</sub> range is divided into two segments providing designers improved resolution, which are A grade ( $\Delta$ I<sub>DSS</sub> = 6mA) and B grade ( $\Delta$ I<sub>DSS</sub> = 7mA). Contact Linear Systems for improved En, I<sub>DSS</sub>, V<sub>GS</sub>(off),  $\Delta$  V<sub>GS</sub> or any other limits. Based on new limits, LS will assign a new SELXXXX code to be used in shipments.

| Symbol         | Characteristic                                                                      | Min. | Тур. | Max | Units  | Conditions                                                       |

|----------------|-------------------------------------------------------------------------------------|------|------|-----|--------|------------------------------------------------------------------|

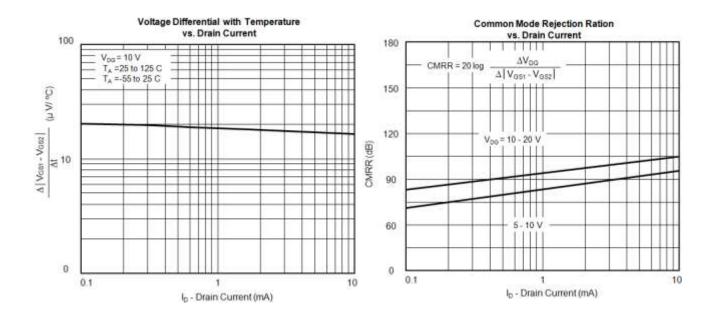

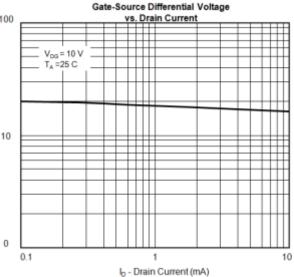

| VGS1-VGS2      | Differential Gate to Source Cutoff Voltage                                          | -    | 8    | 20  | mV     | $V_{DS} = 10V$ , $I_D = 1mA$                                     |

| IDSS1<br>IDSS2 | Gate to Source Saturation Current Ratio                                             | 0.9  | -    | 1.0 | -      | $V_{DS}=10V,V_{GS}=0V$                                           |

| CMRR           | <u>Common Mode Rejection Ratio</u><br>-20 log ΔV <sub>GS1-2</sub> /ΔV <sub>DS</sub> | 95   | 102  | -   | dB     | $V_{DS}$ = 10V to 20V, $I_D$ = 200 $\mu A$                       |

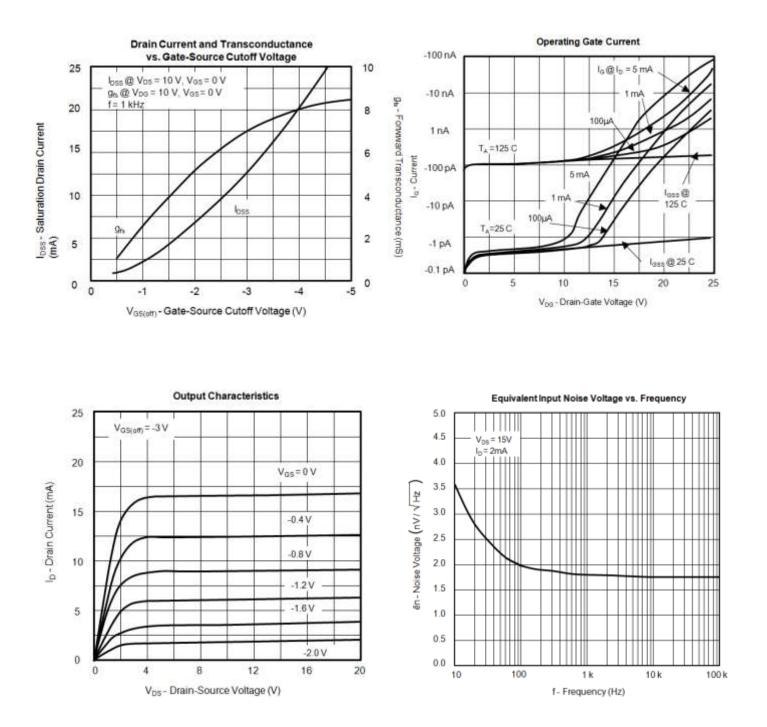

| en             | Noise Voltage                                                                       | -    | 1.8  | -   | nV/√Hz | $V_{DS} = 15V$ , $I_D = 2.0$ mA, $f = 1$ kHz,<br>NBW = 1Hz       |

| en             | Noise Voltage                                                                       | -    | 3.5  | -   | nV/√Hz | $V_{DS} = 15V, I_D = 2.0mA, f = 10Hz, NBW = 1Hz$                 |

| CISS           | Common Source Input Capacitance                                                     | -    | 4    | -   | pF     | - V <sub>DS</sub> = 15V, I <sub>D</sub> = 500μA, <i>f</i> = 1MHz |

| Crss           | Common Source Reverse Transfer<br>Capacitance                                       | -    | 2    | -   | pF     |                                                                  |

#### Matching Characteristics @ 25°C (unless otherwise stated)

#### Electrical Characteristics @ 25°C (unless otherwise stated)

| Symbol                 | Characteristic                        |                        | Min. | Тур. | Max  | Units | Conditions                                           |

|------------------------|---------------------------------------|------------------------|------|------|------|-------|------------------------------------------------------|

| BV <sub>GSS</sub>      | Gate to Source Breakdown Voltage      |                        | -60  | -    | -    | V     | $V_{DS} = 0, I_D = -1nA$                             |

| V(BR)G1 - G2           | Gate to Gate Breakdown Voltage        |                        | ±30  | ±45  | -    | V     | $I_{G}=\pm1\mu A$ , $I_{D}=I_{S}=0$ A (Open Circuit) |

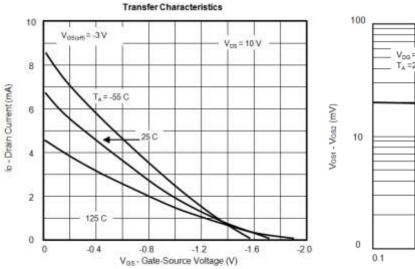

| V <sub>GS(OFF)</sub>   | Gate to Source Pinch-off Voltage      |                        | -1.5 | -    | -3.5 | V     | $V_{DS} = 15V, I_D = 1nA$                            |

| Vgs                    | Gate to Source Operating Voltage      |                        | -0.5 | -    | -3.5 | V     | $V_{DS} = 15V, I_D = 500 \mu A$                      |

|                        | Drain to Source<br>Saturation Current | LSK489A                | 2.5  | 5.5  | 8.5  | mA    | $V_{DG} = 15V, V_{GS} = 0$                           |

| I <sub>DSS</sub>       |                                       | LSK489B                | 8.0  | 11.5 | 15.0 | ШA    | $V_{\text{BG}} = 15V; V_{\text{GS}} = 0$             |

| I <sub>G</sub> Gate Op | Cata Operating Current                | Sate Operating Current |      | -2   | -25  | pА    | $V_{DG} = 15V, I_D = 200\mu A$                       |

|                        | Gale Operating Current                |                        |      | -0.8 | -10  | nA    | T <sub>A</sub> = 125°C                               |

| Igss                   | Gate to Source Leakage Current        |                        | -    | -    | -100 | pА    | $V_{DG} = -15V, V_{DS} = 0$                          |

| G <sub>fs</sub>        | Full Conductance Transconductance     |                        | 1500 | -    | -    | μS    | $V_{DG} = 15V, V_{GS} = 0, f = 1kHz$                 |

| G <sub>fs</sub>        | Transconductance                      |                        | 1000 | 1500 | -    | μS    | $V_{DG} = 15V, I_D = 500\mu A$                       |

| Gos                    | Full Output Conductance               |                        | -    | -    | 40   | μS    | $V_{DG} = 15V, V_{GS} = 0$                           |

| G <sub>OS</sub>        | Output Conductance                    |                        | -    | 1.8  | 2.7  | μS    | $V_{DG} = 15V, I_D = 200\mu A$                       |

#### **Package Dimensions**

#### Notes

- 1. Absolute maximum ratings are limiting values above which serviceability may be impaired.

- 2. Pulse width  $\leq 2_{ms}$ .

- 3. All MIN/TYP/MAX Limits are absolute values. Negative signs indicate electrical polarity only.

- 4. Derate 2.4 mW/°C above 25°C.

- 5. Derate 4 mW/°C above 25°C.

Information furnished by Linear Integrated Systems is believed to be accurate and reliable. However, no responsibility is assumed for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Linear Integrated Systems.

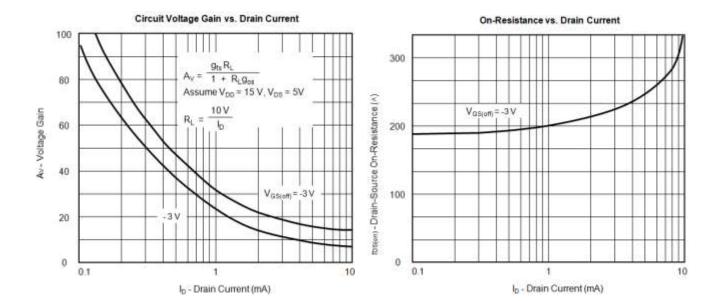

### **Typical Characteristics**

## **Typical Characteristics (Cont'd)**

## **Typical Characteristics (Cont'd)**