# 4-Phase DC/DC Expander with Internal Gate Drivers for Buck Converters

#### **FEATURES**

- Expands Up to Four Phases per Chip

- Up to 80V Input or Output Voltage

- Cascade with Multiple Chips for Very High Current Applications

- Supports Up to 18 Distinct Phases from 20° to 180°

- Phases Can Share Phase Angle

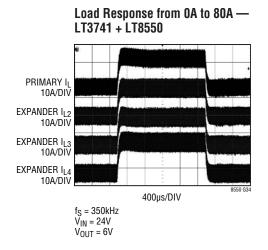

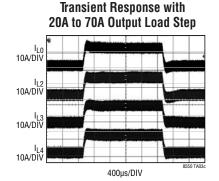

- Excellent DC and Transient Current Sharing

- Phase-Lockable Fixed Frequency 125kHz to 1MHz

- Supports Bidirectional Current Flow

- R<sub>SENSE</sub> or DCR Current Sensing

- Eliminates the Need to Route Sensitive Feedback and Control Signals

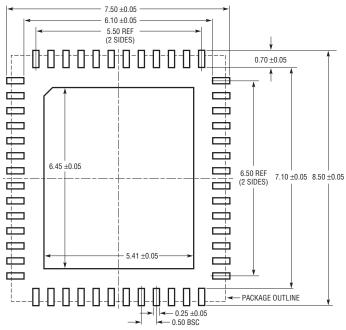

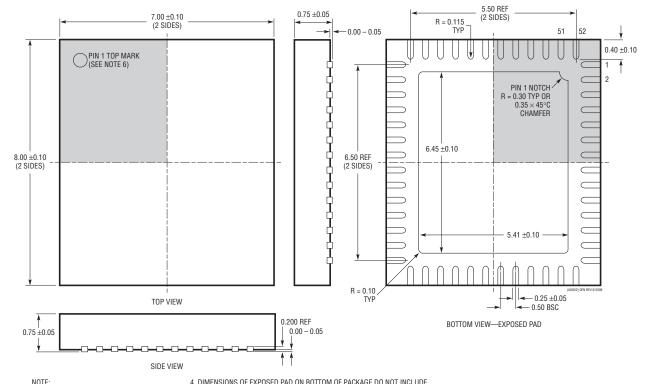

- 52-Lead (7mm × 8mm) QFN Package

#### **APPLICATIONS**

- High Current Distributed Power Systems

- Telecom, Datacom, and Storage Systems

- Industrial and Automotive

#### DESCRIPTION

The LT®8550 is a multiphase expander for synchronous buck DC/DC converters. It operates in tandem with any buck DC/DC converter to increase the load current capability by adding additional phases, which are clocked out-of-phase to reduce ripple current and filtering capacitance. It easily adds phases without the need to route sensitive feedback and control signals.

The LT8550 integrates gate drivers and can support up to four buck phases per device. Multiple LT8550's can be used for up to 18 phases. It accurately monitors and adjusts the current of each channel to achieve excellent DC and transient current sharing.

The LT8550 operates over a fixed frequency from 100kHz to 1MHz, or can be synchronized to an external clock.

All registered trademarks and trademarks are the property of their respective owners. Protected by U.S. Patents, including 9077244.

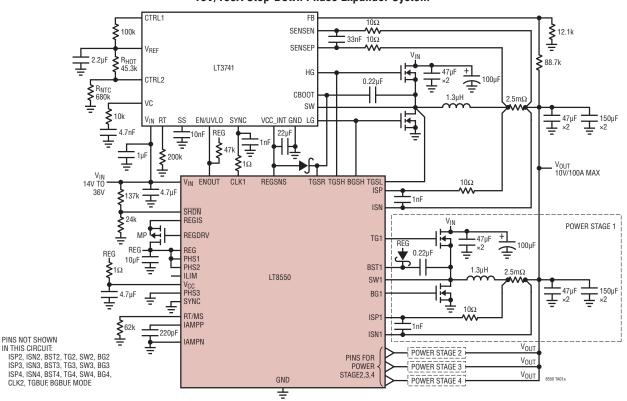

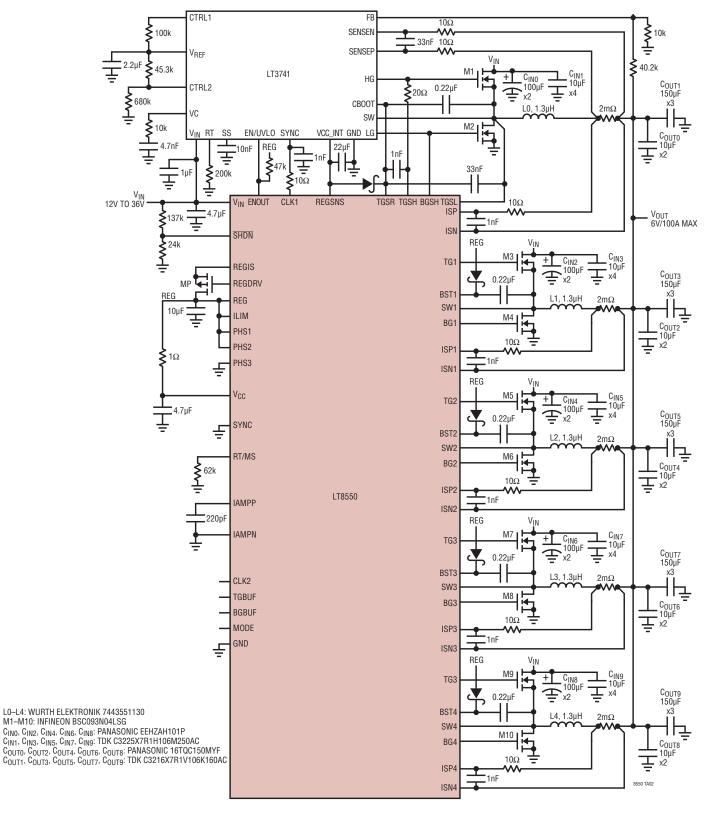

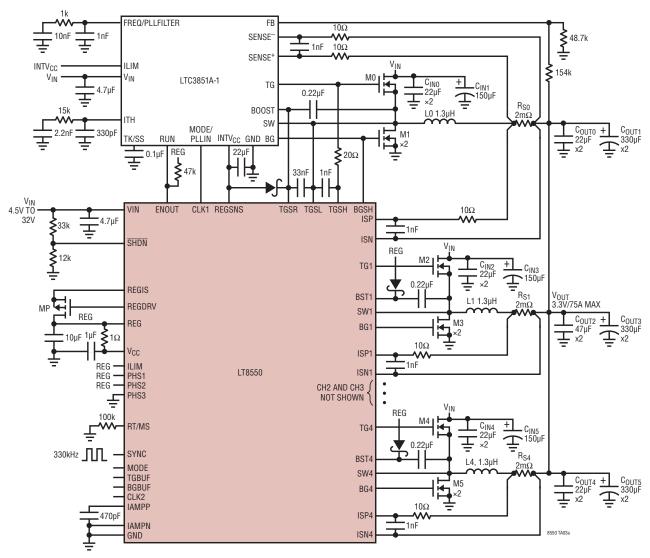

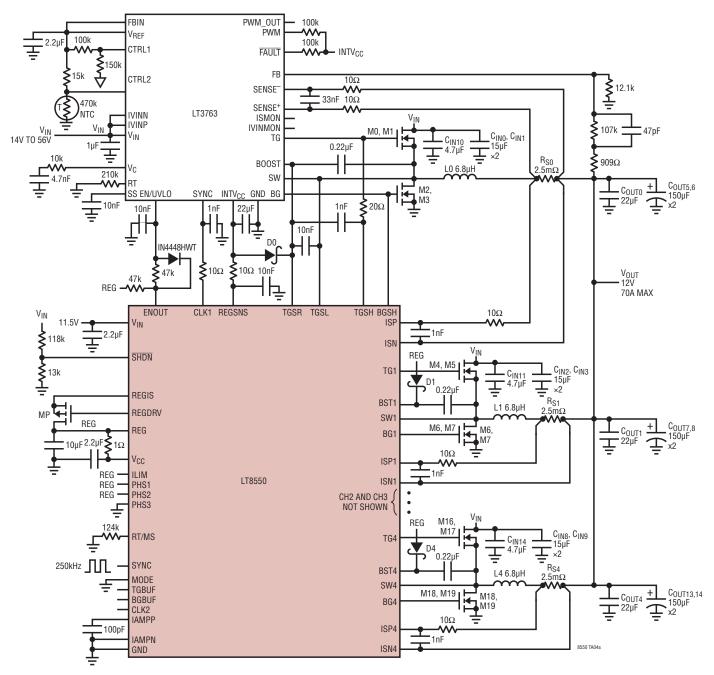

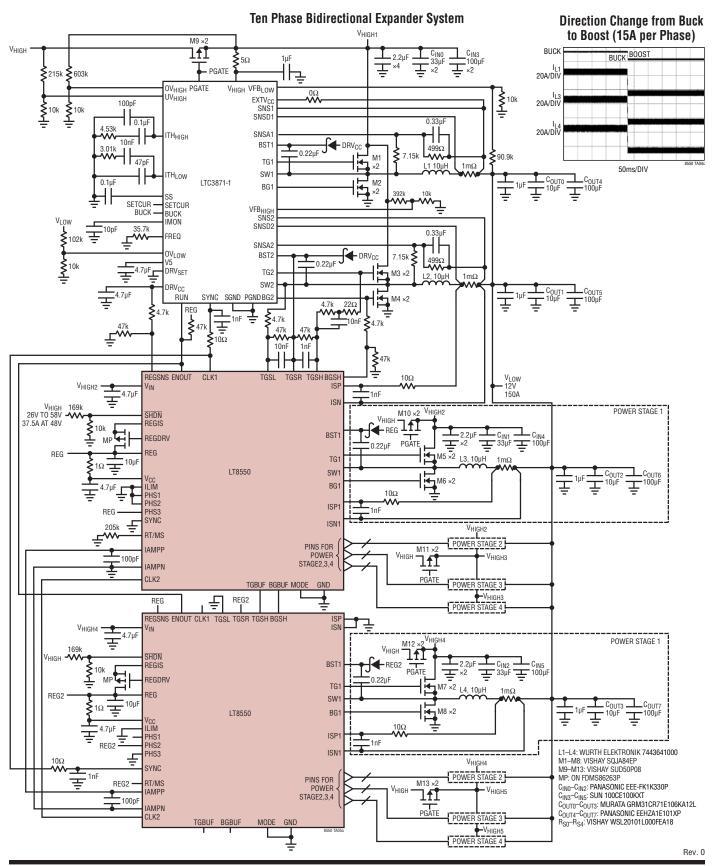

#### TYPICAL APPLICATION

#### 10V/100A Step-Down Phase Expander System

#### **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1) SW1/2/3/4......80V (Note 5) ISP1/2/3/4. ISN1/2/3/4. ISP. ISN. VIN, REGIS, REGDRV Voltage (Note 2)... -0.3V to 80V SHDN Voltage .....-0.3V to 70V TGSL Voltage ...... –3V to 80V TGSH Voltage.....-3V to 86V TG1/2/3/4, BST1/2/3/4, TGSR Voltage ..... -0.3V to 86V BG1/2/3/4, RT/MS, SYNC, PHS1/2/3, CLK1/2, REGSNS, IAMPP, ILIM, BGSH, BGBUF, TGBUF, ENOUT, MODE, V<sub>CC</sub>, REG, (BST-SW)1/2/3/4, (TG-SW)1/2/3/4, (V<sub>IN</sub>-REGDRV), (TGSR-TGSL), (TGSH-TGSL) Voltage ..... -0.3V to 6.0V IAMPN Voltage......-0.6V to 0.6V (ISP-ISN)1/2/3/4, (ISP-ISN) Voltage ....... -0.3V to 0.3V Operating Junction Temperature Range (Note 3) LT8550E ......-40°C to 125°C LT8550I ......-40°C to 125°C Storage Temperature Range .....--65°C to 150°C

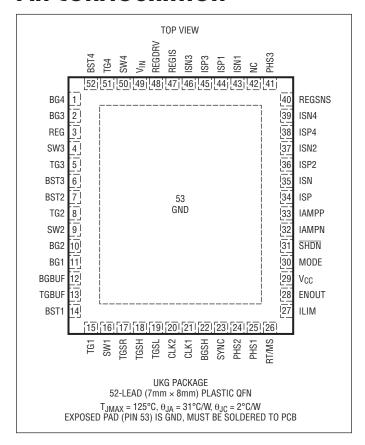

#### PIN CONFIGURATION

#### ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL    | PART MARKING* | PACKAGE DESCRIPTION            | TEMPERATURE RANGE |

|------------------|------------------|---------------|--------------------------------|-------------------|

| LT8550EUKG#PBF   | LT8550EUKG#TRPBF | 8550          | 52-PIN (7mm × 8mm) Plastic QFN | -40°C to 125°C    |

| LT8550IUKG#PBF   | LT8550IUKG#TRPBF | 8550          | 52-PIN (7mm × 8mm) Plastic QFN | -40°C to 125°C    |

Contact the factory for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_{IN} = 12V$ , REG = 5V, $V_{CC} = 5V$ , SHDN = High, unless otherwise noted.

| PARAMETER                                           | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | MIN                                                                  | TYP                                                                  | MAX                                                                  | UNITS                      |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------|

| V <sub>IN</sub> Operating Voltage Range             | For Min Spec V <sub>CC</sub> , REG = 0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | • | 3.6                                                                  |                                                                      | 80                                                                   | V                          |

| V <sub>IN</sub> Quiescent Current                   | REG = V <sub>CC</sub> = 5V, REGDRV REGIS Floating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |                                                                      | 800                                                                  |                                                                      | μА                         |

| V <sub>IN</sub> Quiescent Current in Shutdown       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |                                                                      |                                                                      | 2                                                                    | μA                         |

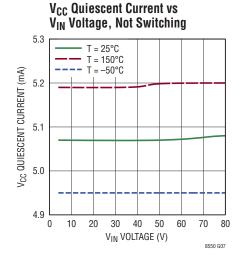

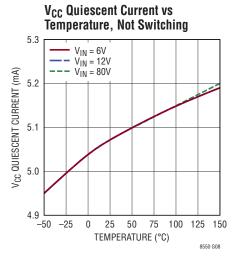

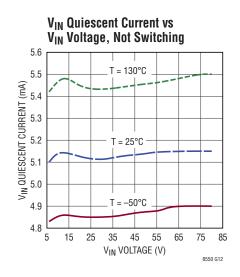

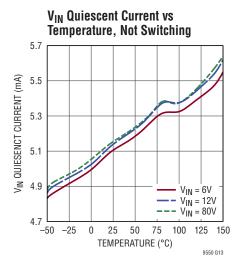

| V <sub>CC</sub> Quiescent Current                   | Not Switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |                                                                      | 5                                                                    |                                                                      | mA                         |

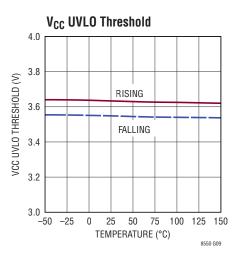

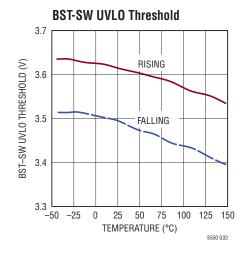

| V <sub>CC</sub> Undervoltage Lockout                | $V_{CC}$ Falling, REG = $V_{CC}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | • | 3.3                                                                  | 3.55                                                                 | 3.8                                                                  | V                          |

| V <sub>CC</sub> Undervoltage Lockout Hysteresis     | REG = V <sub>CC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |                                                                      | 0.1                                                                  |                                                                      | V                          |

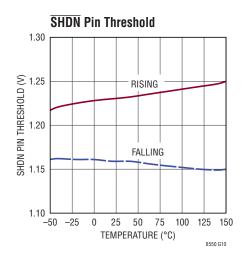

| SHDN Input Voltage High                             | SHDN Falling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | • | 1.05                                                                 | 1.15                                                                 | 1.25                                                                 | V                          |

| SHDN Input Voltage High Hysteresis                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |                                                                      | 60                                                                   |                                                                      | mV                         |

| SHDN Input Voltage Low                              | Device Disabled, Low Quiescent Current, V <sub>CC</sub> = 3V, REG = 3V                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | • |                                                                      |                                                                      | 0.3                                                                  | V                          |

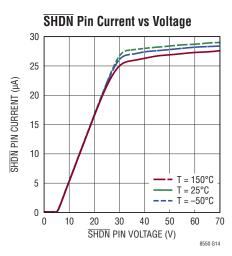

| SHDN Pin Bias Current                               | $V_{\overline{SHDN}} = 3V$<br>$V_{\overline{SHDN}} = 12V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |                                                                      | 0<br>8.5                                                             | 1<br>20                                                              | μA<br>μA                   |

| MODE Low Falling Threshold                          | Slave LT8550                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | • | 0.5                                                                  |                                                                      |                                                                      | V                          |

| MODE High Rising Threshold                          | Slave LT8550                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | • |                                                                      |                                                                      | 4.5                                                                  | V                          |

| MODE Output Voltage Low                             | Master LT8550, 200μA into MODE Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |                                                                      | 50                                                                   |                                                                      | mV                         |

| MODE Output Voltage High                            | Master LT8550, 20µA Out of MODE Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |                                                                      | 4.8                                                                  |                                                                      | V                          |

| MODE Pin Impedance in Middle State                  | Master LT8550                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |                                                                      | 9                                                                    |                                                                      | kΩ                         |

| ENOUT Output Voltage Low                            | Master LT8550, 1mA into ENOUT Pin, V <sub>CC</sub> , REG in UVLO                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |                                                                      | 60                                                                   |                                                                      | mV                         |

| ENOUT Leakage Current                               | ENOUT = 5V, REG, V <sub>CC</sub> = 3V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |                                                                      | 0.2                                                                  | 1                                                                    | μА                         |

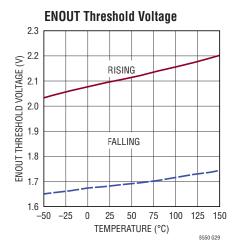

| ENOUT Rising Threshold                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |                                                                      | 2.1                                                                  |                                                                      | V                          |

| ENOUT Threshold Hysteresis                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |                                                                      | 0.4                                                                  |                                                                      | V                          |

| Current Sensing                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |                                                                      |                                                                      |                                                                      |                            |

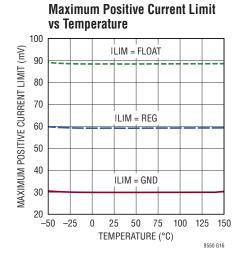

| Maximum Positive Current Sense Voltage, (ISPn-ISNn) | ILIM = 0V, ISNn = 12V, ISPn Rising ILIM = REG, ISNn = 12V, ISPn Rising ILIM = Float, ISNn = 12V, ISPn Rising                                                                                                                                                                                                                                                                                                                                                                                                                              | • | 27<br>56<br>84.5                                                     | 30<br>60<br>90                                                       | 32.5<br>64<br>95.5                                                   | mV<br>mV<br>mV             |

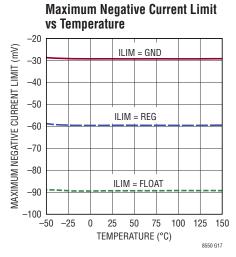

| Maximum Negative Current Sense Voltage, (ISNn-ISPn) | ILIM = 0V, ISNn = 12V, ISPn Falling ILIM = REG, ISNn = 12V, ISPn Falling ILIM = Float, ISNn = 12V, ISPn Falling                                                                                                                                                                                                                                                                                                                                                                                                                           | • | 26.5<br>55.5<br>84                                                   | 30<br>60<br>90                                                       | 33<br>64.5<br>96                                                     | mV<br>mV<br>mV             |

| ISP, ISN Common Mode Operating Voltage<br>Range     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | • | 0                                                                    |                                                                      | 80                                                                   | V                          |

| ISPn, ISNn Common Mode Operating<br>Voltage Range   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | • | 0                                                                    |                                                                      | 80                                                                   | V                          |

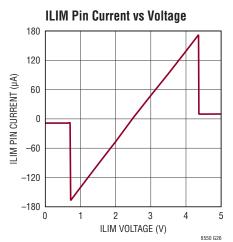

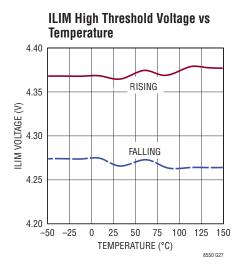

| ILIM High Rising Threshold                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | • |                                                                      |                                                                      | 4.65                                                                 | V                          |

| ILIM High Threshold Hysteresis                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |                                                                      | 90                                                                   |                                                                      | mV                         |

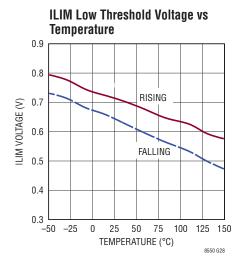

| ILIM Low Falling Threshold                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | • | 0.3                                                                  |                                                                      |                                                                      | V                          |

| ILIM Low Threshold Hysteresis                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |                                                                      | 80                                                                   |                                                                      | mV                         |

| ILIM Impedance at Floating                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |                                                                      | 11                                                                   |                                                                      | kΩ                         |

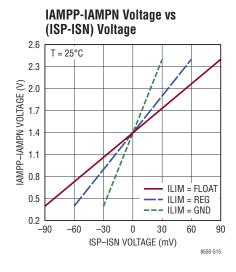

| IAMPP Output Voltage                                | (ISP-ISN) = 30mV, ILIM = 0V, Master LT8550, ISN = 12V<br>(ISP-ISN) = 0mV, ILIM = 0V, Master LT8550, ISN = 12V<br>(ISP-ISN) = -30mV, ILIM = 0V, Master LT8550, ISN = 12V<br>(ISP-ISN) = 60mV, ILIM = REG, Master LT8550, ISN = 12V<br>(ISP-ISN) = 0mV, ILIM = REG, Master LT8550, ISN = 12V<br>(ISP-ISN) = -60mV, ILIM = REG, Master LT8550, ISN = 12V<br>(ISP-ISN) = 90mV, ILIM = Float, Master LT8550, ISN = 12V<br>(ISP-ISN) = 0mV, ILIM = Float, Master LT8550, ISN = 12V<br>(ISP-ISN) = -90mV, ILIM = Float, Master LT8550, ISN = 12V | • | 2.33<br>1.33<br>0.33<br>2.33<br>1.35<br>0.34<br>2.33<br>1.35<br>0.34 | 2.40<br>1.40<br>0.40<br>2.40<br>1.40<br>0.40<br>2.40<br>1.40<br>0.40 | 2.47<br>1.47<br>0.47<br>2.47<br>1.45<br>0.46<br>2.47<br>1.45<br>0.46 | V<br>V<br>V<br>V<br>V<br>V |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_{IN} = 12V$ , REG = 5V, $V_{CC} = 5V$ , SHDN = High, unless otherwise noted.

| PARAMETER                                                                | CONDITIONS                                                                                                                                                                                                                                                                                                                   |   | MIN                                                 | TYP                  | MAX                                                 | UNITS                      |

|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------------------------------------------|----------------------|-----------------------------------------------------|----------------------------|

| (ISPn-ISNn) Voltage In Regulation                                        | IAMPP = 2.20V, IAMPN = 0V, ILIM = 0V, ISNn = 12V<br>IAMPP = 0.60V, IAMPN = 0V, ILIM = 0V, ISNn = 12V<br>IAMPP = 2.20V, IAMPN = 0V, ILIM = REG, ISNn = 12V<br>IAMPP = 0.60V, IAMPN = 0V, ILIM = REG, ISNn = 12V<br>IAMPP = 2.20V, IAMPN = 0V, ILIM = Float, ISNn = 12V<br>IAMPP = 0.60V, IAMPN = 0V, ILIM = Float, ISNn = 12V | • | 21.25<br>-26.75<br>45.0<br>-51.0<br>67.25<br>-76.75 |                      | 26.75<br>-21.25<br>51.0<br>-45.0<br>76.75<br>-67.25 | mV<br>mV<br>mV<br>mV<br>mV |

| (ISP-ISN) to IAMPP Voltage Gain                                          | ILIM = 0V, Master LT8550, ISN = 0V<br>ILIM = REG, Master LT8550, ISN = 0V<br>ILIM = FLOAT, Master LT8550, ISN = 0V                                                                                                                                                                                                           |   |                                                     | 33.3<br>16.7<br>11.1 |                                                     |                            |

| IAMPP Sourcing Current Limit                                             | (ISP-ISN) = 0mV, Master LT8550                                                                                                                                                                                                                                                                                               | • | 250                                                 |                      |                                                     | μА                         |

| IAMPP Sinking Current Limit                                              | (ISP-ISN) = 0mV, Master LT8550                                                                                                                                                                                                                                                                                               | • | 60                                                  |                      |                                                     | μА                         |

| IAMPP Load Regulation                                                    | I <sub>LOAD</sub> = -200μA to 50μA, Master LT8550                                                                                                                                                                                                                                                                            |   |                                                     |                      | 1                                                   | m۷                         |

| IAMPP Pin Bias Current                                                   | IAMPP = 1.2V, Slave LT8550<br>IAMPP = 2.4V, Slave LT8550                                                                                                                                                                                                                                                                     |   |                                                     | 3<br>6               |                                                     | μA<br>μA                   |

| Mismatch Between (ISPn-ISNn) and Master LT8550's (ISP-ISN) in Regulation | ILIM = REG                                                                                                                                                                                                                                                                                                                   | • | -6<br>-4.75                                         |                      | 6<br>4.75                                           | %<br>%                     |

| Mismatch Between (ISPn-ISNn) and Master LT8550's (ISP-ISN) in Regulation | ILIM = FLOAT                                                                                                                                                                                                                                                                                                                 | • | −6<br>−5.5                                          |                      | 6<br>5.5                                            | %<br>%                     |

| Mismatch Between (ISPn-ISNn) and Master LT8550's (ISP-ISN) in Regulation | ILIM = 0V                                                                                                                                                                                                                                                                                                                    | • | -10<br>-8                                           |                      | 10<br>8                                             | %<br>%                     |

| Oscillator                                                               |                                                                                                                                                                                                                                                                                                                              |   |                                                     |                      |                                                     |                            |

| CLK1 Frequency                                                           | RT/MS = $24.3k\Omega$ , Master LT8550<br>RT/MS = $100 k\Omega$ , Master LT8550<br>RT/MS = $249k\Omega$ , Master LT8550                                                                                                                                                                                                       | • | 900<br>236<br>90                                    | 1000<br>250<br>100   | 1100<br>264<br>110                                  | kHz<br>kHz<br>kHz          |

| Switching Frequency Range                                                | Free-Running<br>Synchronizing                                                                                                                                                                                                                                                                                                | • | 100<br>125                                          |                      | 1000<br>1000                                        | kHz<br>kHz                 |

| SYNC High Level for Synchronization                                      |                                                                                                                                                                                                                                                                                                                              | • | 1.2                                                 |                      |                                                     | V                          |

| SYNC Low Level for Synchronization                                       |                                                                                                                                                                                                                                                                                                                              | • |                                                     |                      | 0.8                                                 | V                          |

| CLK1, CLK2 Rise Time                                                     | C <sub>LOAD</sub> = 220pF, Master LT8550 (Note 4)                                                                                                                                                                                                                                                                            |   |                                                     | 7                    |                                                     | ns                         |

| CLK1, CLK2 Fall Time                                                     | C <sub>LOAD</sub> = 220pF, Master LT8550 (Note 4)                                                                                                                                                                                                                                                                            |   |                                                     | 5                    |                                                     | ns                         |

| CLK2 Rising Threshold                                                    | Slave LT8550                                                                                                                                                                                                                                                                                                                 | • |                                                     |                      | 4.0                                                 | V                          |

| CLK2 Falling Threshold                                                   | Slave LT8550                                                                                                                                                                                                                                                                                                                 | • | 1.0                                                 |                      |                                                     | V                          |

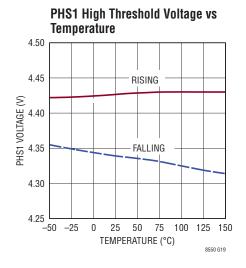

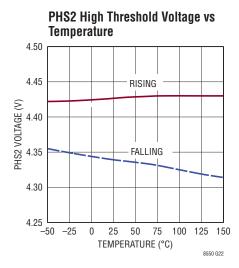

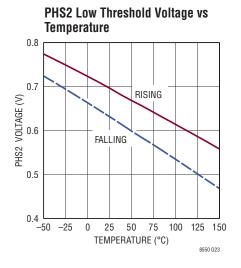

| PHS1, PHS2 High Rising Threshold                                         |                                                                                                                                                                                                                                                                                                                              | • |                                                     |                      | 4.65                                                | V                          |

| PHS1, PHS2 High Threshold Hysteresis                                     |                                                                                                                                                                                                                                                                                                                              |   |                                                     | 80                   |                                                     | mV                         |

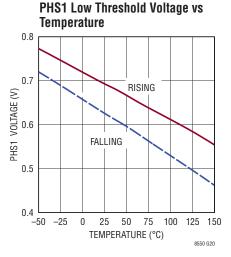

| PHS1, PHS2 Low Falling Threshold                                         |                                                                                                                                                                                                                                                                                                                              | • | 0.3                                                 |                      |                                                     | V                          |

| PHS1, PHS2 Low Threshold Hysteresis                                      |                                                                                                                                                                                                                                                                                                                              |   |                                                     | 80                   |                                                     | m۷                         |

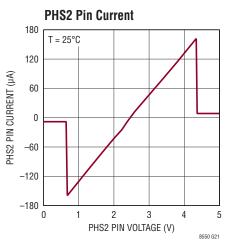

| PHS1, PHS2 Impedance at Floating                                         |                                                                                                                                                                                                                                                                                                                              |   |                                                     | 11                   |                                                     | kΩ                         |

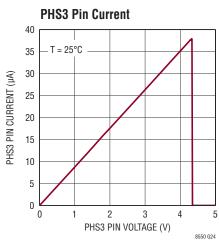

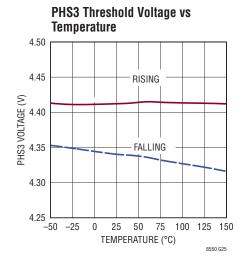

| PHS3 Rising Threshold                                                    |                                                                                                                                                                                                                                                                                                                              | • |                                                     |                      | 4.65                                                | V                          |

| PHS3 Threshold Hysteresis                                                |                                                                                                                                                                                                                                                                                                                              |   |                                                     | 80                   |                                                     | m۷                         |

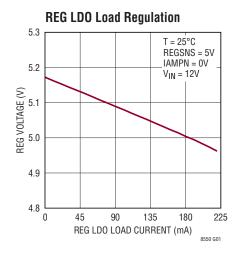

| REG LDO                                                                  |                                                                                                                                                                                                                                                                                                                              |   |                                                     |                      |                                                     |                            |

| REG Voltage                                                              | REGSNS = 5V, IAMPN = 0V, I <sub>LOAD</sub> = 45mA                                                                                                                                                                                                                                                                            | • | 4.9                                                 | 5.1                  | 5.3                                                 | V                          |

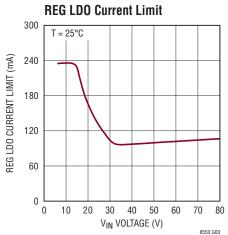

| REG LDO Current Limit                                                    | $V_{IN}$ = 12V, REGSNS = 5V, REG, $V_{CC}$ = 4V<br>$V_{IN}$ = 24V, REGSNS = 5V, REG, $V_{CC}$ = 4V                                                                                                                                                                                                                           |   |                                                     | 250<br>145           |                                                     | mA<br>mA                   |

| REG LDO Gate Drive Clamp Voltage                                         | (V <sub>IN</sub> – REGDRV) Voltage, REG, V <sub>CC</sub> = 4.5V                                                                                                                                                                                                                                                              |   |                                                     | 5.3                  |                                                     | V                          |

| REG Load Regulation                                                      | I <sub>LOAD</sub> = 0 to 100mA, REGSNS = 5V, IAMPN = 0V                                                                                                                                                                                                                                                                      |   |                                                     | 90                   |                                                     | mV                         |

| REGSNS Pin Bias Current                                                  | REGSNS = 5V                                                                                                                                                                                                                                                                                                                  |   |                                                     | 12                   |                                                     | μA                         |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_{IN} = 12V$ , REG = 5V, $V_{CC} = 5V$ , SHDN = High, unless otherwise noted.

| PARAMETER                          | CONDITIONS                                                                                                                 |   |     | TYP      | MAX | UNITS    |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---|-----|----------|-----|----------|

| Gate Drivers                       |                                                                                                                            |   |     |          |     |          |

| TG1, TG2, TG3, TG4 Rise Time       | C <sub>LOAD</sub> = 3.3nF, SWx = 0V, BSTx = 5V (Note 4)                                                                    |   |     | 30       |     | ns       |

| TG1, TG2, TG3, TG4 Fall Time       | C <sub>LOAD</sub> = 3.3nF, SWx = 0V, BSTx = 5V (Note 4)                                                                    |   |     | 20       |     | ns       |

| BG1, BG2, BG3, BG4 Rise Time       | C <sub>LOAD</sub> = 3.3nF (Note 4)                                                                                         |   |     | 50       |     | ns       |

| BG1, BG2, BG3, BG4 Fall Time       | C <sub>LOAD</sub> = 3.3nF (Note 4)                                                                                         |   |     | 27       |     | ns       |

| Bottom & Top Gate Non-Overlap Time | TG Falling to BG Rising, C <sub>LOAD</sub> = 3.3nF (Note 4)<br>BG Falling to TG Rising, C <sub>LOAD</sub> = 3.3nF (Note 4) |   |     | 85<br>80 |     | ns<br>ns |

| Bottom & Top Gate Minimum Off-Time | C <sub>LOAD</sub> = 3.3nF (Note 4)                                                                                         |   |     | 140      |     | ns       |

| Primary Gate Sensing               |                                                                                                                            | ` |     |          |     |          |

| BGSH Rising Threshold              |                                                                                                                            | • |     |          | 4.0 | V        |

| BGSH Falling Threshold             |                                                                                                                            | • | 1.0 |          |     | V        |

| BGSH Threshold Hysteresis          |                                                                                                                            |   |     | 1.4      |     | V        |

| BGSH to BGBUF Delay                | C <sub>LOAD</sub> = 220pF, Master LT8550 (Note 4)                                                                          |   |     | 45       |     | ns       |

| BGBUF Rise Time                    | C <sub>LOAD</sub> = 220pF, Master LT8550 (Note 4)                                                                          |   |     | 8        |     | ns       |

| BGBUF Fall Time                    | C <sub>LOAD</sub> = 220pF, Master LT8550 (Note 4)                                                                          |   |     | 6        |     | ns       |

| TGSH Rising Threshold              | TGSR = 5V, TGSL = 0V                                                                                                       | • |     |          | 4.0 | V        |

| TGSH Falling Threshold             | TGSR = 5V, TGSL = 0V                                                                                                       | • | 1.0 |          |     | V        |

| TGSH Threshold Hysteresis          |                                                                                                                            |   |     | 1.4      |     | V        |

| TGSH to TGBUF Delay                | C <sub>LOAD</sub> = 220pF, Master LT8550 (Note 4)                                                                          |   |     | 45       |     | ns       |

| TGBUF Rise Time                    | C <sub>LOAD</sub> = 220pF, Master LT8550 (Note 4)                                                                          |   |     | 8        |     | ns       |

| TGBUF Fall Time                    | C <sub>LOAD</sub> = 220pF, Master LT8550 (Note 4)                                                                          |   |     | 6        |     | ns       |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating Condition for extended periods may affect device reliability and lifetime.

**Note 2:** Do not apply a positive or negative voltage or current source to REGDRV, BG1, BG2, BG3, BG4, TG1, TG2, TG3 and TG4, otherwise permanent damage may occur.

**Note 3:** The LT8550E is guaranteed to meet performance specifications from 0°C to 125°C junction temperature. Specifications over the –40°C to 125°C operating junction temperature range are assured by design,

characterization and correlation with statistical process controls. The LT8550l is guaranteed to meet performance specifications from  $-40^{\circ}$ C to 125°C junction temperature.

**Note 4:** Rise and fall times are measured using 10% and 90% levels. Delay times are measured using 50% levels.

**Note 5:** Negative voltages on SW1/2/3/4 pins are limited, in an application, by the body diodes of the external NMOS devices, or the parallel Schottky diodes when present. The SW1/2/3/4 pins are tolerant of these negative voltages in excess of one diode drop below ground, guaranteed by design.

### TYPICAL PERFORMANCE CHARACTERISTICS TA = 25°C, unless otherwise noted.

## TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C, unless otherwise noted.

## TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C, unless otherwise noted.

## TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C, unless otherwise noted.

\_50 <u>\_25</u> 0

# Oscillator Frequency vs Temperature 600 (2HX) 400 RT = 49.9K RT = 100K RT = 249K

75 100

TEMPERATURE (°C)

125 150

#### PIN FUNCTIONS (QFN)

**REG (Pin 3):** Output of REG LDO. Power supply for gate drivers. Decouple this pin to ground with a minimum 4.7μF low ESR ceramic capacitor. Connect this pin to the external PMOS drain side.

**BG1**, **BG2**, **BG3**, **BG4** (**Pins 11**, **10**, **2**, **1**): Bottom Gate Driver Output. These pins drive the gates of the bottom N-channel MOSFETs. Voltage swing at these pins is from ground to REG.

**BGBUF (Pin 12):** Logic Output Pin. This pin is pulled up to REG when BGSH is at logic high, and it is pulled down to ground when BGSH is at logic low. For a slave LT8550, leave this pin floating. See the Applications Information section for more information.

**TGBUF (Pin 13):** Logic Output Pin. For a master LT8550, this pin is pulled up to REG voltage when (TGSH-TGSL) is at logic high, and it is pulled down to ground when (TGSH-TGSL) is at logic low. For a slave LT8550, leave this pin floating. See the Applications Information section for more information.

**BST1**, **BST2**, **BST3**, **BST4** (**Pins 14**, **7**, **6**, **52**): Boosted Floating Driver Supply. The (+) terminal of the boost-strap capacitor is connected to this pin. This pin swings from a diode voltage drop below REG up to  $V_{IN}$  + REG.

**TG1**, **TG2**, **TG3**, **TG4** (**Pins 15**, **8**, **5**, **51**): Top Gate Driver Output. This is the output of a floating driver with a voltage swing equal to REG superimposed on the switch node voltage.

**SW1**, **SW2**, **SW3**, **SW4** (Pins 16, 9, 4, 50): Switch Node. Voltage swing at these pins is from a diode voltage drop below ground to  $V_{\text{IN}}$ .

**TGSR (Pin 17):** The Rail of Primary Channel Top Gate Sense Circuit. For a master LT8550, connect this pin to the primary channel top gate driver's boost node. This pin, combined with TGSH, TGSL pins, is to sense the primary channel top MOSFET's state. For a slave LT8550, connect this pin to REG.

**TGSH (Pin 18):** Input of Primary Channel Top Gate Sense Circuit. For a master LT8550, connect this pin to the primary channel top MOSFET's gate. This pin, combined with TGSR, TGSL pins, is to sense the primary channel

top MOSFET's state. For a slave LT8550, connect this pin to the master LT8550's TGBUF pin.

**TGSL (Pin 19):** Lower Rail of Primary Channel Top Gate Sense Circuit. For a master LT8550, connect this pin to the primary channel top MOSFET's source. This pin, combined with TGSR, TGSH pins, is to sense the primary channel top MOSFET's state. For a slave LT8550, connect this pin to ground.

**CLK1**, **CLK2** (**Pins 21**, **20**): Clock Pin. These two pins are used to synchronize the primary channel to all other channels. See the Applications Information section for more information.

**BGSH (Pin 22):** Logic Input of Primary Channel Bottom Gate Sense Circuit. For a master LT8550, connect this pin to the primary channel bottom MOSFET's gate. This pin is to sense the primary channel bottom MOSFET's state. For a slave LT8550, connect this pin to the master LT8550's BGBUF pin.

**SYNC (Pin 23):** To synchronize the switching frequency to an outside clock, simply drive this pin with a clock. The high voltage level of the clock must exceed 1.2V, and the low level must be less than 0.8V. Drive this pin to less than 0.8V to revert to the internal free-running clock. See the Typical Applications section.

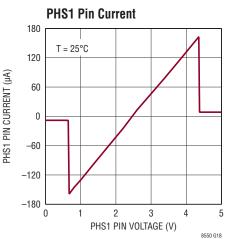

PHS1, PHS2 (Pins 25, 24): Phase Selection Pin. These pins, combined with PHS3 and RT/MS, set the switching frequency and the phase of each channel. PHS1 and PHS2 are three-level input pins, they can be floated, set to REG or ground. When the PHS1/PHS2 is floating, add a 1nF cap from PHS1/PHS2 to ground. See the Operation section for more information.

**RT/MS (Pin 26):** Timing Resistor Pin and Master Slave Selection Pin. This pin, combined with PHS1, PHS2 and PHS3, sets the switching frequency and the phase of each channel. Connecting a resistor to ground sets the chip as master LT8550. Connecting this pin to the REG pin sets the chip as slave LT8550. See the Applications Information section for more information.

#### PIN FUNCTIONS (QFN)

**ILIM (Pin 27):** Maximum Current Sense Voltage Programming Pin. This pin is used to set the maximum sense voltage in the primary channel current sense amplifier and expanded channel current sense amplifier. It is a three level input pin. Connecting this pin to ground, REG or leaving it floating sets the maximum current sense voltage to 30mV, 60mV or 90mV, respectively. When the ILIM is floating, add a 1nF cap from the ILIM to ground.

**ENOUT (Pin 28):** For a master LT8550, this pin is an opendrain logic output pin. For a slave LT8550, it is an input pin. See more details in ENOUT Connection Section.

$V_{CC}$  (Pin 29): Power supply for control circuits. Decouple this pin to ground with a minimum  $1\mu F$  low ESR ceramic capacitor.  $V_{CC}$  and REG need to be connected through a  $1\Omega$  resistor.

**MODE (Pin 30):** Stage Shedding Selection Pin. Connecting this pin to GND disables stage shedding feature. See the Operation section for more information.

**SHDN (Pin 31):** Shutdown Pin. This pin is used to enable/disable the chip. Drive below 0.3V to disable the chip. Drive above 1.2V (typical) to activate the chip. Do not float this pin.

**IAMPN (Pin 32):** For a master LT8550, connect this pin to local ground. For a slave LT8550, connect this pin to the master LT8550's IAMPN. See the Applications Information section for more information.

**IAMPP (Pin 33):** For a master LT8550, this is an output pin. It is the buffered signal of the Primary Channel Current Sense Amplifier output. For a slave LT8550, this is an input pin. When multiple LT8550s are used, connect all IAMPP pins together. See the Applications Information section for more information.

**ISP (Pin 34):** Primary Channel Current Sense Amplifier Input. The (+) input to the current sense amplifier is normally connected to DCR sensing network or current sensing resistor. This pin is only used for a master LT8550. Ground this pin for a slave LT8550.

**ISN (Pin 35):** Primary Channel Current Sense Amplifier Input. The (–) input to the current sense amplifier is normally connected to DCR sensing networks or current sensing resistors. This pin is only used for a master LT8550. Ground this pin for a slave LT8550.

**REGSNS (Pin 40):** REG LDO Voltage Sense Pin. Connect this pin to the primary channel gate driver power supply pin.

**PHS3 (Pin 41):** Phase Select Pin. This pin, combined with PHS1, PHS2 and RT/MS, set the switching frequency and the phase of each channel. PHS3 connects to REG or ground. See the Operation section for more information.

**NC (Pin 42):** No Connection. Leave this pin floating or connect to any adjacent pin.

**ISN1**, **ISN2**, **ISN3**, **ISN4** (**Pins 43**, **37**, **46**, **39**): Expanded Channel Current Sense Amplifier (–) Input. The (–) input to the current sense amplifier is normally connected to DCR sensing network or current sensing resistor.

**ISP1**, **ISP2**, **ISP3**, **ISP4** (**Pins 44**, **36**, **45**, **38**): Expanded Channel Current Sense Amplifier (+) Input. The (+) input to the current sense amplifier is normally connected to DCR sensing network or current sensing resistor.

**REGIS (Pin 47):** REG LDO Current Sense Pin. Connect this pin to the external PMOS source side.

**REGDRV (Pin 48):** Gate Driver Output for REG LDO. Connect this pin to the external PMOS gate.

$V_{IN}$  (Pin 49): Input Supply Pin. Must be locally bypassed to ground.

**GND (Exposed Pad Pin 53/Pin 27):** Ground. Tie directly to local ground plane.

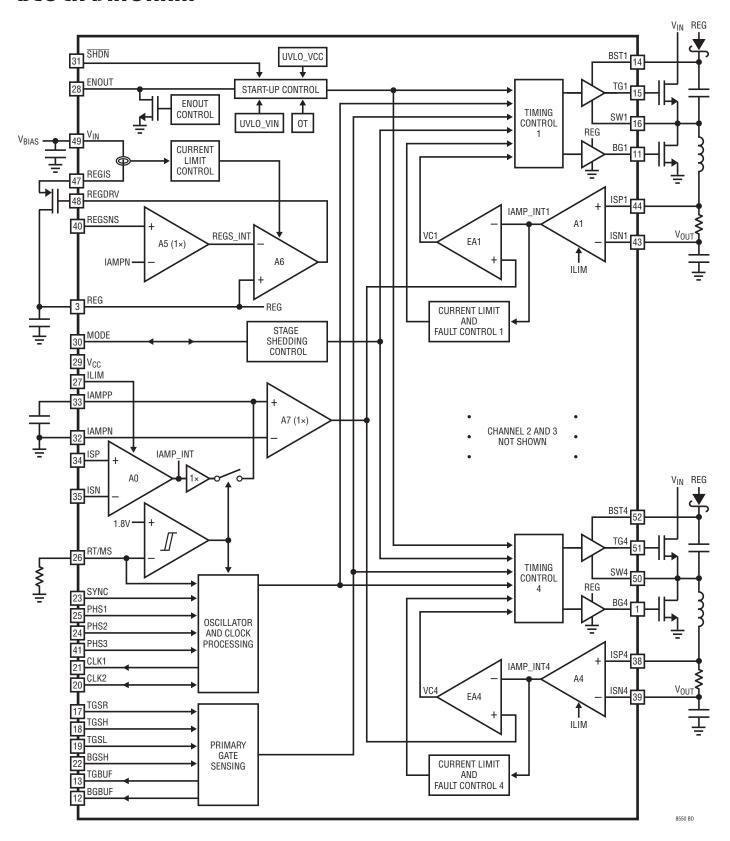

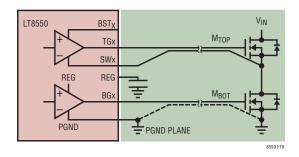

#### **BLOCK DIAGRAM**

#### Introduction

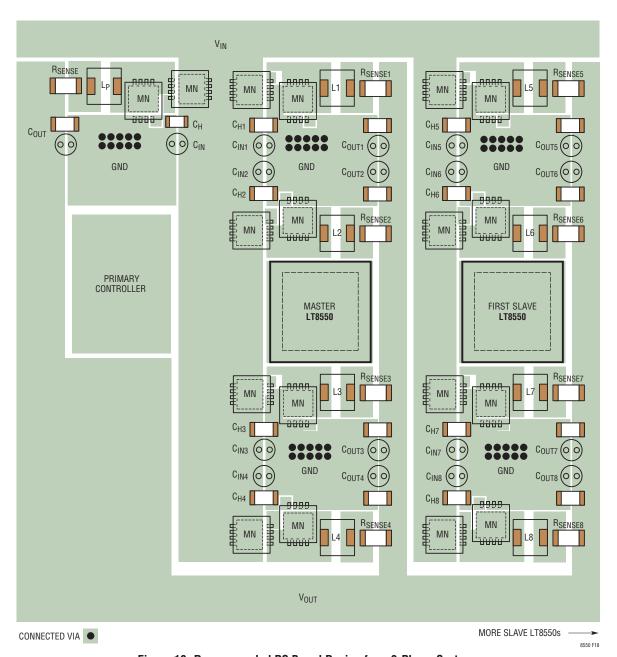

The LT8550 is a multiphase expander for synchronous buck controllers. Each LT8550, which has 8 gate drivers, can expand up to four phases. Multiple LT8550s can also be used together in a system, and up to 18 different phases can be supported. In addition, the part supports more than one phase per phase angle.

The ADI proprietary control architecture allows the LT8550 to cycle-by-cycle duplicate the operation of a buck controller (named as Primary Controller). The LT8550 measures the primary controller's inductor current as well as primary controller's gate driver operation timing, and at the same time, accurately monitors and adjusts the current of each expanded channel to achieve excellent DC and transient current sharing. The current sharing accuracy is  $\pm 6\%$ ,  $\pm 6\%$  and  $\pm 10\%$  over temperature when ILIM set at REG, Float and GND, respectively.

In normal operation, the primary buck regulator's switch current is compared with the expanded channel's switch current by the EA (EA1/2/3/4 in the Block Diagram). When the primary channel's current increases, the VC (VC1/2/3/4 in the Block Diagram) voltage also increases, which in turn controls the expanded channel's switches to increase the current until the expanded channel's current matches the primary channel's current.

#### System with Multiple LT8550s

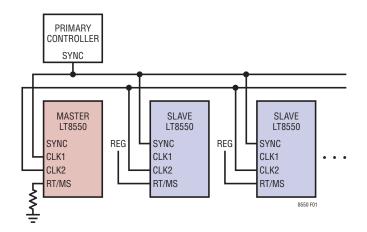

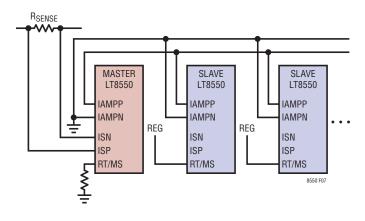

One LT8550 can expand up to four channels. This configuration can provide enough power for most high current applications. However, for even higher power applications, the LT8550 can be configured for multi-chip operation. When two or more LT8550s are used together in a system, one LT8550 is the master and other LT8550s are slaves. Connecting a resistor from the RT/MS pin to ground sets the chip as the master and connecting the RT/MS pin to REG sets the chip as a slave. When only one LT8550 is used in a system, this LT8550 needs to be set as a master.

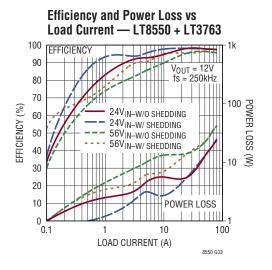

#### Stage Shedding Mode

The MODE pin is dedicated for the Stage Shedding feature. The MODE pin is an output pin for a master LT8550, and it is an input pin for a slave LT8550.

For a master LT8550, when the MODE pin is floating, the LT8550 operates in Stage Shedding mode at light loads. In this case, when the (ISP-ISN) peak voltage is lower than a certain value for some period of time, the part turns off channels 1 and 3 to increase overall efficiency. After channel 1 and 3 are off, if the (ISP-ISN) peak voltage is still lower than a certain value for some period of time, the part also turns off channel 4 and only leaves channel 2 running. For bidirectional applications, stage shedding should be disabled when the current is regulated in the reverse direction. Driving the MODE pin below 0.5V disables the Stage Shedding feature.

In a multiple LT8550s system, all chips' MODE pins need to be connected together and left floating if the Stage Shedding feature is desired. The master LT8550 senses the (ISP-ISN) voltage to decide proper operation. The slave LT8550s follows the master LT8550's Stage Shedding operation with some delay. Driving all chips' MODE pins below 0.5V disables the Stage Shedding feature.

#### **Clock Scheme**

This section discusses the LT8550 clock scheme for a multiple LT8550 system. This clock scheme can easily apply to a single LT8550 system by ignoring the slave LT8550s.

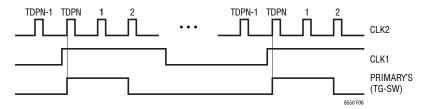

A master LT8550 generates two clock signals: CLK1 and CLK2. In a multiple LT8550 system, as shown in Figure 1, all LT8550s' CLK2 pins need to be connected together. The CLK1 signal is at the fundamental switching frequency (Refer to Internal Oscillator and SYNC Pin and Clock Synchronization sections for more information), and it is used to synchronize the primary buck controller and the slaves (in Figure 1). Under normal operation, the CLK2 frequency is at the CLK1 frequency times the total distinct phase number (TDPN), as shown in Figure 2. The number shown above the CLK2 pulses in Figure 2 is called the phase angle number (PAN).

The total distinct phase number is programmed through the master LT8550's PHS1, PHS2 and PHS3 pins, according to Table 1. There is a delay locked loop in the chip which can force the primary controller's (TG-SW) rising edge to align with the pulse whose phase angle number equals the TDPN (in Figure 2).

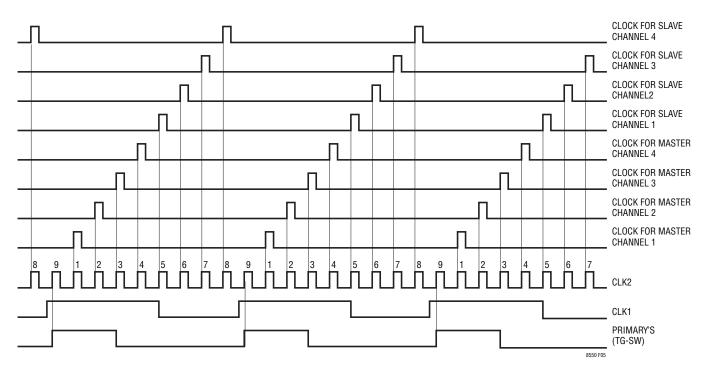

Each expanded channel chooses one pulse from CLK2 in one CLK1 clock cycle. The rising edge of this chosen pulse aligns with the corresponding channel's top gate turn on edge with a very short delay. The master LT8550's channel 1 to channel 4 always choose the pulses whose phase angle number equals 1 to 4, respectively. Four channels of a slave LT8550 choose pulses with four consecutive phase angles. The phase angle number of the slave LT8550's channel 1 pulse is also programmed through PHS1, PHS2 and PHS3 pins, according to Table 1, and the pulses of the slave LT8550's channel 2, channel 3 and channel 4 have the next three phase angle number in succession.

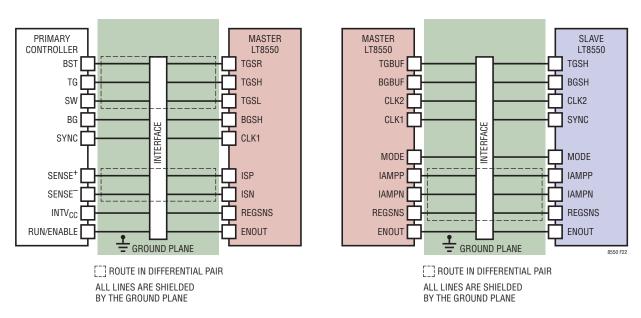

Figure 1. Clock Configuration in a Multiple LT8550 System

Table 2 shows the PHS1, PHS2 and PHS3 connections for a two LT8550 system with a total of 9 phases, including the primary controller's phase, as an example. The

primary controller uses the CLK1 signal. The clocks used by the eight expanded channels are shown in Figure 3.

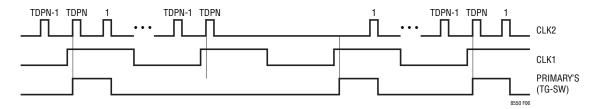

When the primary controller skips one or more pulses, the expanded channels also skip the same number of pulse(s). This function is realized by CLK2. As shown in Figure 4, when the primary controller skips one (TG-SW) pulse, the CLK2 also skips a group of pulses with phase number from 1 to TDPN.

Table 1. Table for Programming Total Distinct Phase Number (TDPN) and Phase Angle Number (PAN)

| (1211) |          |          |                 | PAN of Slave    |

|--------|----------|----------|-----------------|-----------------|

| PHS3   | PHS2     | PHS1     | TDPN for Master | Channel 1 Pulse |

| GND    | GND      | GND      | NA              | 1               |

| GND    | GND      | REG      | 2               | 2               |

| GND    | GND      | Floating | 3               | 3               |

| GND    | REG      | GND      | 4               | 4               |

| GND    | REG      | REG      | 5               | 5               |

| GND    | REG      | Floating | 6               | 6               |

| GND    | Floating | GND      | 7               | 7               |

| GND    | Floating | REG      | 8               | 8               |

| GND    | Floating | Floating | 9               | 9               |

| REG    | GND      | GND      | 10              | 10              |

| REG    | GND      | REG      | 11              | 11              |

| REG    | GND      | Floating | 12              | 12              |

| REG    | REG      | GND      | 13              | 13              |

| REG    | REG      | REG      | 14              | 14              |

| REG    | REG      | Floating | 15              | 15              |

| REG    | Floating | GND      | 16              | 16              |

| REG    | Floating | REG      | 17              | 17              |

| REG    | Floating | Floating | 18              | 18              |

Table 2. Design Example for a 9-Phase Application

| Table 2. Design Example for a 9-1 hase Application |      |          |          |                                  |  |  |  |

|----------------------------------------------------|------|----------|----------|----------------------------------|--|--|--|

|                                                    | PHS3 | PHS2     | PHS1     | PAN for Channel<br>1, 2, 3 and 4 |  |  |  |

| Master LT8550                                      | GND  | Floating | Floating | 1,2,3,4                          |  |  |  |

| Slave LT8550                                       | GND  | REG      | REG      | 5,6,7,8                          |  |  |  |

Figure 2. CLK1, CLK2 and Primary's (TG-SW)

Figure 3. Clock Waveforms for a Two LT8550 System

Figure 4. CLK1, CLK2 and Primary's (TG-SW) Waveforms for Pulse Skipping

#### **Primary Controller's Switch State Detection**

This section discusses a system with multiple LT8550s. For a single LT8550 system, simply ignore the slave LT8550s in this discussion.

The primary controller's switch states are detected by the master LT8550, and this information is used by both master and slave LT8550s.

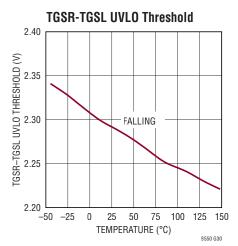

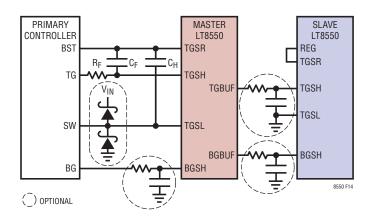

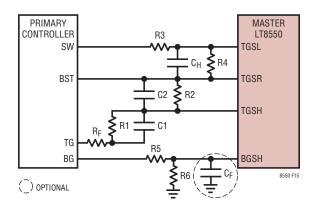

The primary controller's top switch state is sensed by the master LT8550's TGSR, TGSH, and TGSL pins, as shown in Figure 5. This floating top gate logic signal is converted to a ground based logic signal, and outputted to the TGBUF pin. The master LT8550's TGBUF is then connected to the downstream slaves' TGSH, as shown in Figure 5. The slave's TGSR and TGSL are connected to the REG and GND respectively. If the (TGSR-TGSL) voltage is less than 2.3V (typical), the TGBUF pin will be forced to ground for both of the master and slave LT8550. See the Applications Information section for more information.

A similar method is used for the primary controller's bottom switch state detection, also shown in Figure 5. Since the primary BG is a ground based signal, only one pin (BGSH) is needed for the primary's BG detection.

Since the master LT8550 passes the primary's switch states to the slaves, this avoids routing the primary's noisy BST, TG, SW and BG signals around the board.

#### MASTER SLAVE SLAVE LT8550 LT8550 LT8550 TGBUF TGBUF TGBUF REG REG **BGBUF BGBUF BGBUF** PRIMARY CONTROLLER TGSR TGSR TGSR BS<sub>1</sub> TGSH TGSH **TGSH** TGSL TGSL SW TGSL BGSH BG **BGSH BGSH** RT/MS RT/MS RT/MS

Figure 5. Gate Sensing in a Multiple LT8550 System

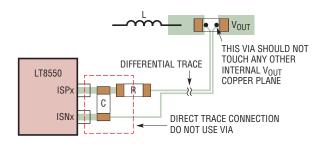

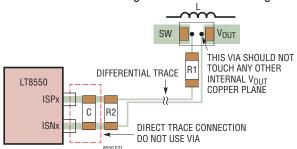

#### **Primary Controller's Inductor Current Sensing**

This section discusses a system with multiple LT8550s. For a single LT8550 system, simply ignore the slave LT8550s in this discussion.

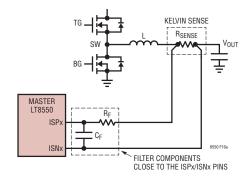

The primary controller's inductor current is detected by the master LT8550, and this information is used by both the master and slave LT8550s.

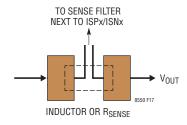

As shown in Figure 6, the primary controller's inductor current is detected by the master LT8550's ISP and ISN pins. This signal is amplified, and then outputted to the master LT8550's IAMPP pin. For stability purposes, a cap is required from the IAMPP to GND, and total capacitance must be between 100pF and 470pF. For a slave LT8550, the ISP and ISN pins are not used and should be grounded, and the IAMPP is an input pin. To pass the primary's inductor current information from the master LT8550 to the slave LT8550s, all LT8550s' IAMPP and IAMPN pins are connected together, respectively. Connect the IAMPN pins to the master LT8550's local ground. The IAMPP and IAMPN are connected to the inputs of a unity gain differential sense amplify (A7 in the Block Diagram). See the Applications Information section for more information.

The signal across the primary inductor current sense resistor is only tens of mV. By passing the amplified current signal from the master to the slaves, routing sensitive small signals around the board is avoided.

Figure 6. Primary Regulator's Switch Current Sensing in Multiple LT8550 System

#### **Current Sensing Gain, Limit and Fault**

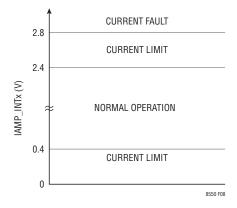

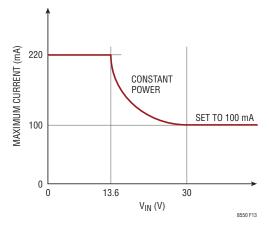

The gain of five current amplifiers (A0 to A4 in the Block Diagram) has three gain levels which are set by the ILIM pin. Connecting the ILIM pin to GND/REG/Floating sets the gain to 33.3/16.7/11.1, respectively. The outputs of these amplifiers are called IAMP\_INT/IMAP\_INTx (in the Block Diagram). The relation between the IAMP\_INT/IAMP\_INTx and the (ISP-ISN)/(ISPx-ISNx) are shown in Figure 7. There is a 1.4V offset. For expanded channels, the IAMP\_INTx's value determines the current limit and current fault as shown in Figure 8.

Figure 7. Current Sensing Amplifier Output Vs. Input at Three Different Gains

Figure 8. IAMP\_INTx Voltage for Current Limit and Current Fault

When the IAMP\_INTx reaches 2.4V but lower than 2.8V, or if it drops below 0.4V, the corresponding channel enters current limit. When the current limit condition is detected, both corresponding channel's BGx and TGx are pulled low immediately. The channel resumes switching at the next clock rising edge after the current limit condition is removed. The corresponding (ISPx-ISNx) voltages at current limit are indicated in Figure 7.

When the IAMP\_INTx reaches 2.8V, the corresponding channel enters current fault. When the current fault condition is detected, the corresponding channel enters into a fault sequence which is described in more detail in the Fault Sequence section.

#### **Shutdown and Start-Up**

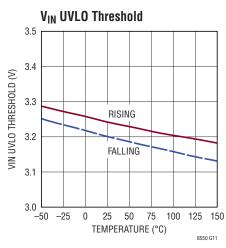

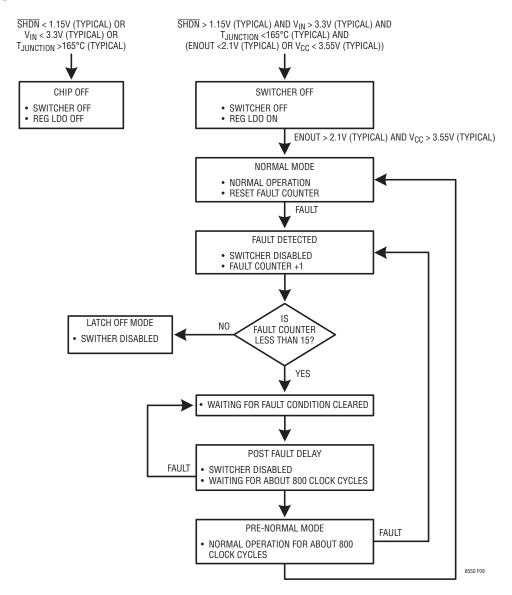

Figure 9 illustrates the start-up sequence for the LT8550. The shutdown pin for the chip is \$\overline{SHDN}\$. When it is driven below 0.3V, the chip is disabled (chip off state) and quiescent current is minimal. Increasing the \$\overline{SHDN}\$ voltage can increase quiescent current but will not enable the chip until \$\overline{SHDN}\$ is driven above 1.15V (typical) after which the REG LD0 is enabled (switcher off state).

Starting up the switching regulator happens after  $V_{CC}$  has risen above 3.55V (typical) and the ENOUT has been driven above 2.1V (typical). For a master LT8550, the ENOUT is an open drain pin. When  $V_{CC}$  is lower than 3.55V, the ENOUT is pulled to GND to disable switching. For a slave LT8550, the ENOUT is always a high impedance input pin.

#### **Fault Sequence**

The LT8550 activates a fault sequence (see Figure 9) when IAMP\_INTx is higher than 2.8V, which is the fault condition for a LT8550. The fault event is independent of channels, which means that the fault condition occurring in one channel won't directly affect other channels. If one of these conditions occurs for a certain channel, the corresponding channel's gate driver outputs are pulled low. If one of the LT8550's channels enters latch off mode (see Figure 9), only restarting the whole chip will reactivate the channel.

Figure 9. Start-Up and Fault Sequence

#### **ENOUT Connection**

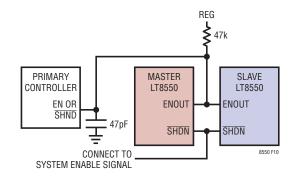

For a master LT8550, this pin is an open-drain logic output pin. The master LT8550's ENOUT pin is pulled to ground when it is not ready for switching. For a slave LT8550, this pin is an input pin. For both master and slave LT8550s, when the ENOUT pin is lower than 2.1V (typical), the gate driver's switching activity is disabled.

When a master LT8550 is not ready for switching, it is desired to disable the primary controller and the slave LT8550s' switching activity. Figure 10 is one recommended configuration.

Figure 10. Recommended ENOUT Connection

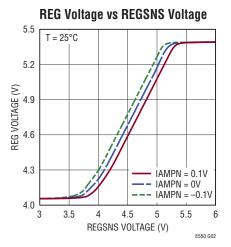

#### REG LDO and V<sub>CC</sub> Power

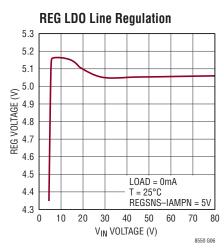

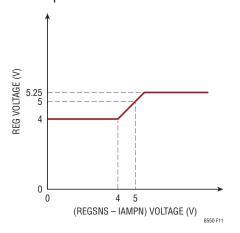

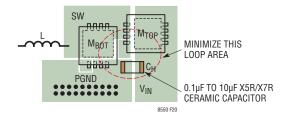

The REG LDO supplies the power for the gate drivers and output stages of CLK1, CLK2, TGBUF and BGBUF. Once the SHDN pin is higher than 1.15V, REG will be regulated to 4V (typical), (REGSNS – IAMPN) voltage, or 5.25V (typical) from  $V_{IN}$ , depending on whether (REGSNS – IAMPN) is lower than 4V, or higher than 4V but lower than 5.25V, or higher than 5.25V respectively, as shown in Figure 11. The REG pin must be bypassed to power ground with an X5R or X7R ceramic capacitor of at least 4.7µF placed close to the REG pin.

Figure 11. REG Voltage vs REGSNS Voltage

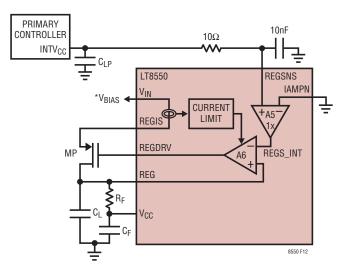

$V_{CC}$  is the power supply for most of the internal circuitry and it's connected to REG through an external filter (R<sub>F</sub>, C<sub>F</sub>) to filter the switching noise in REG, as shown in Figure 12, the filter should be placed close to the  $V_{CC}$  pin, typical value of R<sub>F</sub> =  $1\Omega$ ,C<sub>F</sub> =  $1\mu$ F is recommended. The internal UVLO comparator disables the LT8550's switching activity when  $V_{CC}$  is lower than 3.55V (typical).

#### Primary INTV<sub>CC</sub> Sensing

The primary controller gate driver's power supply is  $INTV_{CC}$ , as shown in Figure 12.

The primary  $INTV_{CC}$  voltage is filtered and then sensed by the differential unity gain amplifier A5 in Figure 12, and buffered to REGS\_INT as the reference voltage of the REG LDO.

Notice that the (-) of A5 is connected to IAMPN. As has been discussed in the Primary Controller's Inductor