## **FEATURES**

- Easily Configurable as a Synchronous Buck, Boost, SEPIC, ZETA or Nonsynchronous Buck-Boost Converter

- Wide Input Range: 4.5V to 42V (V<sub>IN</sub> Can Operate to OV, when EXTV<sub>CC</sub> > 4.5V)

- Automatic Low Noise Burst Mode® Operation

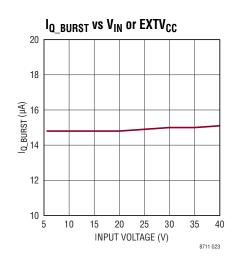

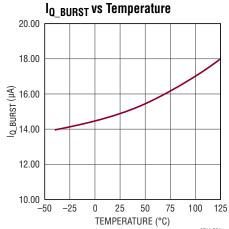

- Low I<sub>O</sub> in Burst Mode Operation (15µA Operating)

- Input Voltage Regulation for High Impedance Source

- 100% Duty Cycle in Dropout (Buck Mode)

- 2A Gate Drivers (BG and TG)

- Adjustable Soft-Start with One Capacitor

- Frequency Programmable from 100kHz to 750kHz

- Can Be Synchronized to External Clock

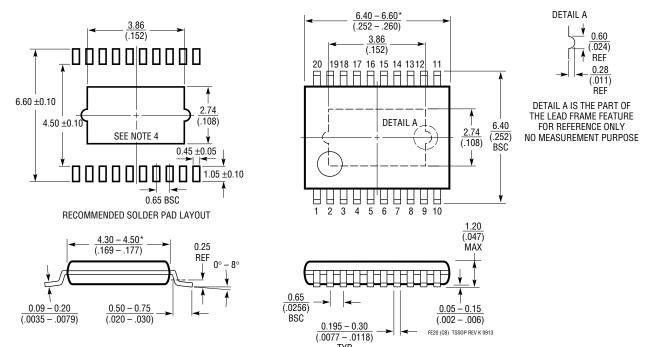

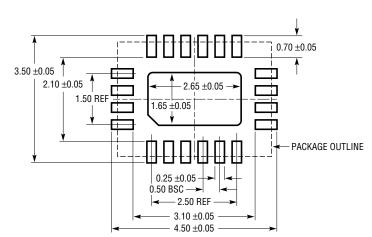

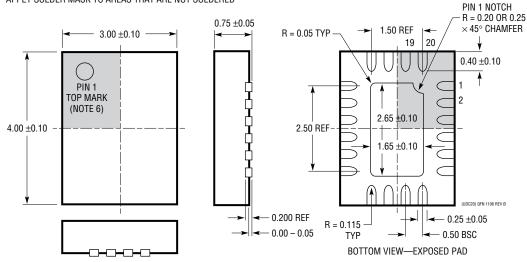

- Available in 20-Lead TSSOP and 20-Lead 3mm×4mm QFN Packages

## **APPLICATIONS**

- General Purpose DC/DC Conversion

- Automotive Systems

- Industrial Supplies

- Solar Panel Power Converter

# Micropower Synchronous Multitopology Controller with 42V Input Capability

## **DESCRIPTION**

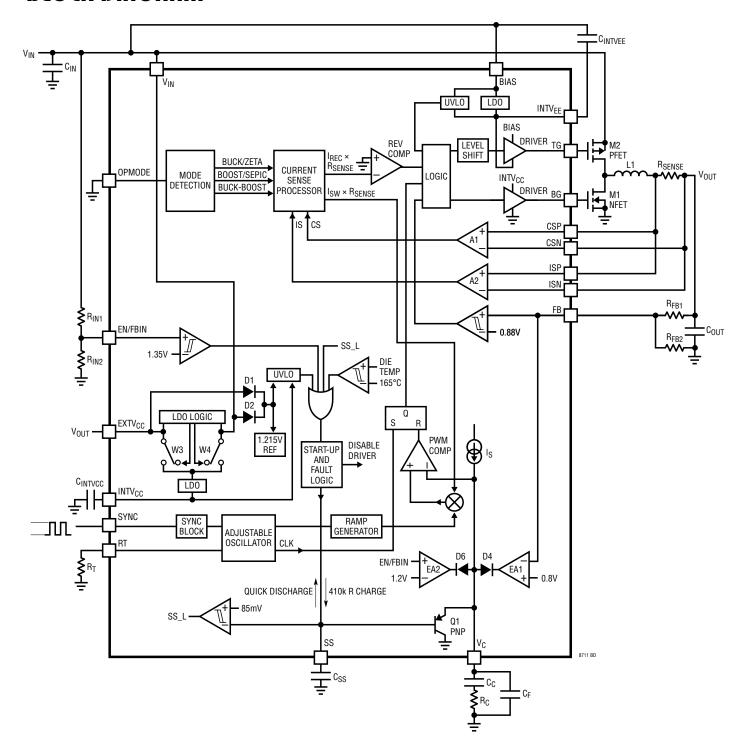

The LT®8711 is a multitopology current mode PWM controller that can easily be configured as a synchronous buck, boost, SEPIC, ZETA or as a nonsynchronous buck-boost converter. Its dual gate drive voltage inputs optimize gate driver efficiency.

The  $15\mu A$  no-load quiescent current with the output voltage in regulation extends operating run time in battery powered systems. Low ripple Burst Mode operation enables high efficiency at very light loads while maintaining low output voltage ripple. The LT8711's fixed switching frequency can be set from 100kHz to 750kHz or can be synchronized to an external clock.

The additional features include 100% duty cycle capability when in buck mode, a topology selection pin and adjustable soft-start. LT8711 is available in the 20-lead TSSOP and 20-lead 3mm × 4mm QFN packages.

All registered trademarks and trademarks are the property of their respective owners.

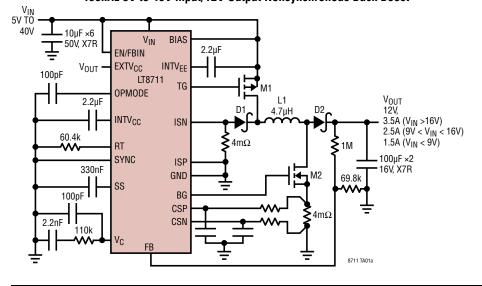

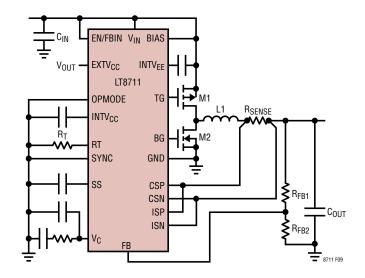

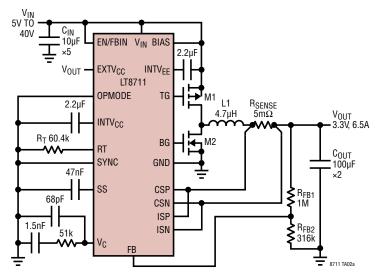

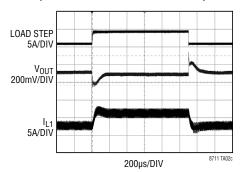

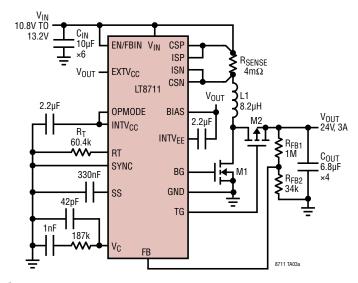

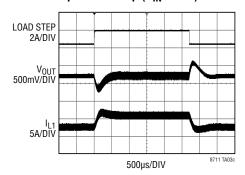

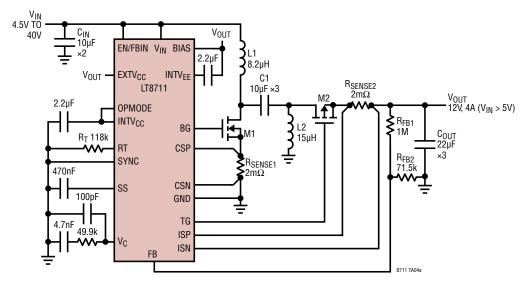

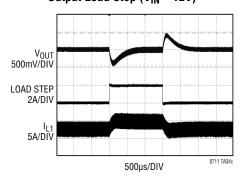

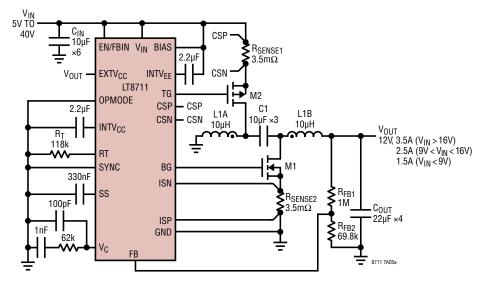

## TYPICAL APPLICATION

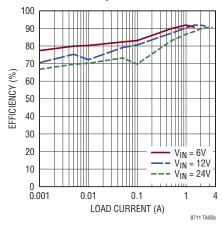

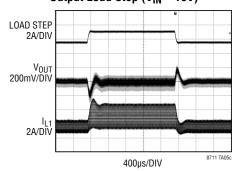

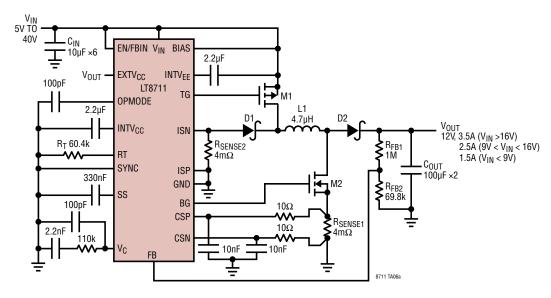

400kHz 5V to 40V Input/12V Output Nonsynchronous Buck Boost

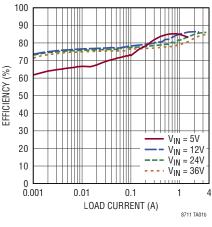

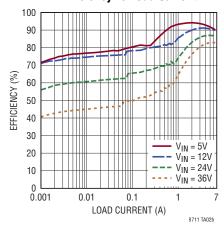

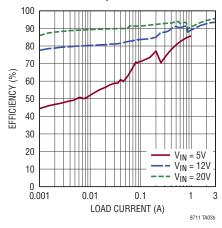

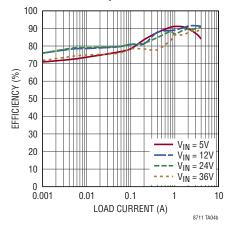

# Efficiency vs Load Current

Rev A

1

## **ABSOLUTE MAXIMUM RATINGS**

(Note 1)

| 0.3V to 42V<br>0.3V to 42V                                          |

|---------------------------------------------------------------------|

| 0.3V to 42V                                                         |

| Note 2<br>0.3V to 5.5V                                              |

| 0.3V to 2.5V                                                        |

| -0.3V to MAX(V <sub>IN</sub> , EXTV <sub>CC</sub> )<br>0.3V to 5.5V |

| 0.3V to 5.5V                                                        |

| Note 2<br>0.3V to 42V                                               |

|                                                                     |

| CSN Voltage                          | CSP - 0.3V to $CSP + 0.3V$ |

|--------------------------------------|----------------------------|

| ISP Voltage                          | ISN - 0.3V to $ISN + 0.3V$ |

| ISN Voltage                          | 0.3V to BIAS               |

| INTV <sub>CC</sub> Voltage           | 0.3V to 5.5V               |

| RT Voltage                           |                            |

| SS Voltage                           |                            |

| <b>Operating Junction Temperatur</b> | e Range                    |

| LT8711E                              | 40°C to 125°C              |

| LT8711I                              | 40°C to 125°C              |

| Storage Temperature Range            | 65°C to 150°C              |

| Lead Temperature (Soldering, 1       | 0 sec)300°C                |

|                                      |                            |

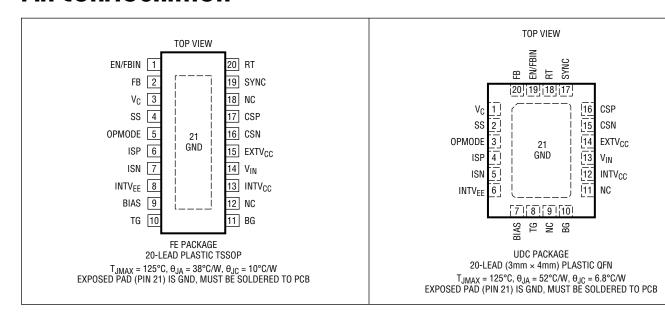

## PIN CONFIGURATION

# ORDER INFORMATION http://www.linear.com/product/LT8711#orderinfo

| LEAD FREE FINISH | TAPE AND REEL    | PART MARKING* | PACKAGE DESCRIPTION   | TEMPERATURE RANGE |

|------------------|------------------|---------------|-----------------------|-------------------|

| LT8711EFE#PBF    | LT8711EFE#TRPBF  | LT8711 FE     | 20-Lead TSSOP         | -40°C to 125°C    |

| LT8711IFE#PBF    | LT8711IFE#TRPBF  | LT8711 FE     | 20-Lead TSSOP         | -40°C to 125°C    |

| LT8711EUDC#PBF   | LT8711EUDC#TRPBF | LGQJ          | 20-Lead 3mm × 4mm QFN | -40°C to 125°C    |

| LT8711IUDC#PBF   | LT8711IUDC#TRPBF | LGQJ          | 20-Lead 3mm × 4mm QFN | -40°C to 125°C    |

Consult ADI Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25\,^{\circ}\text{C}$ . $V_{IN} = 12\text{V}$ , $V_{BIAS} = 12\text{V}$ , unless otherwise noted (Note 3).

| PARAMETER                                                                                               | CONDITIONS                                                                                                                              |   | MIN         | TYP              | MAX            | UNITS      |

|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---|-------------|------------------|----------------|------------|

| V <sub>IN</sub> Operating Voltage Range                                                                 | V <sub>EXTVCC</sub> = 0V<br>V <sub>EXTVCC</sub> = 4.5V                                                                                  | • | 4.5<br>0    |                  | 42<br>42       | V          |

| Quiescent Current in Normal Operation (I <sub>VIN</sub> + I <sub>EXTVCC</sub> + I <sub>BIAS</sub> )     | V <sub>EN/FBIN</sub> = 2.5V, Not Switching                                                                                              |   |             | 2.0              | 2.5            | mA         |

| Quiescent Current in Burst Mode Operation (I <sub>VIN</sub> + I <sub>EXTVCC</sub> + I <sub>BIAS</sub> ) | $V_{FB} = V_{FB\_REG} + 3mV$                                                                                                            |   |             | 15               | 25             | μА         |

| Quiescent Current in Shutdown (I <sub>VIN</sub> + I <sub>EXTVCC</sub> + I <sub>BIAS</sub> )             | V <sub>EN/FBIN</sub> = 0V                                                                                                               |   |             | 1                | 2              | μА         |

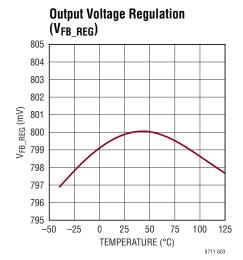

| FB Output Regulation Voltage, V <sub>FB_REG</sub>                                                       |                                                                                                                                         | • | 784<br>795  | 800<br>800       | 816<br>805     | mV<br>mV   |

| FB Line Regulation                                                                                      | $4.5V \le V_{IN} \le 42V$                                                                                                               |   |             | 0.01             | 0.05           | %/V        |

| FB Pin Input Bias Current                                                                               | V <sub>FB</sub> = 0.8V                                                                                                                  | • | -50         | 0                | 50             | nA         |

| Error Amp Transconductance                                                                              | $\Delta I = \pm 5 \mu A$                                                                                                                |   |             | 250              |                | μmhos      |

| Error Amp Voltage Gain                                                                                  |                                                                                                                                         |   |             | 90               |                | dB         |

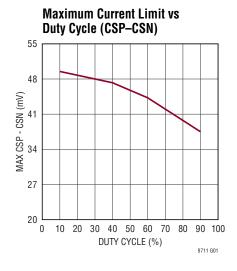

| Maximum Current Sense Voltage,<br>V <sub>CSP</sub> - V <sub>CSN</sub>                                   | Minimum Duty Cycle<br>Maximum Duty Cycle                                                                                                | • | 46<br>26    | 50<br>33         | 54<br>40       | mV<br>mV   |

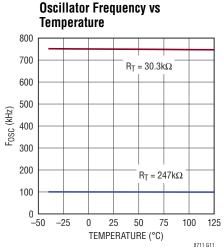

| Switching Frequency, f <sub>OSC</sub>                                                                   | $R_T = 30.3k$<br>$R_T = 247k$                                                                                                           | • | 675<br>85   | 750<br>100       | 825<br>115     | kHz<br>kHz |

| Switching Frequency Range                                                                               | Free-Running<br>Synchronizing                                                                                                           | • | 85<br>140   |                  | 825<br>750     | kHz<br>kHz |

| SYNC Input Voltage High                                                                                 |                                                                                                                                         | • | 1.3         |                  |                | V          |

| SYNC Input Voltage Low                                                                                  |                                                                                                                                         | • |             |                  | 0.4            | V          |

| SYNC Clock Pulse Duty Cycle                                                                             | V <sub>SYNC</sub> = 0V to 2V, f <sub>SYNC</sub> = 500kHz                                                                                |   | 20          |                  | 80             | %          |

| Recommended SYNC Ratio f <sub>SYNC</sub> /f <sub>OSC</sub>                                              |                                                                                                                                         |   | 0.8         |                  | 1.2            |            |

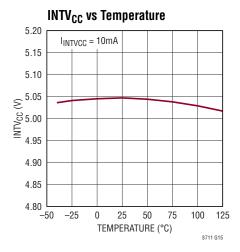

| INTV <sub>CC</sub> Voltage                                                                              | I <sub>INTVCC</sub> = 10mA                                                                                                              | • | 4.75        | 5                | 5.25           | V          |

| INTV <sub>CC</sub> Line Regulation                                                                      | $6V \le V_{IN} \le 42V$ , $V_{EXTVCC} = 0$ , $I_{INTVCC} = 10$ mA<br>$6V \le V_{EXTVCC} \le 42V$ , $V_{VIN} = 0$ , $I_{INTVCC} = 10$ mA |   |             | -0.003<br>-0.003 | -0.03<br>-0.03 | %/V<br>%/V |

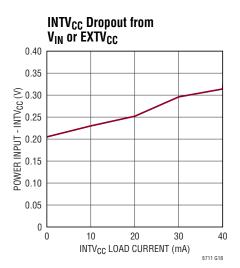

| INTV <sub>CC</sub> Load Regulation                                                                      | I <sub>INTVCC</sub> = 0mA to 40mA                                                                                                       |   |             | -1               | -2             | %          |

| INTV <sub>CC</sub> Maximum External Load Current                                                        | Internal Load Current = 40mA                                                                                                            |   |             | 10               |                | mA         |

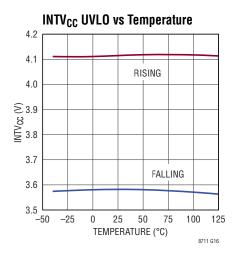

| INTV <sub>CC</sub> Undervoltage Lockout                                                                 | INTV <sub>CC</sub> Rising<br>INTV <sub>CC</sub> Falling                                                                                 | • | 3.9<br>3.45 | 4.1<br>3.6       | 4.3<br>3.75    | V          |

| INTV <sub>CC</sub> Undervoltage Lockout Hysteresis                                                      |                                                                                                                                         |   |             | 500              |                | mV         |

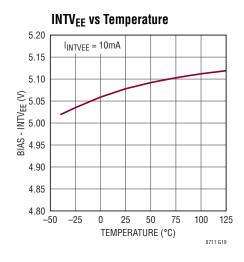

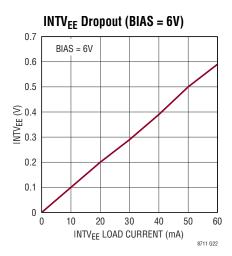

| INTV <sub>EE</sub> Voltage, V <sub>BIAS</sub> – V <sub>INTVEE</sub>                                     | I <sub>INTVEE</sub> = 10mA                                                                                                              | • | 4.85        | 5.15             | 5.4            | V          |

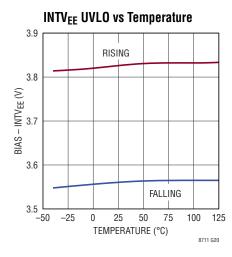

| INTV <sub>EE</sub> Undervoltage Lockout, V <sub>BIAS</sub> – V <sub>INTVEE</sub>                        | V <sub>BIAS</sub> – V <sub>INTVEE</sub> Rising<br>V <sub>BIAS</sub> – V <sub>INTVEE</sub> Falling                                       | • | 3.6<br>3.4  | 3.85<br>3.6      | 4.1<br>3.8     | V          |

| INTV <sub>EE</sub> Undervoltage Lockout Hysteresis,<br>V <sub>BIAS</sub> – V <sub>INTVEE</sub>          |                                                                                                                                         |   |             | 250              |                | mV         |

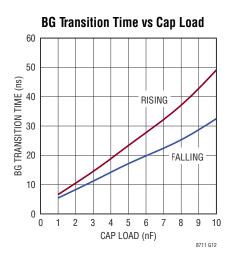

| BG Rise Time                                                                                            | C <sub>BG</sub> = 3.3nF (Note 4)                                                                                                        |   |             | 14               |                | ns         |

| BG Fall Time                                                                                            | C <sub>BG</sub> = 3.3nF (Note 4)                                                                                                        |   |             | 12               |                | ns         |

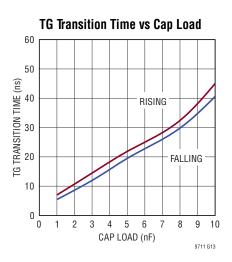

| TG Rise Time                                                                                            | C <sub>TG</sub> = 3.3nF (Note 4)                                                                                                        |   |             | 11               |                | ns         |

| TG Fall Time                                                                                            | C <sub>TG</sub> = 3.3nF (Note 4)                                                                                                        |   |             | 14               |                | ns         |

| BG and TG Non-Overlap Time                                                                              | TG Rising to BG Rising, $C_{BG} = C_{TG} = 3.3$ nF (Note 4)                                                                             |   |             | 70               |                | ns         |

| BG and TG Non-Overlap Time                                                                              | BG Falling to TG Falling, C <sub>BG</sub> = C <sub>TG</sub> = 3.3nF (Note 4)                                                            |   |             | 70               |                | ns         |

| Minimum On-Time                                                                                         | $C_{BG} = C_{TG} = 3.3 nF$                                                                                                              |   |             | 100              |                | ns         |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25$ °C. $V_{IN} = 12V$ , $V_{BIAS} = 12V$ , unless otherwise noted (Note 3).

| PARAMETER                                | CONDITIONS                                        |   | MIN          | TYP       | MAX          | UNITS |

|------------------------------------------|---------------------------------------------------|---|--------------|-----------|--------------|-------|

| SS Charge Current                        | V <sub>SS</sub> = 0V, Current Flows Out of SS pin | • | 6            | 10        | 15           | μА    |

| SS Low Detection Voltage                 | Part Exiting Undervoltage Lockout                 | • | 65           | 85        | 105          | mV    |

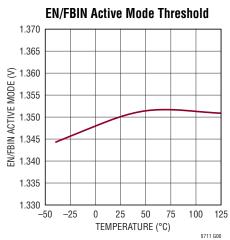

| EN/FBIN Active Mode                      | EN/FBIN Rising                                    | • | 1.28         | 1.35      | 1.42         | V     |

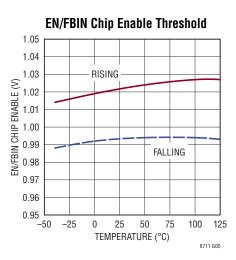

| EN/FBIN Chip Enable                      | EN/FBIN Rising<br>EN/FBIN Falling                 | • | 0.97<br>0.94 | 1.03<br>1 | 1.11<br>1.08 | V     |

| EN/FBIN Chip Enable Hysteresis           |                                                   |   |              | 30        |              | mV    |

| EN/FBIN Input Voltage Low                | Shutdown Mode                                     | • |              |           | 0.2          | V     |

| EN/FBIN Current Limit Adjustment Voltage | Full Current Limit<br>Near Zero Current Limit     | • | 1.12         |           | 1.27         | V     |

| EN/FBIN Pin Input Bias Current           | V <sub>EN/FBIN</sub> = 12V                        | • | -50          | 0         | 50           | nA    |

| EN/FBIN Amp Transconductance             | V <sub>FB</sub> = 0.6V                            |   |              | 40        |              | μmhos |

| EN/FBIN Amp Voltage Gain                 | V <sub>FB</sub> = 0.6V                            |   |              | 100       |              | V/V   |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** Do not apply a positive or negative voltage or current source to BG, TG and INTV<sub>EE</sub> pins, otherwise permanent damage may occur.

Note 3: The LT8711E is guaranteed to meet performance specifications from 0°C to 125°C junction temperature. Specifications over the -40°C to 125°C operating temperature range are assured by design,

characterization and correlation with statistical process controls. The LT8711I is guaranteed over the full –40°C to 125°C operating junction temperature range.

**Note 4:** Rise and fall times are measured using 10% and 90% levels. Delay times are measured using 50% levels.

**Note 5:** This IC includes overtemperature protection that is intended to protect the device during momentary overload conditions. Junction temperature will exceed 125°C when overtemperature protection is active. Continuous operation over the specified maximum operating junction temperature may impair device reliability.

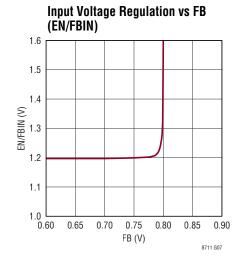

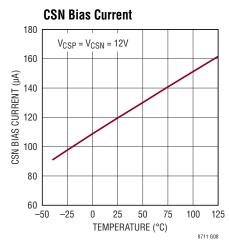

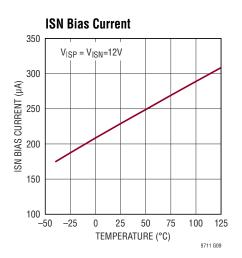

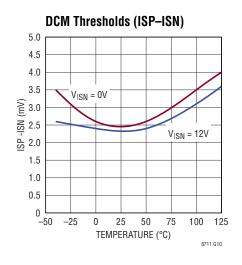

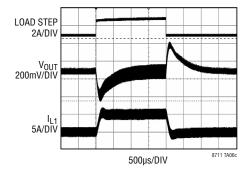

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C, unless otherwise noted.

Rev A

## TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ , unless otherwise noted.

Rev A

## TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C, unless otherwise noted.

## PIN FUNCTIONS (TSSOP/QFN)

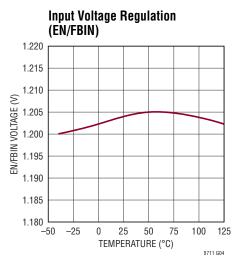

**EN/FBIN (Pin 1/Pin 19):** Enable and Input Voltage Regulation Pin. In conjunction with the UVLO (undervoltage lockout) circuit, this pin is used to enable/disable the chip and restart the soft-start sequence. The EN/FBIN pin is also used to limit the switching regulator current to avoid collapsing the input supply. Drive below 0.2V to disable the chip with very low quiescent current. Drive above 1.03V (typical) to activate the chip. The commanded input current will adjust when the EN/FBIN pin voltage is between 1.12V and 1.27V. Drive above 1.35V (typical) to activate switching with no reduction in input current and restart the soft-start sequence. See the Block Diagram and Applications section for more information. Do not float this pin.

**FB (Pin 2/Pin 20):** Feedback Input Pin. The LT8711 regulates the FB pin to 0.8V. Connect the feedback resistor divider tap to this pin.

**V<sub>C</sub> (Pin 3/Pin 1):** Error Amplifier Output Pin. Tie external compensation network to this pin.

**SS** (Pin 4/Pin 2): Soft Start Pin. Place a soft-start capacitor here. Upon start-up, the SS pin will be charged by a 410k resistor to about 4.3V. During an overtemperature or UVLO condition, the SS pin will be quickly discharged to reset the part. Once those conditions are clear, the part will attempt to restart.

**OPMODE (Pin 5/Pin 3):** Topology Selection Pin. Tie this pin to ground to select buck/ZETA mode. Tie to INTV $_{\rm CC}$  to select SEPIC/boost mode. Tie to a 100pF capacitor to GND to select nonsynchronous buck-boost mode.

**ISP & ISN (Pins 6 & 7/ Pins 4 & 5):** Current Sense Positive and Negative Input Pins respectively. Kelvin connect ISP and ISN pins to a sense resistor.

INTV<sub>EE</sub> (Pin 8/Pin 6): 5V Below BIAS LDO Regulator Pin. Must be locally bypassed with a minimum capacitance of 2.2µF to BIAS. This pin sets the bottom rail for the TG gate driver. The TG gate driver can begin switching when BIAS – INTV<sub>EE</sub> exceeds 3.6V (typical).

**BIAS (Pin 9/Pin 7):** Power Supply for the TG PFET Driver. Must be locally bypassed with a minimum capacitance of 2.2μF to INTV<sub>EE</sub>. The BIAS pin sets the top rail for the TG gate driver.

**TG (Pin 10/Pin 8):** PFET Gate Drive Pin. Low and high levels are INTV<sub>EE</sub> and BIAS respectively with a 2A drive capability.

**BG (Pin 11/Pin 10):** NFET Gate Drive Pin. Low and high levels are GND and INTV<sub>CC</sub> respectively with a 2A drive capability.

**NC (Pin 12/Pin 9):** No Connection. Do not connect. Must be floated.

INTV<sub>CC</sub> (Pin 13/Pin 12): 5V Dual Input LDO Regulator Pin. Must be locally bypassed with a minimum capacitance of  $2.2\mu F$  to GND. Logic will choose to run INTV<sub>CC</sub> from the VIN or EXTV<sub>CC</sub> pins. A maximum 10mA external load can connect to the INTV<sub>CC</sub> pin. The undervoltage lockout on INTV<sub>CC</sub> is 3.6V (typical). The BG gate driver can begin switching when INTV<sub>CC</sub> exceeds 4.1V (typical).

$V_{IN}$  (Pin 14/Pin 13): Input Supply Pin. Must be locally bypassed. Can run down to 0V as long as EXTV<sub>CC</sub> > 4.5V.

**EXTV**<sub>CC</sub> (**Pin 15/Pin 14**): Alternate Input Supply Pin. Must be locally bypassed. Can run down to 0V as long as  $V_{IN} > 4.5V$ .

**CSN & CSP (Pins 16 & 17/ Pins 15 & 16):** Current Sense Negative and Positive Input Pins Respectively. Kelvin connect CSN and CSP pins to a sense resistor to limit the input current. The maximum sense voltage at low duty cycle is 50mV.

NC (Pin 18/Pin 11): No Connection. Do not connect. Must be floated.

**SYNC** (Pin 19/Pin 17): To synchronize the switching frequency to an outside clock, simply drive this pin with a clock. The high voltage level of the clock must exceed 1.3V, and the low level must be less than 0.4V. Drive this pin to less than 0.4V to revert to the internal free running clock. See the Applications Information section for more information.

**RT (Pin 20/Pin 18):** Timing Resistor Pin. Adjusts the LT8711's switching frequency. Place a resistor from this pin to ground to set the frequency to a fixed free running level. Do not float this pin.

**GND (Pin 21/Pin 21):** Ground. Must be soldered directly to the local ground plane.

Rev A

## **BLOCK DIAGRAM**

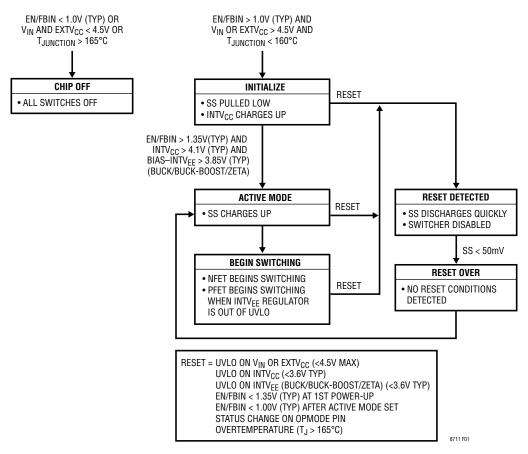

# START-UP AND FAULT SEQUENCE

Figure 1. State Diagram

## **OPERATION**

#### OPERATION—OVERVIEW

The LT8711 uses a constant frequency, current mode control scheme to provide excellent line and load regulation. The part's undervoltage lockout (UVLO) function, together with soft-start, offers a controlled means of starting up. Output voltage and input voltage have control over the commanded peak current which allows a wide range of applications to be built using the LT8711. Synchronous switching makes high efficiency and high output current applications possible. When operating at light load condition, the LT8711 will enter burst mode to minimize switching loss. Refer to the Block Diagram and the State Diagram (Figure 1) for the following description of the part's operation.

#### OPERATION—TOPOLOGY SELECTING

The 8711 can be configured as a synchronous buck, boost, SEPIC, ZETA or nonsynchronous buck-boost converter by configuration of the OPMODE pin.

When the OPMODE pin is connected to GND, the controller operates in buck/ZETA mode.

When the OPMODE pin is connected to the INTV<sub>CC</sub> pin, the controller operates in SEPIC/boost mode.

When the OPMODE pin is tied to a 100pF capacitor to GND, the controller operates in nonsynchronous buckboost mode.

#### OPERATION—START-UP

Several functions are provided to enable a very clean start-up of the LT8711.

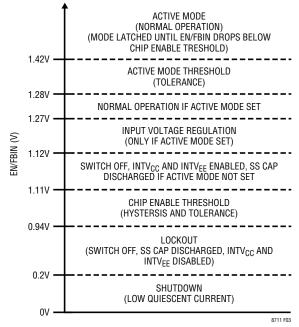

## **Precise Turn-On Voltages**

The EN/FBIN pin has two voltage levels for activating the part: one that enables the part and allows internal rails to operate and a 2nd voltage threshold which activates a soft-start cycle and switching can begin. To enable the part, take the EN/FBIN pin above 1.03V (typical). This comparator has 50mV of hysteresis to protect against glitches and slow ramping. To activate a soft-start cycle and allow switching, take EN/FBIN above 1.35V (typical). When EN/FBIN exceeds 1.35V (typical), the logic state is

latched so that if EN/FBIN drops between 1.03V to 1.35V (typical), the SS pin is not pulled low by the EN/FBIN pin. The EN/FBIN pin is also used for input voltage regulation which is at 1.200V (typical). Input voltage regulation is explained in more detail in the Operation—Regulation section. Taking the EN/FBIN pin below 0.2V shuts down the chip, resulting in extremely low quiescent current. See Figure 2 that illustrates the different EN/FBIN voltage thresholds.

Figure 2. EN/FBIN Modes of Operation

### Undervoltage Lockout (UVLO)

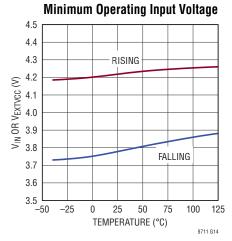

The LT8711 has internal UVLO circuitry that disables the chip when the greater of  $V_{IN}$  or EXTV $_{CC}$  < 3.6V (typical). The EN/FBIN pin can also be used to create a configurable UVLO.

#### **Soft-Start of Switch Current**

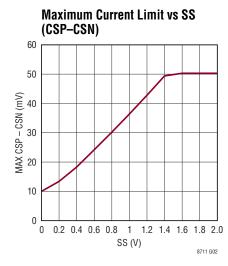

The soft-start circuitry provides for a gradual ramp-up of the switch current (refer to Max Current Limit vs SS in Typical Performance Characteristics). When the part is brought out of shutdown, the external SS capacitor is first discharged which resets the states of the logic circuits in the chip. Once the chip is in active mode, an integrated 410k resistor pulls the SS pin to  $\sim$ 4.3V at a ramp rate set by the external capacitor connected to the pin. Typical values for the soft-start capacitor range from 100nFto 1 $\mu$ F.

## **OPERATION**

#### OPERATION—REGULATION

Use the Block Diagram when stepping through the following description of the LT8711 operating in regulation. The LT8711 has two modes of regulation:

- 1. Output Voltage (via FB pin)

- 2. Input Voltage (via EN/FBIN pin)

Both of these regulation loops control the peak commanded current. At the start of each oscillator cycle, the SR latch is set, which first turns off the external rectifier switch (NFET in Block Diagram), and then turns on the external main switch (PFET in Block Diagram). The PFET's current flows through an external current sense resistor (RSENSE) generating a voltage proportional to the PFET switch current. This voltage is then amplified by A1 and added to a stabilizing ramp. The resulting sum is fed into the positive terminal of the PWM comparator. When the voltage on the positive input of the PWM comparator exceeds the voltage on the negative input ( $V_C$  pin), the SR latch is reset, turning off the PFET and then turning on the NFET. The voltage on the  $V_C$  pin is controlled by one of the regulation loops, or a combination of regulation loops.

Slope compensation provides stability in constant frequency current mode control architectures by preventing subharmonic oscillations at high duty cycles. This is accomplished internally by adding a compensating ramp to the positive terminal of the PWM comparator.

### **Output Voltage Regulation**

The error amplifier servos the  $V_{\mathbb{C}}$  node by comparing the voltage on the FB pin with an internal 0.800V reference. When the load current increases it causes a reduction in the feedback voltage relative to the reference causing the error amplifier to raise the  $V_{\mathbb{C}}$  voltage. In this manner, the FB error amplifier sets the correct peak current level to maintain output voltage regulation.

## **Input Voltage Regulation**

A resistor divider from the converter's input voltage to the EN/FBIN pin sets the input voltage regulation point. The EN/FBIN pin voltage connects to the positive input of amplifier EA2. The  $V_{\rm C}$  pin voltage is set by EA2, which is the amplified difference between the EN/FBIN pin voltage and an internal 1.200V reference voltage. In this manner, the EN/FBIN error amplifier sets the correct peak current level to maintain input voltage regulation.

#### OPERATION—RESET CONDITIONS

The LT8711 has three reset cases. When the part is in reset, the SS pin is pulled low and both power switches, NFET and PFET, are forced off. Once all of the reset conditions are gone, the part is allowed to begin a soft-start sequence and switching can commence. Each of the following events can cause the LT8711 to be in reset:

- 1. UVLO

- a. The greater of  $V_{IN}$  and  $EXTV_{CC}$  is < 4.5V (maximum)

- b. UVLO on INTV<sub>CC</sub>. INTV<sub>CC</sub> < 3.6V (typical)

- c. UVLO on INTV<sub>EE</sub>.  $V_{BIAS} V_{INTVEE} < 3.6V$  (typical) unless BOOST/SEPIC topology is selected

- d. EN/FBIN < 1.35V (typical) at first power-up

- e. EN/FBIN < 1.00V (typical) after active mode set

- 2. OPMODE pin status changes

- 3. Die Temperature > 165°C

#### OPERATION—POWER SWITCH CONTROL

The external PFET and NFET switches are never on at the same time (except buck-boost mode), and there is a non-overlap time of about 100ns to prevent cross conduction.

## **OPERATION**

#### **Light Load Operation Modes**

The SYNC pin can be used to tell the LT8711 to operate in FCM regardless of load current, or operate in DCM and Burst Mode at light loads.

SYNC = logic high: FCM

SYNC = logic low: DCM or Burst Mode operation

If a clock is applied to the SYNC pin the part will synchronize to an external clock frequency and operate in FCM mode.

# OPERATION—AUTOMATIC LOW NOISE Burst Mode OPERATION

At no load or very light load condition, high FB voltage causes  $V_{C}$  to decrease. When  $V_{C}$  voltage is lower than a threshold voltage, the controller operates in Burst Mode to minimize switching loss. Between bursts, all circuitry associated with controlling the output switch is shut down, reducing the average input supply current to  $15\mu A$  in a typical application. Low standby power and higher conversion efficiency is thus achieved. To optimize the quiescent current performance at light loads, the current in the feedback resistor divider must be minimized as it appears to the output as load current.

### OPERATION—LDO REGULATORS (INTV<sub>CC</sub> AND INTV<sub>EE</sub>)

The INTV<sub>CC</sub> LDO regulates at 5.0V (typical) and is used as the top rail for the BG gate driver. The INTV<sub>CC</sub> LDO can run from V<sub>IN</sub> or EXTV<sub>CC</sub> and will intelligently select to run from the best rail to minimize power loss in the chip, but at the same time, select the proper input for maintaining INTV<sub>CC</sub> as close to 5.0V as possible. The INTV<sub>CC</sub> regulator also has safety features to limit the power dissipation in the internal pass device and also to prevent it from damage if the pin is shorted to ground. The UVLO threshold on INTV<sub>CC</sub> is 3.6V (typical), and the LT8711 will be in reset until the LDO comes out of UVLO.

The INTV<sub>EE</sub> regulator regulates to 5.15V (typical) below the BIAS pin voltage. The BIAS and INTV<sub>EE</sub> voltages are used for the top and bottom rails of the TG gate driver respectively. Just like the INTV<sub>CC</sub> regulator, the INTV<sub>EE</sub> regulator has a safety feature to limit the power dissipation in the internal pass device. The TG pin can begin switching only after the INTV<sub>EE</sub> regulator comes out of UVLO (3.85V typical across the BIAS and INTV<sub>EE</sub> pins). When the INTV<sub>EE</sub> regulator is in UVLO, for the boost and SEPIC topologies, the bottom switch is allowed to switch. The output current would flow through the body diode of the PFET. To protect the PFET from thermal damage under this condition, the maximum commanded current is folded back to 27mV (typical) across the CSP-CSN pins.

#### **BUCK CONVERTER COMPONENT SELECTION**

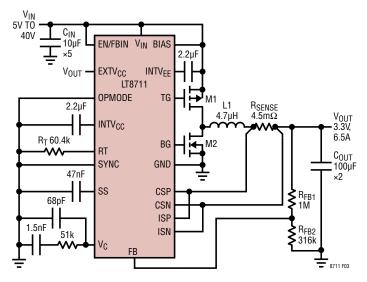

The LT8711 can be configured as a buck converter as in Figure 3.

For a desired output current and output voltage over a given input voltage range, Table 1 is a step-by-step set of equations to calculate component values for the LT8711 when operating as a buck converter. Refer to more detail in this section and the Appendix for further information on the design equations presented in Table 1.

#### Variable Definitions:

V<sub>IN(MIN)</sub> = Minimum Input Voltage

V<sub>IN(MAX)</sub> = Maximum Input Voltage

V<sub>OUT</sub> = Output Voltage

I<sub>OUT</sub> = Output Current of Converter

f = Switching Frequency

$DC_{MAX}$  = Power Switch Duty Cycle at  $V_{IN(MIN)}$

$V_{CSPN}$  = Current Limit Voltage at  $DC_{MAX}$

ADDITIONAL 470  $\mu F$  6.3V ELECTROLYTIC CAP ON  $V_{OUT}$  47  $\mu F$  50V ELECTROLYTIC CAP ON  $V_{IN}$

Figure 3. Buck Converter—The Component Values Given Are Typical Values for a 400kHz, 5V-40V to 3.3V/6.5A Buck

**Table 1. Buck Design Equations**

| Table 1: Back Be                           |                                                                                                                                                                                                                                                                                                                                                       |  |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                            | Parameters/Equations                                                                                                                                                                                                                                                                                                                                  |  |

| Step 1: Inputs                             | Pick $V_{\text{IN}}, V_{\text{OUT}}, I_{\text{OUT}},$ and f to calculate equations below.                                                                                                                                                                                                                                                             |  |

| Step 2: DC <sub>MAX</sub>                  | $DC_{MAX} \cong \frac{V_{OUT}}{V_{IN(MIN)}}$                                                                                                                                                                                                                                                                                                          |  |

| Step 3: V <sub>CSPN</sub>                  | See $\it Max$ $\it Current$ $\it Limit$ $\it vs$ $\it Duty$ $\it Cycle$ plot in Typical Performance Characteristics to find $\it V_{\it CSPN}$ at $\it DC_{\it MAX}$ .                                                                                                                                                                                |  |

| Step 4: R <sub>SENSE</sub>                 | $R_{SENSE} \le 0.75 \bullet \frac{V_{CSPN}}{I_{OUT}}$                                                                                                                                                                                                                                                                                                 |  |

| Step 5: L                                  | $L_{TYP} = \frac{R_{SENSE} \cdot \left(V_{IN(MIN)} - V_{OUT}\right)}{12.5m \cdot f} \cdot \frac{V_{OUT}}{V_{IN(MIN)}}$ $L_{MIN} = \frac{R_{SENSE} \cdot V_{IN(MIN)}}{40m \cdot f} \cdot \frac{2V_{OUT} - V_{IN(MIN)}}{V_{OUT}}$ $L_{MAX} = \frac{R_{SENSE} \cdot \left(V_{IN(MIN)} - V_{OUT}\right)}{2.5m \cdot f} \cdot \frac{V_{OUT}}{V_{IN(MIN)}}$ |  |

|                                            | Solve equations 1 to 4 for a range of L values.     The minimum value of the L range is the higher of L <sub>TYP</sub> and L <sub>MIN</sub> .                                                                                                                                                                                                         |  |

| Step 6: C <sub>OUT</sub>                   | $C_{OUT} \ge \frac{1 - DC_{MIN}}{8 \cdot L \cdot f^2 \cdot 0.005}$                                                                                                                                                                                                                                                                                    |  |

| Step 7: C <sub>IN</sub>                    | $C_{IN} \geq \frac{I_{OUT} \bullet DC_{MAX}}{f \bullet \Delta V_{IN}}$ $\Delta V_{IN} \text{ is acceptable maximum input ripple voltage.}$                                                                                                                                                                                                            |  |

| Step 8: R <sub>FB1</sub> /R <sub>FB2</sub> | $R_{FB1} = \left(\frac{V_{OUT}}{0.8V} - 1\right) \bullet R_{FB2}$                                                                                                                                                                                                                                                                                     |  |

| Step 9: R <sub>T</sub>                     | $R_T = \frac{25000}{f} - 2$ : f is in kHz and $R_T$ is in k $\Omega$                                                                                                                                                                                                                                                                                  |  |

| MOTE TI C I I                              |                                                                                                                                                                                                                                                                                                                                                       |  |

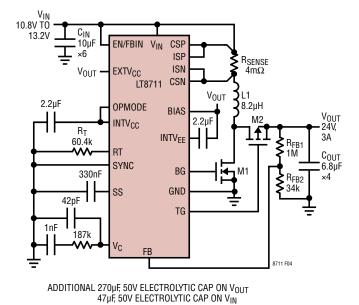

#### **BOOST CONVERTER COMPONENT SELECTION**

The LT8711 can be configured as a boost converter as in Figure 4.

For a desired output current and output voltage over a given input voltage range, Table 2 is a step-by-step set of equations to calculate component values for the LT8711 when operating as a boost converter. Refer to more detail in this section and the Appendix for further information on the design equations presented in Table 2.

#### Variable Definitions:

$V_{IN(MIN)}$  = Minimum Input Voltage

V<sub>IN(MAX)</sub> = Maximum Input Voltage

V<sub>OUT</sub> = Output Voltage

I<sub>OUT</sub> = Output Current of Converter

f = Switching Frequency

DC<sub>MAX</sub> = Power Switch Duty Cycle at V<sub>IN(MIN)</sub>

$V_{CSPN}$  = Current Limit Voltage at  $DC_{MAX}$

Figure 4. Boost Converter—The Component Values Given are Typical Values for a 400kHz, 12V to 24V/3A Boost

**Table 2. Boost Design Equations**

| iadie 2. Boost Design Equations                                                                                                                                |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Parameters/Equations                                                                                                                                           |  |  |

| Pick V <sub>IN</sub> , V <sub>OUT</sub> , I <sub>OUT</sub> , and f to calculate equations below.                                                               |  |  |

| $DC_{MAX} \cong 1 - \frac{V_{IN(MIN)}}{V_{OUT}}$                                                                                                               |  |  |

| See $\it Max$ $\it Current$ $\it Limit$ $\it vs$ $\it Duty$ $\it Cycle$ plot in Typical Performance Characteristics to find $\it V_{CSPN}$ at $\it DC_{MAX}$ . |  |  |

| $R_{SENSE} \le 0.63 \cdot \frac{V_{CSPN}}{I_{OUT}} (1 - DC_{MAX})$                                                                                             |  |  |

| $L_{TYP} = \frac{R_{SENSE} \cdot V_{IN(MIN)}}{12.5m \cdot f} \cdot \left(1 - \frac{V_{IN(MIN)}}{V_{OUT}}\right)$                                               |  |  |

| $L_{MIN} = \frac{R_{SENSE} \cdot V_{OUT}}{40m \cdot f} \cdot \left(1 - \frac{V_{IN(MIN)}}{V_{OUT} - V_{IN(MIN)}}\right)$                                       |  |  |

| $L_{MAX1} = \frac{R_{SENSE} \cdot V_{IN(MIN)}}{5m \cdot f} \cdot \left(1 - \frac{V_{IN(MIN)}}{V_{OUT}}\right)$                                                 |  |  |

| $L_{MAX2} = \frac{R_{SENSE} \cdot V_{IN(MAX)}}{5m \cdot f} \cdot \left(1 - \frac{V_{IN(MAX)}}{V_{OUT}}\right)$                                                 |  |  |

| Solve equations 1 to 4 for a range of L values.                                                                                                                |  |  |

| The minimum value of the L range is the higher of L <sub>TYP</sub> and L <sub>MIN</sub> . The maximum of the L value range is the lower of L <sub>MAX</sub> .  |  |  |

| $C_{OUT} \ge \frac{I_{OUT} \bullet DC_{MAX}}{f \bullet 0.005 \bullet V_{OUT}}$                                                                                 |  |  |

| $C_{IN} \ge \frac{DC_{MAX}}{8 \cdot L \cdot f^2 \cdot 0.005}$                                                                                                  |  |  |

| $R_{FB1} = \left(\frac{V_{OUT}}{0.8V} - 1\right) \bullet R_{FB2}$                                                                                              |  |  |

| $R_T = \frac{25000}{f} - 2$ : f is in kHz and $R_T$ is in k $\Omega$                                                                                           |  |  |

|                                                                                                                                                                |  |  |

#### SEPIC CONVERTER COMPONENT SELECTION

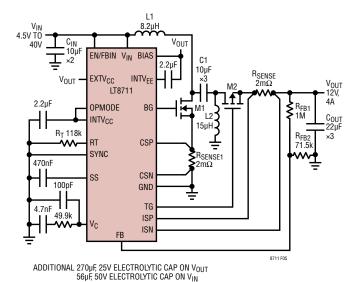

The LT8711 can be configured as a SEPIC converter as in Figure 5.

For a desired output current and output voltage over a given input voltage range, Table 3 is a step-by-step set of equations to calculate component values for the LT8711 when operating as a SEPIC converter. Refer to more detail in this section and the Appendix for further information on the design equations presented in Table 3.

#### Variable Definitions:

$V_{IN(MIN)}$  = Minimum Input Voltage

$V_{IN(MAX)}$  = Maximum Input Voltage

V<sub>OUT</sub> = Output Voltage

I<sub>OUT</sub> = Output Current of Converter

f = Switching Frequency

$DC_{MAX}$  = Power Switch Duty Cycle at  $V_{IN(MIN)}$

$V_{CSPN}$  = Current Limit Voltage at  $DC_{MAX}$

Figure 5. SEPIC Converter—The Component Values Given Are Typical Values for a 200kHz, 4.5V-40V to 12V/4A SEPIC

**Table 3. SEPIC Design Equations**

| 10010 0. 021 10 0                          | ooigii Equationo                                                                                                                                              |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                            | Parameters/Equations                                                                                                                                          |

| Step 1: Inputs                             | Pick $V_{\text{IN}},V_{\text{OUT}},I_{\text{OUT}},\text{and}\text{f}\text{to}\text{calculate}\text{equations}$ below.                                         |

| Step 2: DC <sub>MAX</sub>                  | $DC_{MAX} \cong \frac{V_{OUT}}{V_{IN(MIN)} + V_{OUT}}$                                                                                                        |

| Step 3: V <sub>CSPN</sub>                  | See <i>Max Current Limit vs Duty Cycle</i> plot in Typical Performance Characteristics to find V <sub>CSPN</sub> at DC <sub>MAX</sub> .                       |

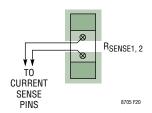

| Step 4: R <sub>SENSE</sub>                 | $R_{SENSE} \le 0.63 \bullet \frac{V_{CSPN}}{I_{OUT}} (1 - DC_{MAX})$ $R_{SENSE1} = R_{SENSE2} = R_{SENSE}$                                                    |

| Step 5: L                                  | $L_{TYP} = \frac{R_{SENSE} \cdot V_{OUT}}{12.5m \cdot f} \cdot \frac{V_{IN(MIN)}}{V_{IN(MIN)} + V_{OUT}}$                                                     |

|                                            | $L_{MIN} = \frac{R_{SENSE} \cdot V_{OUT}}{40m \cdot f} \cdot \left(1 - \left(\frac{V_{IN(MIN)}}{V_{OUT}}\right)^{2}\right)$                                   |

|                                            | $L_{MAX} = \frac{R_{SENSE} \cdot V_{OUT}}{5m \cdot f} \cdot \frac{V_{IN(MIN)}}{V_{IN(MIN)} + V_{OUT}}$                                                        |

|                                            | Solve equations 1 to 4 for a range of L values.                                                                                                               |

|                                            | The minimum value of the L range is the higher of L <sub>TYP</sub> and L <sub>MIN</sub> . The maximum of the L value range is the lower of L <sub>MAX</sub> . |

|                                            | L = L1 = L2 for coupled inductors.                                                                                                                            |

|                                            | L = L1    L2 for uncoupled inductors.                                                                                                                         |

| Step 6: C1                                 | $C1 \ge 10\mu F$ (Typical); $V_{RATING} > V_{IN}$                                                                                                             |

| Step 7: C <sub>OUT</sub>                   | $C_{OUT} \ge \frac{I_{OUT} \bullet DC_{MAX}}{f \bullet 0.005 \bullet V_{OUT}}$                                                                                |

| Step 8: C <sub>IN</sub>                    | $C_{IN} \ge \frac{DC_{MAX}}{8 \cdot L \cdot f^2 \cdot 0.005}$                                                                                                 |

| Step 9: R <sub>FB1</sub> /R <sub>FB2</sub> | $R_{FB1} = \left(\frac{V_{OUT}}{0.8V} - 1\right) \bullet R_{FB2}$                                                                                             |

| Step 10: R <sub>T</sub>                    | $R_T = \frac{25000}{f} - 2$ : f is in kHz and $R_T$ is in k $\Omega$                                                                                          |

#### ZETA CONVERTER COMPONENT SELECTION

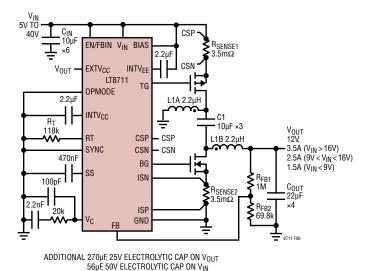

The LT8711 can be configured as a ZETA converter as in Figure 6.

For a desired output current and output voltage over a given input voltage range, Table 4 is a step-by-step set of equations to calculate component values for the LT8711 when operating as a ZETA converter. Refer to more detail in this section and the Appendix for further information on the design equations presented in Table 4.

#### Variable Definitions:

$V_{IN(MIN)}$  = Minimum Input Voltage

V<sub>IN(MAX)</sub> = Maximum Input Voltage

V<sub>OUT</sub> = Output Voltage

I<sub>OUT</sub> = Output Current of Converter

f = Switching Frequency

$DC_{MAX}$  = Power Switch Duty Cycle at  $V_{IN(MIN)}$

$V_{CSPN}$  = Current Limit Voltage at  $DC_{MAX}$

Figure 6. ZETA Converter—The Component Values Given Are Typical Values for a 200kHz, 5V-40V to 12V/3.5A ZETA

**Table 4. ZETA Design Equations**

| IUDIC 4. ZEIA DO                           | olyn Equations                                                                                                                                                                                                                                                                    |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                            | Parameters/Equations                                                                                                                                                                                                                                                              |

| Step 1: Inputs                             | Pick $V_{\text{IN}}, V_{\text{OUT}}, I_{\text{OUT}},$ and f to calculate equations below.                                                                                                                                                                                         |

| Step 2: DC <sub>MAX</sub>                  | $DC_{MAX} \cong \frac{V_{OUT}}{V_{IN(MIN)} + V_{OUT}}$                                                                                                                                                                                                                            |

| Step 3: V <sub>CSPN</sub>                  | See $\it Max$ $\it Current$ $\it Limit$ $\it vs$ $\it Duty$ $\it Cycle$ plot in Typical Performance Characteristics to find $\it V_{CSPN}$ at $\it DC_{MAX}$ .                                                                                                                    |

| Step 4: R <sub>SENSE</sub>                 | $R_{SENSE} \le 0.63 \bullet \frac{V_{CSPN}}{I_{OUT}} (1 - DC_{MAX})$                                                                                                                                                                                                              |

|                                            | R <sub>SENSE1</sub> = R <sub>SENSE2</sub> = R <sub>SENSE</sub>                                                                                                                                                                                                                    |

| Step 5: L                                  | $L_{TYP} = \frac{R_{SENSE} \bullet V_{OUT}}{12.5m \bullet f} \bullet \frac{V_{IN(MIN)}}{V_{IN(MIN)} + V_{OUT}}$                                                                                                                                                                   |

|                                            | $L_{MIN} = \frac{R_{SENSE} \cdot V_{OUT}}{40m \cdot f} \cdot \left(1 - \left(\frac{V_{IN(MIN)}}{V_{OUT}}\right)^{2}\right)$                                                                                                                                                       |

|                                            | $L_{MAX} = \frac{R_{SENSE} \cdot V_{OUT}}{5m \cdot f} \cdot \frac{V_{IN(MIN)}}{V_{IN(MIN)} + V_{OUT}}$                                                                                                                                                                            |

|                                            | <ul> <li>Solve equations 1 to 4 for a range of L values.</li> <li>The minimum value of the L range is the higher of L<sub>TYP</sub> and L<sub>MIN</sub>. The maximum of the L value range is the lower of L<sub>MAX</sub>.</li> <li>L = L1 = L2 for coupled inductors.</li> </ul> |

|                                            | L = L1 = L2 for coupled inductors.      L = L1    L2 for uncoupled inductors.                                                                                                                                                                                                     |

| Step 6: C1                                 | $C1 \ge 10\mu F$ (Typical); $V_{RATING} > V_{IN}$                                                                                                                                                                                                                                 |

| Step 7: C <sub>OUT</sub>                   | $C_{OUT} \ge \frac{I_{OUT} \bullet DC_{MAX}}{f \bullet 0.005 \bullet V_{OUT}}$                                                                                                                                                                                                    |

| Step 8: C <sub>IN</sub>                    | $C_{IN} \ge \frac{DC_{MAX}}{8 \cdot L \cdot f^2 \cdot 0.005}$                                                                                                                                                                                                                     |

| Step 9: R <sub>FB1</sub> /R <sub>FB2</sub> | $R_{FB1} = \left(\frac{V_{OUT}}{0.8V} - 1\right) \bullet R_{FB2}$                                                                                                                                                                                                                 |

| Step 10: R <sub>T</sub>                    | $R_T = \frac{25000}{f} - 2$ : f is in kHz and $R_T$ is in k $\Omega$                                                                                                                                                                                                              |

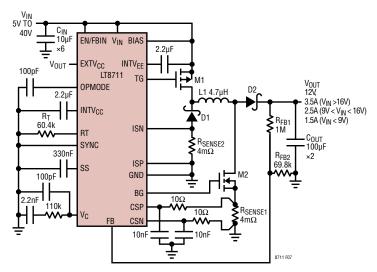

#### **BUCK-BOOST CONVERTER COMPONENT SELECTION**

The LT8711 can be configured as a buck-boost converter as in Figure 7.

For a desired output current and output voltage over a given input voltage range, Table 5 is a step-by-step set of equations to calculate component values for the LT8711 when operating as a buck-boost converter. Refer to more detail in this section and the Appendix for further information on the design equations presented in Table 5.

#### Variable Definitions:

V<sub>IN(MIN)</sub> = Minimum Input Voltage

V<sub>IN(MAX)</sub> = Maximum Input Voltage

V<sub>OUT</sub> = Output Voltage

I<sub>OUT</sub> = Output Current of Converter

f = Switching Frequency

$DC_{MAX}$  = Power Switch Duty Cycle at  $V_{IN(MIN)}$

$V_{CSPN}$  = Current Limit Voltage at  $DC_{MAX}$

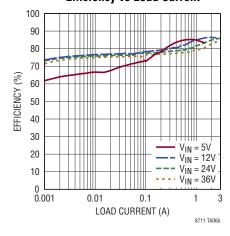

Figure 7. Buck-Boost Converter—The Component Values Given Are Typical Values for a 400kHz, 5V-40V to 12V/2.5A Buck-Boost

Table 5. Buck-Boost Design Equations

| Table 6. Back Be                           | Joot Boorgii Equationo                                                                                                                                                                                            |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                            | Parameters/Equations                                                                                                                                                                                              |

| Step 1: Inputs                             | Pick V <sub>IN</sub> , V <sub>OUT</sub> , I <sub>OUT</sub> , and f to calculate equations below.                                                                                                                  |

| Step 2: DC <sub>MAX</sub>                  | $DC_{MAX} \cong \frac{V_{OUT}}{V_{IN(MIN)} + V_{OUT}}$                                                                                                                                                            |

| Step 3: V <sub>CSPN</sub>                  | See <i>Max Current Limit vs Duty Cycle</i> plot in Typical Performance Characteristics to find V <sub>CSPN</sub> at DC <sub>MAX</sub> .                                                                           |

| Step 4: R <sub>SENSE</sub>                 | $R_{SENSE} \le 0.63 \cdot \frac{V_{CSPN}}{I_{OUT}} (1 - DC_{MAX})$ $R_{SENSE1} = R_{SENSE2} = R_{SENSE}$                                                                                                          |

| Step 5: L                                  | $L_{TYP} = \frac{R_{SENSE} \cdot V_{OUT}}{12.5m \cdot f} \cdot \frac{V_{IN(MIN)}}{V_{IN(MIN)} + V_{OUT}}$                                                                                                         |

|                                            | $L_{MIN} = \frac{R_{SENSE} \cdot V_{OUT}}{40m \cdot f} \cdot \left(1 - \left(\frac{V_{IN(MIN)}}{V_{OUT}}\right)^{2}\right)$                                                                                       |

|                                            | $L_{MAX} = \frac{R_{SENSE} \cdot V_{OUT}}{5m \cdot f} \cdot \frac{V_{IN(MIN)}}{V_{IN(MIN)} + V_{OUT}}$                                                                                                            |

|                                            | Solve equations 1 to 4 for a range of L values.     The minimum value of the L range is the higher of L <sub>TYP</sub> and L <sub>MIN</sub> . The maximum of the L value range is the lower of L <sub>MAX</sub> . |

| Step 6: C <sub>OUT</sub>                   | $C_{OUT} \ge \frac{I_{OUT} \cdot DC_{MAX}}{f \cdot 0.005 \cdot V_{OUT}}$                                                                                                                                          |

| Step 7: C <sub>IN</sub>                    | $C_{IN} \ge \frac{DC_{MAX}}{8 \cdot L \cdot f^2 \cdot 0.005}$                                                                                                                                                     |

| Step 8: R <sub>FB1</sub> /R <sub>FB2</sub> | $R_{FB1} = \left(\frac{V_{OUT}}{0.8V} - 1\right) \bullet R_{FB2}$                                                                                                                                                 |

| Step 9: R <sub>T</sub>                     | $R_T = \frac{25000}{f} - 2$ : f is in kHz and $R_T$ is in k $\Omega$                                                                                                                                              |

| NOTE: The final val                        | use for C and C may deviate from the above                                                                                                                                                                        |

#### SETTING THE OUTPUT VOLTAGE REGULATION

The LT8711 output voltage is set by a resistor divider between  $V_{OUT}$ , FB, and GND.

$$V_{OUT} = 0.8V \bullet \left(1 + \frac{R_{FB1}}{R_{FB2}}\right)$$

where R<sub>FB1</sub> and R<sub>FB2</sub> are shown in the Block Diagram.

See the Electrical Characteristics for tolerances on the FB regulation voltage.

# SETTING THE INPUT VOLTAGE REGULATION OR UNDERVOLTAGE LOCKOUT

By connecting a resistor divider between  $V_{IN}$ , EN/FBIN, and GND, the EN/FBIN pin provides a means to regulate the input voltage or to create an undervoltage lockout function. Referring to error amplifier EA2 in the block diagram, when EN/FBIN is lower than the 1.2V reference,  $V_C$  is pulled low. For example, if  $V_{IN}$  is provided by a relatively high impedance source (e.g. a solar panel) and the current draw pulls  $V_{IN}$  below a preset limit,  $V_C$  will be reduced, thus reducing current draw from the input supply and limiting the input voltage drop.

To set the minimum or regulated input voltage use:

$$V_{IN(MIN-REG)} = 1.2V \cdot \left(1 + \frac{R_{IN1}}{R_{IN2}}\right)$$

where  $R_{IN1}$  and  $R_{IN2}$  are shown in the Block Diagram.

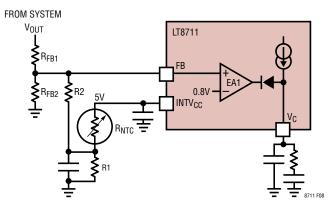

# Temperature Dependent Output Voltage Using NTC Resistor

It may be desirable to regulate the converter's output based on the ambient temperature. The INTV $_{CC}$  LDO regulated voltage is 5.0V  $\pm$  4% (see Electrical Characteristics), and a negative temperature coefficient (NTC) resistor can be used to sum into the FB pin to create an output voltage that decreases with temperature. See Figure 8 for the necessary connections.

Figure 8. Temperature Dependent Output Using an NTC Resistor Divider

The FB voltages regulates to 0.8V (typical). For an accurate room temperature output voltage, size the resistor divider off the INTV<sub>CC</sub> pin to give 0.8V such that the current through R2 is ~0 at room temperature. Choose  $R_{NTC(25)} \leq 10 k\Omega$  and use the equations below to calculate R1,  $R_{FB1}$ , and  $V_{OUT}$  at room temperature and  $R_{FB2}$  for a desired  $V_{OUT}$  change over temperature.

$$\begin{split} R1 &= R_{NTC(25)} \frac{0.8V}{5.0V - 0.8V} \\ V_{OUT} &\cong 0.8V + \frac{R_{FB1}}{R2} \\ & \bullet \left( 0.8V - 5.0V \bullet \frac{R1}{R1 + R_{NTC(25)}} \right) + 0.8V \bullet \frac{R_{FB1}}{R_{FB2}} \\ R_{NTC} &= R_{NTC(25)} \bullet e^{\beta \bullet \left( \frac{1}{T} - \frac{1}{T_{25}} \right)} \\ \Delta V_{OUT} &= -5.0V \bullet \frac{R_{FB1}}{R2} \bullet R1 \\ & \bullet \left( \frac{1}{R1 + R_{NTC(T(MAX))}} - \frac{1}{R1 + R_{NTC(T(MIN))}} \right) \\ R2 &= \frac{-5.0V}{\Delta V_{OUT}} \bullet R_{FB1} \bullet R1 \\ & \bullet \left( \frac{1}{R1 + R_{NTC(T(MAX))}} - \frac{1}{R1 + R_{NTC(T(MIN))}} \right) \end{split}$$

where:

$R_{NTC(25)}$  = Resistance of the NTC resistor at 25°C

$\beta$  = Material-specific constant of NTC resistor. Specified at two temperatures such as  $\beta_{25/85}$ . If more than two  $\beta$ s are specified, use the most appropriate for the application.

T = Absolute temperature in Kelvin

$T_{25}$  = Room temperature in Kelvin (298.15K)

# SWITCH CURRENT LIMIT (CSP-CSN CURRENT SENSING)

The external current sense resistor ( $R_{SENSE}$ ) sets the maximum peak current. The maximum voltage across  $R_{SENSE}$  is 50mV (typical) at very low switch duty cycles, and then slope compensation decreases the current limit as the duty cycle increases (see the *Max Current Limit vs Duty Cycle (CSP-CSN)* plot in the Typical Performance Characteristics). The equation below gives the switch current limit for a given duty cycle and current sense resistor (find  $V_{CSPN}$  at the operating duty cycle in the plot mentioned).

$$I_{SW(LIMIT)} = \frac{V_{CSPN}}{R_{SENSE}}$$

To provide a desired load current for any given application,  $R_{SENSE}$  must be sized appropriately. The equation below calculates  $R_{SENSE}$  for a desired output current:

$$R_{SENSE} \leq 0.74 \bullet \eta \bullet \frac{V_{CSPN}}{I_{OUT}} \bullet \left(1 - DC_{MAX}\right) \bullet \left(1 - \frac{i_{RIPPLE}}{2}\right)$$

$\eta$  = Converter efficiency (assume ~90%)

V<sub>CSPN</sub> = Max current limit voltage (see *Max Current Limit vs Duty Cycle (CSP-CSN)* plot in the Typical Performance Characteristics)

I<sub>OUT</sub> = Converter load current

DC<sub>MAX</sub> = Switching duty cycle at minimum V<sub>IN</sub> (see Power Switch Duty Cycle in Appendix)

$i_{RIPPLE}$  = Peak-to-peak inductor ripple current percentage at minimum  $V_{IN}$  (recommended to use 25%)

#### **ISP-ISN CURRENT SENSING**

CSP/CSN current sensing is used in switching regulator peak current control.

ISP/ISN current sensing monitors the current of the rectifier switch and helps protect the circuit from overload conditions.

The ISP-ISN circuitry delays switching if the rectifier switch current goes too high. This mechanism also protects the part during short-circuit and overload conditions by keeping the current through the inductor under control.

Let's see a buck mode example.

Figure 9. ISP-ISN Current Sensing Example

A potential controllability problem could occur under short-circuit conditions without rectifier switch current sensing. If the power supply output is short circuited, the feedback amplifier (EA) responds to the low output voltage by raising the control voltage,  $V_C$ , to its peak current limit value. Ideally, the top switch would be turned on, and then turned off as its current exceeded the value indicated by  $V_C$ . However, there is finite response time involved in both the current comparator and turnoff of the top switch. These result in a minimum on time,  $t_{ON(MIN)}$ . When combined with high  $V_{IN}$ , the potential exists for a loss of control.

Expressed mathematically the requirement to maintain control is:

$$f \bullet t_{ON} \le \frac{V_{R(SENSE)\_L} + V_{DS\_NMOS} + I \bullet R}{V_{IN}}$$

where:

f = switching frequency

$t_{ON}$  = switch minimum on time

$V_{R(SENSE)}$  L = voltage drop on high side sense resistor

V<sub>DS\_NMOS</sub> = voltage drop on high side PMOS switch

V<sub>IN</sub> = Input voltage

I • R = inductor I • R voltage drop

If this condition is not observed, the current will not be limited at  $I_{PK}$ , but will cycle-by-cycle ratchet up to some higher value. With rectifier switch current sensing, the current through the inductor would be controlled under the whole clock cycle. The switching will only resume once rectifier switch current has fallen below  $I_{PK}$ .

ISP-ISN current sensing is also used in reverse current detecting for DCM operation.

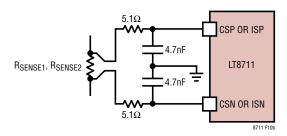

#### **CURRENT SENSE FILTERING**

Certain applications may require filtering of the current sense signals due to excessive switching noise that can appear across R<sub>SENSE1</sub> and/or R<sub>SENSE2</sub>. Higher operating voltages, higher inductor current, higher values of R<sub>SENSE</sub>, and more capacitive MOSFETs will all contribute additional noise across R<sub>SENSE</sub> when MOSFETs transition. The CSP/ CSN and/or the ISP/ISN sense signals can be filtered by adding one of the RC networks shown in Figure 10. The filter shown in Figure 10a filters out differential noise, whereas the filter in Figure 10b filters out the differential and common mode noise at the expense of an additional capacitor and approximately twice the capacitance value. It is recommended to Kelvin tie the ground connection directly to the paddle of the LT8711 if using the filter in Figure 10b. The filter network should be placed as close as possible to the LT8711. Resistors greater than  $10\Omega$ should be avoided as this can Increase the offset voltages at the CSP/CSN and ISP/ISN pins.

Table 6. CSP/CSN, ISP/ISN Bias Current:

|             | V <sub>CM</sub> = 0V | V <sub>CM</sub> > 3V |

|-------------|----------------------|----------------------|

| I_CSP (typ) | 0μΑ                  | 4μΑ ~ 25μΑ           |

| I_CSN (typ) | –4μA ~ –25μA         | 110µA                |

| I_ISP (typ) | 0μΑ                  | 4μΑ ~ 25μΑ           |

| I_ISN (typ) | –4μA ~ –25μA         | 220μΑ                |

When  $V_{CM}$  changes from 0V to 3V, bias current changes gradually from low side values to high side values as shown in Table 6.

CSN/ISN bias current at high side is proportional to temperature (see the *CSN/ISN Bias Current vs Temperature* plots in the Typical Performance Characteristics).

Positive bias currents flow into the pins. Negative bias currents flow out of the pins.

Bias current of  $4\mu A \sim 25\mu A$  and  $-4\mu A \sim -25\mu A$  in the table changes according to the  $V_C$  voltage.  $4\mu A$  ( $-4\mu A$ ) corresponds to the minimum  $V_C$  voltage.  $25\mu A$  ( $-25\mu A$ ) corresponds to the maximum  $V_C$  voltage.

Figure 10a. Differential RC Filter on CSP/CSN and/or ISP/ISN Pins

Figure 10b. Differential and Common Mode RC Filter on CSP/ CSN and/or ISP/ISN Pins

#### SWITCHING FREQUENCY

The LT8711 uses a constant frequency architecture whose frequency can be between 100kHz and 750kHz. The frequency can be set using the internal oscillator or can be synchronized to an external clock source. Selection of

the switching frequency is a trade-off between efficiency and component size. Low frequency operation increases efficiency by reducing MOSFET switching losses, but requires larger inductance and/or capacitance to maintain low output ripple voltage. For high power applications, consider operating at lower frequencies to minimize MOSFET heating from switching losses. The switching frequency can be set by placing an appropriate resistor from the RT pin to ground and tying the SYNC pin low. The frequency can also be synchronized to an external clock source driven into the SYNC pin. The following sections provide more details.

### Oscillator Timing Resistor (RT)

The operating frequency of the LT8711 can be set by the internal free-running oscillator. When the SYNC pin is driven low (< 0.4V), the frequency of operation is set by a resistor from the RT pin to ground. The oscillator frequency is calculated using the following formula:

$$f = \frac{25000}{R_T + 2}$$

where f is in kHz and  $R_T$  is in k $\Omega$ . Conversely,  $R_T$  can be calculated from the desired frequency using:

$$R_T = \frac{25000}{f} - 2$$

#### **Clock Synchronization**

An external source can set the operating frequency of the LT8711 by providing a digital clock signal into the SYNC pin (RT resistor still required). The LT8711 will operate at the SYNC clock frequency. The LT8711 will revert to its internal free-running oscillator clock when the SYNC pin is driven below 0.4V for a few free-running clock periods. The LT8711 will operate in FCM mode with internal free-running oscillator clock if driving SYNC high for an extended period of time.

The duty cycle of the SYNC signal must be between 20% and 80% for proper operation. Also, the frequency of the SYNC signal must meet the following two criteria:

1. SYNC may not toggle outside the frequency range of 140kHz to 750kHz unless it is stopped below 0.4V to enable the free-running oscillator.

The SYNC frequency can always be higher than the freerunning oscillator frequency (as set by the R<sub>T</sub> resistor), f<sub>OSC</sub>, but should not be less than 20% below f<sub>OSC</sub>.

#### LDO REGULATORS

The LT8711 has two linear regulators to run the BG and TG gate drivers. The  $INTV_{CC}$  LDO regulates 5V (typical) above ground, and the  $INTV_{EE}$  regulator regulates 5.15V (typical) below the BIAS pin.

#### INTV<sub>CC</sub> LDO Regulator

The INTV<sub>CC</sub> LDO is used as the top rail for the BG gate driver. An external capacitor greater than  $2.2\mu F$  must be placed from the INTV<sub>CC</sub> pin to ground. The capacitor should have low ESR, such as a ceramic capacitor.

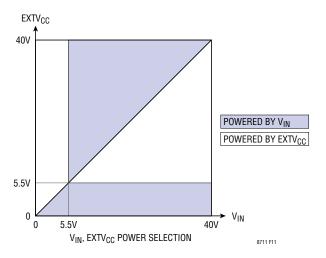

The  $INTV_{CC}$  LDO can run off  $V_{IN}$  or  $EXTV_{CC}$  and will intelligently select to run off the best rail for minimizing chip power loss, but at the same time, select the proper input for maintaining  $INTV_{CC}$  as close to 5V as possible. For example, Figure 11 is a plot that shows how  $V_{IN}$  or  $EXTV_{CC}$  is selected.

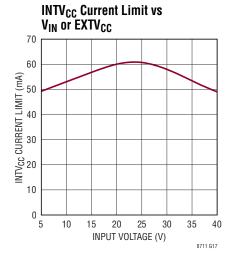

Overcurrent protection circuitry typically limits the maximum current draw from the LDO to ~50mA. If the selected input voltage is greater than 24V (typical), then the current limit of the LDO reduces linearly with input voltage to limit the maximum power in the INTV<sub>CC</sub> pass device. See the INTV<sub>CC</sub> Current Limit vs  $V_{IN}$  or  $EXTV_{CC}$  plot in the Typical Performance Characteristics.

Figure 11. INTV<sub>CC</sub> Input Voltage Selection

Rev A

Power dissipated in the INTV $_{CC}$  LDO should be minimized to improve efficiency and prevent overheating of the LT8711. The current limit reduction with input voltage circuit helps prevent the part from overheating, but these guidelines should be followed. The maximum current drawn through the INTV $_{CC}$  LDO occurs under the following conditions:

- Large (capacitive) MOSFETs being driven at high frequencies

- 2. The converter's switch voltage ( $V_{IN}$  for BUCK,  $V_{OUT}$  for BOOST and BUCK-BOOST,  $V_{IN} + V_{OUT}$  for SEPIC converters) is high, thus requiring more charge to turn the MOSFET gates on and off.

In general, use appropriately sized MOSFETs and lower the switching frequency for higher voltage applications to keep the INTV $_{\rm CC}$  current at a minimum.

## **INTV<sub>EE</sub> LDO Regulator**

The BIAS and INTV<sub>EE</sub> voltages are used for the top and bottom rails of the TG gate driver respectively. An external capacitor greater than  $2.2\mu F$  must be placed between the BIAS and INTV<sub>EE</sub> pins. The capacitor should have low ESR, such as ceramic capacitor.

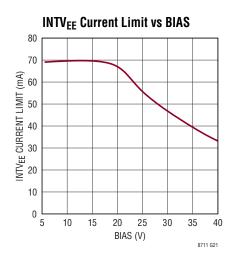

Overcurrent protection circuitry typically limits the maximum current draw from the regulator to  $\sim 80 \text{mA}$ . If the BIAS voltage is greater than 15V (typical), then the current limit of the regulator reduces linearly with input voltage to limit the maximum power in the INTV<sub>EE</sub> pass device. See the *INTV<sub>EE</sub> Current Limit vs BIAS* plot in the Typical Performance Characteristics.

The same thermal guidelines from the  $INTV_{CC}$  LDO Regulator section apply to the  $INTV_{FF}$  regulator as well.

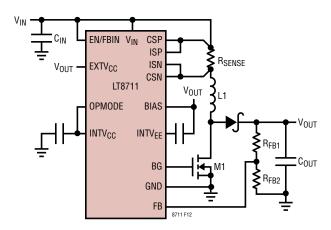

#### NONSYNCHRONOUS CONVERTER

It may be desirable in some applications to replace the external PFET with a Schottky diode to make a nonsynchronous converter. One example would be a high output voltage application because the voltage drop across the rectifier has a small effect on the efficiency of the converter. In fact, for high output voltage applications, replacing the PFET with a Schottky may result in higher efficiency

because the LT8711 doesn't have to supply gate drive to the PFET. Figure 12 shows the recommended connections for using the LT8711 as a nonsynchronous boost converter, however the same concept can be used for any other converter topology.

Figure 12. Simplified Schematic of a Nonsynchronous Boost Converter

# LAYOUT GUIDELINES FOR BUCK, BOOST, SEPIC, ZETA AND BUCK-BOOST TOPOLOGIES

#### **General Layout Guidelines**

- To optimize thermal performance, solder the exposed pad of the LT8711 to the ground plane with multiple vias around the pad connecting to additional ground planes.

- High speed switching path (see specific topology below for more information) must be kept as short as possible.

- The FB, V<sub>C</sub> and RT components should be placed as close to the LT8711 as possible, while being far away as practically possible from switching nodes. The ground for these components should be separated from the switch current path.

- Place bypass capacitors for the V<sub>IN</sub> and EXTV<sub>CC</sub> pins (1µF or greater) as close as possible to the LT8711.

- Place bypass capacitors for the INTV<sub>CC</sub> and INTV<sub>EE</sub> (between BIAS and INTV<sub>EE</sub>) pins (2.2μF or greater) as close as possible to the LT8711.

The load should connect directly to the positive and negative terminals of the output capacitor for best load regulation.

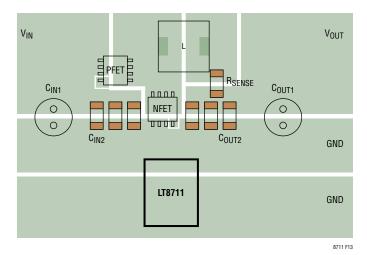

#### **BUCK Topology Specific Layout Guidelines**

Keep length of loop (high speed switching path) governing MN, MP, C<sub>IN</sub>, and ground return as short as possible to minimize parasitic inductive spikes at the switch node during switching.

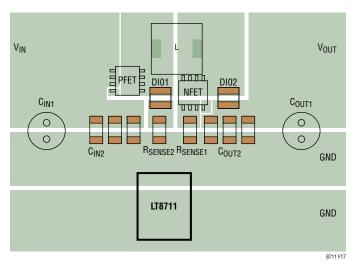

Figure 13. Suggested Component Placement for Buck Topology

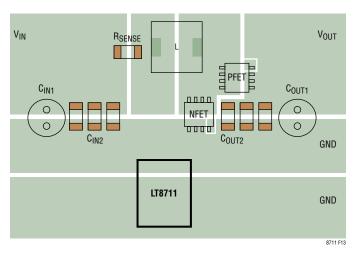

#### **Boost Topology Specific Layout Guidelines**

Keep length of loop (high speed switching path) governing MN, MP, C<sub>OUT</sub>, and ground return as short as possible to minimize parasitic inductive spikes at the switch node during switching.

Figure 14. Suggested Component Placement for Boost Topology

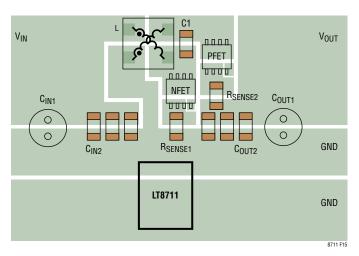

#### **SEPIC Topology Specific Layout Guidelines**

Keep length of loop (high speed switching path) governing R<sub>SENSE1</sub>, MN, C1, MP, R<sub>SENSE2</sub>, C<sub>OUT</sub>, and ground return as short as possible to minimize parasitic inductive spikes at the switch node during switching.

Figure 15. Suggested Component Placement for SEPIC Topology

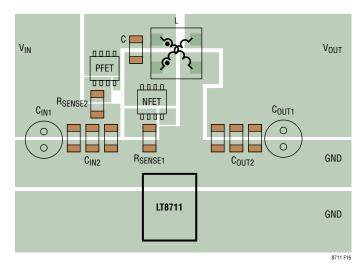

### **ZETA Topology Specific Layout Guidelines**

Keep length of loop (high speed switching path) governing R<sub>SENSE1</sub>, MN, C1, MP, R<sub>SENSE2</sub>, C<sub>IN</sub>, and ground return as short as possible to minimize parasitic inductive spikes at the switch node during switching.

Figure 16. Suggested Component Placement for ZETA Topology

Rev A

#### **Buck-Boost Topology Specific Layout Guidelines**

- Keep length of loop (high speed switching path) governing R<sub>SENSE1</sub>, DIO1, MP, C<sub>IN</sub>, and ground return as short as possible to minimize parasitic inductive spikes at the switch node during switching.