LTC1345

# Single Supply V.35 Transceiver

### FEATURES

- Single Chip Provides All V.35 Differential Clock and Data Signals

- Operates From Single 5V Supply

- Software Selectable DTE or DCE Configuration

- Transmitters and Receivers Will Withstand Repeated ±10kV ESD Pulses

- Shutdown Mode Reduces I<sub>CC</sub> to 1µA Typ

- 10MBaud Transmission Rate

- Transmitter Maintains High Impedance When Disabled, Shut Down, or with Power Off

- Meets CCITT V.35 Specification

- Transmitters are Short-Circuit Protected

### **APPLICATIONS**

- Modems

- Telecommunications

- Data Routers

### DESCRIPTION

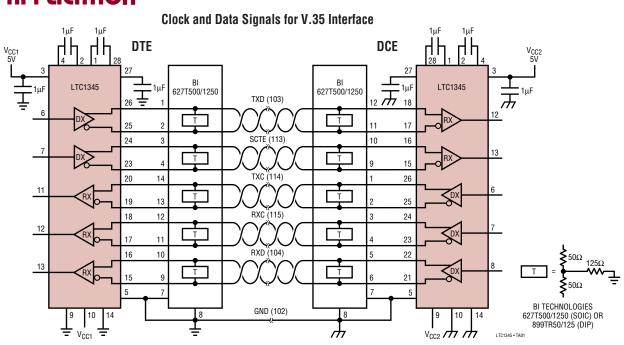

The LTC<sup>®</sup>1345 is a single chip transceiver that provides the differential clock and data signals for a V.35 interface from a single 5V supply. Combined with an external resistor termination network and an LT<sup>®</sup>1134A RS232 transceiver for the control signals, the LTC1345 forms a complete low power DTE or DCE V.35 interface port operating from a single 5V supply.

The LTC1345 features three current output differential transmitters, three differential receivers, and a charge pump. The transceiver can be configured for DTE or DCE operation or shut down using two Select pins. In the Shutdown mode, the supply current is reduced to  $1\mu$ A.

The transceiver operates up to 10Mbaud. All transmitters feature short-circuit protection and a Receiver Output Enable pin allows the receiver outputs to be forced into a high impedance state. Both transmitter outputs and receiver inputs feature  $\pm 10kV$  ESD protection. The charge pump features a regulated V<sub>EE</sub> output using three external 1µF capacitors.

C, LTC and LT are registered trademarks of Linear Technology Corporation.

### TYPICAL APPLICATION

### **ABSOLUTE MAXIMUM RATINGS**

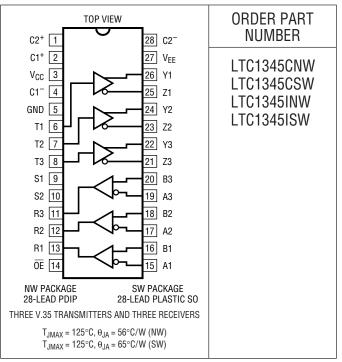

### **PACKAGE/ORDER INFORMATION**

Consult factory for Military grade parts.

**DC ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>CC</sub> = 5V ±5% (Notes 2, 3), unless otherwise specified.

| SYMBOL           | PARAMETER                                     | CONDITIONS                                     |   | MIN   | ТҮР      | MAX  | UNITS   |

|------------------|-----------------------------------------------|------------------------------------------------|---|-------|----------|------|---------|

| V <sub>OD</sub>  | Transmitter Differential Output Voltage       | Figure 1, $-4V \le V_{OS} \le 4V$              |   | 0.44  | 0.55     | 0.66 | V       |

| V <sub>OC</sub>  | Transmitter Common-Mode Output Voltage        | Figure 1, V <sub>OS</sub> = 0V                 | ٠ | -0.6  | 0        | 0.6  | V       |

| I <sub>OH</sub>  | Transmitter Output High Current               | V <sub>Y, Z</sub> = 0V                         |   | -12.6 | -11      | -9.4 | mA      |

| I <sub>OL</sub>  | Transmitter Output Low Current                | V <sub>Y, Z</sub> = 0V                         |   | 9.4   | 11       | 12.6 | mA      |

| I <sub>OZ</sub>  | Transmitter Output Leakage Current            | $S1 = S2 = 0V, -5V \le V_{Y, Z} \le 5V$        |   |       | ±1       | ±100 | μA      |

| R <sub>0</sub>   | Transmitter Output Impedance                  | $-2V \le V_{Y, Z} \le 2V$                      |   |       | 100      |      | kΩ      |

| V <sub>TH</sub>  | Differential Receiver Input Threshold Voltage | $-7V \le (V_A + V_B)/2 \le 7V$                 |   |       | 25       | 200  | mV      |

| $\Delta V_{TH}$  | Receiver Input Hysterisis                     | $-7V \le (V_A + V_B)/2 \le 7V$                 |   |       | 50       |      | mV      |

| I <sub>IN</sub>  | Receiver Input Current (A, B)                 | $-7V \le V_{A, B} \le 7V$                      |   |       |          | 0.4  | mA      |

| R <sub>IN</sub>  | Receiver Input Impedance                      | $-7V \le V_{A, B} \le 7V$                      |   | 17.5  | 30       |      | kΩ      |

| V <sub>OH</sub>  | Receiver Output High Voltage                  | I <sub>0</sub> = 4mA, V <sub>B, A</sub> = 0.2V |   | 3     | 4.5      |      | V       |

| V <sub>OL</sub>  | Receiver Output Low Voltage                   | $I_0 = 4mA, V_{B, A} = -0.2V$                  |   |       | 0.2      | 0.4  | V       |

| I <sub>OSR</sub> | Receiver Output Short-Circuit Current         | $0V \le V_0 \le V_{CC}$                        |   | 7     |          | 85   | mA      |

| I <sub>OZR</sub> | Receiver Three-State Output Current           | $S1 = S2 = 0V, 0V \le V_0 \le V_{CC}$          |   |       |          | ±10  | μA      |

| V <sub>IH</sub>  | Logic Input High Voltage                      | T, S1, S2, 0E                                  |   | 2     |          |      | V       |

| V <sub>IL</sub>  | Logic Input Low Voltage                       | T, S1, S2, 0E                                  |   |       |          | 0.8  | V       |

| I <sub>IN</sub>  | Logic Input Current                           | T, S1, S2, 0E                                  |   |       |          | ±10  | μA      |

| I <sub>CC</sub>  | V <sub>CC</sub> Supply Current                | Figure 1, $V_{OS}$ = 0, S1 = S2 = HIGH         |   |       | 118      | 170  | mA      |

|                  |                                               | No Load, $S1 = S2 = HIGH$                      |   |       | 19       | 30   | mA      |

| M                | V. Voltoro                                    | Shutdown, $S1 = S2 = 0V$                       |   |       | I<br>5.5 | 100  | μΑ<br>V |

| V <sub>EE</sub>  | V <sub>EE</sub> Voltage                       | No Load, S1 = S2 = HIGH                        |   |       | -5.5     |      | V       |

### AC ELECTRICAL CHARACTERISTICS

The • denotes specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{CC} = 5V \pm 5\%$  (Notes 2, 3), unless otherwise specified.

| SYMBOL                          | PARAMETER                                                       | CONDITIONS                                | MIN | ТҮР | MAX | UNITS |

|---------------------------------|-----------------------------------------------------------------|-------------------------------------------|-----|-----|-----|-------|

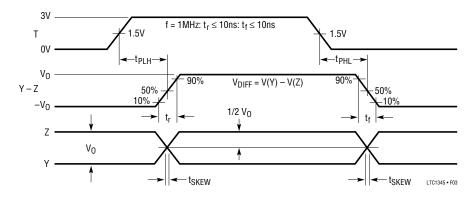

| t <sub>R</sub> , t <sub>F</sub> | Transmitter Rise or Fall Time                                   | Figures 1 and 3, $V_{OS} = 0V$            |     | 7   | 40  | ns    |

| t <sub>PLH</sub>                | Transmitter Input to Output                                     | Figures 1 and 3, $V_{OS} = 0V$            |     | 25  | 70  | ns    |

| t <sub>PHL</sub>                | Transmitter Input to Output 🏾 雀                                 | Figures 1 and 3, $V_{OS} = 0V$            |     | 25  | 70  | ns    |

| t <sub>SKEW</sub>               | Transmitter Output to Output                                    | Figures 1 and 3, $V_{OS} = 0V$            |     | 0   |     | ns    |

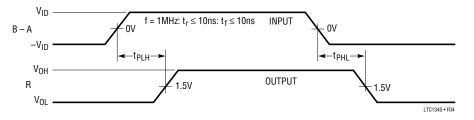

| t <sub>PLH</sub>                | Receiver Input to Output                                        | Figures 1 and 4, $V_{OS} = 0V$            |     | 49  | 100 | ns    |

| t <sub>PHL</sub>                | Receiver Input to Output                                        | Figures 1 and 4, $V_{OS} = 0V$            |     | 52  | 100 | ns    |

| t <sub>SKEW</sub>               | Differential Receiver Skew, t <sub>PLH</sub> – t <sub>PHL</sub> | Figures 1 and 4, $V_{OS} = 0V$            |     | 3   |     | ns    |

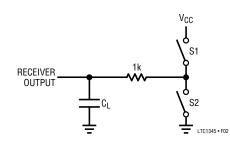

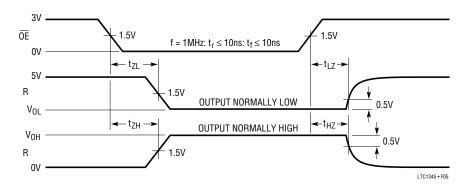

| t <sub>ZL</sub>                 | Receiver Enable to Output LOW                                   | Figures 2 and 5, $C_L = 15pF$ , S1 Closed |     | 40  | 70  | ns    |

| t <sub>ZH</sub>                 | Receiver Enable to Output HIGH                                  | Figures 2 and 5, $C_L = 15pF$ , S2 Closed |     | 35  | 70  | ns    |

| t <sub>LZ</sub>                 | Receiver Disable From LOW                                       | Figures 2 and 5, $C_L = 15pF$ , S1 Closed |     | 30  | 70  | ns    |

| t <sub>HZ</sub>                 | Receiver Disable From HIGH                                      | Figures 2 and 5, $C_L = 15pF$ , S2 Closed |     | 35  | 70  | ns    |

| f <sub>OSC</sub>                | Charge Pump Oscillator Frequency                                |                                           |     | 200 |     | kHz   |

| BR <sub>MAX</sub>               | Maximum Data Rate (Note 4)                                      |                                           | 10  | 15  |     | Mbaud |

Note 1: The absolute maximum ratings are those values beyond which the safety of the device cannot be guaranteed.

Note 2: All currents into device pins are termed positive; all currents out of device pins are termed negative. All voltages are referenced to device ground unless otherwise specified.

Note 3: All typicals are given for  $V_{CC} = 5V$ ,  $C1 = C2 = C3 = 1\mu F$  ceramic capacitors and  $T_A = 25^{\circ}C$ .

Note 4: Maximum data rate is specified for NRZ data encoding scheme. The maximum data rate may be different for other data encoding schemes. Data rate is guaranteed by correlation and is not tested.

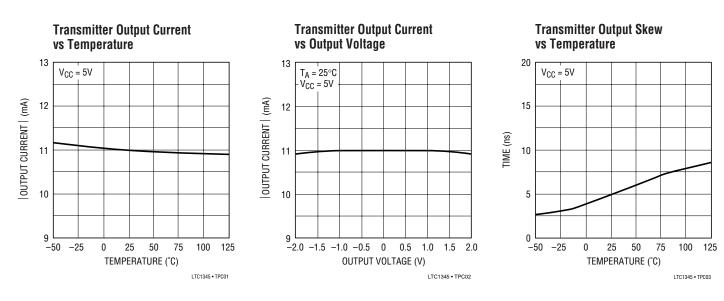

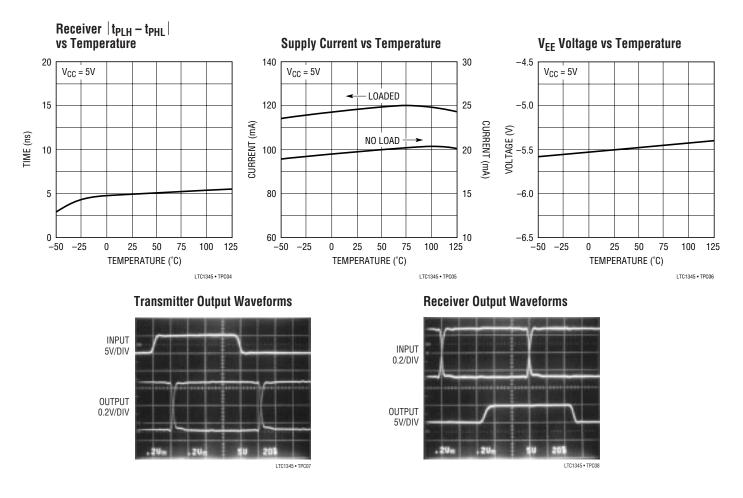

# **TYPICAL PERFORMANCE CHARACTERISTICS**

# TYPICAL PERFORMANCE CHARACTERISTICS

### PIN FUNCTIONS

- C2+ (Pin 1): Capacitor C2 Positive Terminal.

- C1+ (Pin 2): Capacitor C1 Positive Terminal.

- **V<sub>CC</sub> (Pin 3)**: Positive Supply,  $4.75 \le V_{CC} \le 5.25V$ .

- C1<sup>-</sup> (Pin 4): Capacitor C1 Negative Terminal.

- **GND (Pin 5):** Ground. The positive terminal of C3 is connected to ground.

- **T1 (Pin 6):** Transmitter 1 Input.

- T2 (Pin 7): Transmitter 2 Input.

- T3 (Pin 8): Transmitter 3 Input.

- S1 (Pin 9): Select Input 1.

- S2 (Pin 10): Select Input 2.

- R3 (Pin 11): Receiver 3 Output.

- R2 (Pin 12): Receiver 2 Output.

- R1 (Pin 13): Receiver 1 Output.

- **OE** (Pin 14): Receiver Output Enable.

- A1 (Pin 15): Receiver 1 Inverting Input.

- B1 (Pin 16): Receiver 1 Noninverting Input.

- A2 (Pin 17): Receiver 2 Inverting Input.

- B2 (Pin 18): Receiver 2 Noninverting Input.

- A3 (Pin 19): Receiver 3 Inverting Input.

- B3 (Pin 20): Receiver 3 Noninverting Input.

- Z3 (Pin 21): Transmitter 3 Inverting Output.

### **PIN FUNCTIONS**

- Y3 (Pin 22): Transmitter 3 Noninverting Output.

- **Z2 (Pin 23):** Transmitter 2 Inverting Output.

- Y2 (Pin 24): Transmitter 2 Noninverting Output

- **Z1 (Pin 25):** Transmitter 1 Inverting Output.

### FUNCTION TABLES

**Transmitter and Receiver Configuration**

| <b>S1</b> | \$2 | TX#     | RX#     | REMARKS                 |

|-----------|-----|---------|---------|-------------------------|

| 0         | 0   | —       | —       | Shutdown                |

| 1         | 0   | 1, 2, 3 | 1, 2    | DCE Mode, RX3 Shut Down |

| 0         | 1   | 1, 2    | 1, 2, 3 | DTE Mode, TX3 Shut Down |

| 1         | 1   | 1, 2, 3 | 1, 2, 3 | All Active              |

#### Transmitter

|               | INPUTS    |    |   | OUTPUTS   |           |    |    |  |

|---------------|-----------|----|---|-----------|-----------|----|----|--|

| CONFIGURATION | <b>S1</b> | S2 | Т | Y1 AND Y2 | Z1 AND Z2 | Y3 | Z3 |  |

| DTE           | 0         | 1  | 0 | 0         | 1         | Ζ  | Ζ  |  |

| DTE           | 0         | 1  | 1 | 1         | 0         | Ζ  | Ζ  |  |

| DCE or All ON | 1         | Х  | 0 | 0         | 1         | 0  | 1  |  |

| DCE or All ON | 1         | Х  | 1 | 1         | 0         | 1  | 0  |  |

| Shutdown      | 0         | 0  | Х | Z         | Z         | Ζ  | Z  |  |

### Y1 (Pin 26): Transmitter 1 Noninverting Output.

**V<sub>EE</sub> (Pin 27):** Charge Pump Output. Connected to negative terminal of capacitor C3.

C2<sup>-</sup> (Pin 28): Capacitor C2 Negative Terminal.

#### Receiver

|               |    |            | INPU | JTS    | OUTPUTS   |    |  |

|---------------|----|------------|------|--------|-----------|----|--|

| CONFIGURATION | S1 | <b>S</b> 2 | ŌE   | B – A  | R1 AND R2 | R3 |  |

| DTE or All ON | Х  | 1          | 0    | ≥0.2V  | 1         | 1  |  |

| DTE or All ON | Х  | 1          | 0    | ≤-0.2V | 0         | 0  |  |

| DCE           | 1  | 0          | 0    | ≥0.2V  | 1         | Z  |  |

| DCE           | 1  | 0          | 0    | ≤-0.2V | 0         | Z  |  |

| Disabled      | Х  | Х          | 1    | Х      | Z         | Z  |  |

| Shutdown      | 0  | 0          | Х    | Х      | Z         | Z  |  |

### **TEST CIRCUITS**

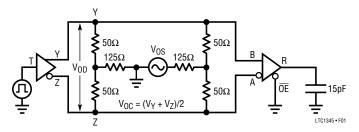

Figure 1. V.35 Transmitter/Receiver Test Circuit

Figure 2. Receiver Output Enable/Disable Timing Test Load

# SWITCHING TIME WAVEFORMS

Figure 3. V.35 Transmitter Propagation Delays

Figure 4. V.35 Receiver Propagation Delays

Figure 5. Receiver Enable and Disable Times

#### Review of CCITT Recommendation V.35 Electrical Specifications

V.35 is a CCITT recommendation for synchronous data transmission via modems. Appendix 2 of the recommendation describes the electrical specifications which are summarized below:

1. The interface cable is balanced twisted-pair with  $80\Omega$  to  $120\Omega$  impedance.

2. The transmitter's source impedance is between  $50\Omega$  and  $150\Omega.$

3. The transmitter's resistance between shorted terminals and ground is  $150\Omega \pm 15\Omega.$

4. When terminated by a  $100\Omega$  resistive load, the terminal-to-terminal voltage should be 0.55V  $\pm 20\%$ .

5. The transmitter's rise time should be less than 1% of the signal pulse or 40ns, whichever is greater.

6. The common-mode voltage at the transmitter output should not exceed 0.6V.

7. The receiver impedance is  $100\Omega \pm 10\Omega$ .

8. The receiver impedance to ground is  $150\Omega \pm 15\Omega$ .

9. The transmitter or receiver should not be damaged by connection to earth ground, short-circuiting, or cross connection to other lines.

10. No data errors should occur with  $\pm 2V$  common-mode change at either the transmitter or receiver, or  $\pm 4V$  ground potential difference between transmitter and receiver.

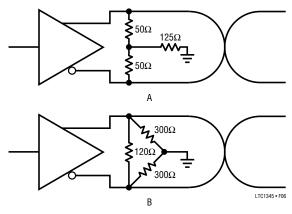

#### **Cable Termination**

Each end of the cable connected to an LTC1345 must be terminated by either one of two electrically equivalent external Y or  $\Delta$  resistor networks for proper operation. The Y-termination has two series connected 50 $\Omega$  resistors and a 125 $\Omega$  resistor connected between ground and the center tap of the two 50 $\Omega$  resistors as shown in Figure 6A.

Figure 6. Y and  $\Delta$  Termination Networks

The alternative  $\Delta$ -termination has a 120 $\Omega$  resistor across the twisted wires and two 300 $\Omega$  resistors between each wire and ground as shown in Figure 6B. Standard 1/8W, 5% surface mount resistors can be used for the termination network. To maintain the proper differential output swing, the resistor tolerance must be 5% or less. A termination network that combines all the resistors into an SO-14 package is available from:

BI Technologies (Formerly Beckman Industrial) Resistor Networks 4200 Bonita Place Fullerton, CA 92635 Phone: (714) 447-2357 FAX: (714) 447-2500 Part #: BI Technologies 627T500/1250 (SOIC) 899TR50/125 (DIP)

### **Theory of Operation**

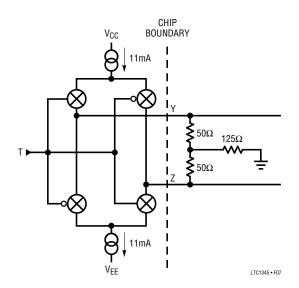

The transmitter output consists of complementary switched-current sources as shown in Figure 7.

Figure 7. Simplified Transmitter Schematic

With a logic zero at the transmitter input, the inverting output Z sources 11mA and the noninverting output Y sinks 11mA. The differential transmitter output voltage is then set by the termination resistors. With two differential 50 $\Omega$  resistors at each end of the cable, the voltage is set to  $(50\Omega \times 11\text{mA}) = 0.55\text{V}$ . With a logic 1 at the transmitter input, output Z sinks 11mA and Y sources 11mA. The common-mode voltage of Y and Z is 0V when both current sources are matched and there is no ground potential difference between the cable terminations. The transmitter current sources have a common-mode range of  $\pm 2\text{V}$ , which allows for a ground difference between cable terminations of  $\pm 4\text{V}$ .

Each receiver input has a 30k resistance to ground and requires external termination to meet the V.35 input impedance specification. The receivers have an input hysteresis of 50mV to improve noise immunity. The receiver output

may be forced into a high impedance state by pulling the output enable ( $\overline{OE}$ ) pin high. For normal operation  $\overline{OE}$  should be pulled low.

A charge pump generates the regulated negative supply voltage ( $V_{EE}$ ) with three 1µF capacitors. Commutating capacitors C1 and C2 form a voltage doubler and inverter while C3 acts as a reservoir capacitor. To insure proper operation, the capacitors must have an ESR less than 1 $\Omega$ . Monolithic ceramic or solid tantalum capacitors are good choices. Under light loads, regulation at about –5.2V is provided by a pulse-skipping scheme. Under heavy loads the charge pump is on continuously. A small ripple of about 500mV will be present on V<sub>EE</sub>.

Two Select pins, S1 and S2, configure the chip for DTE, DCE, all transmitters and receivers on, or Shutdown. In Shutdown mode,  $I_{CC}$  drops to  $1\mu$ A. The outputs of the transmitters and receivers are in high impedance states, the charge pump stops and V<sub>EE</sub> is clamped to ground.

### **ESD** Protection

LTC1345 transmitter outputs and receiver inputs have onchip protection from multiple  $\pm 10$ kV ESD transients. ESD testing is done using the Human Body ESD Model. ESD testing must be done with an AC ground on the V<sub>CC</sub> and V<sub>EE</sub> supply pins. The low ESR supply decoupling and V<sub>EE</sub> reservoir capacitors provide this AC ground during normal operation.

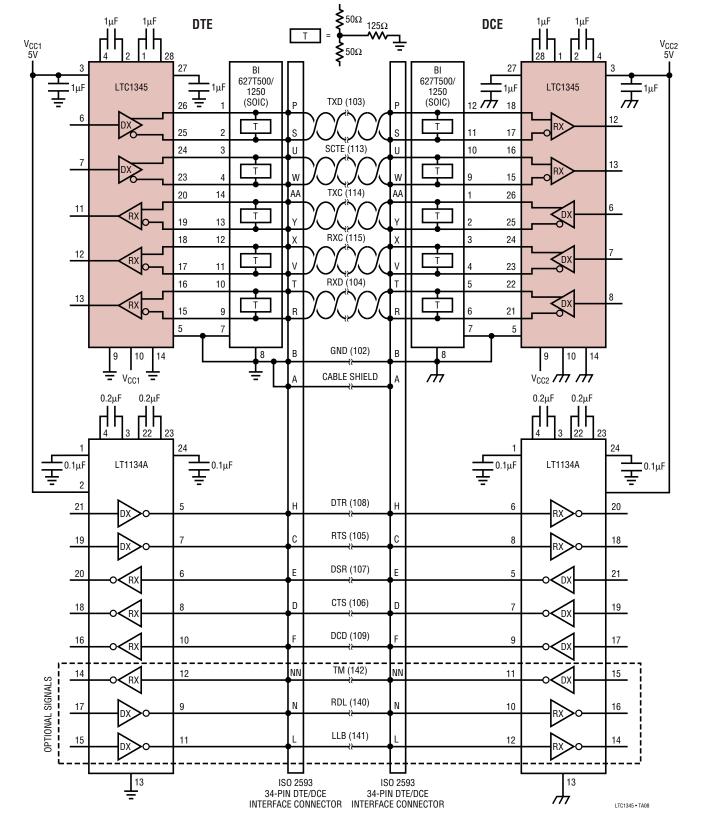

### **Complete V.35 Port**

Figure 8 shows the schematic of a complete surface mounted, single 5V DTE and DCE V.35 port using only three ICs and eight capacitors per port. The LTC1345 is used to transmit the clock and data signals, and the LT1134A to transmit the control signals. If test signals 140, 141, and 142 are not used, the transmitter inputs should be tied to  $V_{CC}$ .

9

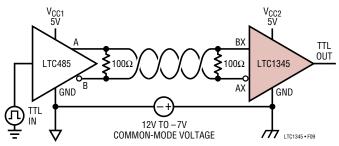

### RS422/RS485 Applications

The receivers on the LTC1345 are ideal for RS422 and RS485 applications. Using the test circuit in Figure 9, the LTC1345 receivers are able to successfully reconstruct the data stream with the common-mode voltage meeting RS422 and RS485 requirements (12V to -7V).

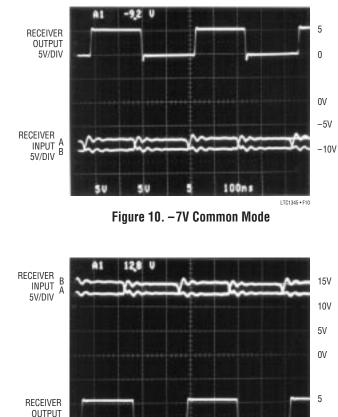

Figures 10 and 11 show that the LTC1345 receivers are very capable of reconstructing data at rates up to 10Mbaud.

Figure 9 RS422/RS485 Receiver Interface

Figure 11. 12V Common Mode

510

100ns

5V/DIV

0

1 TC1345 • F11

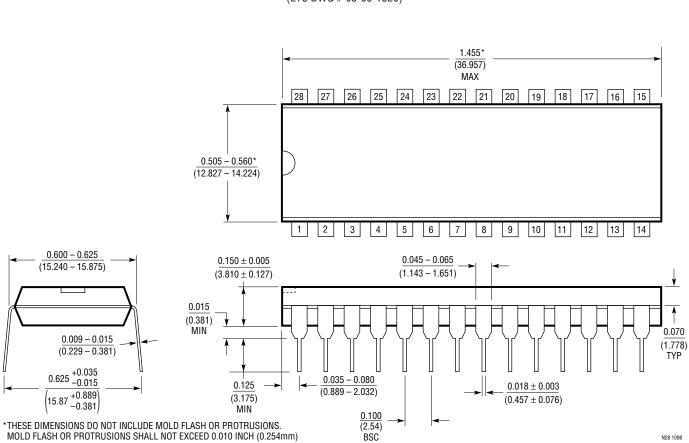

# **PACKAGE DESCRIPTION** Dimensions in inches (millimeters) unless otherwise noted.

NW Package 28-Lead PDIP (Wide 0.600) (LTC DWG # 05-08-1520)