LTC1566-1

GY Low Noise 2.3MHz Continuous Time Lowpass Filter

### FEATURES

- 7th Order, 2.3MHz Lowpass Filter in an SO-8

- 62µV<sub>RMS</sub> Input Referred Noise

- Operates on a Single 5V or a ±5V Supply

- Differential Inputs and Outputs

- Low Offset (3mV typical, 10mV<sub>MAX</sub>)

- Adjustable Output Common Mode Voltage

- 40dB Attenuation at 1.5 × f<sub>CUTOFF</sub>

- Requires No External Components

#### **APPLICATIONS**

- WCDMA Basestations

- Communication Filters

- Antialiasing Filters

- Smoothing or Reconstruction Filters

- Matched Filter Pairs

- Replacement for LC Filters

## DESCRIPTION

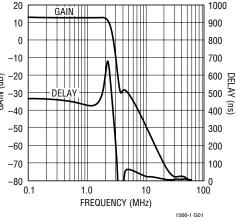

The LTC<sup>®</sup>1566-1 is a 7th order continuous time lowpass filter with 12dB of passband gain. The selectivity, linearity and dynamic range makes the LTC1566-1 suitable for filtering in data communications or data acquisition systems. The filter attenuation is 40dB at  $1.5 \times f_{CUTOFF}$  and at least 60dB for frequencies above 10MHz.

The LTC1566-1 has an input referred noise of  $62\mu V_{RMS}$  in a 2MHz bandwidth. In receiver applications where the signal levels are small, the filter features 71dB of spurious free dynamic range.

With 5% accuracy of the cutoff frequency, the LTC1566-1 can be used in applications requiring pairs of matched filters, such as transceiver I and Q channels.

The differential inputs and outputs provide a simple interface for wireless systems. The high impedance inputs are easily coupled to differential demodulators or D/A converters. The output DC common mode voltage and output DC offset voltage are adjustable so the signal path can be optimized for driving an A/D converter or differential modulator.

Other cutoff frequencies and single-ended I/O can be provided upon request. Please contact LTC Marketing.

T, LTC and LT are registered trademarks of Linear Technology Corporation.

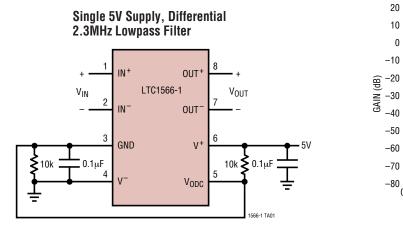

## TYPICAL APPLICATION

#### Frequency Response

15661fa

## **ABSOLUTE MAXIMUM RATINGS**

| (Note | 1) |

|-------|----|

|-------|----|

| Total Supply Voltage                 | 11V           |

|--------------------------------------|---------------|

| Power Dissipation                    | 500mW         |

| Operating Temperature Range          |               |

| LTC1566-1CS                          | 0°C to 70°C   |

| LTC1566-1IS                          | 40°C to 85°C  |

| Storage Temperature Range            | 65°C to 150°C |

| Lead Temperature (Soldering, 10 sec) | )             |

|                                      |               |

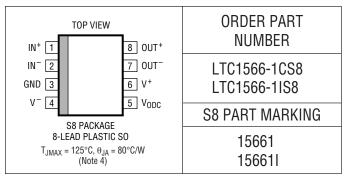

## PACKAGE/ORDER INFORMATION

Consult factory for parts specified with wider operating temperature ranges.

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}$ C.  $V_S = 5V$  (V<sup>+</sup> = 5V, V<sup>-</sup> = 0V),  $R_{LOAD} = 10k$  from each output to AC ground, Pin 5 connected to Pin 3, Pin 3 biased to mid supply, unless otherwise specified.

| PARAMETER                        | CONDITIONS                                                                                            |                                                    | MIN   | ТҮР  | MAX   | UNITS         |

|----------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------|------|-------|---------------|

| Filter Gain, V <sub>S</sub> = 5V | $V_{IN} = 0.25V_{P-P}$ $f_{IN} = 20kHz$ to 100kHz                                                     | •                                                  | 11.8  | 12.1 | 12.3  | dB            |

|                                  | f <sub>IN</sub> = 1.8MHz (Gain Relative to 10                                                         | )0kHz)                                             | -0.35 | 0    | 0.8   | dB            |

|                                  | f <sub>IN</sub> = 2MHz (Gain Relative to 100                                                          | kHz)                                               | -0.85 | -0.1 | 0.8   | dB            |

|                                  | f <sub>IN</sub> = 2.3MHz (Gain Relative to 10                                                         |                                                    | -7.5  | -3   | -0.95 | dB            |

|                                  | f <sub>IN</sub> = 3MHz (Gain Relative to 100                                                          |                                                    |       | -22  | -17   | dB            |

|                                  | f <sub>IN</sub> = 5MHz (Gain Relative to 100                                                          |                                                    |       | -42  |       | dB            |

|                                  | f <sub>IN</sub> = 10MHz (Gain Relative to 10                                                          | 0kHz)                                              |       | -62  |       | dB            |

| Filter Phase, $V_S = \pm 5V$     | $V_{IN} = 0.25V_{P-P}$ $f_{IN} = 900kHz$                                                              | •                                                  | -165  | -150 | -135  | deg           |

|                                  | f <sub>IN</sub> = 1.8MHz                                                                              | •                                                  | -330  | -285 | -265  | deg           |

| Phase Linearity, $V_S = \pm 5V$  | Ratio of phases: 1.8MHz/900kHz                                                                        |                                                    | 1.9   | 1.95 | 2.05  |               |

| Filter Gain, $V_S = \pm 5V$      | $V_{IN} = 0.25 V_{P-P}$ $f_{IN} = 20 kHz$ to 100kHz                                                   |                                                    | 11.9  | 12.1 | 12.3  | dB            |

|                                  | f <sub>IN</sub> = 900kHz (Gain Relative to 10                                                         | f <sub>IN</sub> = 900kHz (Gain Relative to 100kHz) |       | 0    | 0.2   | dB            |

|                                  | $f_{IN} = 1.8 MHz$ (Gain Relative to 10                                                               |                                                    | -0.3  | 0.1  | 0.9   | dB            |

|                                  | f <sub>IN</sub> = 2MHz (Gain Relative to 100kHz)                                                      |                                                    | -0.55 | 0.1  | 0.75  | dB            |

|                                  | f <sub>IN</sub> = 2.3MHz (Gain Relative to 100kHz)                                                    |                                                    | -6    | -2   | -0.3  | dB            |

|                                  | f <sub>IN</sub> = 3MHz (Gain Relative to 100                                                          |                                                    |       | -20  | -16   | dB            |

|                                  | f <sub>IN</sub> = 5MHz (Gain Relative to 100kHz)<br>f <sub>IN</sub> = 10MHz (Gain Relative to 100kHz) |                                                    |       | -41  |       | dB            |

|                                  |                                                                                                       |                                                    |       | -61  |       | dB            |

| Input Referred Wideband Noise    | Noise BW = 50kHz to 2MHz                                                                              | Noise BW = 50kHz to 2MHz                           |       | 62   |       | $\mu V_{RMS}$ |

| THD                              | $f_{IN} = 100 \text{kHz}, V_{OUT} = 2V_{P-P} \text{ (Note 2)}$                                        |                                                    |       | 80   |       | dB            |

| Filter Differential DC Swing     | Maximum Difference Between Pins 7 and Pin 8                                                           | V <sub>S</sub> = 5V                                | ±1.3  | ±1.7 |       | VP            |

|                                  | with Pin 5, Pin 3 Biased to Mid Supply                                                                | $V_{\rm S} = \pm 5V$                               | ±2.7  | ±2.9 |       | VP            |

| Input Bias Current               |                                                                                                       |                                                    |       | 300  | 600   | nA            |

| Input Offset Current             |                                                                                                       |                                                    |       | ±10  |       | nA            |

| Input Resistance                 | Common Mode, $V_{IN} = 1.5V$ to $3.5V$                                                                |                                                    |       | 70   |       | MΩ            |

|                                  | Differential                                                                                          |                                                    |       | 140  |       | MΩ            |

| Input Capacitance                |                                                                                                       |                                                    |       | 2    |       | pF            |

| Output DC Offset                 |                                                                                                       | $V_{S} = 5V$                                       |       | ±3   | ±10   | mV            |

| (Notes 3, 5)                     |                                                                                                       | $V_{S} = \pm 5V$                                   |       | ±3   | ±10   | mV            |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>S</sub> = 5V (V<sup>+</sup> = 5V, V<sup>-</sup> = 0V), R<sub>LOAD</sub> = 10k from each output to AC ground, and Pin 5 connected to Pin 3 unless otherwise specified

| PARAMETER                     | CONDITIONS                             |                                             |   | MIN | ТҮР          | MAX      | UNITS          |

|-------------------------------|----------------------------------------|---------------------------------------------|---|-----|--------------|----------|----------------|

| Output DC Offset Drift        |                                        | V <sub>S</sub> = 5V<br>V <sub>S</sub> = ±5V |   |     | -160<br>-160 |          | μV/°C<br>μV/°C |

| Output DC Common Mode Voltage | $V_{\rm S} = 5V, V_{\rm S} = \pm 2.5V$ |                                             |   |     | -80          |          | mV             |

| Power Supply Current          |                                        | $V_{S} = 5V$<br>$V_{S} = \pm 5V$            | • |     | 24<br>25     | 32<br>34 | mA<br>mA       |

Note 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

**Note 2:** Input and output voltages expressed as peak-to-peak numbers are assumed to be fully differential.

Note 3: Output DC offset is measured between Pin 8 and Pin 7 with Pin 1, Pin 2 and Pin 5 connected to Pin 3. Pin 3 biased to mid supply.

Note 4: Thermal resistance varies depending upon the amount of PC board metal attached to the device.  $\theta_{JA}$  is specified for a 3.8 square inch test board covered with 2oz copper on both sides.

Note 5: Output DC offset measurements are performed by automatic test equipment approximately 0.5 seconds after application of power.

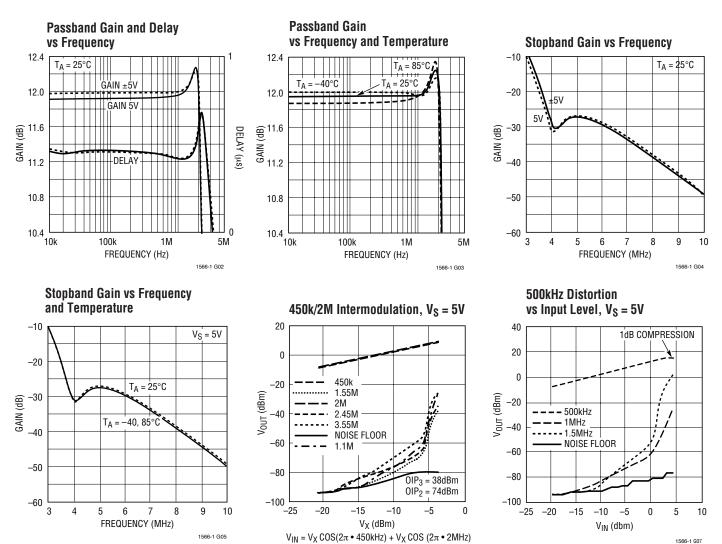

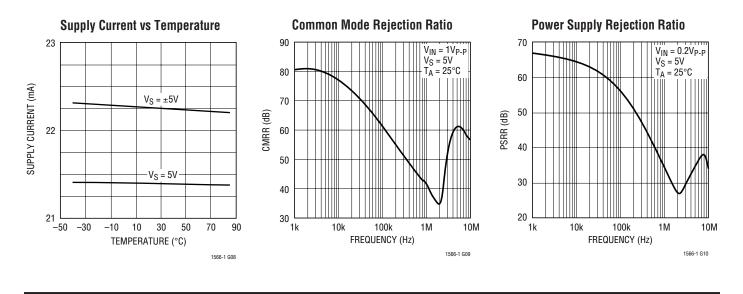

## TYPICAL PERFORMANCE CHARACTERISTICS

15661fa

## **TYPICAL PERFORMANCE CHARACTERISTICS**

## **PIN FUNCTIONS**

**IN+**, **IN-** (**Pins 1, 2**): Input Pins. Signals can be applied to either or both input pins. The DC gain from differential inputs (Pin 1 to Pin 2) to the differential outputs (Pin 8 to Pin 7) is 4V/V. The input range is described in the Applications Information section.

**GND (Pin 3):** Ground. The ground pin is the reference voltage for the filter. This is a high impedance input, which requires an external biasing network. Biasing GND to one-half the total power supply voltage of the filter maximizes the dynamic range. For single supply operation the ground pin should be bypassed with a quality  $0.1\mu$ F ceramic capacitor to Pin 4. For dual supply operation, connect Pin 3 to a high quality DC ground. A ground plane should be used. A poor ground will increase noise and distortion. Pin 3 also serves as the DC reference voltage for Pin 7.

**V<sup>-</sup>, V<sup>+</sup> (Pins 4, 6):** Power Supply Pins. For a single 5V supply (Pin 4 grounded) a quality  $0.1\mu$ F ceramic bypass capacitor is required from the positive supply pin (Pin 6)

to the negative supply pin (Pin 4). The bypass should be as close as possible to the IC. For dual supply applications (Pin 3 is grounded), bypass Pin 6 to Pin 3 and Pin 4 to Pin 3 with a quality  $0.1 \mu$ F ceramic capacitor.

**V**<sub>ODC</sub> (**Pin 5**): Output DC Offset. Pin 5 is the DC reference voltage for Pin 8. By applying a DC offset between Pin 3 and Pin 5, a DC offset will be added to the differential signal between Pin 7 and Pin 8. Like the GND pin, the V<sub>ODC</sub> pin is a high impedance which requires no bias current. Care should be taken when biasing Pin 5 since noise between Pin 3 and Pin 5 will appear at the filter output unattenuated. The frequency response of Pin 5 is described in the Applications Information section.

**OUT<sup>-</sup>**, **OUT<sup>+</sup>** (**Pins 7, 8**): Output Pins. Pins 7 and 8 are the filter differential outputs. Each pin can drive  $1k\Omega$  or 300pF loads. The DC reference voltage of Pin 8 is the same as the voltage at Pin 5. The DC reference voltage of Pin 7 is the same as the voltage at Pin 3.

15661fa

#### $IN^+$ 1× 8 OUT+ 1× R 7th ORDER R FILTER NETWORK WITH 12dB GAIN 1× INPUT AMPLIFIERS OUT-IN<sup>-</sup> 7 2 1× WITH COMMON MODE TRANSLATION CIRCUIT 6 V+ GND 3 UNITY GAIN OUTPUT BUFFERS WITH DC V-4 REFERENCE 5 Vodc AD.IUSTMENT 566-1 BD

#### **BLOCK DIAGRAM**

#### **APPLICATIONS INFORMATION**

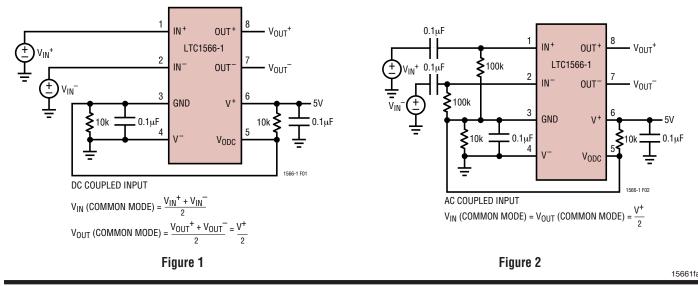

#### Interfacing to the LTC1566-1

The difference between the voltages at Pin 1 and Pin 2 is the "differential input voltage." The average of the voltages at Pin 1 and Pin 2 is the "common mode input voltage." The difference between the voltages at Pin 7 and Pin 8 is the "differential output voltage." The average of the voltages at Pin 7 and Pin 8 is the "common mode output voltage." The input and output common mode voltages are independent. The input common mode voltage is set by the signal source, if DC coupled, or by an external biasing network, if AC coupled (Figures 1 and 2). The output can also be AC coupled.

The output common mode voltage is equal to the voltage of Pin 3, the GND pin, whenever Pin 5 is shorted to Pin 3. In configurations where Pin 5, the  $V_{ODC}$  pin, is not shorted to Pin 3, the output common mode voltage is equal to the average of the voltages at Pin 3 and Pin 5. The operation of Pin 5 is described in the paragraph "Output DC Offset Control". Pin 3 is a high impedance pin and must be biased externally with an external resistor network or reference voltage.

## **APPLICATIONS INFORMATION**

#### Input Common Mode and Differential Voltage Range

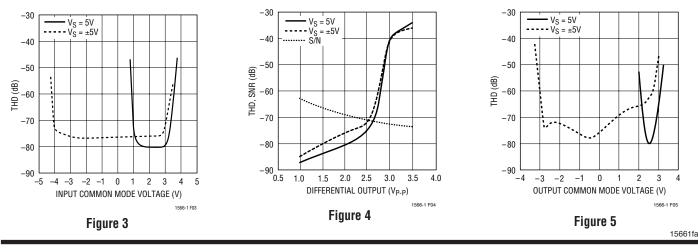

The range of voltage each input can support while operating in its linear region is typically 0.8V to 3.7V for a single 5V supply and -4.2V to 3.2V for a ±5V supply. Therefore, the filter can accept a variety of common mode input voltages. Figure 3 shows the total harmonic distortion of the filter versus input common mode voltage with a  $2V_{P-P}$  differential output signal.

Figure 4 shows the total harmonic distortion and signal to noise ratio versus differential output voltage level for both a single 5V and a  $\pm$ 5V supply. The common mode voltage of the input signal is one-half the total power supply voltage of the filter. The spurious free dynamic range (SFDR), the level where the THD and S/N ratio are equal, is 72dB.

For best performance, the inputs should be driven differentially. For single-ended signals, connect the unused input to Pin 3 or a common mode reference.

The filter DC differential swings listed in the "Electrical Characteristics" are measured with input differential voltages of  $0.9V_{P-P}$  and  $1.5V_{P-P}$  for 5V and  $\pm$ 5V supplies respectively. Ideally the corresponding output levels would be  $3.6V_{P-P}$  and  $6V_{P-P}$ . As seen in Figure 4, these levels are above the range of linear operation. Input signals larger than  $0.9V_{P-P}/1.5V_{P-P}$  will result in phase inversion and should be avoided.

#### **Output Common Mode and Differential Voltage Range**

The output is a fully differential signal with a common mode level equal to the voltage at Pin 3 when Pin 5 is shorted to Pin 3. The best performance is achieved using a common mode voltage that is equal to one-half of the total supply voltage. Figure 5 illustrates the THD versus output common mode voltage for a  $0.5V_{P-P}/2.0V_{P-P}$  differential input/output voltage and a common mode input voltage that is equal to one-half the total supply voltage.

#### **Output DC Offset Control**

A unique feature of the LTC1566-1 is the ability to introduce a differential offset voltage at the output of the filter. As seen in the "Block Diagram", if a DC voltage is applied to Pin 5 with respect to Pin 3, the same voltage will be added to the differential voltage seen between Pins 8 and 7.

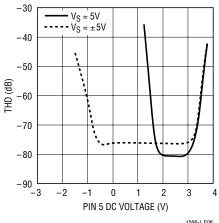

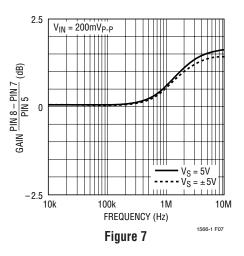

The output DC offset control pin can be used for sideband suppression in differential modulators, calibration of A/D converters, or simple signal summation. Since the voltage summing occurs at the output of the filter, Pin 5 acts as a unfiltered input. The response from Pin 5 to Pin 8 – Pin 7 with Pins 1,2 and 3 grounded is shown in Figure 7. The range of voltages that can be applied to Pin 5 is shown in Figure 6 where THD is plotted versus output offset. Pin 3 is biased to mid supply.

#### **Output Drive**

Pins 7 and 8 can drive a  $1k\Omega$  or 300pF load connected to AC ground with a  $\pm 0.5V$  signal (corresponding to a  $2V_{P-P}$  differential signal). For differential loads (loads connected across Pins 7 and 8) the outputs can produce a  $2V_{P-P}$  differential signal across  $2k\Omega$  or 150pF. For smaller signal amplitudes the outputs can drive correspondingly larger loads.

#### **APPLICATIONS INFORMATION**

Figure 6

#### Noise

The wideband noise of the filter is the RMS value of the output noise power spectral density integrated over a given bandwidth. Since the filter has a DC gain of 4, the wideband noise is divided by 4 when referred to the input. The input referred wideband noise is used to determine the signal-to-noise ratio at a given distortion level and hence the spurious free dynamic range. Most of the noise is concentrated in the filter passband and cannot be removed with post filtering (Table 1). The noise is mostly independent of supply level (Table 2).

# Table 1. Input Referred Wideband Noise vs Bandwidth,Single 5V Supply

| BANDWIDTH     | TOTAL INTEGRATED NOISE |

|---------------|------------------------|

| 50kHz to 2MHz | 62µV <sub>RMS</sub>    |

| 50kHz to 4MHz | 76μV <sub>RMS</sub>    |

## Table 2. Input Referred Wideband Noise vs Supply Voltage, 50kHz to 2MHz

| BANDWIDTH             | TOTAL INTEGRATED NOISE |

|-----------------------|------------------------|

| $V_{\rm S} = 5V$      | 62µV <sub>RMS</sub>    |

| $V_{\rm S} = \pm 5 V$ | 63μV <sub>RMS</sub>    |

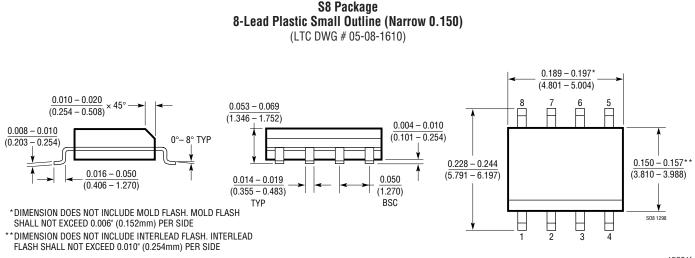

#### PACKAGE DESCRIPTION

Dimensions in inches (millimeters) unless otherwise noted.

TECHNOLOGY

Information furnished by Linear Technology Corporation is believed to be accurate and reliable. However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.