## SMBus Dual High Side Switch Controller

### **FEATURES**

- SMBus and I<sup>2</sup>C Compatible

- Built-In Charge Pumps Drive N-Channel Switches

- 16 Available Switches on the Same Bus

- 0.6V V<sub>IL</sub> and 1.4V V<sub>IH</sub> for DATA and CLK

- Available in 8-Lead MSOP and SO Packages

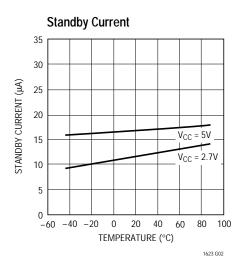

- Low Standby Current: 14μA

- Eight Addresses from Two Three-State Address Pins

- Internal Power-On Reset Timer

- Internal Undervoltage Lockout

- No Need for External Pull-Up Resistors at Output

- No Need for Secondary Power Source

### **APPLICATIONS**

- Computer Peripheral Control

- Laptop Computer Power Plane Switching

- Portable Equipment Power Control

- Industrial Control Systems

- Handheld Equipment

### **DESCRIPTION**

The LTC  $^{\circ}$ 1623 SMBus switch controller is a slave device that controls two high-side N-channel MOSFETs on either the SMBus or the I $^{2}$ C bus. The LTC1623 operates with an input voltage from 2.7V to 5.5V with a low standby current of 14 $\mu$ A (at 3.3V). In accordance with the SMBus specification, the LTC1623 maintains the 0.6V V<sub>IL</sub> and 1.4V V<sub>IH</sub> input thresholds throughout the supply voltage range.

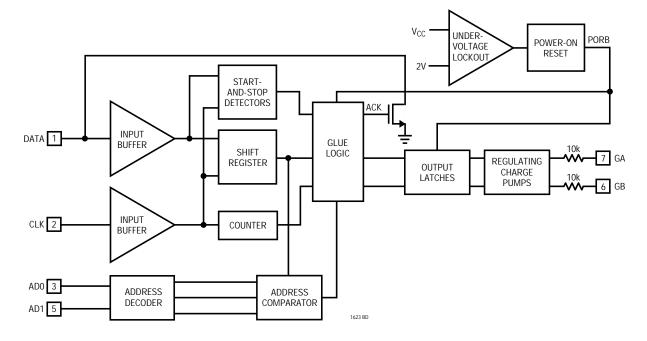

Using the 2-wire interface, CLK and DATA, the LTC1623 monitors the bus for a start condition (DATA going from high to low while CLK is high). Once detected, the LTC1623 compares its address with the first (address) byte sent over the bus from the master. If matched, the LTC1623 will execute the second (command) byte from the master and independently control the built-in charge pumps to drive two external switches.

The LTC1623 has two three-state programmable address pins, thus allowing eight different addresses and a total of sixteen available switches on the same bus.

17, LTC and LT are registered trademarks of Linear Technology Corporation.

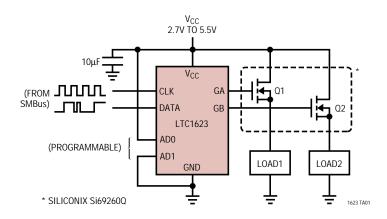

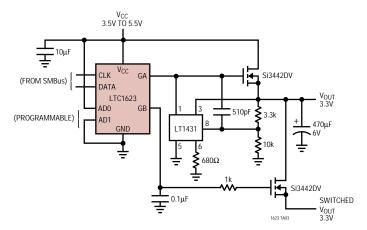

## TYPICAL APPLICATION

### ABSOLUTE MAXIMUM RATINGS

| 0° to 70°C    |

|---------------|

| 40°C to 85°C  |

| 65°C to 150°C |

| c)300°C       |

|               |

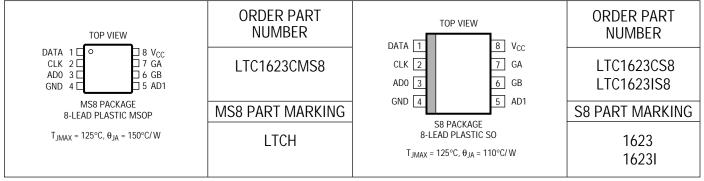

## PACKAGE/ORDER INFORMATION

Consult factory for Military grade parts.

## ELECTRICAL CHARACTERISTICS $T_A = 25^{\circ}C$ , $V_{CC} = 5V$ unless otherwise specified. $C_{GA} = 1000pF$ , $C_{GB} = 1000pF$

| SYMBOL              | PARAMETER                                 | CONDITIONS                                                                                                    |                                               |   | MIN               | TYP               | MAX            | UNITS          |

|---------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---|-------------------|-------------------|----------------|----------------|

| $V_{CC}$            | Operating Supply Voltage Range            |                                                                                                               |                                               |   | 2.7               |                   | 5.5            | V              |

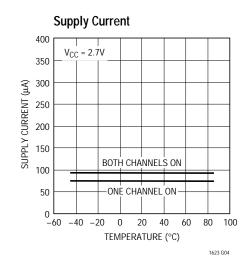

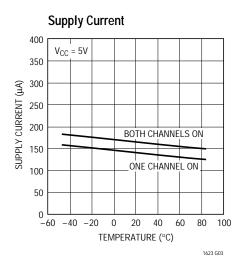

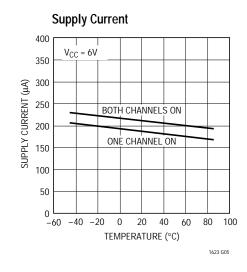

| I <sub>VCC</sub>    | Supply Current                            | Charge Pump Off, ADO and AD1High or Low, DATA and CLK High                                                    | $V_{CC} = 2.7V$ $V_{CC} = 3.3V$ $V_{CC} = 5V$ | • |                   | 12<br>14<br>17    | 30<br>30<br>30 | μΑ<br>μΑ<br>μΑ |

| I <sub>VCC</sub>    | Supply Current                            | GA or GB High (Command Byte 00000001 or 0<br>Both GA and GB High (Command Byte 000000                         |                                               | • |                   | 140<br>162        | 250<br>250     | μA<br>μA       |

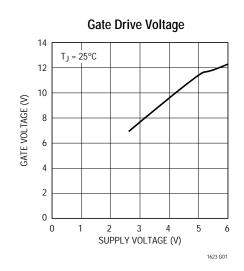

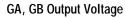

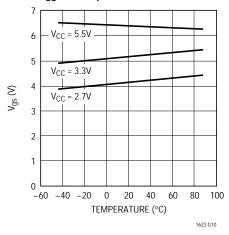

| $\overline{V_{GS}}$ | Gate Voltage Above Supply                 | $V_{CC} = 2.7V$ $V_{CC} = 3.3V$ $V_{CC} = 5.5V$                                                               |                                               | • | 2.7<br>4.5<br>4.5 | 4.2<br>5.4<br>6.4 | 7<br>7<br>7    | V<br>V<br>V    |

| V <sub>UVLO</sub>   | Undervoltage Lockout                      | Falling Edge (Note1)                                                                                          |                                               | • | 1.5               | 2.0               | 2.5            | V              |

| t <sub>POR</sub>    | Power-On Reset Delay Time                 | V <sub>CC</sub> = 2.7V (Note2)<br>V <sub>CC</sub> = 5.5V                                                      |                                               |   |                   | 300<br>300        | 1000<br>1000   | μs<br>μs       |

| f <sub>OSC</sub>    | Charge Pump Oscillator Frequency (Note 3) |                                                                                                               |                                               |   |                   | 300               |                | kHz            |

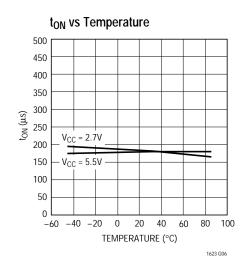

| t <sub>ON</sub>     | Turn-On Time into 1000pF                  | $V_{CC}$ = 2.7V (From ON to GA, GB = $V_{CC}$ + 1V) (I $V_{CC}$ = 5.5V (From ON to GA, GB = $V_{CC}$ + 2V) (I | •                                             |   |                   | 170<br>180        |                | μs<br>μs       |

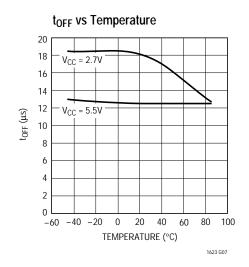

| t <sub>OFF</sub>    | Turn-Off Time into 1000pF                 | $V_{CC}$ = 2.7V (From OFF to GA, GB = 100mV) (N $V_{CC}$ = 5.5V (From OFF to GA, GB = 100mV) (N               |                                               |   |                   | 17<br>12          |                | μs<br>μs       |

| V <sub>IL</sub>     | DATA/CLK Input Low Voltage                | V <sub>CC</sub> = 2.7V to 5.5V                                                                                |                                               |   |                   |                   | 0.6            | V              |

| V <sub>IH</sub>     | DATA/CLK Input High Voltage               | V <sub>CC</sub> = 2.7V to 5.5V                                                                                |                                               |   | 1.4               |                   |                | V              |

# ELECTRICAL CHARACTERISTICS $T_A = 25^{\circ}C$ , $V_{CC} = 5V$ unless otherwise specified. $C_{GA} = 1000pF$ , $C_{GB} = 1000pF$

| SYMBOL              | PARAMETER                                                | CONDITIONS                                                          | MIN                   | TYP  | MAX  | UNITS |

|---------------------|----------------------------------------------------------|---------------------------------------------------------------------|-----------------------|------|------|-------|

| V <sub>IL</sub>     | AD0 and AD1 Input Low Voltage                            | V <sub>CC</sub> = 2.7V to 5.5V                                      |                       |      | 0.2  | V     |

| $V_{IH}$            | AD0 and AD1 Input High Voltage                           | V <sub>CC</sub> = 2.7V to 5.5V                                      | V <sub>CC</sub> - 0.2 |      |      | V     |

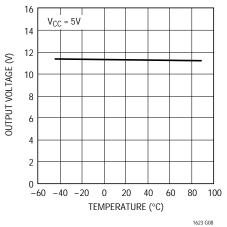

| V <sub>OL</sub>     | Data Output Low Voltage                                  | V <sub>CC</sub> = 2.7 to 5.5V, I <sub>PULLUP</sub> = 350μA          |                       | 0.22 | 0.4  | V     |

| C <sub>IN</sub>     | Input Capacitance<br>(DATA, CLK, ADO, AD1)               |                                                                     |                       | 5    |      | pF    |

| I <sub>IN</sub>     | Input Leakage Current (DATA, CLK)                        |                                                                     |                       |      | ±1   | μА    |

|                     | Input Leakage Current(AD0, AD1)                          |                                                                     |                       |      | ±250 | nA    |

| SMBus Re            | elated Specs (Note 6)                                    |                                                                     |                       |      |      |       |

| f <sub>SMB</sub>    | SMBus Operating Frequency                                |                                                                     | 10                    |      | 100  | kHz   |

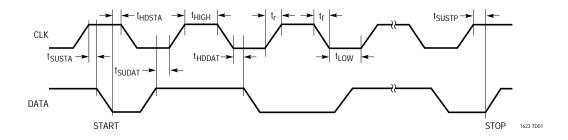

| t <sub>SUSTA</sub>  | Start Condition Setup Time                               |                                                                     | 4.7                   |      |      | μs    |

| t <sub>BUF</sub>    | Bus Free Time Between Stop and Start                     |                                                                     | 4.7                   |      |      | μs    |

| t <sub>HDSTA</sub>  | Start Condition Hold Time                                |                                                                     | 4.0                   |      |      | μs    |

| t <sub>SUSTP</sub>  | Stop Condition Setup Time                                |                                                                     | 4.0                   |      |      | μs    |

| t <sub>HDDAT</sub>  | Data Hold Time                                           |                                                                     | 300                   |      |      | ns    |

| t <sub>SUDAT</sub>  | Data Setup Time                                          |                                                                     | 250                   |      |      | ns    |

| $t_{LOW}$           | Clock Low Period                                         |                                                                     | 4.7                   |      |      | μs    |

| t <sub>HIGH</sub>   | Clock High Period                                        |                                                                     | 4.0                   |      | 50   | μs    |

| t <sub>f</sub>      | Clock /Data Fall Time                                    |                                                                     |                       |      | 300  | ns    |

| t <sub>r</sub>      | Clock/Data Rise Time                                     |                                                                     |                       |      | 1000 | ns    |

| I <sub>PULLUP</sub> | Current Through External Pull-Up<br>Resistor on DATA Pin | (Data Pull-Down Current Capacity)<br>V <sub>CC</sub> = 2.7V to 5.5V | 100                   |      | 350  | μА    |

The ● denotes the specifications which apply over the full operating temperature range.

**Note 1:** Approximately 3% hysteresis is provided to ensure stable operation and eliminate false triggering by minor  $V_{CC}$  glitches.

**Note 2:** Measured from  $V_{CC} > V_{IJVI,O}$  to SMBus ready for data input.

**Note 3:** The oscillator frequency is not tested directly but is inferred from turn-on time.

**Note 4:** ON is enabled upon receiving the Stop condition from the SMBus master.

**Note 5:** OFF is enabled upon receiving the Stop condition from the SMBus master.

Note 6: SMBus timing specs are guaranteed but not tested.

## PIN FUNCTIONS

**DATA:** (Pin 1) Open-Drain Connected Serial Data Interface. Must be pulled high to  $V_{CC}$  with external resistor. The pull-up current must be limited to  $350\mu A$ .

**CLK:** (Pin 2) Serial Clock Interface. Must be pulled high to  $V_{CC}$  with external resistor. The pull-up current must be limited to 350 $\mu$ A.

**ADO:** (Pin 3) Lower Three-State Programmable Address Pin. Must be connected directly to  $V_{CC}$ , GND, or  $V_{CC}/2$  (using two resistors  $\leq$  1M). Do not float this pin.

**GND: (Pin 4)** Ground.

**AD1:** (Pin 5) Higher Three-State Programmable Address Pin. Must be connected directly to  $V_{CC}$ , GND, or  $V_{CC}/2$  (using two resistors  $\leq$  1M). Do not float this pin.

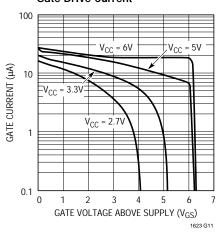

**GB:** (Pin 6) Gate Drive to External High-Side Switch. Fully enhanced by internal charge pump. Controlled by 2nd LSB of command byte.

**GA:** (Pin 7) Gate Drive to External High-Side Switch. Fully enhanced by internal charge pump. Controlled by LSB of command byte.

$V_{CC}$ : (Pin 8) Input Supply Voltage. Range from 2.7V to 5.5V.

## TYPICAL PERFORMANCE CHARACTERISTICS

## TYPICAL PERFORMANCE CHARACTERISTICS

#### DATA V<sub>OL</sub> vs Temperature

### V<sub>GS</sub> vs Temperature

#### **Gate Drive Current**

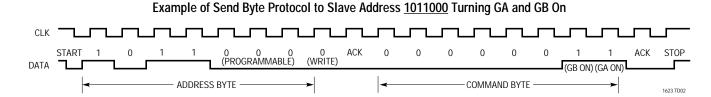

## TIMING DIAGRAM

## FUNCTIONAL BLOCK DIAGRAM

### **OPERATION**

#### **SMBus Operation**

SMBus is a serial bus interface that uses only two bus lines, DATA and CLK, to control low power peripheral devices in portable equipment. It consists of masters, also known as hosts, and slave devices. The master of the SMBus is always the one to initiate communications to its slave devices by varying the status of the DATA and CLK lines. The SMBus specification establishes a set of protocols that devices on the bus must follow during communications.

The protocol that the LTC1623 uses is the Send Byte Protocol. In this protocol, the master first sends out a Start signal by switching the DATA line from high to low while CLK is high. (Because there may be more than one master on the same bus, an arbitration process takes place if two masters attempt to take control of the DATA line simultaneously; the first master that outputs a one while the other master is zero loses the arbitration and becomes a slave itself.) Upon detecting this Start signal, all slave devices on the bus wake up and get ready to shift in the next byte of data.

The master then sends out the first byte. The first seven bits of this byte consist of the address of the device that the master wishes to communicate with. The last bit indicates whether the command will be a read (logic one) or write (logic zero). Because the LTC1623 is a slave device that can only be written to by a master, it will ignore the ensuing commands of the master if it wants to read from the LTC1623, even if the address sent by the master matches that of the LTC1623. After reception of the first byte, the slave device (LTC1623) with the matching address then

acknowledges the master by pulling the data line low before the rising edge of the ninth clock cycle.

By now, all other nonmatching slave devices will have gone back to their original standby states to wait for the next start signal. Meanwhile, upon receiving the acknowledge from the matching slave, the master then sends out the command byte. In the case of the LTC1623, the two LSBs of this second byte from the master are the signals controlling the status of the external switches; a digital "one" turns on the charge pump to drive up the output gate voltage while a digital "zero" shuts down the charge pump and discharges the output gate voltage to zero.

After receiving the command byte, the slave device (LTC1623) needs to again acknowledge the master by pulling the DATA line low on the following clock cycle. The master then ends this Send Byte Protocol by sending the Stop signal, which is a transition from low to high on the DATA line while the CLK line is high. Valid data is shifted into the output latch on the last acknowledge signal; the external switch will not be enabled, however, until the Stop signal is detected. This double-buffering feature allows the user to daisy-chain several differently addressed SMBus devices such that their output executions are synchronous to the Stop signal even though valid data were loaded into their output latches at different times. Figure 1 shows an example of this special protocol. If somehow either the Start or the Stop signal is detected in the middle of a byte, the slave device (LTC1623) will regard this as an error and reject all previous data. Other than the Stop and Start conditions, DATA must be stable during CLK high; DATA can change state only during CLK low.

Figure 1. Daisy-Chaining Multiple SMBus Devices

### **OPERATION**

#### Address

The LTC1623 has an address of 1011XXX; the four MSBs are hard-wired, but the 3 LSBs are programmed by the user with the help of two three-state address pins. Refer to Table 1 for the pin configurations and their corresponding addresses.

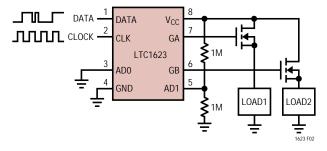

To conserve standby current, it is preferable to tie the address pins to either  $V_{CC}$  or GND. If more than four addresses are needed, then either one of the address pins can be tied to the third state of  $V_{CC}/2$  by using two equal value resistors ( $\leq 1M$ ) shown in Figure 2. Do not connect both address pins to the  $V_{CC}/2$  state simultaneously because this is not a valid address.

Table 1. Address Pin Truth Table

| AD0                | AD1                | ADDRESS |  |  |

|--------------------|--------------------|---------|--|--|

| GND                | GND                | 1011000 |  |  |

| GND                | V <sub>CC</sub> /2 | 1011001 |  |  |

| GND                | V <sub>CC</sub>    | 1011010 |  |  |

| V <sub>CC</sub> /2 | GND                | 1011011 |  |  |

| V <sub>CC</sub> /2 | V <sub>CC</sub> /2 | UNUSED  |  |  |

| V <sub>CC</sub> /2 | V <sub>CC</sub>    | 1011100 |  |  |

| V <sub>CC</sub>    | GND                | 1011101 |  |  |

| V <sub>CC</sub>    | V <sub>CC</sub> /2 | 1011110 |  |  |

| V <sub>CC</sub>    | V <sub>CC</sub>    | 1011111 |  |  |

Figure 2. LTC1623 Programmed with Address 1011001

#### **Charge Pump**

To fully enhance the external N-channel switches, an internal charge pump is used to boost the output gate drive to a minimum of 2.7V and a maximum of 6V above  $V_{CC}$ , depending on  $V_{CC}$  itself. The reason for the maximum output voltage limit is to avoid switch gate source breakdown due to excessive gate overdrive. A feedback network is used to limit the charge pump output to 6V above  $V_{CC}$ . Because the output will only need to drive the gate of the external switch by charging and discharging the parasitic gate capacitances, the internal charge pump, clocked by an approximately 300KHz oscillator, is appropriately sized to source less than 100 $\mu$ A.

### Power-On Reset and Undervoltage Lockout

The LTC1623 starts up with both gate drives low. An internal power-on reset (POR) signal inhibits operation until about 300 $\mu$ s after V<sub>CC</sub> crosses the undervoltage lockout threshold (typically 2V). The circuit includes some hysteresis and delay to avoid nuisance resets. Once operation begins, V<sub>CC</sub> must drop below the threshold for at least 100 $\mu$ s to trigger another POR sequence.

During standby, when both gate drive outputs are disabled, quiescent current is kept to a minimum (13µA typical) because only the UVLO block is active.

#### Input Threshold

Anticipating the trend toward lower supply voltages, the SMBus is specified with a  $V_{IH}$  of 1.4V and a  $V_{IL}$  of 0.6V. While some SMBus parts may violate this stringent SMBus specification by allowing a higher  $V_{IH}$  value for a correspondingly higher input supply voltage, the LTC1623 meets and maintains the constant SMBus input threshold specification across the entire supply voltage range of 2.7V to 5.5V.

### APPLICATIONS INFORMATION

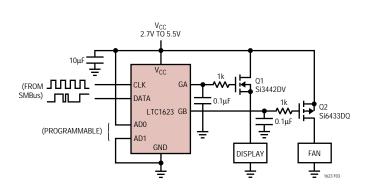

To avoid turning on the external power MOSFETs too quickly, an internal 10k resistor has been placed in series with each of the output gate drive pins (see Functional Block Diagram). Therefore, it only needs an external  $0.1\mu F$  capacitor to create enough RC delay  $(10k \cdot 0.1\mu F = 1ms)$  to slow down the ramp rate of the output gate drive. In other words, it will take a minimum of 1ms to charge up the external MOSFET. An additional external 1k resistor between the  $0.1\mu F$  capacitor and the gate of the MOSFET (Figure 3) is required to eliminate possible MOSFET self oscillations.

For active-low applications in which the load needs to be on upon power-up, an external P-channel switch can be used (Figure 3). This load can be switched off later after the proper protocol has been sent.

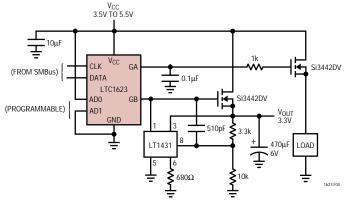

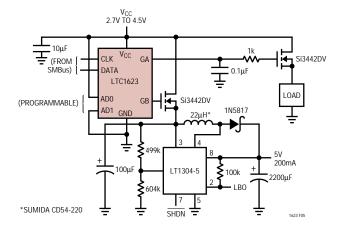

Used with the LT®1431, the LTC1623 makes a 3.3V/3A extremely low voltage drop regulator (Figures 4 and 5). In this application, the other output channel can be used to drive a separate load, or it can also be used to control the output of the LDO so that the user has total control over the switching in and switching out of the LDO (Figure 5). Also, with the help of the LT1304-5, the LTC1623 can be used to make a boost switching regulator with a low standby current of 22µA (Figure 6).

Figure 3. Dual Load Switch with Q2 On upon Power-Up

Figure 4. 3.3V/3A Extremely Low Voltage Drop Regulator and Load Switch

Figure 5. SMBus Controlled Low Dropout Regulator

Figure 6. Switching Regulator with Low-Battery Detect Using 22µA Standby Current

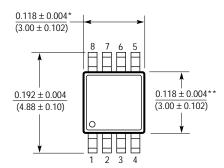

# $PACKAGE\ DESCRIPTIOn\quad \text{Dimensions in inches (millimeters) unless otherwise noted}.$

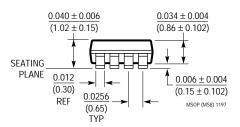

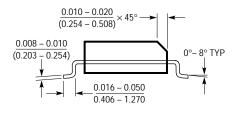

#### MS8 Package 8-Lead Plastic MSOP

(LTC DWG # 05-08-1660)

- \* DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

- \*\* DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

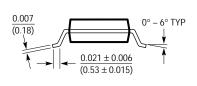

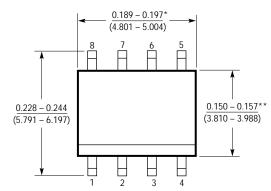

# $PACKAGE\ DESCRIPTIOn\quad \text{Dimensions in inches (millimeters) unless otherwise noted}.$

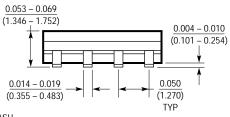

#### S8 Package 8-Lead Plastic Small Outline (Narrow 0.150)

(LTC DWG # 05-08-1610)

<sup>\*</sup>DIMENSION DOES NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

SO8 0996

<sup>\*\*</sup>DIMENSION DOES NOT INCLUDE INTERLEAD FLASH. INTERLEAD FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE