# 5A Ideal Diode

#### **FEATURES**

- Replaces a Power Schottky Diode

- Internal 20mΩ N-Channel MOSFET

- 0.5µs Turn-Off Time Limits Peak Fault Current

- Operating Voltage Range: 9V to 26.5V

- Smooth Switchover without Oscillation

- No Reverse DC Current

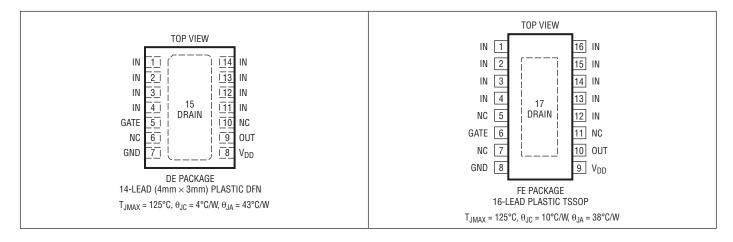

- Available in 14-Pin (4mm × 3mm) DFN and 16-Lead TSSOP Packages

#### **APPLICATIONS**

- N+1 Redundant Power Supplies

- High Availability Systems

- Telecom Infrastructure

- Automotive Systems

### DESCRIPTION

The LTC®4358 is a 5A ideal diode that uses an internal  $20m\Omega$  N-channel MOSFET to replace a Schottky diode when used in diode-OR and high current diode applications. The LTC4358 reduces power consumption, heat dissipation, and PC board area.

The LTC4358 easily ORs power supplies together to increase total system reliability. In diode-OR applications, the LTC4358 regulates the forward voltage drop across the internal MOSFET to ensure smooth current transfer from one path to the other without oscillation. If the power source fails or is shorted, a fast turnoff minimizes reverse current transients.

AT, LT, LTC and LTM are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

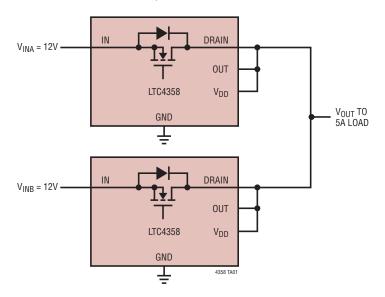

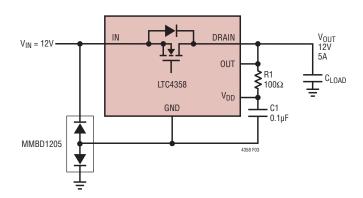

## TYPICAL APPLICATION

#### 12V, 5A Diode-OR

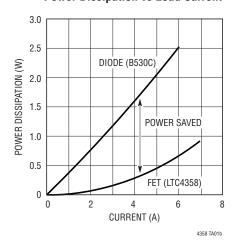

#### **Power Dissipation vs Load Current**

#### **ABSOLUTE MAXIMUM RATINGS** (Notes 1, 2)

| Supply Voltages                                     |

|-----------------------------------------------------|

| IN, OUT, V <sub>DD</sub> , DRAIN Voltage0.3V to 28V |

| Output Voltage                                      |

| GATE (Note 3) $V_{IN} - 0.2V$ to $V_{IN} + 6V$      |

| Operating Ambient Temperature Range                 |

| LTC4358C0°C to 70°C                                 |

| LTC4358I40°C to 85°C                                |

|                                                     |

Storage Temperature Range.....-65°C to 150°C Lead Temperature (Soldering, 10 sec) FE Package ......300°C

## PIN CONFIGURATION

## ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL    | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|------------------|------------------|---------------|---------------------------------|-------------------|

| LTC4358CDE#PBF   | LTC4358CDE#TRPBF | 4358          | 14-Lead (4mm × 3mm) Plastic DFN | 0°C to 70°C       |

| LTC4358IDE#PBF   | LTC4358IDE#TRPBF | 4358          | 14-Lead (4mm × 3mm) Plastic DFN | -40°C to 85°C     |

| LTC4358CFE#PBF   | LTC4358CFE#TRPBF | 4358FE        | 16-Lead Plastic TSSOP           | 0°C to 70°C       |

| LTC4358IFE#PBF   | LTC4358IFE#TRPBF | 4358FE        | 16-Lead Plastic TSSOP           | -40°C to 85°C     |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*Temperature grades are identified by a label on the shipping container. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** The ullet denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_{OUT} = V_{DD}$ , $V_{DD} = 9V$ to 26.5V, unless otherwise noted.

| SYMBOL                  | PARAMETER                                                             | CONDITIONS                                                                                                  |   | MIN | TYP | MAX      | UNITS    |

|-------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---|-----|-----|----------|----------|

| $\overline{V_{DD}}$     | Operating Supply Range                                                |                                                                                                             | • | 9   |     | 26.5     | V        |

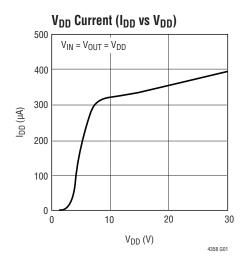

| $I_{DD}$                | Operating Supply Current                                              |                                                                                                             | • |     |     | 0.6      | mA       |

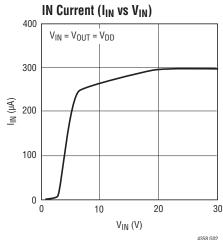

| I <sub>IN</sub>         | IN Pin Current                                                        | V <sub>IN</sub> = V <sub>OUT</sub> ± 1V, No Load                                                            | • | 150 | 350 | 450      | μА       |

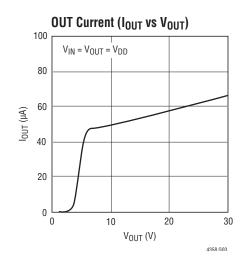

| l <sub>out</sub>        | OUT Pin Current                                                       | V <sub>IN</sub> = V <sub>OUT</sub> ± 1V, No Load                                                            | • |     | 80  | 160      | μА       |

| I <sub>DRAIN</sub>      | DRAIN Pin Current                                                     | $V_{IN} = 0V, V_{OUT} = V_{DD} = V_{DRAIN} = 26.5V$                                                         | • |     |     | 5<br>150 | μA<br>μA |

| $\Delta V_{GATE}$       | N-Channel Gate Drive (V <sub>GATE</sub> – V <sub>IN</sub> )           | V <sub>DD</sub> , V <sub>OUT</sub> = 9V to 26.5V                                                            | • | 4.5 |     | 15       | V        |

| I <sub>GATE(UP)</sub>   | N-Channel Gate Pull Up Current                                        | $V_{GATE} = V_{IN}, V_{IN} - V_{OUT} = 0.1V$                                                                | • | -14 | -20 | -26      | μА       |

| I <sub>GATE(DOWN)</sub> | N-Channel Gate Pull Down<br>Current in Fault Condition                | $V_{GATE} = V_{IN} + 5V$                                                                                    | • | 1   | 2   |          | А        |

| t <sub>ON</sub>         | Turn-On Time                                                          | $V_{IN} - V_{OUT} = -1V \int 0.1V$ , $V_{DRAIN} = V_{IN}$ , $V_{OUT} = V_{DD}$ , $V_{GATE} - V_{IN} > 4.5V$ | • |     | 200 | 500      | μѕ       |

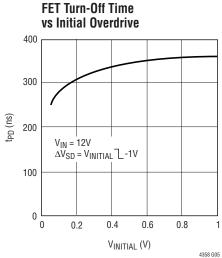

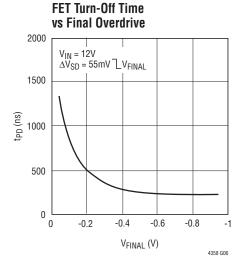

| t <sub>OFF</sub>        | Turn-Off Time                                                         | $V_{IN} - V_{OUT} = 55mV \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \$                                             | • |     | 300 | 500      | ns       |

| $\Delta V_{SD}$         | Source-Drain Regulation Voltage (V <sub>IN</sub> – V <sub>OUT</sub> ) | 1mA < I <sub>IN</sub> < 100mA                                                                               | • | 10  | 25  | 55       | mV       |

| $\Delta V_{SD}$         | Body Diode Forward Voltage Drop                                       | I <sub>IN</sub> = 5A, MOSFET Off                                                                            | • | 0.6 | 0.8 | 1        | V        |

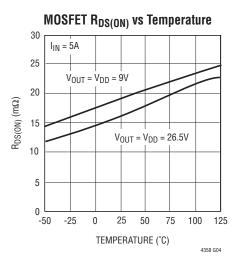

| R <sub>DS(ON)</sub>     | Internal N-Channel MOSFET On<br>Resistance                            | I <sub>IN</sub> = 5A                                                                                        | • |     | 20  | 40       | mΩ       |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** All currents into pins are positive, all voltages are referenced to GND unless otherwise specified.

**Note 3:** An internal clamp limits the GATE pin to a minimum of 6V above IN. Driving this pin to voltages beyond this clamp may damage the device.

# TYPICAL PERFORMANCE CHARACTERISTICS

# PIN FUNCTIONS (DE/FE PACKAGES)

**DRAIN:** The exposed pad is the drain of the internal N-channel MOSFET. This pin must be connected to OUT (Pin 9/Pin 10).

**GATE:** Gate Drive Output. If reverse current flows, a fast pulldown circuit quickly connects the GATE pin to the IN pin, turning off the MOSFET. Leave open if unused.

**GND:** Device Ground.

**IN:** Input Voltage and Fast Pulldown Return. IN is the anode of the ideal diode. The voltage sensed at this pin is used to control the source-drain voltage drop across the internal MOSFET. If reverse current starts to flow, a fast pulldown circuit quickly turns off the internal MOSFET. The fast pulldown current is returned through this pin.

NC: No Connection. Not internally connected.

**OUT:** Output Voltage. The OUT pin is the cathode of the ideal diode and the common output when multiple LTC4358s are configured as an ideal diode-OR. The voltage sensed at this pin is used to control the source-drain voltage drop across the MOSFET. Connect this pin to the drain of the internal N-channel MOSFET (Pin 15/Pin 17).

$V_{DD}$ : Positive Supply Input. The LTC4358 is powered from the  $V_{DD}$  pin. Connect this pin to OUT either directly or through an RC hold-up circuit.

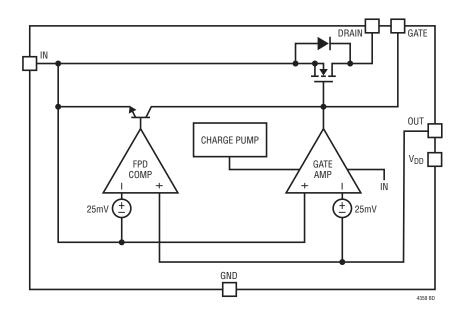

## **BLOCK DIAGRAM**

#### **OPERATION**

High availability systems often employ parallel-connected power supplies or battery feeds to achieve redundancy and enhance system reliability. ORing diodes have been a popular means of connecting these supplies at the point of load. The disadvantage of this approach is the forward voltage drop and resulting efficiency loss. This drop reduces the available supply voltage and dissipates significant power. Using an N-channel MOSFET to replace a Schottky diode reduces the power dissipation and eliminates the need for costly heat sinks or large thermal layouts in high power applications.

The LTC4358 is a single positive voltage ideal diode controller that drives an internal N-channel MOSFET as a pass transistor to replace a Schottky diode. The IN and DRAIN pins form the anode and cathode of the ideal diode. The input supply is connected to the IN pins, while the DRAIN pin serves as the output. The OUT pin is connected directly to DRAIN and  $V_{DD}.\ V_{DD}$  is the supply for the LTC4358 and is derived from the output either directly or through an RC hold-up circuit.

At power-up, the load current initially flows through the body diode of the internal MOSFET. The internal MOSFET turns on and the amplifier tries to regulate the voltage drop across the IN and OUT connections to 25mV. If the load current causes more than 25mV of drop, the MOSFET is driven fully on and the voltage drop is equal to  $R_{DS(ON)} \bullet I_{LOAD}$ .

If the load current is reduced causing the forward drop to fall below 25mV, the internal MOSFET is driven lower by a weak pull-down in an attempt to maintain the drop at 25mV. If the load current reverses the MOSFET is turned off with a strong pull-down.

In the event of a power supply failure, such as if the supply that is conducting most or all of the current is shorted to ground, reverse current temporarily flows through the LTC4358 ideal diode that is on. This current is sourced from any load capacitance and from the other supplies. The ideal diode is turned off within 500ns, preventing reverse current from slewing up to a damaging level and minimizing any disturbance on the output.

#### APPLICATIONS INFORMATION

#### **ORing Two Supply Outputs**

Where LTC4358s are used to combine the outputs of two supplies, the power supply with the highest output voltage sources most or all of the current. If this supply's output is quickly shorted to ground while delivering load current, the current temporarily reverses and flows backwards through the LTC4358. When reverse current flows the LTC4358 ideal diode is quickly turned off.

If the other initially lower supply was not delivering load current at the time of the fault, the output falls until the LTC4358 body diode conducts. Meanwhile, the internal amplifier turns on the MOSFET until the forward drop is reduced to 25mV. If instead this supply was delivering load current at the time of the fault, its ORing MOSFET was already driven at least partially on, and will be driven harder in an effort to maintain a drop of 25mV.

#### **Load Sharing**

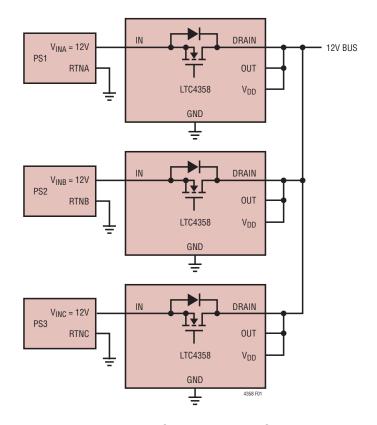

Figure 1 combines the outputs of multiple, redundant supplies using a simple technique known as droop sharing. Load current is first taken from the highest output, with the low outputs contributing as the output voltage falls under increased loading. The 25mV regulation technique ensures smooth load sharing between outputs without oscillation. The degree of sharing depends on the  $20m\Omega$  resistance of the LTC4358 internal MOSFET, the output impedance of the supplies and their initial output voltages.

Figure 1. Droop Sharing Redundant Supplies

## APPLICATIONS INFORMATION

#### **VDD** Hold-Up Circuit

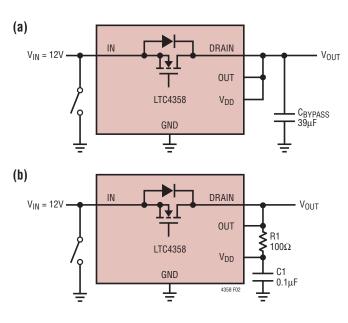

In the event of an input short, parasitic inductance between the input supply of the LTC4358 and the load bypass capacitor may cause  $V_{DD}$  to glitch below its minimum operating voltage. This causes the turn-off time  $(t_{OFF})$  to increase. To preserve the fast turn-off time, local output bypassing of  $39\mu F$  or more is sufficient or a  $100\Omega,\,0.1\mu F$  RC hold-up circuit on the  $V_{DD}$  pin can be used as shown in Figure 2a and Figure 2b.

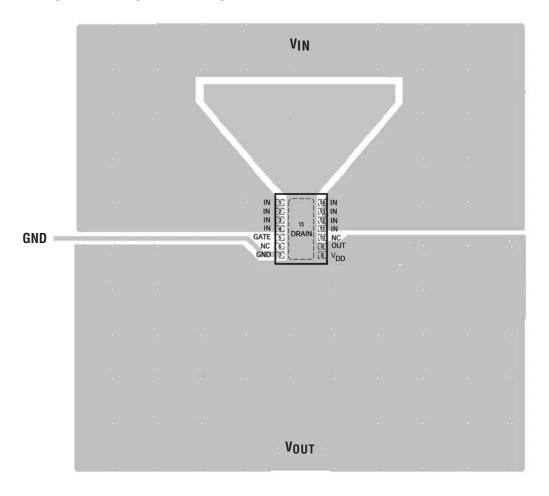

#### **Layout Considerations**

The following advice should be considered when laying out a printed circuit board for the LTC4358: The OUT pin should

be connected as closely as possible to the EXPOSED PAD (drain of the MOSFET) for good accuracy. Keep the traces to the IN and DRAIN wide and short. The PCB traces associated with the power path through the MOSFET should have low resistance. See Figure 4.

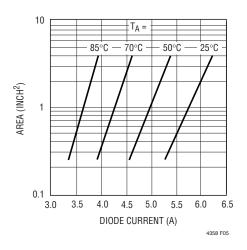

The DRAIN acts as a heatsink to remove the heat from the device. For a single layer PCB with the DFN package, use Figure 5 to determine the PCB area needed for a specified maximum current and ambient temperature. If using a two sided PCB, the maximum current is increased by 10%. If the FE package is used, the maximum current is increased by 4%.

Figure 2. Two Methods of Protecting Against Collapse of  $V_{DD}$  From Input Short and Stray Inductance

Figure 3. -12V Reverse Input Protection

# **APPLICATIONS INFORMATION**

Figure 4. DFN Layout Considerations for 1"  $\times$  1" Single Sided PCB

Figure 5. Maximum Diode Current vs PCB Area

## PACKAGE DESCRIPTION

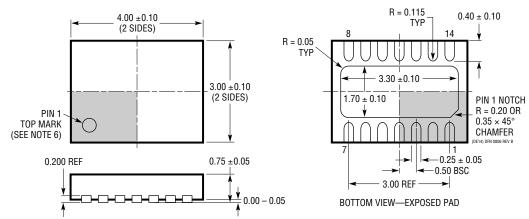

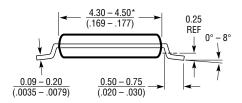

#### **DE Package** 14-Lead Plastic DFN (4mm × 3mm)

(Reference LTC DWG # 05-08-1708)

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS APPLY SOLDER MASK TO AREAS THAT ARE NOT SOLDERED

#### NOTE:

- 1. DRAWING PROPOSED TO BE MADE VARIATION OF VERSION (WGED-3) IN JEDEC PACKAGE OUTLINE MO-229

2. DRAWING NOT TO SCALE

- DRAWING NOT TO SCALE

ALL DIMENSIONS ARE IN MILLIMETERS

DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

EXPOSED PAD SHALL BE SOLDER PLATED

SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

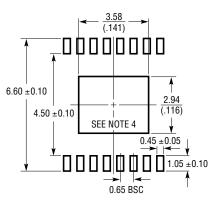

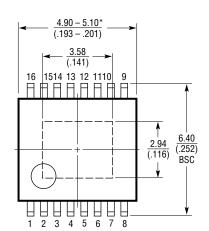

## PACKAGE DESCRIPTION

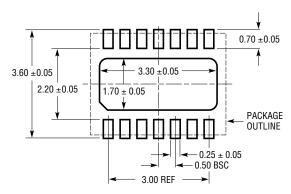

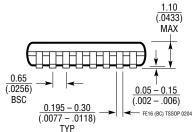

#### FE Package 16-Lead Plastic TSSOP (4.4mm)

(Reference LTC DWG # 05-08-1663)

#### **Exposed Pad Variation BC**

RECOMMENDED SOLDER PAD LAYOUT

#### NOTE

- 1. CONTROLLING DIMENSION: MILLIMETERS

- 2. DIMENSIONS ARE IN MILLIMETERS (INCHES)

- 3. DRAWING NOT TO SCALE

- 4. RECOMMENDED MINIMUM PCB METAL SIZE FOR EXPOSED PAD ATTACHMENT

- \*DIMENSIONS DO NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED 0.150mm (.006") PER SIDE