## 100MHz Isolated ADC Serial Interface

## **FEATURES**

- Isolated Interface: 6000V<sub>RMS</sub> for 1 Minute

- CSA (IEC/UL) Approved, File #255632

- 100MHz SPI-Compatible I/O

- Configurable SPI Word Length 8 to 32 Bits

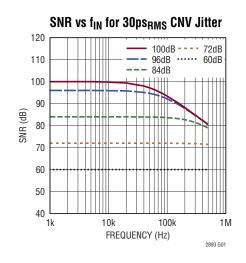

- Low Jitter Conversion Start (30ps<sub>RMS</sub>)

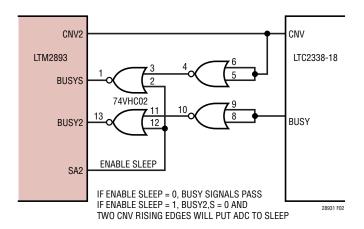

- Supports Simultaneously Sampled ADCs

- Read Only (LTM2893), Read/Write (LTM2893-1)

- Three Isolated Multiplexer Select Signals

- 1.71V to 5.5V I/O Voltages

- 3V to 5.5V Supply Voltages

- High Common Mode Transient Immunity

- 15mm × 6.25mm BGA Package

## **APPLICATIONS**

- Remote Sensing

- High Speed Data Acquisition

- Industrial Process Control

- Test and Measurement Equipment

All registered trademarks and trademarks are the property of their respective owners.

#### DESCRIPTION

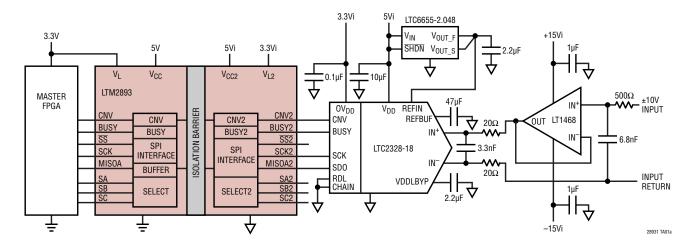

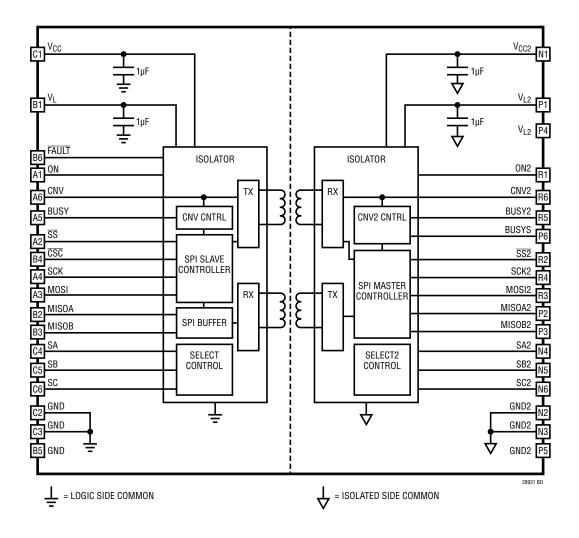

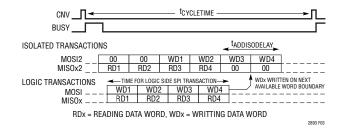

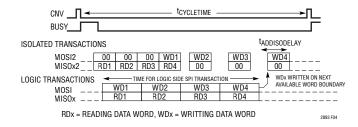

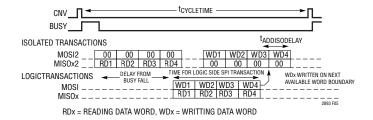

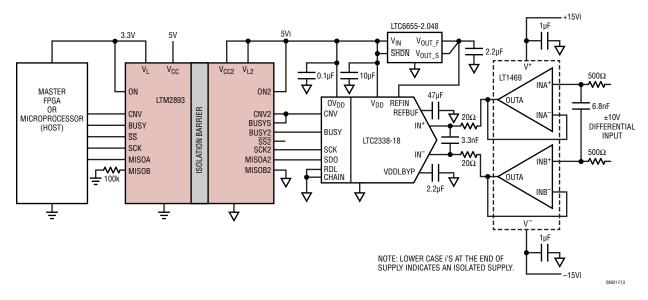

The LTM®2893 is a high speed isolated  $\mu$ Module (micromodule) SPI interface with ADC control signals. The LTM2893 is optimized for isolating 1Msps high resolution 18-bit SAR ADCs, such as the LTC2338 and similar families, and can interface with most general purpose ADCs. The LTM2893-1 is optimized for isolating the LTC2348 and similar families of simultaneous sampling ADCs that require writing configuration settings into the ADC. LTM2893 isolates the conversion start, sampling signal, with very low aperture jitter (30ps) and low latency (20ns).

The interface enables fast throughput with no cycle latency, which makes the LTM2893 ideally suited for a wide variety of applications. The LTM2893 has a high speed SPI-compatible serial port that supports 1.71V to 5.5V logic and is configurable for ADCs with 8 to 32 bit SPI word lengths. It also isolates three select signals (SA, SB, SC) for controlling analog multiplexers or gain settings.

The isolation barrier tolerates large voltage ground variations between the logic interface and the isolated side of the LTM2893. Uninterrupted communication is maintained during voltage transients greater than 50kV/µs.

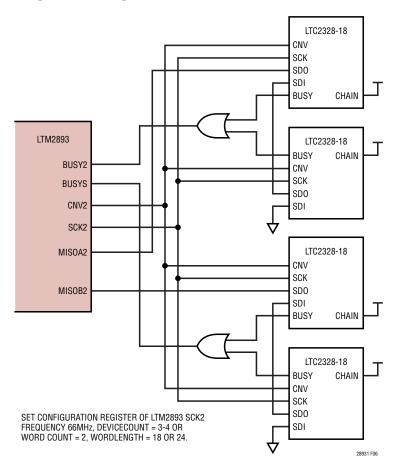

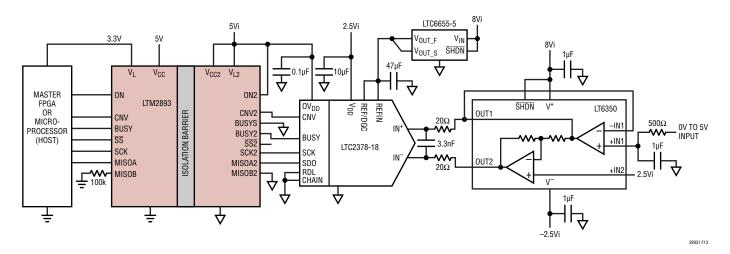

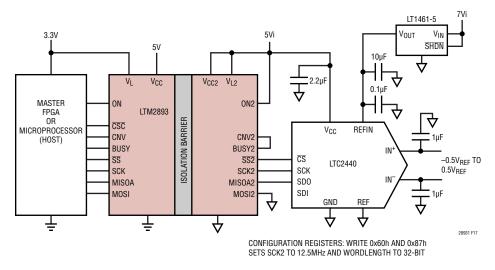

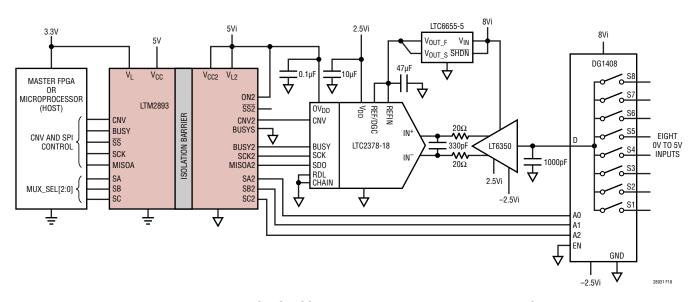

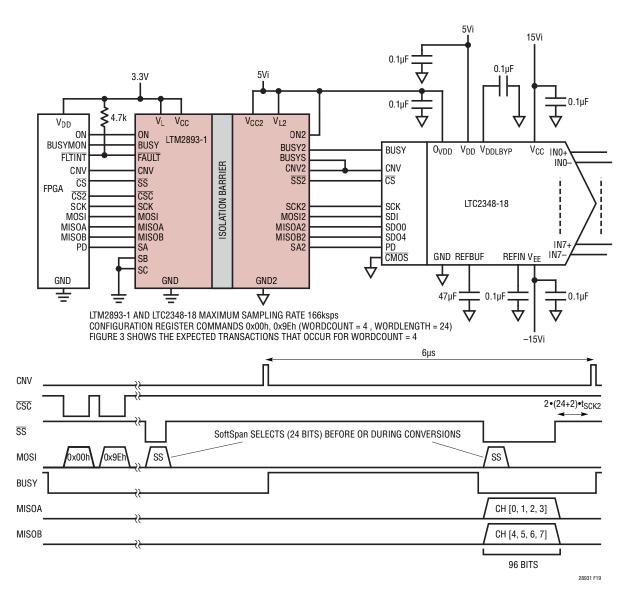

## TYPICAL APPLICATION

#### LTC2328-18 ADC Isolation $A_{IN} = \pm 10.24V$ , SNR = 95dB

Rev C

## **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

#### **Supply Voltages**

| V <sub>L</sub> to GND  | -0.3V | to | 6V |

|------------------------|-------|----|----|

| V <sub>CC</sub> to GND | -0.3V | to | 6V |

#### **Isolated Supply Voltages**

| V <sub>L2</sub> to GND2  | -0.3V to 6V |

|--------------------------|-------------|

| V <sub>CC2</sub> to GND2 | -0.3V to 6V |

### **Logic Signals**

ON, CNV, BUSY, SA, SB, SC, SS, CSC, MISOA, MISOB,

SCK, MOSI...... GND - 0.3V to  $V_L + 0.3V$  FAULT...... GND - 0.3V to 6.3V

#### **Isolated Signals**

MISOA2, MISOB2, ON2, BUSY2, BUSYS, MOSI2, CNV2, SCK2, SS2, SA2, SB2, SC2.....GND2 - 0.3V to  $V_{L2} + 0.3V$

#### **Operating Temperature Range (Note 11)**

| LTM2893C                           | 0°C to 70°C    |

|------------------------------------|----------------|

| LTM2893I                           | 40°C to 85°C   |

| LTM2893H                           | -40°C to 125°C |

| Storage Temperature Range          | -55°C to 125°C |

| Maximum Internal Operating Tempera |                |

| Peak Solder Reflow Temperature     |                |

|                                    |                |

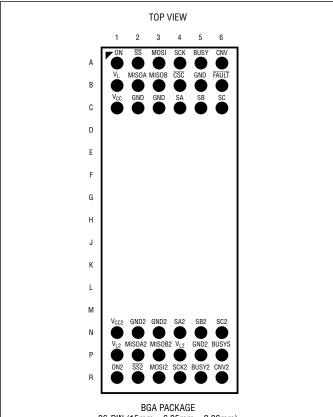

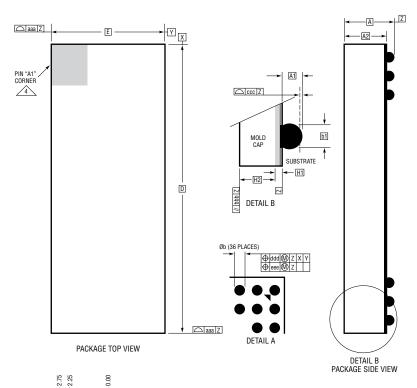

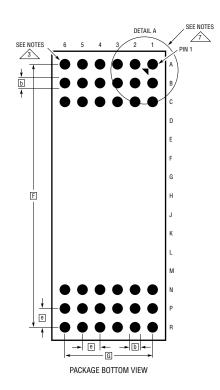

## PIN CONFIGURATION

36-PIN (15mm × 6.25mm × 2.06mm)

$T_{JMAX}=125^{\circ}C,~\theta_{JA}=36^{\circ}C/W,~\theta_{JCTOP}=27.5^{\circ}C/W,~\theta_{JCBOTTOM}=17.5^{\circ}C/W,~\theta_{JCBOTTOM}=17.5^{\circ}C/W,~WEIGHT=0.36g$

## ORDER INFORMATION

|                 | PACKAGE |               | PART       | PART MARKING |               |                   |

|-----------------|---------|---------------|------------|--------------|---------------|-------------------|

| PART NUMBER     | TYPE    | BALL FINISH   | DEVICE     | FINISH CODE  | MSL<br>Rating | TEMPERATURE RANGE |

| LTM2893CY#PBF   | BGA     | SAC305 (RoHS) | LTM2893Y   |              |               | 0°C to 70°C       |

| LTM2893IY#PBF   |         |               |            | e1           | 3             | -40°C to 85°C     |

| LTM2893HY#PBF   |         |               |            |              |               | -40°C to 125°C    |

| LTM2893CY-1#PBF |         |               |            |              |               | 0°C to 70°C       |

| LTM2893IY-1#PBF | BGA     | SAC305 (RoHS) | LTM2893Y-1 | e1           | 3             | -40°C to 85°C     |

| LTM2893HY-1#PBF |         |               |            |              |               | -40°C to 125°C    |

- Device temperature grade is indicated by a label on the shipping container.

- Pad or ball finish code is per IPC/JEDEC J-STD-609.

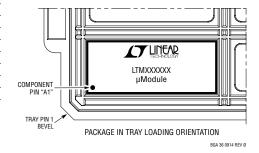

- · BGA Package and Tray Drawings

This product is not recommended for second side reflow. This product is moisture sensitive. For more information, go to Recommended BGA PCB Assembly and Manufacturing Procedures. **ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full specified operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{CC} = 5V$ ,  $V_L = 3.3V$ , GND = 0V,  $V_{CC2} = 5V$ ,  $V_{L2} = 3.3V$ , GND = 0V,  $V_{CC2} = 5V$ ,  $V_{L2} = 3.3V$ , GND = 0V,  $V_{CC2} = 5V$ ,  $V_{L3} = 3.3V$ ,  $V_{CC3} = 5V$ ,  $V_{CC3$

| SYMBOL           | PARAMETER                                                    | CONDITIONS                                                                                                             |   | MIN                   | TYP      | MAX                   | UNITS    |

|------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---|-----------------------|----------|-----------------------|----------|

| Power Su         | pplies                                                       |                                                                                                                        |   |                       |          | <u>'</u>              |          |

| V <sub>CC</sub>  | Operating Supply Range                                       |                                                                                                                        | • | 3.0                   |          | 5.5                   | V        |

| I <sub>CC</sub>  | Operating Supply Current                                     | Idle                                                                                                                   | • |                       | 9        | 12                    | mA       |

|                  | Operating Supply Current 1Msps, ADC<br>Conversion Rate       | 20pF Loads, SCK = 100MHz                                                                                               | • |                       | 12       | 15                    | mA       |

| V <sub>CC2</sub> | Isolated Operating Supply Range                              |                                                                                                                        | • | 3.0                   |          | 5.5                   | V        |

| I <sub>CC2</sub> | Isolated Operating Supply Current                            | Idle                                                                                                                   | • |                       | 9        | 12                    | mA       |

|                  | Isolated Operating Supply Current, 1Msps ADC Conversion Rate | 20pF Loads, SCK2 = 100MHz                                                                                              | • |                       | 12       | 15                    | mA       |

| $V_L$            | Logic Interface Supply Range                                 |                                                                                                                        | • | 1.71                  |          | 5.5                   | V        |

| IL               | Logic Interface Supply Current                               | Inputs and Outputs Static at GND or V <sub>L</sub>                                                                     | • |                       |          | ±200                  | μΑ       |

|                  | Logic Interface Supply Current, 1Msps<br>Conversion Rate     | SCK = 100MHz, 20pF Load                                                                                                | • |                       | 2        | 5                     | mA       |

| $V_{L2}$         | Isolated Interface Supply Range                              |                                                                                                                        | • | 1.71                  |          | 5.5                   | V        |

| $I_{L2}$         | Isolated Interface Supply Current                            | Inputs and Outputs Static at GND2 or V <sub>L2</sub>                                                                   | • |                       |          | ±200                  | μΑ       |

|                  | Isolated Interface Supply Current, 1Msps ADC Conversion Rate | SCK2 = 100MHz, 20pF Load                                                                                               | • |                       | 2.5      | 5                     | mA       |

| Digital In       | puts and Digital Outputs (Logic Side)                        |                                                                                                                        |   |                       |          |                       |          |

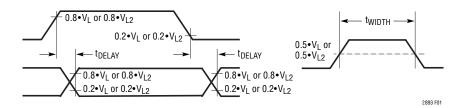

| $V_{IH}$         | High Level Input Voltage                                     | $1.71V \le V_L \le 5.5V$                                                                                               | • | 0.8 • V <sub>L</sub>  |          |                       | V        |

| $V_{IL}$         | Low Level Input Voltage                                      | $1.71V \le V_L \le 5.5V$                                                                                               | • |                       |          | 0.2 • V <sub>L</sub>  | V        |

|                  | Digital Input Current (MOSI, SCK, CNV)                       | $V_{IN} = 0V \text{ to } V_L$                                                                                          | • |                       |          | ±1                    | μΑ       |

|                  | Digital Input Current (SS, CSC, SA, SB, SC, ON)              | $V_{IN} = 0V \text{ to } V_L$                                                                                          | • |                       |          | ±60                   | μA       |

|                  | Digital Input Capacitance                                    | Note 2                                                                                                                 |   |                       | 5        |                       | pF       |

| V <sub>OH</sub>  | High Level Output Voltage                                    | $I_{OUT} = -500\mu A, 1.71V \le V_L \le 5.5V$                                                                          | • | V <sub>L</sub> - 0.2  |          |                       | V        |

| $V_{OL}$         | Low Level Output Voltage                                     | $I_{OUT} = 500\mu A, 1.71V \le V_L \le 5.5V$                                                                           |   |                       |          | 0.2                   | V        |

| I <sub>OZ</sub>  | High-Z Output Leakage Current MISOA, MISOB                   | $\overline{SS} = V_L$                                                                                                  | • |                       |          | ±1                    | μA       |

|                  | Output Source Current (Short-Circuit)                        | V <sub>OUT</sub> = 0V (Note 2)                                                                                         |   |                       | -80      |                       | mA       |

|                  | Output Sink Current (Short-Circuit)                          | V <sub>OUT</sub> = V <sub>L</sub> (Note 2)                                                                             |   |                       | 80       |                       | mA       |

| Digital In       | puts and Digital Outputs (Isolated Side)                     |                                                                                                                        |   |                       |          |                       |          |

| V <sub>IH</sub>  | High Level Input Voltage                                     | $1.71V \le V_{L2} \le 5.5V$                                                                                            | • | 0.8 • V <sub>L2</sub> |          |                       | V        |

| $V_{IL}$         | Low Level Input Voltage                                      | $1.71V \le V_{L2} \le 5.5V$                                                                                            | • |                       |          | 0.2 • V <sub>L2</sub> | V        |

|                  | Digital Input Current (ON2, BUSY2, BUSYS)                    | $V_{IN} = 0V$ to $V_{L2}$ , $ON2 = VL2$                                                                                | • |                       |          | ±60                   | μΑ       |

|                  | Digital Input Current (MISOA2, MISOB2)                       | $V_{IN} = 0V \text{ to } V_{L2}$                                                                                       | • |                       |          | ±10                   | μΑ       |

|                  | Digital Input Capacitance                                    | Note 2                                                                                                                 |   |                       | 5        |                       | pF       |

| V <sub>OH</sub>  | High Level Output Voltage                                    | $I_{OUT} = -500\mu A, 1.71V \le V_{L2} \le 5.5V$                                                                       | • | $V_{L2} - 0.2$        |          |                       | V        |

| $V_{0L}$         | Low Level Output Voltage                                     | $I_{OUT} = 500\mu A, 1.71V \le V_{L2} \le 5.5V$                                                                        | • |                       |          | 0.2                   | V        |

|                  | Output Source Current (Short-Circuit)                        | V <sub>OUT</sub> = 0V (Note 2)                                                                                         |   |                       | -80      |                       | mA       |

|                  | Output Sink Current (Short-Circuit)                          | V <sub>OUT</sub> = V <sub>L2</sub> (Note 2)                                                                            |   |                       | 80       |                       | mA       |

| ESD Perfo        | ormance (Note 7)                                             |                                                                                                                        |   |                       |          |                       |          |

| <u> </u>         | Isolation Barrier                                            | From GND, V <sub>L</sub> , or V <sub>CC</sub> to GND2, V <sub>L2</sub> , or V <sub>CC2</sub>                           |   |                       | ±15      |                       | kV       |

|                  | Logic Side I/O Pins<br>Isolated Side I/O Pins                | With Respect to GND, V <sub>L</sub> , or V <sub>CC</sub>   With Respect to GND2, V <sub>L2</sub> , or V <sub>CC2</sub> |   |                       | ±4<br>±4 |                       | kV<br>kV |

|                  | ISSUALOU GIAG I/O I IIIG                                     | The respect to divide, viz, or vice                                                                                    |   |                       | ±-r      |                       |          |

**SWITCHING CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full specified operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{CC} = 5V$ ,  $V_L = 3.3V$ , GND = 0V,  $V_{CC2} = 5V$ ,  $V_{L2} = 3.3V$ , GND = 0V,  $V_{CC2} = 5V$ ,  $V_{L2} = 3.3V$

| SYMBOL                   | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CONDITIONS                                                                                                                                                               |   | MIN       | TYP | MAX             | UNITS          |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------|-----|-----------------|----------------|

| Conversion S             | tart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ,                                                                                                                                                                        |   |           |     |                 |                |

| t <sub>CNVH</sub>        | CNV Pulse Width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                          | • | 20        |     |                 | ns             |

| t <sub>BUSYLH</sub>      | CNV↑ to BUSY↑ Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                          | • |           |     | 40              | ns             |

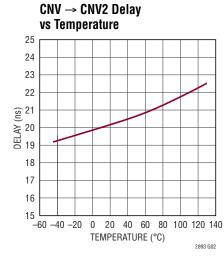

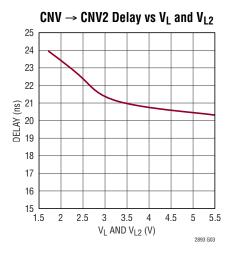

| t <sub>DCNV</sub>        | CNV↑ to CNV2↑ Delay (Aperture Delay)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                          | • | 12        | 21  | 33              | ns             |

| t <sub>CNV2H</sub>       | CNV2 Pulse Width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (Config. SCK2 Frequency ≥ 40MHz)                                                                                                                                         | • | 20        |     | 52              | ns             |

|                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (Config. SCK2 Frequency ≤ 33MHz)                                                                                                                                         | • | 35        |     | 80              | ns             |

|                          | CNV to CNV2 Rising Edge Jitter RMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | (Note 7)                                                                                                                                                                 |   |           | 30  |                 | ps             |

|                          | Minimum Low Time for CNV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                          |   | 100       |     |                 | ns             |

| SPI Timing               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                          |   |           |     |                 |                |

| t <sub>QUIET</sub>       | SCK or SS↑ Space to CNV↑                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | LTM2893<br>LTM2893-1, Configuration Register = 0x9F                                                                                                                      | • | 20<br>320 |     |                 | ns<br>ns       |

| t <sub>SCK</sub>         | SCK Input Period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SCK2 Frequency 100MHz LTM2893 (Note 3)<br>SCK2 Frequency 100MHz LTM2893-1 (Note 3)                                                                                       | • | 10<br>10  |     | 1185            | ns<br>ns       |

| t <sub>SCKH</sub>        | SCK Input High Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | (Note 2)                                                                                                                                                                 | • | 4         |     |                 | ns             |

| t <sub>SCKL</sub>        | SCK Input Low Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | (Note 2)                                                                                                                                                                 | • | 4         |     |                 | ns             |

| t <sub>SCK2</sub>        | SCK2 Output Period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SCK2 Frequency 100MHz (Notes 3, 8)                                                                                                                                       | • | 9.5       | 10  | 10.8            | ns             |

| t <sub>SCK2H</sub>       | SCK2 Output High Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | (Note 2)                                                                                                                                                                 | • | 4         |     |                 | ns             |

| t <sub>SCK2L</sub>       | SCK2 Output Low Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (Note 2)                                                                                                                                                                 | • | 4         |     |                 | ns             |

| t <sub>HDMISO2</sub>     | MISOA2, MISOB2 Data Hold Time from SCK2↑                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | (Note 2)                                                                                                                                                                 | • | 1         |     |                 | ns             |

| t <sub>DMISO</sub>       | MISOA, MISOB Data Valid Delay from SCK↑<br>SCK2 Frequency = 100MHz or 66MHz or from<br>SCK↓ SCK2 Frequency ≤ 50MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | C <sub>L</sub> = 20pF, V <sub>L</sub> = 5.5V (Note 2)<br>C <sub>L</sub> = 20pF, V <sub>L</sub> = 2.5V (Note 2)<br>C <sub>L</sub> = 20pF, V <sub>L</sub> = 1.71V (Note 2) | • |           | 5   | 7.5<br>8<br>9.5 | ns<br>ns<br>ns |

| t <sub>SUMISO2</sub>     | MISOA2, MISOB2, Setup Time to SCK2↑                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | (Note 2)                                                                                                                                                                 | • | 1.8       |     |                 | ns             |

| t <sub>HMISO</sub>       | MISOA, MISOB Data Remains Valid Delay<br>from SCK↑<br>SCK2 Frequency = 100MHz or 66MHz or from<br>SCK↓ SCK2 Frequency ≤ 50MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | C <sub>L</sub> = 20pF (Note 2)                                                                                                                                           | • | 2         |     |                 | ns             |

| t <sub>DMISOSSF</sub>    | MISOA, MISOB Data Valid Delay from SS↓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | C <sub>L</sub> = 20pF                                                                                                                                                    | • |           |     | 10              | ns             |

|                          | MISOA, MISOB Data Valid Delay from BUSY↓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <del>SS</del> = 0V, LTM2893                                                                                                                                              | • |           |     | 10              | ns             |

| t <sub>SSFSCK</sub>      | SS↓ Delay to SCK↑                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SCK2 Frequency 100MHz (Note 8), LTM2893-1                                                                                                                                | • | 20        |     | 1185            | ns             |

| t <sub>BUSYFSCKR</sub>   | BUSY↓ Delay to SCK↑                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SS = 0V, SCK2 Frequency 100MHz<br>(Notes 9, 10)                                                                                                                          | • | 20        |     |                 | ns             |

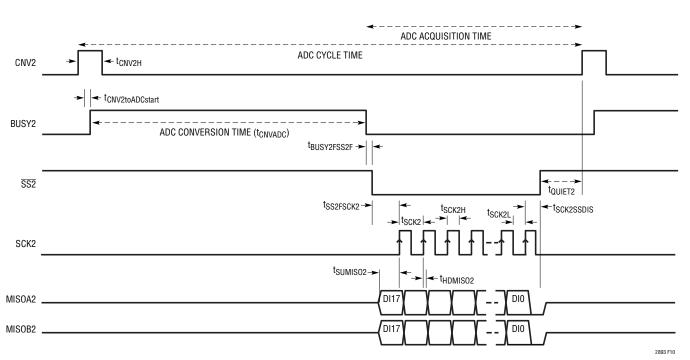

| t <sub>BUSY2FSS2F</sub>  | BUSY2↓ Delay to \$\overline{\SS2}\$↓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                          | • | 15        |     | 35              | ns             |