# **High-Accuracy, Adjustable Power Limiter**

### **General Description**

The MAX14721–MAX14723 adjustable overvoltage, undervoltage, and overcurrent protection devices guard systems against overcurrent faults in addition to positive overvoltage and reverse-voltage faults. When used with an optional external p-channel MOSFET, the devices also protect downstream circuitry from voltage faults up to +60V, -60V (for -60V external pFET rating). The devices feature a low,  $76m\Omega$ , on-resistance integrated FET.

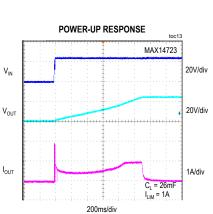

During startup, the devices are designed to charge large capacitances on the output in a continuous mode for applications where large reservoir capacitors are used on the inputs to downstream devices. Additionally, the MAX14721–MAX14723 feature a dual-stage, current-limit mode in which the current is continuously limited to 1x, 1.5x, and 2x the programmed limit, respectively, for a short time after startup. This enables faster charging of large loads during startup.

The MAX14721–MAX14723 also feature reverse-current and overtemperature protection. The devices are available in a 20-pin (5mm x 5mm) TQFN package and operate over a -40°C to 125°C temperature range.

Applications

Industrial Power Systems

Control and Automation

Motion System Drives

Human Machine Interfaces

High-Power Applications

Ordering Information appears at end of data sheet.

#### **Benefits and Features**

- Robust, High-Power Protection Reduces System Downtime

- Wide Input Supply Range: +5.5V to +60V

- Programmable Input Supply Overvoltage Setting Up to 40V

- Thermal Foldback Current-Limit Protection

- Negative Input Tolerance to -60V (for -60V External pFET Rating)

- Low 76mΩ (typ) R<sub>ON</sub>

- Reverse Current-Blocking Protection with External pFET

- Enables Safer Startup By Preventing Overheating of FFTs

- Dual-Stage Current Limiting

- 1.0x Startup Current (MAX14721)

- 1.5x Startup Current (MAX14722)

- · 2.0x Startup Current (MAX14723)

- Flexible Design Enables Reuse and Less Requalification

- · Adjustable OVLO and UVLO Thresholds

- Programmable Forward Current Limit From 0.2A to 2A with ±15% Accuracy Over Full Temperature Range

- Normal and High-Voltage Enable Inputs (EN and HVEN)

- Protected External pFET Gate Drive

- Saves Board Space and Reduces External BOM Count

- 20-Pin, 5mm x 5mm TQFN Package

- Integrated nFET

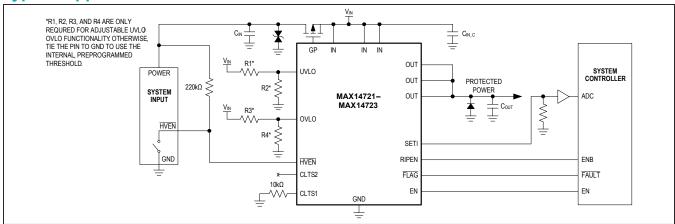

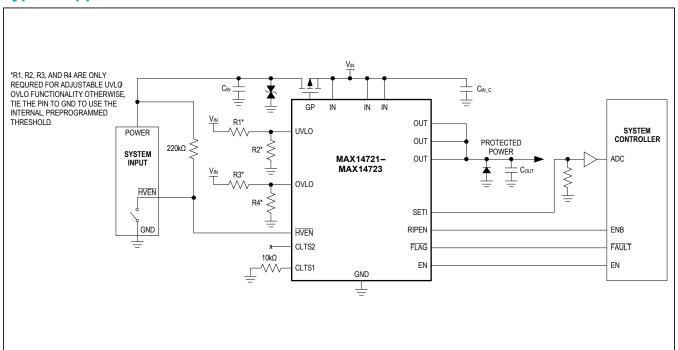

### **Typical Application Circuit**

# High-Accuracy, Adjustable Power Limiter

### **Absolute Maximum Ratings**

| (All voltages referenced to GNI | D.)                                        |

|---------------------------------|--------------------------------------------|

| IN (Note 1)                     | 0.3V to +60.5V                             |

| OUT                             | 0.3V to V <sub>IN</sub> + 0.3V             |

| HVEN (Note 1)                   | 0.3V to V <sub>IN</sub> + 0.3V             |

| GPmax                           | $(-0.3V, V_{IN} - 20V)$ to $V_{IN} + 0.3V$ |

| UVLO, OVLO                      | 0.3V to min $(V_{IN} + 0.3V, 20V)$         |

| FLAG, EN, RIPEN, CLTS1, CL      | ΓS20.3V to +6V                             |

| Maximum Current into IN (DC)    | (Note 2)2A                                 |

| SETI0.3V to                                          | $min(V_{IN} + 0.3V, 6V)$ |

|------------------------------------------------------|--------------------------|

| Continuous Power Dissipation (T <sub>A</sub> = +70°C | C)                       |

| TQFN (derate 31.3mW/°C above +70°C                   | )2500mW                  |

| Operating Temperature Range                          | 40°C to +125°C           |

| Junction Temperature                                 | +150°C                   |

| Storage Temperature Range                            | 65°C to +150°C           |

| Lead Temperature (soldering, 10s)                    | +300°C                   |

| Soldering Temperature (reflow)                       | +260°C                   |

Note 1: An external pFET or diode is required to achieve negative input protection.

Note 2: DC current-limited by R<sub>SETI</sub> as well as by thermal design.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

| PACKAGE TYPE: 20 TQFN                  |          |  |  |  |

|----------------------------------------|----------|--|--|--|

| Package Code                           | T2055+3C |  |  |  |

| Outline Number                         | 21-0140  |  |  |  |

| Land Pattern Number                    | 90-0008  |  |  |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD   |          |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 32°C/W   |  |  |  |

| Junction to Case (θ <sub>JC</sub> )    | 3°C/W    |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to **www.maximintegrated.com/thermal-tutorial**.

### **Electrical Characteristics**

$(V_{IN} = 5.5 V \text{ to } 60 V, T_A = -40 ^{\circ} C \text{ to } +125 ^{\circ} C, \text{ unless otherwise noted.}$  Typical values are at  $V_{IN} = 24 V, T_A = +25 ^{\circ} C.)$  (Note 3)

| PARAMETER                                  | SYMBOL                | CONDITIONS                                                          | MIN  | TYP  | MAX  | UNITS |  |

|--------------------------------------------|-----------------------|---------------------------------------------------------------------|------|------|------|-------|--|

| POWER SUPPLY                               | POWER SUPPLY          |                                                                     |      |      |      |       |  |

| IN Voltage Range                           | V <sub>IN</sub>       |                                                                     | 5.5  |      | 60   | V     |  |

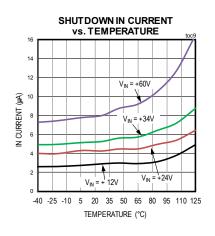

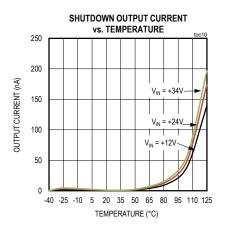

| Charles and IN Commonst                    |                       | V <sub>EN</sub> = 0V, V <sub>HVEN</sub> = 5V, V <sub>IN</sub> < 40V |      | 5.25 | 15   |       |  |

| Shutdown IN Current                        | I <sub>SHDN</sub>     | V <sub>EN</sub> = 0V, V <sub>HVEN</sub> = 5V                        |      | 5.25 | 150  | μA    |  |

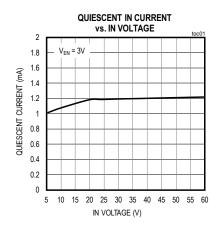

| Supply Current                             | I <sub>IN</sub>       | V <sub>IN</sub> = V <sub>OUT</sub> = 24V, V <sub>HVEN</sub> = 0V    |      | 1.4  | 1.9  | mA    |  |

| Shutdown OUT Current                       | I <sub>OFF</sub>      | V <sub>EN</sub> = 0V, V <sub>HVEN</sub> = 5V                        |      | 50   | 100  | μA    |  |

| UVLO, OVLO                                 |                       |                                                                     |      |      |      |       |  |

| Internal IIIVI O Trin Level                |                       | V <sub>IN</sub> falling, UVLO trip point                            | 11.5 | 12   | 12.5 | V     |  |

| Internal UVLO Trip Level                   | V <sub>UVLO</sub>     | V <sub>IN</sub> rising                                              | 11.9 | 12.4 | 13   | ]     |  |

| UVLO Hysteresis                            |                       | % of typical UVLO                                                   |      | 3    |      | %     |  |

| Internal OV/I O Trip I avail               | V                     | V <sub>IN</sub> falling                                             | 32.1 | 33.8 | 35.6 | V     |  |

| Internal OVLO Trip Level                   | V <sub>OVLO</sub>     | V <sub>IN</sub> rising, OVLO trip point                             | 34.5 | 36   | 37.4 | ] V   |  |

| OVLO Hysteresis                            |                       | % of typical OVLO                                                   |      | 6    |      | %     |  |

| External UVLO Adjustment<br>Range (Note 4) |                       |                                                                     | 5.5  |      | 24   | V     |  |

| External UVLO Select Voltage               | V <sub>UVLO_SEL</sub> |                                                                     | 0.15 | 0.38 | 0.5  | V     |  |

| External UVLO Leakage<br>Current           | luvlo_leak            |                                                                     | -250 |      | +250 | nA    |  |

| External OVLO Adjustment Range (Note 4)    |                       |                                                                     | 6    |      | 40   | V     |  |

| External OVLO Select Voltage               | V <sub>OVLO_SEL</sub> |                                                                     | 0.15 | 0.38 | 0.5  | V     |  |

| External OVLO Leakage<br>Current           | IOVLO_LEAK            |                                                                     | -250 |      | +250 | nA    |  |

| External UVLO/OVLO Set Voltage             | V <sub>SET</sub>      |                                                                     | 1.18 | 1.22 | 1.27 | V     |  |

| Hadamakan Tib Landan Oli                   | V <sub>UVLO_OUT</sub> | V <sub>OUT</sub> falling, UVLO trip point                           | 11.5 | 12   | 12.5 | V     |  |

| Undervoltage Trip Level on OUT             |                       | V <sub>OUT</sub> rising                                             | 11.9 | 12.4 | 13   |       |  |

| GP                                         |                       |                                                                     |      |      |      |       |  |

| Gate Clamp Voltage                         | V <sub>GP</sub>       |                                                                     | 10   | 16.1 | 20   | V     |  |

| Gate Active Pullup                         |                       |                                                                     |      | 25   | 50   | Ω     |  |

| Gate Active Pulldown                       |                       | V <sub>EN</sub> = 5V                                                | 50   | 110  |      | μA    |  |

| Shutdown Gate Active Pullup                |                       | V <sub>EN</sub> = 0V, V <sub>HVEN</sub> = 5V                        |      | 2.2  |      | ΜΩ    |  |

# **Electrical Characteristics (continued)**

$(V_{IN} = 5.5 \text{V to } 60 \text{V}, T_A = -40 ^{\circ}\text{C to } +125 ^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{IN} = 24 \text{V}, T_A = +25 ^{\circ}\text{C}.)$  (Note 3)

| PARAMETER                                   | SYMBOL                | CONDITIONS                                                                                                                                                            | MIN | TYP  | MAX  | UNITS |  |

|---------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|-------|--|

| INTERNAL FETs                               | INTERNAL FETS         |                                                                                                                                                                       |     |      |      |       |  |

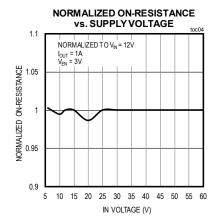

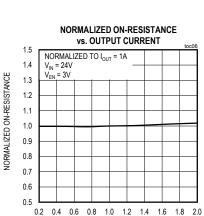

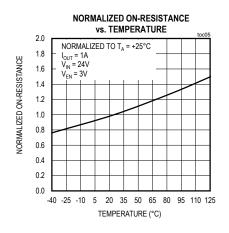

| Internal FETs On-Resistance                 | R <sub>ON</sub>       | $I_{LOAD} = 100 \text{mA}, V_{IN} \ge 10 \text{V},$<br>$T_A = +25 ^{\circ}\text{C}$                                                                                   |     | 76   | 101  | mΩ    |  |

| Current Limit Adjustment Range              | I <sub>LIM</sub>      |                                                                                                                                                                       | 0.2 |      | 2    | А     |  |

| Current Limit Accuracy                      | I                     | $0.3A \le I_{LIM} \le 2A (T_A = +25^{\circ}C)$                                                                                                                        | -10 |      | +10  | 0/    |  |

| Current Limit Accuracy                      | I <sub>LIM_ACC</sub>  | 0.2A ≤ I <sub>LIM</sub> ≤ 2A                                                                                                                                          | -15 |      | +15  | %     |  |

| FLAG Assertion Drop Voltage Threshold       | V <sub>FA</sub>       | Increase in (V <sub>IN</sub> - V <sub>OUT</sub> ) drop until FLAG asserts, V <sub>IN</sub> = 24V                                                                      |     | 480  |      | mV    |  |

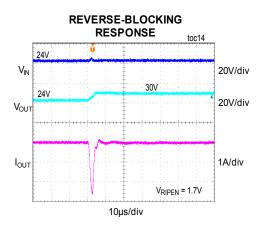

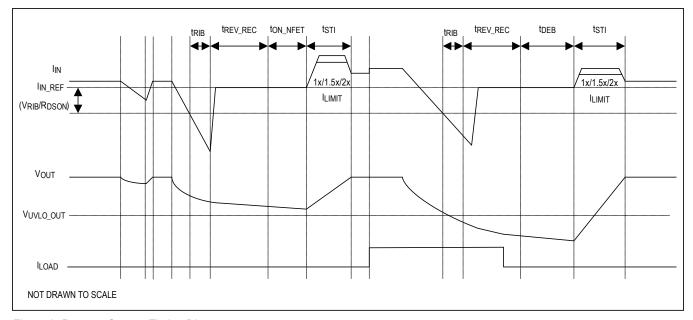

| Reverse Current-Blocking<br>Threshold       | V <sub>RIB</sub>      | V <sub>IN</sub> - V <sub>OUT</sub>                                                                                                                                    | -4  | -9   | -14  | mV    |  |

| Reverse Current-Blocking<br>Response Time   | t <sub>RIB</sub>      | $(V_{IN} - V_{OUT})$ changes from 0.2V to -0.3V in 100nsec, $t_{RIB}$ is the interval between $V_{IN} = V_{OUT}$ and $V_{IN-GP} = 0.5V$ without capacitive load on GP |     | 1    | 1.55 | μs    |  |

| Reverse-Blocking Supply<br>Current          | I <sub>RBS</sub>      | V <sub>OUT</sub> = 24V                                                                                                                                                |     | 2000 | 3900 | μA    |  |

| LOGIC INPUT (HVEN, CLTS1, C                 | LTS2, EN, RIPE        | N)                                                                                                                                                                    |     |      |      |       |  |

| HVEN Threshold Voltage                      | V <sub>HVEN</sub> _TH |                                                                                                                                                                       | 1   | 2    | 3.1  | V     |  |

| HVEN Threshold Hysteresis                   |                       |                                                                                                                                                                       |     | 5    |      | %     |  |

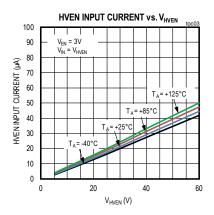

| HVEN Input Leakage Current                  | IHVEN_LEAK            | V <sub>HVEN</sub> = 60V                                                                                                                                               |     | 46   | 67   | μA    |  |

| EN, RIPEN, CLTS1, CLTS2<br>Input Logic-High | V <sub>IH</sub>       |                                                                                                                                                                       | 1.4 |      |      | V     |  |

| EN, RIPEN, CLTS1, CLTS2<br>Input Logic-Low  | V <sub>IL</sub>       |                                                                                                                                                                       |     |      | 0.4  | V     |  |

| EN Input Leakage Current                    | I <sub>EN_LEAK</sub>  | V <sub>EN</sub> = 0V, 5V                                                                                                                                              | -1  |      | +1   | μA    |  |

| RIPEN Leakage Current                       | IRIPEN_LEAK           | RIPEN = GND                                                                                                                                                           |     | 25   |      | μA    |  |

| CLTS_ Leakage Current                       |                       | CLTS_ = GND                                                                                                                                                           |     | 25   |      | μA    |  |

| LOGIC OUTPUT (FLAG)                         |                       |                                                                                                                                                                       | _   |      |      |       |  |

| Logic-Low Voltage                           |                       | I <sub>SINK</sub> = 1mA                                                                                                                                               |     |      | 0.4  | V     |  |

| Input Leakage Current                       |                       | V <sub>IN</sub> = 5.5V, FLAG deasserted                                                                                                                               |     |      | 1    | μA    |  |

| SETI                                        |                       |                                                                                                                                                                       |     |      |      |       |  |

| R <sub>SETI</sub> x I <sub>LIM</sub>        | V <sub>RI</sub>       | See Setting the Current-Limit                                                                                                                                         |     | 1.5  |      | V     |  |

| Current Mirror Output Ratio                 | C <sub>IRATIO</sub>   | Threshold section                                                                                                                                                     |     | 8333 |      |       |  |

### **Electrical Characteristics (continued)**

$(V_{IN} = 5.5V \text{ to } 60V, T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{IN} = 24V, T_A = +25^{\circ}\text{C}.)$  (Note 3)

| PARAMETER                              | SYMBOL               | CONDITIONS                                                                                                                                                             | MIN  | TYP  | MAX  | UNITS |

|----------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| DYNAMIC PERFORMANCE (NO                | OTE 5)               |                                                                                                                                                                        |      |      |      |       |

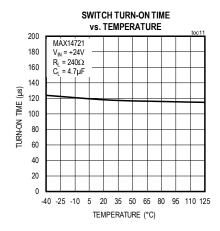

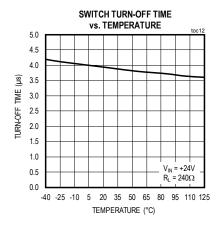

| Switch Turn-On Time                    | t <sub>ON</sub>      | $V_{IN}$ = 24V, switch OFF to ON, R <sub>LOAD</sub><br>= 240Ω, I <sub>LIM</sub> = 1A, C <sub>OUT</sub> = 4.7μF,<br>V <sub>OUT</sub> from 20% to 80% of V <sub>IN</sub> |      | 118  |      | μs    |

| Fault Recovery nFET Turn-on Time       | ton_nfet             | V <sub>OUT</sub> > V <sub>UVLO_OUT</sub> , turn-on delay after fault timers expired                                                                                    |      | 420  | 730  | μs    |

| Reverse-Current Fault<br>Recovery Time | t <sub>REV_REC</sub> |                                                                                                                                                                        | 2.18 | 2.40 | 2.64 | ms    |

| OVP Switch Response Time               | t <sub>OVP_RES</sub> |                                                                                                                                                                        |      | 3    |      | μs    |

| Overcurrent Switch Response time       | tocp_res             | I <sub>LIM</sub> = 2A                                                                                                                                                  |      | 3    |      | μs    |

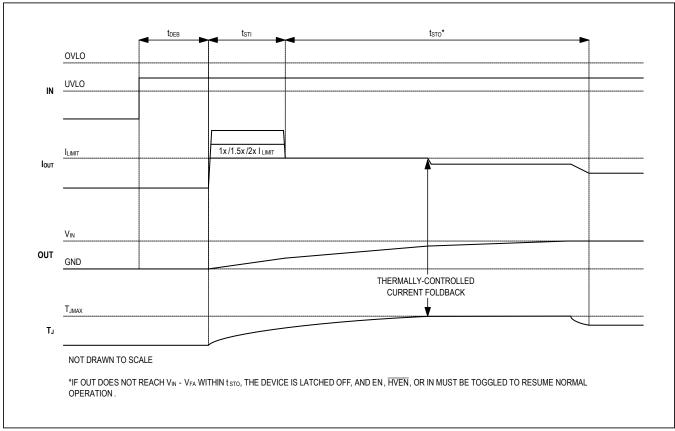

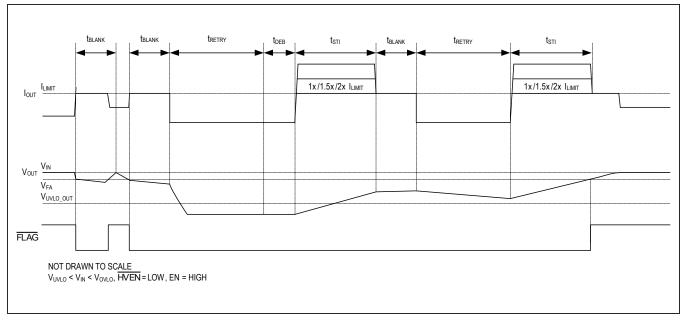

| Startup Timeout                        | tsто                 | Initial start current-limit foldback timeout (Figure 1)                                                                                                                | 1090 | 1200 | 1320 | ms    |

| Startup Initial Time                   | t <sub>STI</sub>     | Current is continuously limited to 1x/1.5x/2x in this interval (Figure 1)                                                                                              | 21.8 | 24   | 26.4 | ms    |

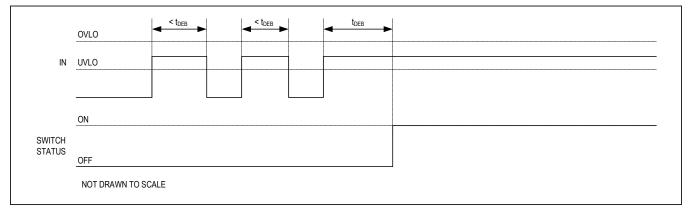

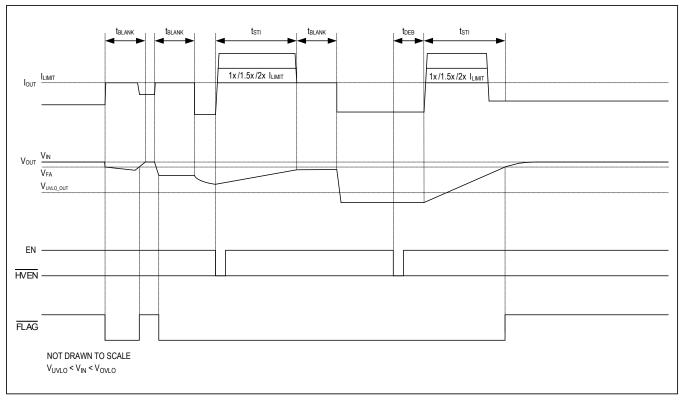

| IN Debounce Time                       | t <sub>DEB</sub>     | Interval between V <sub>IN</sub> > V <sub>UVLO</sub> and V <sub>OUT</sub> = 10% of V <sub>IN</sub> (Figure 2)                                                          | 0.25 | 0.50 | 0.75 | ms    |

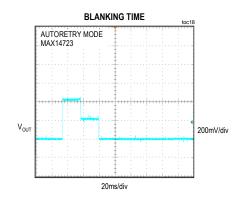

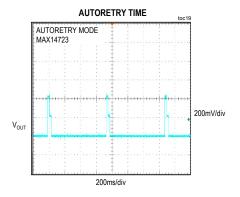

| Blanking Time                          | t <sub>BLANK</sub>   | (Figure 3 and Figure 4)                                                                                                                                                | 21.8 | 24   | 26.4 | ms    |

| Autoretry Time                         | t <sub>RETRY</sub>   | (Figure 3, Note 6)                                                                                                                                                     | 554  | 720  | 792  | ms    |

| THERMAL PROTECTION                     |                      |                                                                                                                                                                        |      |      |      |       |

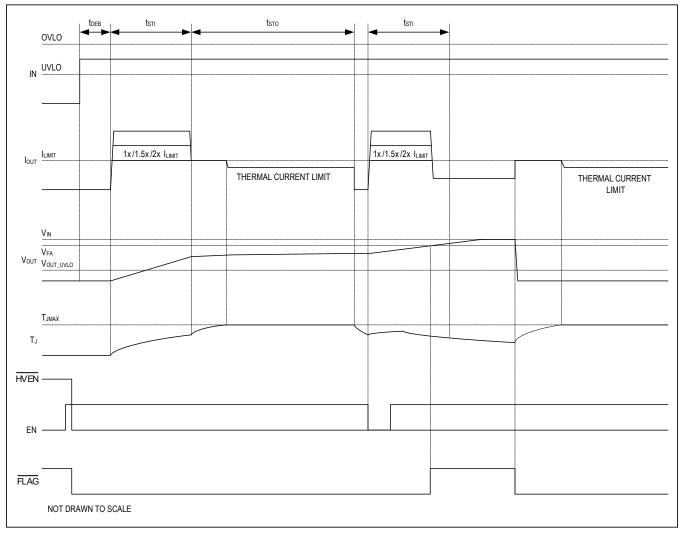

| Thermal Foldback                       | T <sub>J_FB</sub>    |                                                                                                                                                                        |      | 145  |      | °C    |

| Thermal Shutdown                       | T <sub>J_MAX</sub>   |                                                                                                                                                                        |      | 170  |      | °C    |

| Thermal-Shutdown Hysteresis            |                      |                                                                                                                                                                        |      | 20   |      | °C    |

Note 3: All devices are 100% production-tested at T<sub>A</sub> = +25°C. Specifications over the operating temperature range are guaranteed by design.

$<sup>\</sup>textbf{Note 4:} \ \ \text{Not production-tested, user-adjustable. See the} \ \ \underline{\textit{Overvoltage Lockout (OVLO)}} \ \ \text{and} \ \ \underline{\textit{Undervoltage Lockout (UVLO)}} \ \ \text{sections.}$

Note 5: All timing is measured using 20% and 80% levels, unless otherwise specified.

Note 6: The autoretry time-to-blanking time ratio is fixed and is equal to 30.

# **Timing Diagrams**

Figure 1. Startup Timing

Figure 2. Debounce Timing

MAX14721/ MAX14722/ MAX14723

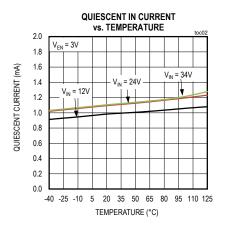

### **Typical Operating Characteristics**

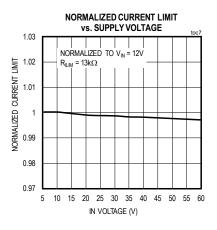

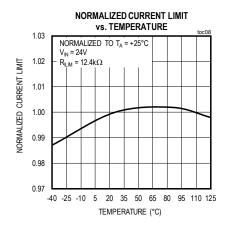

( $V_{IN}$  = 12V,  $C_{IN}$  = 1 $\mu$ F,  $C_{OUT}$  = 4.7 $\mu$ F,  $T_A$  = +25 $^{\circ}$ C, unless otherwise noted.)

OUTPUT CURRENT (A)

### **Typical Operating Characteristics (continued)**

( $V_{IN}$  = 12V,  $C_{IN}$  = 1 $\mu$ F,  $C_{OUT}$  = 4.7 $\mu$ F,  $T_A$  = +25 $^{\circ}$ C, unless otherwise noted.)

MAX14721/ MAX14722/ MAX14723

### **Typical Operating Characteristics**

$(V_{IN}$  = 12V,  $C_{IN}$  = 1 $\mu$ F,  $C_{OUT}$  = 4.7 $\mu$ F,  $T_A$  = +25 $^{\circ}$ C, unless otherwise noted.)

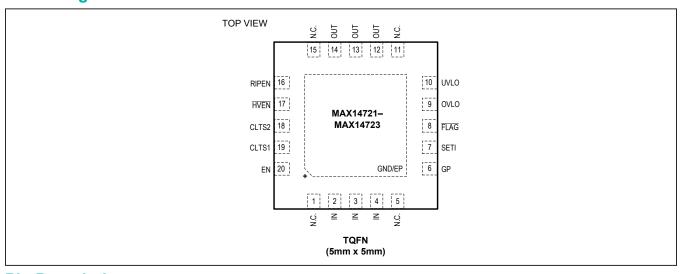

# **Pin Configurations**

# **Pin Description**

| PIN          | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|--------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1, 5, 11, 15 | N.C.   | Not Connected                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 2, 3, 4      | IN     | Switch Input. Bypass IN to ground with a $1\mu F$ ceramic capacitor for $\pm 15 kV$ Human Body Model ESD protection on IN. In applications in which an external pFET is used, a $4.7\mu F$ capacitor should be placed at the drain of the pFET and a reduced capacitor of $10nF$ to $100nF$ should be placed at IN. The maximum slew rate allowed at IN is $30V/\mu s$ . IN serves as the under/overvoltage sensed input when preprogrammed UVLO/OVLO is used. |  |  |

| 6            | GP     | Gate Driver Output for External pFET                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 7            | SETI   | Overload Current-Limit Adjust. Connect a resistor from SETI to GND to program the overcurrent limit. SETI must be connected to a resistor. If SETI is connected to GND during startup, then the switch does not turn on. Do not connect more than 30pF to SETI.                                                                                                                                                                                                |  |  |

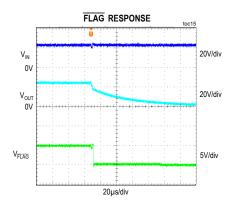

| 8            | FLAG   | Open-Drain Fault Indicator Output. $\overline{\text{FLAG}}$ asserts low when the $V_{\text{IN}}$ - $V_{\text{OUT}}$ voltage exceeds $V_{\text{FA}}$ , reverse-current is detected, thermal shutdown mode is active, OVLO or UVLO threshold is reached, or SETI is connected to GND.                                                                                                                                                                            |  |  |

| 9            | OVLO   | Externally-Programmable Overvoltage Lockout Threshold. Connect OVLO to GND to use the default internal OVLO threshold. Connect OVLO to an external resistor-divider to define a threshold externally and override the preset internal OVLO threshold.                                                                                                                                                                                                          |  |  |

| 10           | UVLO   | Externally-Programmable Undervoltage Lockout Threshold. Connect UVLO to GND to use the default internal UVLO threshold. Connect UVLO to an external resistor-divider to define a threshold externally and override the preset internal UVLO threshold.                                                                                                                                                                                                         |  |  |

| 12, 13, 14   | OUT    | Switch Output. Bypass OUT to GND with a 4.7µF ceramic capacitor placed as close to the device as possible.                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 16           | RIPEN  | Reverse-Current Protection Enable. Internally pulled up. Connect RIPEN to GND with $10k\Omega$ resistor or lower to disable the reverse-current flow protection.                                                                                                                                                                                                                                                                                               |  |  |

| 17           | HVEN   | 60V Capable Active-Low Enable Input. See Table 1.                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 18           | CLTS2  | Current-Limit Type Select 2. See Table 2.                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 19           | CLTS1  | Current-Limit Type Select 1. See Table 2.                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 20           | EN     | Active-High Enable Input. See Table 1.                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| _            | GND/EP | Ground/Exposed Pad. Connect to a large copper ground plane to maximize thermal performance.                                                                                                                                                                                                                                                                                                                                                                    |  |  |

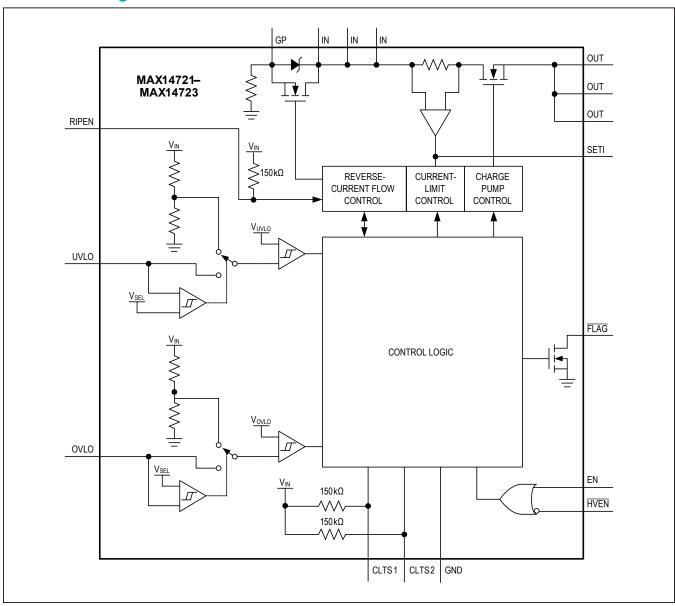

# **Functional Diagram**

# High-Accuracy, Adjustable Power Limiter

### **Detailed Description**

The MAX14721-MAX14723 adjustable overvoltage, undervoltage, and overcurrent protection devices guard systems against overcurrent faults in addition to positive overvoltage and reverse-voltage faults. When used with an optional external p-channel MOSFET, these devices also protect downstream circuitry from voltage faults up to +60V, -60V (for-60V external pFET rating). The MAX14721-MAX14723 feature a low,  $76m\Omega$ , onresistance integrated FET. During startup, the devices are designed to charge large capacitances on the output in a continuous mode for applications where large reservoir capacitors are used on the inputs to downstream devices. Additionally, the MAX14721, MAX14722, and MAX14723 feature a dual-stage current-limit mode in which the current is continuously limited to 1x, 1.5x, and 2x the programmed limit, respectively, for a short time after startup. This enables faster charging of large loads during startup.

The MAX14721–MAX14723 feature the option to set the overvoltage lockout (OVLO) and undervoltage lockout (UVLO) thresholds manually using external voltage dividers or to use the factory-preset internal thresholds by connecting the OVLO and/or UVLO pin(s) to GND. The permitted overvoltage lockout set point range of the devices is 6V to 40V, while the permitted undervoltage lockout set point range is 5.5V to 24V. Therefore, the pFET and internal nFET must be kept off in the 40V to 60V range by appropriate OVLO resistor divider.

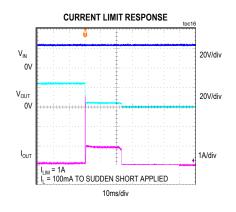

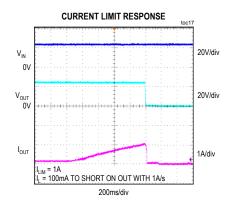

The devices' programmable current-limit threshold can be set for currents up to 2A in autoretry, latchoff, or continuous fault response mode. When the device is set to autoretry mode and the current exceeds the threshold for more than 24ms (typ), both FETs are turned off for 720ms (typ), then turned back on. If the fault is still present, the cycle repeats. In latchoff mode, if a fault is present for more than 24ms (typ), both FETs are turned off until enable is toggled or the power is cycled. In continuous mode, the current is limited continuously to the programmed current-limit value. In all modes,  $\overline{\text{FLAG}}$  asserts if  $\text{V}_{\text{IN}}$  -  $\text{V}_{\text{OUT}}$  is greater than the  $\overline{\text{FLAG}}$  assertion drop voltage threshold (VFA).

### Startup Control

These devices feature a dual-stage startup sequence that continuously limits the current to 1x/1.5x/2x the set current limit during the startup initial time ( $t_{\rm STI}$ ), allowing large capacitors present on the output of the switch to be rapidly charged. The MAX14721 limits the current to 1x the set limit during this period while the MAX14722 and MAX14723 limit the current to 1.5x and 2x the set limit, respectively. If the temperature of any device rises to the thermal foldback threshold ( $T_{\rm J}$  FB), the device will enter

power-limiting mode (Figure 1). In this mode, the device thermally regulates the current through the switch in order to protect itself while still delivering as much current as possible to the output regardless of the current limit type selected. If the output is not charged within the startup timeout period ( $t_{STO}$ ), the switch turns off and IN, EN, or  $\overline{HVEN}$  must be toggled to resume normal operation.

The MAX14721–MAX14723 have a 16ms (typ) time delay at the end of startup, during which the reverse threshold is set at -90mV (typ) to prevent false reverse faults due to oscillation. After this delay, the reverse current-blocking threshold is reduced to -9mV ( $V_{RIB}$ , typ).

#### Overvoltage Lockout (OVLO)

The devices feature two methods for determining the OVLO threshold. By connecting the OVLO pin to GND, the preset internal OVLO threshold of 36V (typ) is selected. If the voltage at OVLO rises above the OVLO select threshold (VOVLO\_SEL), the device enters adjustable OVLO mode. Connect an external voltage divider to the OVLO pin as shown in the *Typical Application Circuit* to adjust the OVLO threshold. The permitted overvoltage lockout set point range of the device is 6V to 40V. R3 = 2.2M $\Omega$  is a good starting value for minimum current consumption. Since V<sub>SET</sub> is known (1.22V, typ), R3 has been chosen, and V<sub>OVLO</sub> is the target OVLO value, R4 can then be calculated by the following equation:

$$R4 = \frac{R3 \times V_{SET}}{V_{OVLO} - V_{SET}}$$

#### **Undervoltage Lockout (UVLO)**

The devices feature two methods for determining the UVLO threshold. By connecting the UVLO pin to GND, the preset, internal UVLO threshold of 12V (typ) is selected. If the voltage at UVLO rises above the UVLO select threshold ( $V_{UVLO\_SEL}$ ) the device enters adjustable UVLO mode. Connect an external voltage divider to the UVLO pin as shown in the <u>Typical Application Circuit</u> to adjust the UVLO threshold. The permitted undervoltage lockout set point range of the device is 5.5V to 24V. R1 = 2.2M $\Omega$  is a good starting value for minimum current consumption. Since  $V_{SET}$  is known (1.22V, typ), R1 has been chosen, and  $V_{UVLO}$  is the target value, R2 can then be calculated by the following equation:

$$R2 = \frac{R1 \times V_{SET}}{V_{UVLO} - V_{SET}}$$

#### **Switch Control**

There are two independent enable inputs on the devices:  $\overline{HVEN}$  and  $\overline{EN}$ .  $\overline{HVEN}$  is a high-voltage-capable input,

### High-Accuracy, Adjustable Power Limiter

Table 1. Enable Inputs

| HVEN | EN | SWITCH STATUS |

|------|----|---------------|

| 0    | 0  | ON            |

| 0    | 1  | ON            |

| 1    | 0  | OFF           |

| 1    | 1  | ON            |

accepting signals up to 60V. EN is a low-voltage input, accepting a maximum voltage of 5V. In case of a fault condition, toggling HVEN or EN resets the fault. The enable inputs control the state of the switch based on the truth table (Table 1).

### **Input Debounce**

The MAX14721–MAX14723 feature a built-in input debounce time ( $t_{DEB}$ ). The debounce time is a delay between a POR event and the switch being turned on. If the input voltage rises above the UVLO threshold voltage or if, with a voltage greater than  $V_{UVLO}$  present on IN, the enable pins toggle to the on state, the switch turns on after  $t_{DEB}$ . In cases where the voltage at IN falls below  $V_{UVLO}$  before  $t_{DEB}$  has passed, the switch remains off (Figure 2). If the voltage at OUT is already above  $V_{UVLO}$ \_OUT when the device is turned on through either enable pin or coming out of OVLO, there is no debounce interval. This is due to the device already being out of the POR condition with OUT above  $V_{UVLO}$ \_OUT.

#### **Current-Limit Type Select**

The MAX14721–MAX14723 feature three selectable current-limiting modes. During power-up, all devices default to continuous mode and follow the procedure defined in the <u>Startup Control</u> section. Once the part has been successfully powered on and  $t_{STO}$  has expired, the device senses the condition of CLTS1 and CLTS2. The condition of CLTS1 and CLTS2 sets the current-limit mode type according to <u>Table 2</u>. CLTS1,2 are internally pulled up to an internal 5V supply. Therefore, the device is in continuous current-limit mode when CLTS1 and CLTS2 are open. To set CLTS\_ state to low, connect a  $10k\Omega$  resistor or below to ground.

In addition to the selectable current-limiting modes, the device has a protection feature against a severe over load condition. If the output current exceeds 2 times the set current limit, the device will turn off the internal nFET and external pFET immediately and will attempt to restart to allow the overcurrent to last for  $t_{BLANK}$  time. The OFF duration depends on fault condition occurred after the FETs turn off, with the shortest duration of 420µs ( $t_{ON\_FET}$ )

**Table 2. Current-Limit Type Select**

| CLTS2 | CLTS1 | CURRENT-LIMIT TYPE |

|-------|-------|--------------------|

| 0     | 0     | LATCHOFF MODE      |

| 0     | 1     | AUTORETRY MODE     |

| 1     | 0     | CONTINUOUS MODE    |

| 1     | 1     | CONTINUOUS MODE    |

if there is no fault. In Latchoff mode, the device will latch off if the overcurrent fault last longer than t<sub>BLANK</sub>.

#### **Autoretry Mode (Figure 3)**

In autoretry current-limit mode, when current through the device reaches the threshold, the  $t_{BLANK}$  timer begins counting. The  $\overline{FLAG}$  output asserts low when the voltage drop across the switch rises above  $V_{FA}.$  If the overcurrent condition is present for  $t_{BLANK},$  the switch is turned off. The timer resets if the overcurrent condition disappears before  $t_{BLANK}$  has elapsed. A retry time delay  $(t_{RETRY})$  starts immediately once  $t_{BLANK}$  has elapsed. During the retry time, the switch remains off and, once  $t_{RETRY}$  has elapsed, the switch is turned back on. If the fault still exists, the cycle is repeated and  $\overline{FLAG}$  remains low. If the fault has been removed, the switch stays on.

The autoretry feature reduces system power in case of overcurrent or short-circuit conditions. When the switch is on during  $t_{BLANK}$  time, the supply current is held at the current limit. When the switch is off during  $t_{RETRY}$  time, there is no current through the switch. Thus, the output current is much less than the programmed current limit. Calculate the average output current using the following equation.

$$I_{LOAD} = I_{LIM} \left[ \frac{t_{BLANK} + t_{STI} \times K}{t_{BLANK} + t_{RETRY} + t_{STI}} \right]$$

where K is the multiplication factor of the initial current limit (1x, 1.5x or 2x). With a 24ms (typ)  $t_{BLANK}$ , 24ms  $t_{STI}$ , K = 1 and 720ms (typ)  $t_{RETRY}$ , the duty cycle is 3.1%, resulting in 97% power saving as compared to the switch being on the entire time.

#### Latchoff Mode (Figure 4)

In latchoff current-limit mode, when current through the device reaches the threshold, the  $t_{BLANK}$  timer begins counting. The  $\overline{FLAG}$  asserts when the voltage drop across the switch rises above  $V_{FA}.$  The timer resets if the overcurrent condition disappears before  $t_{BLANK}$  has elapsed. The switch turns off if the overcurrent condition remains for the blanking time. The switch remains off until the control logic (EN or  $\overline{HVEN})$  is toggled or the input voltage is cycled.

Figure 3. Autoretry Fault Diagram

Figure 4. Latchoff Fault Diagram

# High-Accuracy, Adjustable Power Limiter

#### **Continuous Mode (Figure 5)**

In continuous current-limit mode, when current through the device reaches the threshold, the device limits the current to the programmed limit.  $\overline{\text{FLAG}}$  asserts when the voltage drop across the switch rises above  $V_{FA},$  and deasserting when it falls below  $V_{FA}.$

#### **Reverse-Current Blocking (Figure 6)**

The MAX14721–MAX14723 feature current-blocking functionality to be used with external pFET. To enable the reverse-current blocking feature, pull RIPEN high. With RIPEN high, if a reverse-current condition is detected ( $V_{IN}$  -  $V_{OUT}$  <  $V_{RIB}$ ), the internal nFET and the external pFET are turned off for 2.4ms ( $t_{REV}$  REC). During and after this

time, the device monitors the voltage difference between OUT and IN pins to determine whether the reverse current is still present. Once  $t_{REV\_REC}$  expired and the reverse-current condition has been removed, the nFET and pFET are turned back on after an additional time delay follows by the dual-stage startup control mechanism as defined in the Startup Control section above. The additional time delay will be 420us ( $t_{ON\_NFET}$ ) if voltage at OUT is more than or equal to  $v_{UVLO\_OUT}$  falling at the end of  $t_{REV\_REC}$  delay, otherwise the delay will be 0.5ms ( $t_{DEB}$ ). After a reverse-current event, the device will attempt a restart regardless of the current-type select.

Figure 5. Continuous Fault Diagram

Figure 6. Reverse-Current Timing Diagram

# High-Accuracy, Adjustable Power Limiter

### Fault Indicator (FLAG) Output

FLAG is an open-drain fault indicator output. It requires an external pullup resistor to a DC supply. FLAG asserts when any of the following conditions occur:

- V<sub>IN</sub> V<sub>OUT</sub> > V<sub>FA</sub>

- The reverse-current protection is tripped

- The die temperature exceeds +170°C

- SETI is connected to ground

- UVLO threshold has not been reached

- OVLO threshold is reached

#### **Thermal Shutdown Protection**

Thermal shutdown circuitry protects the <u>devices</u> from overheating. The switch turns off and <u>FLAG</u> asserts when the junction temperature exceeds +170°C (typ). The MAX14721–MAX14723 exit thermal shutdown and resume normal operation once the junction temperature cools by 20°C (typ) if the device is in autoretry or continuous current-limiting mode. When in latchoff mode, the device remains latched off until the input voltage is cycled or one of the enable pins is toggled.

The thermal-shutdown technology built into the MAX14721–MAX14723 behaves in accordance with the selected current limit mode. While the devices are in autoretry mode, the thermal limit uses the autoretry timing when coming out of a fault condition. When the MAX14721–MAX14723 detects an overtemperature fault, the switch turns off. Once the temperature of the junction falls below the falling thermal threshold, the device turns on after the time interval t<sub>RETRY</sub>. In latchoff mode, the device latches off until the input is cycled or one of the enable pins is toggled. In continuous current-limiting mode, the device turns off while the temperature is over the limit, then turns back on after t<sub>DEB</sub> when the temperature reaches the falling threshold. There is no retry time for thermal protection.

### **Applications Information**

### **Setting the Current-Limit Threshold**

Connect a resistor between SETI and ground to program the current-limit threshold for the MAX14721–MAX14723. Leaving SETI unconnected sets the current-limit threshold to 0A and, since connecting SETI to ground is a fault condition, this causes the switch to remain off and  $\overline{\text{FLAG}}$  to assert. Use the following formula to calculate the current-limit threshold:

$$R_{SETI}(k\Omega) = \frac{V_{RI}(\Omega \times A)}{I_{I,IM}(mA)} \times C_{IRATIO}$$

Do not use a R<sub>SETI</sub> smaller than  $6k\Omega$ . Table 3 shows current-limit thresholds for different resistor values at SETI.

A current mirror with a ratio of  $C_{IRATIO}$  is implemented with a current sense auto-zero operational amplifier. The mirrored current of the IN-OUT FET is provided on the SETI pin. Therefore, the voltage ( $V_{SETI}$ ) read on the SETI pin should be interpreted as the current through the IN-OUT FET, as shown below:

$$\begin{split} I_{IN-OUT} = I_{SETI} \times C_{IRATIO} &= \frac{V_{SETI}(V)}{R_{SETI}(k\Omega)} \\ \times C_{IRATIO} &= \frac{V_{SETI}(V)}{V_{PI}(V)} \times I_{LIM} \end{split}$$

#### **IN Bypass Capacitor**

In applications in which an external PFET is not used, connect a minimum of  $1\mu F$  capacitor from IN to GND to limit the input voltage drop during momentary output short-circuit conditions. Larger capacitor values further reduce the voltage droop at the input caused by load transients.

In applications in which an external PFET is used, a  $4.7\mu F$  capacitor is placed at the drain of the PFET and capacitor at IN is reduced to 10nF (100nF, max).

#### **Hot Plug-In**

In many power applications, an input filtering capacitor is required to lower the radiated emission, enhance the ESD capability, etc. In hot plug applications, parasitic cable inductance, along with the input capacitor, causes overshoot and ringing when a powered cable is suddenly connected to the input terminal. This effect causes the protection device to see almost twice the applied voltage. An input voltage of 24V can easily exceed 40V due to ringing. The MAX14721–MAX14723 contain internal protection against hot plug input transients on the IN pins, with slew rate up to 30V/µs. However, in the case where the harsh industrial EMC test is required, use a

Table 3. Current-Limit Threshold vs. Resistor Values

| R <sub>SETI</sub> (kΩ) | CURRENT LIMIT (A) |  |

|------------------------|-------------------|--|

| 62.5                   | 0.2               |  |

| 25.0                   | 0.5               |  |

| 12.5                   | 1.0               |  |

| 8.3                    | 1.5               |  |

| 6.25                   | 2.0               |  |

transient voltage suppressor (TVS) placed close to the

input terminal that is capable of limiting the input surge to a maximimum of 60V.

#### **OUT Capacitance**

For stable operation over the full temperature range and over the entire programmable current-limit range, connect a 4.7µF ceramic capacitor from OUT to ground. Other circuits connected to the output of the device may introduce additional capacitance, but it should be noted that excessive output capacitance on the MAX14721-MAX14723 can cause faults. If the capacitance is too high, the MAX14721-MAX14723 may not be able to charge the capacitor before the startup timeout. Calculate the maximum capacitive load (C<sub>MAX</sub>) value that can be connected to OUT using the following formula:

$$C_{MAX}(mF) = I_{LIM}(A) \left[ \frac{M \times t_{STI}(ms) + t_{STO}(ms)}{V_{IN\_MAX}(V)} \right]$$

where M is the multiplier (1x/1.5x/2x) applied to the current limit during startup. For example, when using MAX14721, if  $V_{IN\ MAX} = 20V$ ,  $t_{STO}$  (min) = 1090ms,  $t_{STI}$  (min) = 22ms, and  $\overline{I_{LIM}}$  = 2A,  $C_{MAX}$  results in the theoretical maximum of 111mF. In this case, any capacitance larger than 111mF will cause a fault condition because the capacitor cannot be charged to a sufficient voltage before tsto has expired. In practical applications, the output capacitor size is limited by the thermal performance of the PCB board. Poor thermal design can cause the thermal foldback currentlimiting function of the device to kick in too early, which may further limit the maximum capacitance that can be charged. Therefore, good thermal PCB design is imperative in order to charge large capacitor banks.

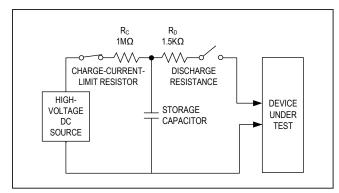

Figure 7. Human Body ESD Test Model

#### **OUT Freewheeling Diode for Inductive Hard** Short to Ground

In applications with a highly inductive load, a freewheeling diode is required between the OUT terminal and GND. This protects the device from inductive kickback that occurs during short-to-ground events.

### **Layout and Thermal Dissipation**

To optimize the switch response to output short-circuit conditions, it is important to reduce the effect of undesirable parasitic inductance by keeping all traces as short as possible. Place input and output capacitors as close as possible to the device (no more than 5mm). IN and OUT must be connected with wide short traces to the power bus. During steady-state operation, the power dissipation is typically low and the package temperature change is usually minimal.

Attention must be given when using continuous currentlimit mode. In this mode, the power dissipation during a fault condition can quickly cause the device to reach the thermal shutdown threshold. A large copper plane and multiple thermal vias from the exposed pad to ground plane are necessary to increase the thermal capacitance and reduce the thermal resistance of the board.

#### **ESD Test Conditions**

The MAX14721-MAX14723 are specified for ±15kV (HBM) ESD on IN when IN is bypassed to ground with a 1µF, low ESR ceramic capacitor. No capacitor is required for ±2kV (HBM) (typ) ESD on IN. All pins have ±2kV (HBM) ESD protection. In applications in which an external pFET is used, see IN Bypass Capacitor section.

#### **HBM ESD Protection**

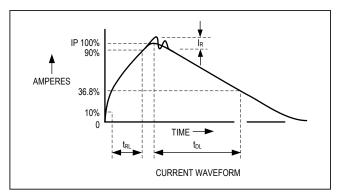

Figure 7 shows the Human Body Model and Figure 8 shows the current waveform it generates when discharged into low impedance. This model consists of a 100pF capacitor charged to the ESD voltage of interest, which is then discharged into the device through a  $1.5k\Omega$  resistor.

Figure 8. Human Body Current Waveform

# **Typical Application Circuit**

### **Ordering Information**

| PART          | INITIAL CURRENT LIMIT | TEMP RANGE      | PIN-PACKAGE |

|---------------|-----------------------|-----------------|-------------|

| MAX14721ATP+T | 1.0x                  | -40°C to +125°C | 20 TQFN-EP* |

| MAX14722ATP+T | 1.5x                  | -40°C to +125°C | 20 TQFN-EP* |

| MAX14723ATP+T | 2.0x                  | -40°C to +125°C | 20 TQFN-EP* |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

# **Chip Information**

PROCESS: BICMOS

T = Tape and reel.

<sup>\*</sup>EP = Exposed pad.