### **General Description**

The MAX14808 evaluation kit (EV kit) provides a proven design to evaluate the MAX14808 high-voltage, high-frequency pulse driver IC.

The MAX14808 evaluation system (EV system) consists of the MAX14808 EV kit and a companion MAXINT1 serial interface board. The EV system also includes Windows XP®-, Windows Vista®-, and Windows® 7-compatible software that provides a simple graphical user interface (GUI) for exercising the features of the IC. The MAXINT1 board provides the inputs to the IC. Order the EV system for a complete PC-based evaluation of the IC, including test waveform generation. Order the EV kit if you already have a MAXINT1 board or a MAX14808-compatible controller interface.

The EV kit comes with a MAX14808ETK+ installed.

#### Features

- Windows XP-, Windows Vista-, and Windows 7-Compatible Software

- 3.5mm Scope-Probe Jacks for High-Voltage Outputs

- USB-PC Connection (Cable Included)

- RoHS Compliant

- ♦ 40-Pin Signal Header

- Proven PCB Layout

- Fully Assembled and Tested

Ordering Information appears at end of data sheet.

### **Component List**

#### MAX14808 EV System

| PART           | QTY | DESCRIPTION                |

|----------------|-----|----------------------------|

| MAX14808EVKIT# | 1   | MAX14808 EV kit            |

| MAXINT1#       | 1   | Controller interface board |

#### MAX14808 EV Kit

| DESIGNATION                                     | QTY | DESCRIPTION                                                                             |

|-------------------------------------------------|-----|-----------------------------------------------------------------------------------------|

| C1, C2, C3, C16,<br>C17, C18, C27, C44          | 8   | 0.1µF ±10%, 16V X7R<br>ceramic capacitors (0402)<br>Murata GRM155R71C104K               |

| C4, C5, C14, C15,<br>C26, C28, C29, C36,<br>C41 | 9   | 1μF ±10%, 10V X7R<br>ceramic capacitors (0603)<br>TDK C1608X7R1A105K                    |

| C6, C7, C12                                     | 3   | 10µF ±10%, 25V X7R<br>ceramic capacitors (1206)<br>Murata GRM31CR71E106K                |

| C8–C11, C24, C25,<br>C30–C35                    | 12  | 0.1µF ±10%, 100V X7R<br>ceramic capacitors (0603)<br>Murata GRM188R72A104K              |

| C13, C19, C20, C21                              | 4   | 10µF ±20%, 160V<br>aluminium electrolytic<br>capacitors (G13)<br>Panasonic EEV-EB2C100Q |

|               |     | MAX14808 EV KIT                                                                    |

|---------------|-----|------------------------------------------------------------------------------------|

| DESIGNATION   | QTY | DESCRIPTION                                                                        |

| C22, C23, C43 | 3   | 1nF ±20%, 10V X7R<br>ceramic capacitors (0402)<br>KEMET C0402C102M8RAC             |

| C37           | 1   | 47μF ±10%, 10V low-ESR<br>tantalum capacitor<br>(7343-31)<br>KEMET B45197A2476K409 |

| C38           | 1   | 10µF ±20%, 10V low-ESR<br>tantalum capacitor (1206)<br>TPSA106M010R0900            |

| C39           | 1   | 82pF ±5%, 50V C0G<br>ceramic capacitor (0603)<br>Murata GRM1885C1H820J             |

| C40           | 1   | 1μF ±10%, 10V tantalum<br>capacitor (0805)<br>AVX TAJR105K010R                     |

Windows, Windows XP, and Windows Vista are registered trademarks of Microsoft Corporation.

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

### **Component List (continued)**

### MAX14808 EV Kit (continued)

| DESIGNATION                            | QTY | DESCRIPTION                                                                         |

|----------------------------------------|-----|-------------------------------------------------------------------------------------|

| C42                                    | 1   | 100µF ±20%, 10V low-ESR<br>tantalum capacitor (7343)<br>Vishay<br>593D107X0010D2TE3 |

| COUT1-COUT8                            | 8   | 220pF ±10%, 100V X7R<br>ceramic capacitors (0402)<br>Murata GRM155R72A221K          |

| D1                                     | 1   | 20V, 1A SMA Schottky<br>diode<br>Fairchild SS12                                     |

| FB1, FB2, FB3                          | 3   | 600Ω ±25% 500mA ferrite<br>beads (0603)<br>TDK MMZ1608B601C                         |

| GND                                    | 17  | Black test points                                                                   |

| H1                                     | 1   | 40-pin (2 x 20) dual-row<br>header<br>Samtec LS2-120-01-S-D-<br>RA2                 |

| H2                                     | 1   | 40-pin (2 x 20) dual-row,<br>straight header<br>Sullins PEC36DAAN                   |

| JU1–JU4, JU9, JU20,<br>JU21, JU23–JU33 | 18  | 3-pin headers                                                                       |

| JU5–JU8,<br>JU10–JU19, JU22            | 15  | 2-pin headers                                                                       |

| L1                                     | 1   | 10µH ±20%, 1.44A power<br>inductor<br>Sumida CR54NP-100MC                           |

| LVOUT1–LVOUT8,<br>OUT1–OUT8, THP       | 17  | White test points                                                                   |

| R1                                     | 1   | 1k $\Omega$ ±5% resistor (1210)                                                     |

| R2                                     | 1   | $47k\Omega \pm 1\%$ resistor (0402)                                                 |

| R3                                     | 1   | 10k $\Omega$ ±5% resistor (0603)                                                    |

| MAX14808 EV Kit (continued |                                                                                       |  |  |  |

|----------------------------|---------------------------------------------------------------------------------------|--|--|--|

| QTY                        | DESCRIPTION                                                                           |  |  |  |

| 1                          | 130k $\Omega$ ±1% resistor (0603)                                                     |  |  |  |

| 1                          | 300k $\Omega$ ±5% resistor (0201)                                                     |  |  |  |

| 1                          | $100\Omega \pm 1\%$ resistor (0201)                                                   |  |  |  |

| 8                          | 1kΩ ±5%, 1W resistors<br>(2512)<br>Panasonic ERJ-1TYJ102U                             |  |  |  |

| 0                          | Not installed, 3.5mm<br>scope-probe jacks                                             |  |  |  |

| 8                          | 3.5mm scope-probe jacks                                                               |  |  |  |

| 1                          | High-voltage, high-<br>frequency pulse driver (68<br>TQFN-EP*)<br>Maxim MAX14808ETK+  |  |  |  |

| 1                          | Negative-output inverting<br>current-mode PWM<br>regulator (8 SO)<br>Maxim MAX755CSA+ |  |  |  |

| 1                          | 200mA, negative-output<br>LDO linear regulator<br>(5 SOT23)<br>Maxim MAX1735EUK50+    |  |  |  |

| 1                          | LVDS line driver (8 SOT23)<br>Maxim MAX9110EKA+                                       |  |  |  |

| 1                          | SPI serial flash (8 SO)<br>Micron M25P16-VMW6TG                                       |  |  |  |

| 7                          | Red test points                                                                       |  |  |  |

| 0                          | Not installed, black test points                                                      |  |  |  |

| 1                          | PCB: MAX14808<br>EVALUATION KIT                                                       |  |  |  |

|                            | 1<br>1<br>1<br>8<br>0<br>8<br>1<br>1<br>1<br>1<br>1<br>1<br>7<br>0                    |  |  |  |

\*EP = Exposed pad.

### **Component Suppliers**

| SUPPLIER                              | PHONE        | WEBSITE                     |

|---------------------------------------|--------------|-----------------------------|

| AVX Corporation                       | 843-946-0238 | www.avx.com                 |

| Fairchild Semiconductors              | 888-522-5372 | www.fairchildsemi.com       |

| KEMET Corp.                           | 864-963-6300 | www.kemet.com               |

| Murata Electronics North America Inc. | 770-436-1300 | www.murata-northamerica.com |

| Panasonic Corp.                       | 800-344-2112 | www.panasonic.com           |

| TDK Corp.                             | 847-803-6100 | www.component.tdk.com       |

| Vishay                                | 402-563-6866 | www.vishay.com              |

Note: Indicate that you are using the MAX14808 when contacting these component suppliers.

### MAX14808 EV Kit Files

| FILE                    | DESCRIPTION                                   |

|-------------------------|-----------------------------------------------|

| INSTALL.EXE             | Installs the EV kit files on<br>your computer |

| MAX14808.EXE            | Application program                           |

| CDM20600.EXE            | Installs the USB device driver                |

| UNINSTALL.EXE           | Uninstalls the EV kit software                |

| USB_Driver_Help_200.PDF | USB driver installation help file             |

### Quick-Start Stand-Alone Mode Procedure

#### **Required Equipment**

- MAX14808 EV kit

- Custom interface controller board (other than the MAXINT1 board)

- +3.3V DC, 600μA power supply

- +5V DC, 1A power supply

- +5V to +100V DC, 30mA (+100V) to 600mA (+5V) power supply

- -5V to -100V DC, -30mA (-100V) to -600mA (-5V) power supply

- Digital storage oscilloscope

#### Procedure

The EV kit is fully assembled and tested. Follow the steps below to verify board operation:

- Connect the custom interface controller board to the EV kit through header H2.

- 2) Verify that all jumpers (JU1–JU33) are in their default positions, as shown in Table 1.

- 3) Connect the +5V DC power supply to VCC.

- 4) Connect the +3.3V DC power supply to VDD.

- 5) Connect the +5V to +100V DC power supply to VPPA.

- 6) Connect the -5V to -100V DC power supply to VNNA.

- 7) Place the shunts on jumpers JU10 and JU11 such that VNNB is shorted to VNNA and VPPB is shorted to VPPA.

- 8) Connect the required power supply to the custom board.

- 9) The FPGA/microcontroller on the external board has to provide the inputs to the IC through the

DINN1–DINN8 and DINP1–DINP8 pins. It needs to be programmed accordingly. See the MAX14808/ MAX14809 IC data sheet for more information.

10) To observe the output signals from the IC, connect the oscilloscope to the OUT1–OUT8 test points or the TOUT1–TOUT8 scope-probe jacks and GND.

### Quick-Start with the MAXINT1 Board

#### **Required Equipment**

- MAX14808 EV kit

- MAXINT1 interface board (USB cable included)

- +5V DC, 1A power supply

- +5V to +100V DC, 30mA (+100V) to 600mA (+5V) power supply

- -5V to -100V DC, -30mA (-100V) to -600mA (-5V) power supply

- Digital storage oscilloscope

**Note:** In the following sections, software-related items are identified by bolding. Text in **bold** refers to items directly from the EV kit software. Text in **bold and under**<u>lined</u> refers to items from the Windows operating system.

#### Procedure

The EV kit is fully assembled and tested. Follow the steps below to verify board operation:

- Visit <u>www.maximintegrated.com/evkitsoftware</u> to download the latest version of the EV kit software, 14808Rxx.ZIP. Save the EV kit software to a temporary folder and uncompress the ZIP file.

- 2) Install the EV kit software and USB driver on your computer by running the INSTALL.EXE program inside the temporary folder. The program files are copied to your PC and icons are created in the Windows <u>Start I Programs</u> menu. During software installation, some versions of Windows may show a warning message indicating that this software is from an unknown publisher. This is not an error condition and it is safe to proceed with installation. Administrator privileges are required to install the USB device driver on Windows.

- 3) Connect the MAXINT1 board to the EV kit through header H1.

- 4) Verify that all the shunts (JU1–JU33) on the EV kit board are in their default positions, as shown in Table 1.

- 5) For the EV kit board, change the shunt position to pins 2-3 for jumpers JU1 and JU2, and to the 1-2 position for jumpers JU24, JU26, JU28, and JU30.

- 6) Verify that all the shunts (JU1–JU13) on the MAXINT1 interface board are in their default positions, as shown in Table 2.

- 7) Connect the +5V to +100V DC power supply to VPPA.

- 8) Connect the -5V to -100V DC power supply to VNNA.

- 9) Place the shunts on jumpers JU10 and JU11 such that VNNB is shorted to VNNA and VPPB is shorted to VPPA. Separate power supplies can also be used for VNNA/VNNB and VPPA/VPPB.

- 10) Connect the USB cable from the PC to the MAXINT1 board. A Windows message appears when connecting the MAXINT1 board to the PC for the first time. Each version of Windows has a slightly different message. If you see a Windows message stating <u>ready</u> <u>to use</u>, then proceed to the next step. Otherwise, open the USB\_Driver\_Help\_200.PDF document in the Windows <u>Start I Programs</u> menu to verify that the USB driver was installed successfully.

- Start the EV kit software by opening its icon in the Windows <u>Start I Programs</u> menu. The EV kit software main window appears, as shown in Figure 1.

- 12) Enable the +5V to +100V DC and -5V to -100V DC power supplies.

- 13) Click on the Connect button to connect to the MAXINT1 board.

- 14) Click on the radio buttons on the GUI to select the operating mode, waveform, output frequency, frequency of pulses, and output current.

**Note:** For continuous-wave mode, it is recommended that the current output should not be more than 0.5A. Lower VPP and VNN to 5V before switching to CW mode. The GUI does not count the supply of the EV kit.

15) To observe the output signals from the IC, connect the oscilloscope to the OUT1–OUT8 test points or the TOUT1–TOUT8 scope-probe jacks and GND.

**Note:** With MAXINT1 boards, some USB ports may not be able to supply enough current for VEE to be generated on the EV kit from VCC coming from the MAXINT1 board. In that case, there are two options:

- 1) An external +5V, 1A supply could be provided at the VCC\_EXT test point on the EV kit after shorting pins 1-2 on jumper JU2 and pins 2-3 on jumper JU21.

- 2) An external -5V, 1A supply could be provided at the VEE\_EXT test point on the EV kit after shorting pins 1-2 on JU21 and pins 2-3 on JU2.

### **Detailed Description of Software**

The software sends commands to the FPGA, which provides input signals to the MAX14808 IC. The PC GUI has a **Connect** and a **Close** button that are used to connect to the MAXINT1 board or close the connection to the MAXINT1 board, respectively. It has five radio button group boxes used to select the operating mode, output waveform, output frequency, frequency of pulses, and the output current of IC. It also displays the nature of the waveform to be expected at the IC output, although the frequency of the waveform and the pulses might be different.

| Connect Clo                    | . 1              |                          |

|--------------------------------|------------------|--------------------------|

|                                | 3e               |                          |

| Mode                           | Output Frequency | Waveform                 |

| C ShutDown                     |                  | • NRZ pulses, DINP first |

| Octal 3 levels                 | C 2.5 MHz        | C NRZ pulses, DINN first |

| C Quad 5 levels                | C 5 MHz          | C RZ pulses, DINP first  |

| C Disable                      | C 10 MHz         | C RZ pulses, DINN first  |

|                                | C 20 MHz         | C CW pulses, NRZ         |

|                                |                  |                          |

|                                |                  |                          |

| Frequency of Pulses every 100u | s Output Current |                          |

| I pulse                        | C 2A             |                          |

| C 2 pulses                     | C 1.5A           |                          |

| C 3 pulses                     | C 1A             | and                      |

| C 4 pulses                     | @ 0.5A           | 017                      |

|                                |                  |                          |

Figure 1. MAX14808 EV Kit Software

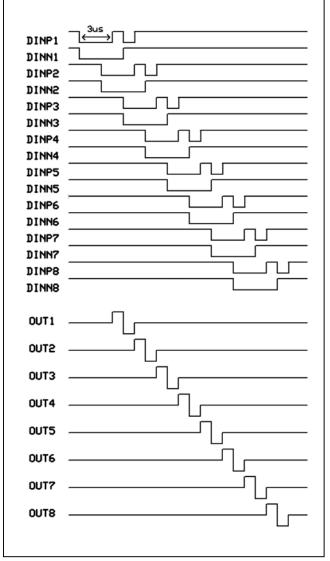

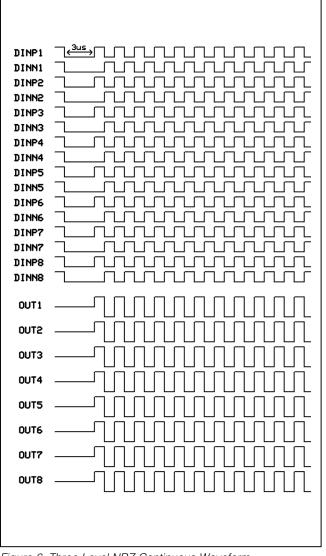

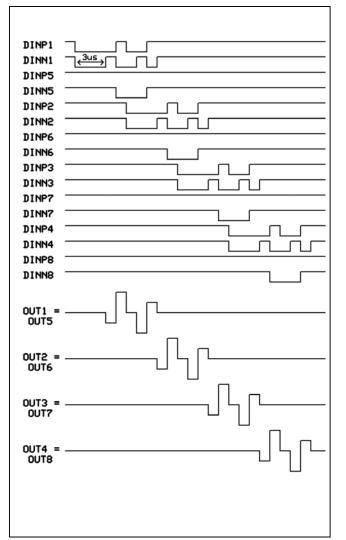

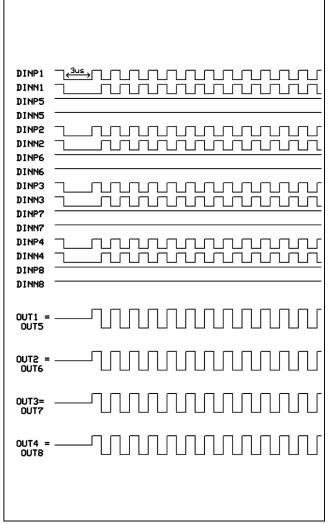

Figure 2. Three-Level NRZ Waveform (DINP First)

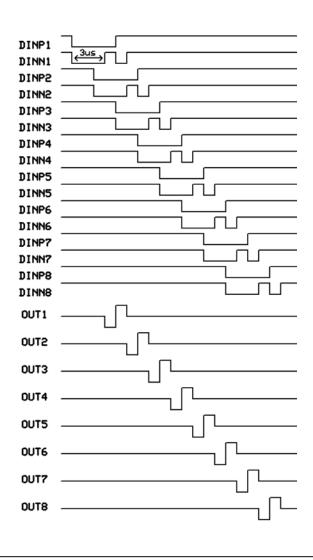

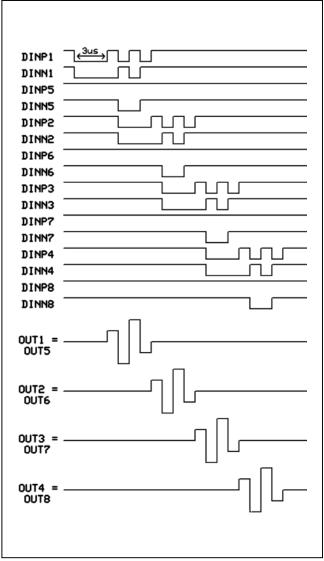

Figure 3. Three-Level NRZ Waveform (DINN First)

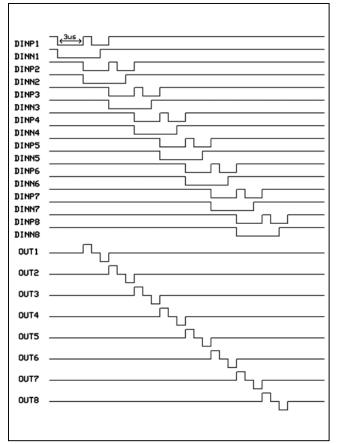

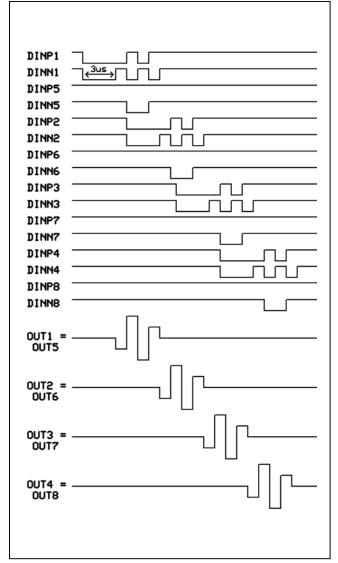

Figure 4. Three-Level RZ Waveform (DINP First)

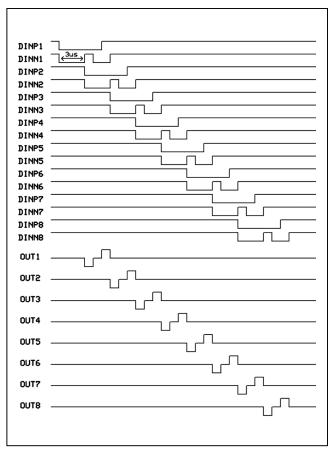

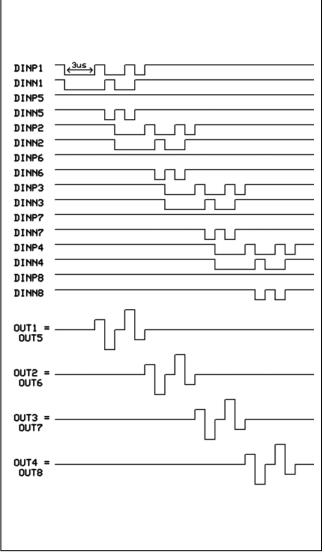

Figure 5. Three-Level RZ Waveform (DINN First)

Figure 6. Three-Level NRZ Continuous Waveform

Figure 7. Five-Level NRZ Waveform (DINP First)

Figure 8. Five-Level NRZ Waveform (DINN First)

Figure 9. Five-Level RZ Waveform (DINP First)

Figure 10. Five-Level RZ Waveform (DINN First)

Figure 11. Five-Level NRZ Continuous Waveform

### **Detailed Description of Hardware**

The MAX14808 EV system includes the MAX14808 EV kit and the MAXINT1 serial interface board. The EV kit provides a proven layout for the IC. The MAXINT1 board is used to provide input signals to the MAX14808 device (U1).

#### **Power Supplies**

The EV kit has the option of getting +5V DC VCC from the MAXINT1, or from an external power supply determined by the shunt position on jumper JU2. It also has the option of getting -5V DC VEE from either the MAX1735 (U3), driven by a MAX755 (U2), or from an external power supply determined by the shunt position on jumper JU21. The U2 and U3 devices can be shut down to reduce the switching noise from the U2 device by placing a shunt on pins 2-3 on jumper JU20. The +3.3V VDD can also be supplied from the MAXINT1 board or from an external power supply through the use of jumper JU1. The two fully independent dual high-voltage supplies (VNNA, VNNB and VPPA, VPPB) can be provided from external power supplies by the use of the VNNA, VNNB, VPPA, and VPPB test points, respectively. A common voltage supply can be used for VNNA and VNNB by shorting jumper JU10. Similarly, a common voltage supply can be used for VPPA and VPPB by shorting jumper JU11.

#### **Differential Clock Generator**

The EV kit has a single MAX9110 LVDS line driver (U4) that requires a single-ended clock input. The singleended clock input to the U4 or U1 device can be provided from either the MAXINT1 through connector H1, or a custom interface controller board through connector H2. The differential-ended clock signals to the U1 device can be provided by the U4 device or an external interface controller board through connector H2, depending on the shunt positions on jumpers JU32 and JU33, as shown in Table 1. While giving differentialended clock signals, termination resistor R6 can be added by placing a shunt in the 1-2 position on jumper JU22. The single-ended or differential clocks come into play only when the SYNC input to the U1 device is high, which is decided by jumper JU4. Otherwise, the U1 device does not do any clock conditioning.

#### Internal LDO

For disabling the internal LDO, a shunt should be placed in the 1-2 position on jumper JU3. If internal LDOs are not used, then external bias has to be provided at the VGNA, VGPA, VGNB, and VGPB test points.

#### **Operating Modes**

The operating modes can be chosen by the MODE0 and MODE1 inputs on the U1 device. These two inputs can be provided from the MAXINT1 through connector H1 or from a custom interface controller board through connector H2 by placing a shunt in the 1-2 position on jumpers JU28 and JU30, or from the board jumpers (JU29, JU31) by placing a shunt in the 2-3 position on JU28 and JU30, as shown in Table 1.

In octal three-level mode, OUT1/OUT5, OUT2/OUT6, OUT3/OUT7, and OUT4/OUT8 need to be disconnected by placing a shunt on pin 1 on jumpers JU5–JU8. In quad five-level mode, OUT1/OUT5, OUT2/OUT6, OUT3/OUT7, and OUT4/OUT8 need to be shorted by placing a shunt in the 1-2 position on JU5–JU8.

#### **Pulser Current Capability**

The pulser current capability can be chosen by the CC0 and CC1 inputs on the U1 device. These two inputs can be provided from the MAXINT1 through connector H1 or a custom interface controller board through connector H2 by placing a shunt in the 1-2 position on jumpers JU24 and JU26, or from the board jumpers (JU25, JU27) by placing a shunt in the 2-3 position on JU24 and JU2, as shown in Table 1.

#### **High-Voltage Outputs**

The high-voltage outputs can be observed on the oscilloscope using test points OUT1–OUT8 or SMA connectors TOUT1–TOUT8.

#### Low-Voltage Outputs

The low-voltage outputs can be observed on the oscilloscope using test points LVOUT1–LVOUT8 or SMA connectors TLVOUT1–TLVOUT8. The low-voltage output SMA connectors are not installed but the pads are present on the PCB.

#### **On-Board Flash**

The on-board M25P16 flash device (U5) on the EV kit is provided to store the firmware for the Spartan 3 FPGA on the MAXINT1 board.

| JUMPER | SHUNT<br>POSITION | DESCRIPTION                                                                                                                                          |  |  |  |

|--------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| JU1    | 1-2*              | Connects VDD to the external +3.3V supply.                                                                                                           |  |  |  |

| 2-3    |                   | Connects VDD to the +3.3V supply from the MAXINT1.                                                                                                   |  |  |  |

| 1-2*   |                   | Connects VCC to an external +5V supply.                                                                                                              |  |  |  |

| JU2    | 2-3               | Connects VCC to the +5V supply from the MAXINT1.                                                                                                     |  |  |  |

| 11.10  | 1-2               | Disables the U1 device's internal LDO.                                                                                                               |  |  |  |

| JU3    | 2-3*              | Enables the U1 device's internal LDO.                                                                                                                |  |  |  |

| 11.1.4 | 1-2               | Enables the SYNC feature.                                                                                                                            |  |  |  |

| JU4    | 2-3*              | Disables the SYNC feature.                                                                                                                           |  |  |  |

|        | Pin 1*            | Disconnects OUT1 and OUT5 in octal three-level mode.                                                                                                 |  |  |  |

| JU5    | 1-2               | Shorts OUT1 and OUT5 in quad five-level dual mode.                                                                                                   |  |  |  |

|        | Pin 1*            | Disconnects OUT2 and OUT6 in octal three-level mode.                                                                                                 |  |  |  |

| JU6    | 1-2               | Shorts OUT2 and OUT6 in guad five-level dual mode.                                                                                                   |  |  |  |

|        | Pin 1*            | Disconnects OUT3 and OUT7 in octal three-level mode.                                                                                                 |  |  |  |

| JU7    | 1-2               | Shorts OUT3 and OUT7 in quad five-level dual mode.                                                                                                   |  |  |  |

|        | Pin 1*            | Disconnects OUT4 and OUT8 in octal three-level mode.                                                                                                 |  |  |  |

| JU8    | 1-2               | Shorts OUT4 and OUT8 in guad five-level dual mode.                                                                                                   |  |  |  |

|        | 1-2*              | Connects CLK to GND for single-ended operation or when the SYNC feature is disabled.                                                                 |  |  |  |

| JU9    |                   |                                                                                                                                                      |  |  |  |

|        | Pin 1             | Disconnects VPPA and VPPB in case separate supplies are used for VPPA and VPPB.                                                                      |  |  |  |

| JU10   | 1-2*              | Shorts VPPA and VPPB in case the same supply is to be used for VPPA and VPPB.                                                                        |  |  |  |

|        | Pin 1             | Disconnects VNNA and VNNB in case separate supplies are used for VNNA and VNNB.                                                                      |  |  |  |

| JU11   | 1-2*              | Shorts VNNA and VNNB in case the same supply is to be used for VNNA and VNNB.                                                                        |  |  |  |

|        | Pin 1*            | Dummy load ROUT1 and COUT1 is disconnected.                                                                                                          |  |  |  |

| JU12   | 1-2               | Dummy load ROUT1 and COUT1 connects to OUT1.                                                                                                         |  |  |  |

|        | Pin 1*            | Dummy load ROUT2 and COUT2 is disconnected.                                                                                                          |  |  |  |

| JU13   | 1-2               | Dummy load ROUT2 and COUT2 connects to OUT2.                                                                                                         |  |  |  |

|        | Pin 1*            | Dummy load ROUT5 and COUT5 is disconnected.                                                                                                          |  |  |  |

| JU14   | 1-2               | Dummy load ROUT5 and COUT5 connects to OUT5.                                                                                                         |  |  |  |

|        | Pin 1*            | Dummy load ROUT6 and COUT6 is disconnected.                                                                                                          |  |  |  |

| JU15   | 1-2               | Dummy load ROUT6 and COUT6 connects to OUT6.                                                                                                         |  |  |  |

|        | Pin 1*            | Dummy load ROUT3 and COUT3 is disconnected.                                                                                                          |  |  |  |

| JU16   | 1-2               | Dummy load ROUT3 and COUT3 connects to OUT3.                                                                                                         |  |  |  |

|        | Pin 1*            | Dummy load ROUT4 and COUT4 is disconnected.                                                                                                          |  |  |  |

| JU17   | 1-2               | Dummy load ROUT4 and COUT4 connects to OUT4.                                                                                                         |  |  |  |

|        | Pin 1*            | Dummy load ROUT7 and COUT7 is disconnected.                                                                                                          |  |  |  |

| JU18   | 1-2               | Dummy load ROUT7 and COUT7 connects to OUT7.                                                                                                         |  |  |  |

|        | Pin 1*            | Dummy load ROUT8 and COUT8 is disconnected.                                                                                                          |  |  |  |

| JU19   | 1-2               | Dummy load ROUT8 and COUT8 connects to OUT8.                                                                                                         |  |  |  |

| JU20   | 1-2*              | Connects SHDN on the U2 device and the U3 device to VCC to turn the ICs on. Used if VEE is being connected to the on-board -5V LDO (JU21, pins 2-3). |  |  |  |

|        | 2-3               | Shuts down the U2 device and the U3 device if an external -5V supply is used.                                                                        |  |  |  |

|        | 1-2               | Connects VEE to the external -5V supply.                                                                                                             |  |  |  |

| JU21   | 2-3*              | Connects VEE to the on-board -5V supply from the U3 device.                                                                                          |  |  |  |

### Table 1. EV Kit Jumper Descriptions (JU1–JU33)

| JUMPER           | SHUNT<br>POSITION | DESCRIPTION                                                                                                                         |

|------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| JU22 Pin 1*      |                   | Disconnects termination resistance R6.                                                                                              |

| 0022             | 1-2               | Connects termination resistance R6. Used if a differential clock is used.                                                           |

|                  | 1-2*              | Connects the CLK input on the U1 device to a single-ended clock from MB through H1 or from another external board through H2.       |

| JU23             | 2-3               | Connects the CLK input on the U1 device to a differential clock from the on-board U4 device or an external clock (decided by JU32). |

| JU24             | 1-2               | Connects CC0 on the U1 device to the CC0 output from MB. This is to select the output current mode.                                 |

| JU24             | 2-3*              | Connects CC0 on the U1 device to either VDD or GND depending on JU25. This is to select the output current mode.                    |

| JU25             | 1-2*              | If pins 2-3 are connected for JU24, then connects CC0 on the U1 device to VDD. This is to select the output current mode.           |

| JU25             | 2-3               | If pins 2-3 are connected for JU24, then connects CC0 on the U1 device to GND. This is to select the output current mode.           |

| 1-2              |                   | Connects CC1 on the U1 device to the CC1 output from MB. This is to select the output current mode.                                 |

| JU26             | 2-3*              | Connects CC1 on the U1 device to either VDD or GND depending on JU27. This is to select the output current mode.                    |

| JU27 -           | 1-2*              | If pins 2-3 are connected for JU26, then connects CC1 on the U1 device to VDD. This is to select the output current mode.           |

|                  | 2-3               | If pins 2-3 are connected for JU26, then connects CC1 on the U1 device to GND. This is to select the output current mode.           |

| 1-2              |                   | Connects MODE0 on the U1 device to the MODE0 output from MB. This is to select the operating mode.                                  |

| JU28             | 2-3*              | Connects MODE0 on the U1 device to either VDD or GND depending on JU29. This is to select the operating mode.                       |

| JU29 1-2<br>2-3* |                   | If pins 2-3 are connected for JU28, then connects MODE0 on the U1 device to VDD. This is to select the operating mode.              |

|                  |                   | If pins 2-3 are connected for JU28, then connects MODE0 on the U1 device to GND. This is to select the operating mode.              |

| 11.120           | 1-2               | Connects MODE1 on the U1 device to the MODE1 output from MB. This is to select the operating mode.                                  |

| JU30             | 2-3*              | Connects MODE1 on the U1 device to either VDD or GND depending on JU31. This is to select the operating mode.                       |

| 11 10 1          | 1-2               | If pins 2-3 are connected for JU30, then connects MODE1 on the U1 device to VDD. This is to select the operating mode.              |

| JU31             | 2-3*              | If pins 2-3 are connected for JU30, then connects MODE1 on the U1 device to GND. This is to select the operating mode.              |

| JU32             | 1-2*              | Chooses a differential positive phase clock to come from the on-board U4 device.                                                    |

| JU32             | 2-3               | Chooses a differential positive phase clock to come from an external source through H2.                                             |

| JU33             | 1-2*              | Chooses a differential negative phase clock to come from the on-board U4 device.                                                    |

| 0000             | 2-3               | Chooses a differential negative phase clock to come from an external source through H2.                                             |

### Table 1. EV Kit Jumper Descriptions (JU1–JU33) (continued)

\*Default position.

### Table 2. MAXINT1 Jumper Descriptions (JU1–JU13)

| JUMPER                                      | SHUNT<br>POSITION                                                                     | DESCRIPTION                                                                                                 |  |  |  |

|---------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|--|--|

| JU1                                         | 1-2                                                                                   | IOVDD = +1.8V from U10.                                                                                     |  |  |  |

| (IOVDD select) 1-3*                         |                                                                                       | IOVDD = +3.3V from U7.                                                                                      |  |  |  |

| setting must<br>match FPGA<br>configuration | 1-4                                                                                   | IOVDD = external user-supplied IOVDD from test point TPEXTIOVDD.<br>Note restriction +1.1V < IOVDD < +3.6V. |  |  |  |

| JU2                                         | Pin 1*                                                                                | FPGA mode signal M0 = 1 (see Table 3).                                                                      |  |  |  |

| (FPGA M0)                                   | 1-2                                                                                   | FPGA mode signal M0 = 0 (see Table 3).                                                                      |  |  |  |

| JU3                                         | Pin 1                                                                                 | FPGA mode signal M1 = 1 (see Table 3).                                                                      |  |  |  |

| (FPGA M1)                                   | 1-2*                                                                                  | FPGA mode signal M1 = 0 (see Table 3).                                                                      |  |  |  |

| JU4                                         | Pin 1                                                                                 | FPGA mode signal M2 = 1 (see Table 3).                                                                      |  |  |  |

| (FPGA M2)                                   | 1-2*                                                                                  | FPGA mode signal M2 = 0 (see Table 3).                                                                      |  |  |  |

| JU5                                         | Pin 1*                                                                                | FPGA VS2 = 1 (see Table 4).                                                                                 |  |  |  |

| (FPGA VS2)                                  | 1-2                                                                                   | FPGA VS2 = 0 (see Table 4).                                                                                 |  |  |  |

| JU6                                         | Pin 1*                                                                                | FPGA VS1 = 1 (see Table 4).                                                                                 |  |  |  |

| (FPGA VS1)                                  | 1-2                                                                                   | FPGA VS1 = 0 (see Table 4).                                                                                 |  |  |  |

| JU7                                         | Pin 1*                                                                                | FPGA VS0 = 1 (see Table 4).                                                                                 |  |  |  |

| (FPGA VS0)                                  | 1-2                                                                                   | FPGA VS0 = 0 (see Table 4).                                                                                 |  |  |  |

| JU8                                         | 1-2*                                                                                  | HOLD1 is connected to ground.                                                                               |  |  |  |

| HOLD1/HOLD2)                                | 2-3                                                                                   | HOLD2 is connected to ground.                                                                               |  |  |  |

| JU9                                         | 1-2*                                                                                  | U7 powers the +3.3V supply rail.                                                                            |  |  |  |

| (enables 3.3V<br>from U7)                   | Open                                                                                  | Measures the MAXINT1 +3.3V supply current by putting a current meter in series with the jumper.             |  |  |  |

| JU10                                        | 1-2*                                                                                  | U8 powers the +0.9V supply rail.                                                                            |  |  |  |

| (enables 0.9V<br>from U8)                   | es 0.9V Measures the MAXINT1 +0.9V supply current by putting a current meter in serie |                                                                                                             |  |  |  |

| JU11                                        | 1-2*                                                                                  | U9 powers the +1.2V supply rail.                                                                            |  |  |  |

| (enables 1.2V<br>from U9)                   | Open                                                                                  | Measures the MAXINT1 +1.2V supply current by putting a current meter in series with the jumper.             |  |  |  |

| JU12                                        | 1-2*                                                                                  | U10 powers the +1.8V supply rail.                                                                           |  |  |  |

| (enables 1.8V<br>from U10)                  | Open                                                                                  | Measures the MAXINT1 +1.8V supply current by putting a current meter in series with the jumper.             |  |  |  |

| JU13                                        | 1-2                                                                                   | +5V is supplied by an external power supply.                                                                |  |  |  |

| (+5V supply)                                | 2-3*                                                                                  | +5V is supplied by the USB.                                                                                 |  |  |  |

|                                             | 1-2                                                                                   | USB bridge drives JTAG header J2.                                                                           |  |  |  |

| JUTCK                                       | 2-3                                                                                   | USB bridge drives SPI flash header J3.                                                                      |  |  |  |

|                                             | Pin 1*                                                                                | USB bridge does not drive J2 or J3.                                                                         |  |  |  |

|                                             | 1-2                                                                                   | USB bridge drives JTAG header J2.                                                                           |  |  |  |

| JUTDI                                       | 2-3                                                                                   | USB bridge drives SPI flash header J3.                                                                      |  |  |  |

|                                             | Pin 1*                                                                                | USB bridge does not drive J2 or J3.                                                                         |  |  |  |

|                                             | 1-2                                                                                   | USB bridge drives JTAG header J2.                                                                           |  |  |  |

| JUTDO                                       | 2-3                                                                                   | USB bridge drives SPI flash header J3.                                                                      |  |  |  |

|                                             | Pin 1*                                                                                | USB bridge does not drive J2 or J3.                                                                         |  |  |  |

|                                             | 1-2                                                                                   | USB bridge drives JTAG header J2.                                                                           |  |  |  |

| JUTMS                                       | 2-3                                                                                   | USB bridge drives SPI flash header J3.                                                                      |  |  |  |

| ľ                                           | Pin 1*                                                                                | USB bridge does not drive J2 or J3.                                                                         |  |  |  |

\*Default position.

### Table 3. MAXINT1 FPGA Mode Selection Jumper Descriptions (JU2, JU3, JU4)

| JU2 (M0)      | JU3 (M1)      | JU4 (M2)      | FPGA MODE                                                                     |

|---------------|---------------|---------------|-------------------------------------------------------------------------------|

| Open (M0 = 1) | 1-2 (M1 = 0)  | Open (M2 = 1) | JTAG configuration mode from header J2 or from USB (future).                  |

| Open (M0 = 1) | 1-2 (M1 = 0)  | 1-2 (M2 = 0)  | Master SPI configuration mode from U5 flash.                                  |

| Open (M0 = 1) | Open (M1 = 1) | Open (M2 = 1) | Slave serial configuration mode from U5 flash device on connector J3 or J6.   |

| Open (M0 = 1) | Open (M1 = 1) | 1-2 (M2 = 0)  | Master internal SPI configuration mode from U4 (requires U4 Spartan 3).       |

| 1-2 (M0 = 0)  | 1-2 (M1 = 0)  | Open (M2 = 1) | Reserved.                                                                     |

| 1-2 (M0 = 0)  | 1-2 (M1 = 0)  | 1-2 (M2 = 0)  | Master serial configuration mode from XCFxx platform flash from connector J6. |

| 1-2 (M0 = 0)  | Open (M1 = 1) | Open (M2 = 1) | Reserved (slave parallel mode not supported)                                  |

| 1-2 (M0 = 0)  | Open (M1 = 1) | 1-2 (M2 = 0)  | Reserved (slave BPI mode not supported)                                       |

### Table 4. MAXINT1 FPGA Mode Selection Jumper Descriptions (JU5, JU6, JU7)

| JU5 (VS2)      | JU6 (VS1)      | JU7 (VS0)      | SPI READ COMMAND TO U5 |

|----------------|----------------|----------------|------------------------|

| Open (VS2 = 1) | Open (VS1 = 1) | Open (VS0 = 1) | 0x0B fast read         |

| Open (VS2 = 1) | 1-2 (VS1 = 0)  | Open (VS0 = 1) | 0x03 read              |

| Open (VS2 = 1) | Open (VS1 = 1) | 1-2 (VS0 = 0)  | 0xE8 read array        |

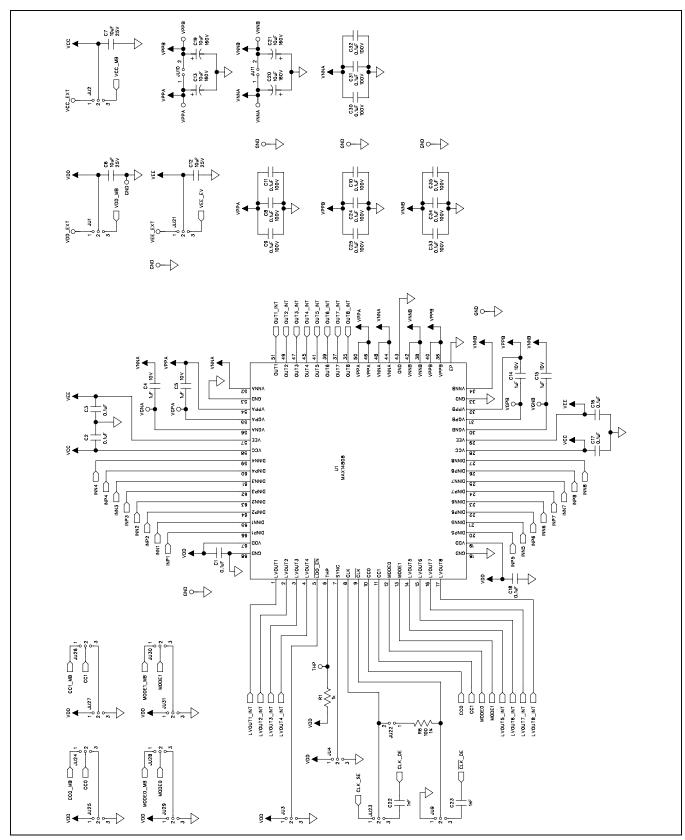

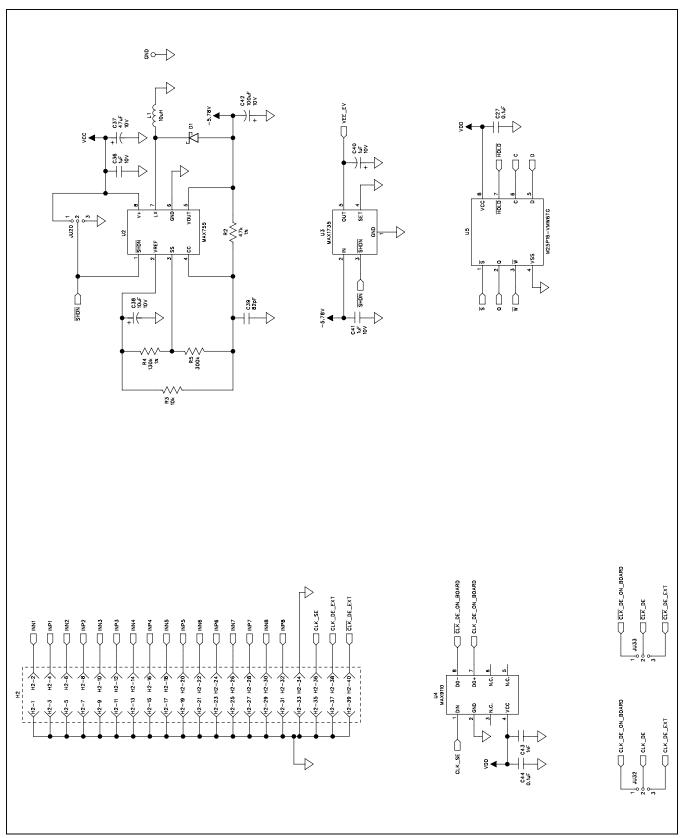

Figure 12a. MAX14808 EV Kit Schematic (Sheet 1 of 3)

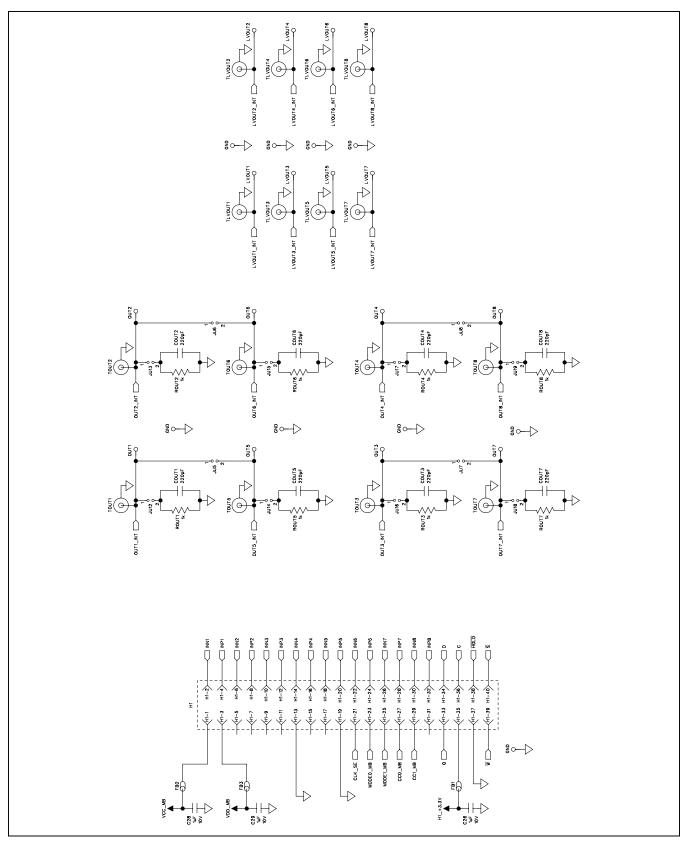

Figure 12b. MAX14808 EV Kit Schematic (Sheet 2 of 3)

Figure 12c. MAX14808 EV Kit Schematic (Sheet 3 of 3)

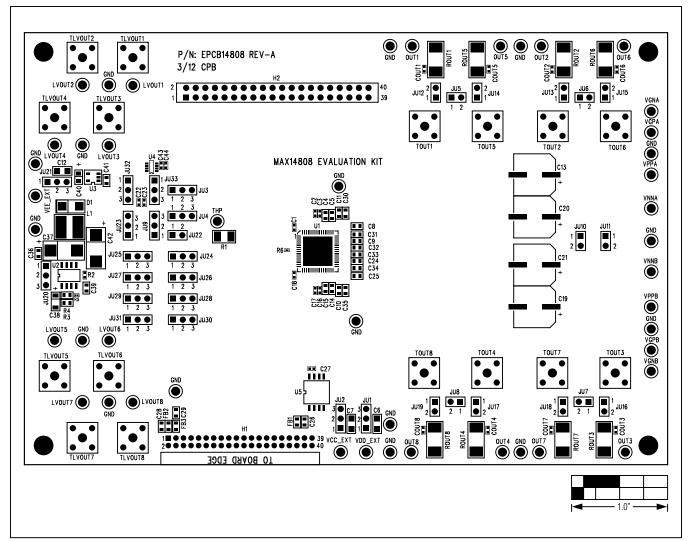

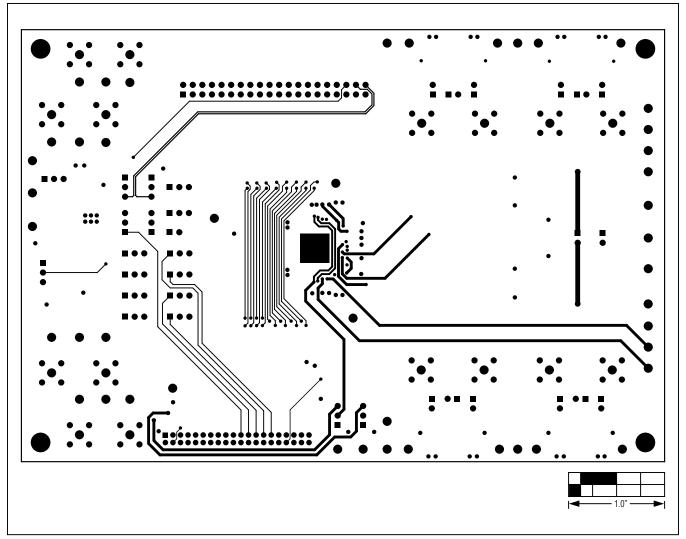

Figure 13. MAX14808 EV Kit Component Placement Guide—Component Side

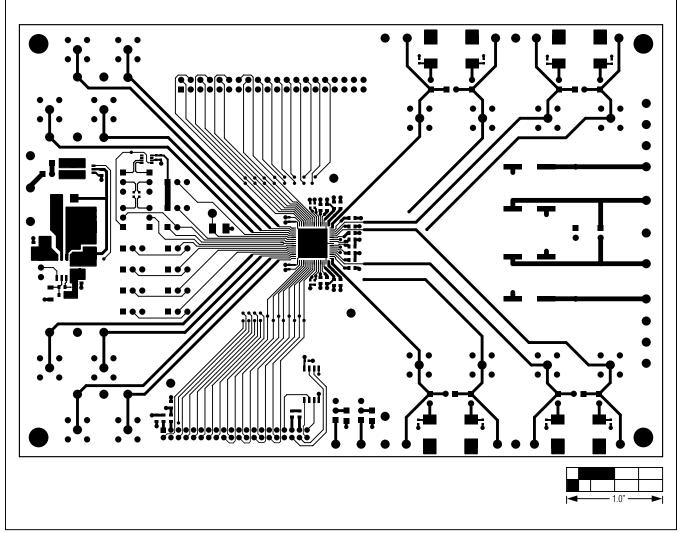

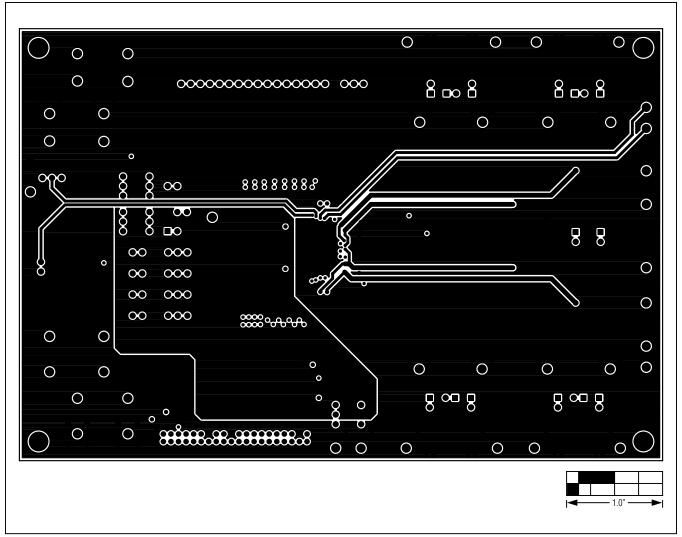

Figure 14. MAX14808 EV Kit PCB Layout—Component Side

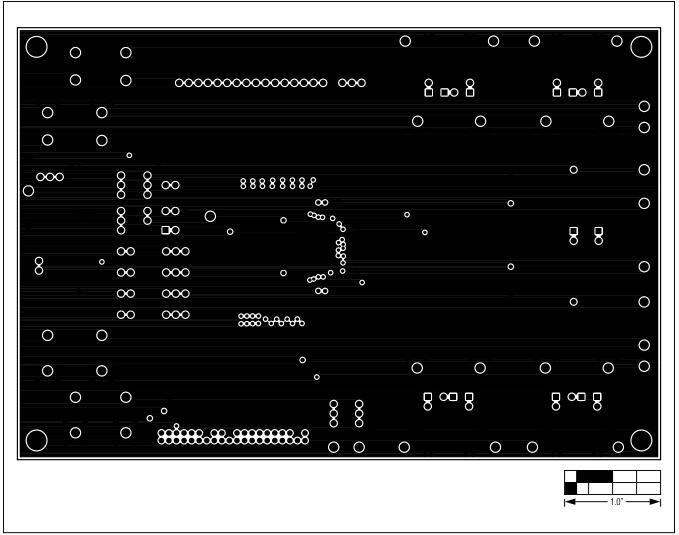

Figure 15. MAX14808 EV Kit PCB Layout—Layer 2 (GND)

Figure 16. MAX14808 EV Kit PCB Layout—Layer 3 (Power)

Figure 17. MAX14808 EV Kit PCB Layout—Solder Side

### **Ordering Information**

| PART           | TYPE      |  |

|----------------|-----------|--|

| MAX14808EVKIT# | EV Kit    |  |

| MAX14808EVSYS# | EV System |  |

#Denotes RoHS compliant.

**Note:** The EV kit software is designed for use with the complete EV system. The EV system includes both the Maxim MAXINT1 interface board and the EV kit. If the customer has their own interface controller, the EV kit board can be purchased without the MAXINT1 board.