#### MAX14882

## **5kV<sub>RMS</sub>** Isolated CAN Transceiver with Integrated Transformer Driver

### **General Description**

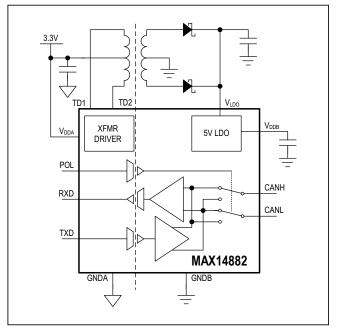

The MAX14882 isolated high-speed CAN transceiver improves communication and safety by integrating galvanic isolation between the CAN-protocol controller-side (TDX, RXD) of the device and the physical wires of the CAN network (CANH, CANL) cable-side/bus-side of the transceiver. Isolation improves communication by breaking ground loops and reduces noise where large differences in ground potentials exists between ports. The MAX14882 provides up to 5000V<sub>RMS</sub> (60s) of galvanic isolation and a continuous working voltage of up to 848V<sub>RMS</sub>, while operating at the maximum high-speed CAN data rate of 1Mbps.

The MAX14882 features additional integrated protection for robust communication. The  $\pm 25$ V receiver input commonmode range exceeds the ISO 11898 specification requirement of -2V to +7V. Additionally, the CANH and CANL IOs are fault tolerant up to  $\pm 54$ V and are protected from electrostatic discharge (ESD) up to  $\pm 15$ kV to GNDB on the bus-side, as specified by the Human Body Model (HBM).

Interfacing with CAN-protocol controllers is simplified by the wide 3.0V to 5.5V supply voltage range ( $V_{DDA}$ ) on the controller-side of the device. The supply voltage range for the CAN bus-side of the device is 4.5V to 5.5V ( $V_{DDB}$ ). An integrated transformer driver and LDO can be used, with an external transformer, to generate the isolated supply for  $V_{DDB}$ .

Field installation and troubleshooting are simplified by the polarity select (POL) input. POL swaps the functions of the CANH and CANL IOs, allowing for simple software correction of cross-wired bus cables in the field.

The MAX14882 operates over the -40°C to +125°C temperature range and is available in a 16-pin wide SOIC (W SOIC) package with 8mm of creepage and clearance.

### **Applications**

- Building Automation

- Industrial Controls

- HVAC

- Switching Gear

### **Benefits and Features**

- Integrated Protection for More Robust Communication

- 5kV<sub>RMS</sub> Withstand Galvanic Isolation (60s)

- ±25V Common Mode Range

- ±54V Fault Protection

- ±15kV ESD (HBM) Protection on Driver Outputs/ Receiver Inputs

- High-Performance Transceiver Enables Flexible Designs

- Wide 3.0V to 5.5V Supply Voltage Range for CAN Controller Interface

- Field Bus Polarity Control (POL)

- Integrated Transformer Driver for Power Transfer to Bus-Side

- · Integrated LDO for Powering CAN Bus-Side

- Safety Regulatory Approvals (Pending)

- UL1577 (Basic Insulation)

- · cUL According to CSA Bulletin 5A

Ordering Information appears at end of data sheet.

## Simplified Block Diagram

### **Absolute Maximum Ratings**

| V <sub>DDA</sub> to GNDA                 | 0.3V to +6V                     | Short-Circuit Duration (RXD to GNDA or \            | DDA)Continuous    |

|------------------------------------------|---------------------------------|-----------------------------------------------------|-------------------|

| V <sub>DDB</sub> to GNDB                 | 0.3V to +6V                     | TD1, TD2 Continuous Current                         | ±1.4A             |

| V <sub>LDO</sub> to GNDB                 | 0.3V to +16V                    | Continuous Power Dissipation (T <sub>A</sub> = +70° | C)                |

| TD1,TD2 to GNDA                          | 0.3V to +12V                    | 16-pin W SOIC (Derate 14.1mW/°C above               | e +70°C) 1126.8mW |

| TXD, POL to GNDA                         | 0.3V to +6V                     | Operating Temperature Range                         | 40°C to +125°C    |

| RXD to GNDA0.3                           | 3V to (V <sub>DDA</sub> + 0.3V) | Junction Temperature                                | +150°C            |

| I.C. to GNDB0.3                          | 3V to (V <sub>DDB</sub> + 0.3V) | Storage Temperature Range                           | 60°C to +150°C    |

| CANH or CANL to GNDB (Continuous)        | 54V to +54V                     | Lead Temperature (soldering, 10s)                   | +300°C            |

| Short-Circuit Duration (CANH to CANL)    | Continuous                      | Soldering Temperature (reflow)                      | +260°C            |

| Short Circuit Duration (CAN to GNDB or V | DDB)Continuous                  |                                                     |                   |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

### Wide 16-SOIC

| W16+10   |

|----------|

| 21-0042  |

| 90-0107  |

|          |

| 107 °C/W |

| 22 °C/W  |

|          |

| 71 °C/W  |

| 23 °C/W  |

|          |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

$(V_{DDA} = 3.0V \text{ to } 5.5V, V_{DDB} = 4.5V \text{ to } 5.5V, POL = GNDA, I.C. = GNDB, T_A = -40^{\circ}C \text{ to } +125^{\circ}C.$  Typical values are at  $V_{DDA} = 3.3V, V_{DDB} = 5V, GNDA = GNDB, and T_A = +25^{\circ}C, unless otherwise noted. (Notes 1, 2) )$

| PARAMETER                                  | SYMBOL           | СО                                       | MIN                     | TYP | MAX | UNITS |    |

|--------------------------------------------|------------------|------------------------------------------|-------------------------|-----|-----|-------|----|

| POWER                                      |                  |                                          |                         |     |     |       |    |

| Controller-Side (A-Side)<br>Voltage Supply | V <sub>DDA</sub> |                                          |                         | 3   |     | 5.5   | V  |

| Bus-Side (B-Side) Voltage<br>Supply        | V <sub>DDB</sub> |                                          |                         | 4.5 |     | 5.5   | V  |

| Controller Side (A-Side)                   |                  | POL = TXD = high<br>or low, RXD          | V <sub>DDA</sub> = 5V   |     | 4.7 | 7.7   |    |

| Supply Current                             | I <sub>DDA</sub> | unconnected,<br>TD1/TD2 uncon-<br>nected | V <sub>DDA</sub> = 3.3V |     | 4.5 | 7.5   | mA |

## **Electrical Characteristics (continued)**

( $V_{DDA}$  = 3.0V to 5.5V,  $V_{DDB}$  = 4.5V to 5.5V, POL =GNDA, I.C. = GNDB,  $T_A$  = -40°C to +125°C. Typical values are at  $V_{DDA}$  = 3.3V,  $V_{DDB}$  = 5V, GNDA = GNDB, and  $T_A$  = +25°C, unless otherwise noted. (Notes 1, 2) )

| PARAMETER                         | SYMBOL              | СО                                         | NDITIONS                                                 | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------|---------------------|--------------------------------------------|----------------------------------------------------------|------|------|------|-------|

|                                   |                     |                                            | TXD = GNDA, R <sub>L</sub> = open                        |      | 9.4  | 15.5 |       |

|                                   |                     |                                            | TXD = GNDA, $R_L = 60\Omega$                             |      | 52   | 76   | 1     |

| Bus-Side (B-Side) Supply          |                     |                                            | TXD = $V_{DDA}$ , $R_L = 60\Omega$                       |      | 8.5  |      | ]     |

| Current                           | I <sub>DDB</sub>    | V <sub>DDB</sub> = 5V                      | TXD = GNDA, CANH<br>shorted to CANL                      |      | 98   | 130  | mA    |

|                                   |                     |                                            | TXD = V <sub>DDA</sub> , CANH<br>shorted to CANL         |      | 8.5  |      |       |

| Controller-Side (A-Side)          |                     |                                            | RXD, TXD, POL                                            |      |      | 1.66 | V     |

| Undervoltage Lockout<br>Threshold | V <sub>UVLOA</sub>  | V <sub>DDA</sub> rising                    | TD1, TD2                                                 |      |      | 2.85 |       |

| Controller-Side (A-Side)          | V                   | \/ falling                                 | RXD, TXD, POL                                            |      | 50   |      | \/    |

| UVLO Hysteresis                   | VUVLOA_HYST         | V <sub>DDA</sub> falling                   | TD1, TD2                                                 |      | 200  |      | mV    |

| Bus-Side (B-Side) Under-          | .,                  | V <sub>DDB</sub> rising                    | ,                                                        |      |      | 4.25 | .,    |

| voltage Lockout Threshold         | V <sub>UVLOB</sub>  | V <sub>DDB</sub> falling                   |                                                          | 3.45 |      |      | V     |

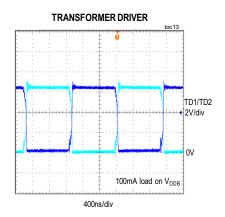

| TRANSFORMER DRIVER                |                     |                                            |                                                          |      |      |      |       |

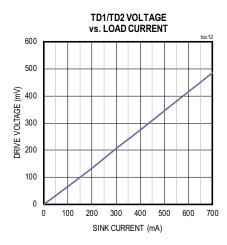

| TD1, TD2 Output Resistance        | RO                  | TD1/TD2 = low, I <sub>TD</sub>             | = 300mA                                                  |      | 0.6  | 1.5  | Ω     |

| TD4 TD0 0                         |                     | 4.5V ≤ V <sub>DDA</sub> ≤ 5.5V             | 1                                                        | 540  | 785  | 1300 | A     |

| TD1, TD2 Current Limit            | I <sub>LIM</sub>    | 3.0V ≤ V <sub>DDA</sub> ≤ 3.6V             | ,                                                        | 485  | 730  | 1170 | mA    |

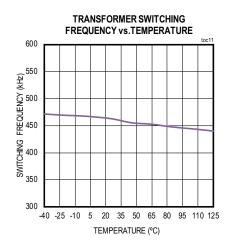

| Switching Frequency               | f <sub>SW</sub>     |                                            | 350                                                      | 450  | 550  | kHz  |       |

| Duty Cycle                        | D                   |                                            |                                                          | 50   |      | %    |       |

| Crossover Dead Time               | t <sub>DEAD</sub>   |                                            |                                                          |      | 50   |      | ns    |

| LDO                               |                     |                                            |                                                          |      |      |      |       |

| LDO Supply Voltage                | V <sub>LDO</sub>    | (Note 3)                                   |                                                          | 4.68 |      | 14   | V     |

| LDO Output Voltage                | $V_{DDB}$           |                                            |                                                          | 4.5  | 5    | 5.5  | V     |

| LDO Current Limit                 |                     |                                            |                                                          |      | 300  |      | mA    |

| Load Regulation                   |                     | V <sub>LDO</sub> = 6V, I <sub>LOAD</sub> = | 20mA to 40mA                                             |      | 0.19 |      | mV/mA |

| Line Regulation                   |                     | $V_{LDO}$ = 6V to 9.5V,                    | I <sub>LOAD</sub> = 20mA                                 |      | 0.12 | 1.8  | mV/V  |

| Dropout Voltage                   |                     | V <sub>LDO</sub> = 4.68V, I <sub>DDB</sub> | = -120mA                                                 |      | 100  | 180  | mV    |

| Load Capacitance                  |                     | Nominal value (Note                        | es 4, 5)                                                 | 1    |      | 10   | μF    |

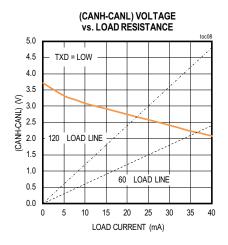

| CAN BUS DRIVER                    |                     |                                            |                                                          |      |      |      |       |

| Dominant Output Voltage           | W                   | TXD = GNDA,                                | CANH, POL = GNDA                                         | 2.75 |      | 4.5  |       |

| High                              | V <sub>CAN_DH</sub> | $50\Omega \le R_L \le \text{to } 65\Omega$ | CANL, POL = V <sub>DDA</sub>                             | 2.75 |      | 4.5  | V     |

| Dominant Output Voltage           | V                   | TXD = GNDA,                                | CANH, POL = GNDA                                         | 0.5  | ,    | 2.25 | \/    |

| Low                               | V <sub>CAN_DL</sub> | $50\Omega \le R_L \le \text{to } 65\Omega$ | CANL, POL = V <sub>DDA</sub>                             | 0.5  |      | 2.25 | V     |

|                                   |                     |                                            | R <sub>CM</sub> = Open                                   | 1.5  |      | 3    |       |

| Dominant Output Voltage,          | · Vob               |                                            | $R_{CM} = 1.25k\Omega$ ,<br>-17V $\leq V_{CM} \leq +17V$ | 1.5  |      | 3    |       |

| Differential                      |                     | Figure 1                                   | $R_{CM} = 1.25k\Omega$ ,<br>$-25V \le V_{CM} \le +25V$   | 1.1  |      | 3    |       |

## **Electrical Characteristics (continued)**

( $V_{DDA}$  = 3.0V to 5.5V,  $V_{DDB}$  = 4.5V to 5.5V, POL =GNDA, I.C. = GNDB,  $T_A$  = -40°C to +125°C. Typical values are at  $V_{DDA}$  = 3.3V,  $V_{DDB}$  = 5V, GNDA = GNDB, and  $T_A$  = +25°C, unless otherwise noted. (Notes 1, 2) )

| PARAMETER                              | SYMBOL               | С                                        | ONDITIONS                                           | MIN                       | TYP  | MAX | UNITS |

|----------------------------------------|----------------------|------------------------------------------|-----------------------------------------------------|---------------------------|------|-----|-------|

| CANH Recessive Output<br>Voltage       | V <sub>CAN_HR</sub>  | TXD = V <sub>DDA</sub> , no I            | oad                                                 | 2                         |      | 3   | V     |

| CANL Recessive Output<br>Voltage       | V <sub>CAN_RL</sub>  | TXD = V <sub>DDA</sub> , no I            | oad                                                 | 2                         |      | 3   | V     |

| Recessive Output Voltage,              |                      | TVD = \/                                 | $R_L = 60\Omega$                                    | -12                       |      | +12 | m\/   |

| Differential                           |                      | $TXD = V_{DDA}$                          | R <sub>L</sub> = Open                               | -50                       |      | +50 | mV    |

| High-Side Short-Circuit                | lauanz u             | TXD = GNDA                               | POL = GNDA,<br>CANH = GNDB                          | 50                        | 75   | 100 | - mA  |

| Current                                | <sup>I</sup> SHORT_H | IND - GNDA                               | POL = V <sub>DDA</sub> ,<br>CANL = GNDB             | 50                        | 75   | 100 |       |

| Low-Side Short-Circuit                 | la                   | TXD = GNDA                               | POL = GNDA,<br>CANL = V <sub>DDB</sub>              | 50                        | 75   | 100 | - mA  |

| Current                                | ISHORT_L             | TAD - GNDA                               | POL = V <sub>DDA</sub> ,<br>CANH = V <sub>DDB</sub> | 50                        | 75   | 100 | IIIA  |

| RECEIVER                               |                      |                                          |                                                     |                           |      |     |       |

| Common Mode Input Range                |                      | CANH or CANL to                          | CANH or CANL to GNDB, RXD output valid              |                           |      |     | V     |

| Differential Input Voltage (Recessive) | $V_{ID\_R}$          | IVCANH - VCANLI,                         | 0.5                                                 |                           |      | V   |       |

| Differential Input Voltage (Dominant)  | V <sub>ID_D</sub>    | IVCANH - VCANLI,                         |                                                     |                           | 0.9  | V   |       |

| Differential Input Hysteresis          |                      |                                          |                                                     |                           | 125  |     | mV    |

| Common-Mode Input<br>Resistance        | R <sub>IN</sub>      | TXD = V <sub>DDA</sub> , R <sub>IN</sub> | = $\Delta V/\Delta I$ , $\Delta V$ = +300mV         | 10                        |      | 50  | kΩ    |

| Differential Input Resistance          | R <sub>DIFF_IN</sub> | TXD = V <sub>DDA</sub> , R <sub>IN</sub> | = ΔV/ΔI, ΔV = +300mV                                | 20                        |      | 100 | kΩ    |

| Input Leakage Current                  | _                    | V <sub>DDB</sub> = GNDB, V               | CANH = V <sub>CANL</sub> = 5V                       |                           |      | 310 | μA    |

| Input Capacitance                      |                      | CANH or CANL to                          | GNDB, T <sub>A</sub> = +25°C (Note 4)               |                           | 14.4 | 20  | pF    |

| Differential Input<br>Capacitance      |                      | CANH to CANL, T                          | A = +25°C (Note 4)                                  |                           | 7.2  | 10  | pF    |

| LOGIC INTERFACE (RXD, TX               | KD, POL)             |                                          |                                                     |                           |      |     |       |

| Input High Voltage                     | V <sub>IH</sub>      | POL, TXD to GNE                          | )A                                                  | 0.7 x<br>V <sub>DDA</sub> |      |     | V     |

| Input Low Voltage                      | V <sub>IL</sub>      | POL, TXD to GNDA                         |                                                     |                           |      | 0.8 | V     |

| Input Hysteresis                       | V <sub>HYS</sub>     |                                          |                                                     |                           | 220  |     | mV    |

| Output High Voltage                    | V <sub>OH</sub>      | RXD, I <sub>OUT</sub> = -4mA             |                                                     | V <sub>DDA</sub> - 0.4    |      |     | V     |

| Output Low Voltage                     | V <sub>OL</sub>      | RXD, I <sub>OUT</sub> = 4mA              |                                                     |                           | 0.4  | V   |       |

| Input Pullup Current                   | I <sub>PU</sub>      | TXD                                      | -10                                                 | -4.5                      | -1.5 | μA  |       |

| Input Pulldown Current                 | I <sub>PD</sub>      | POL                                      |                                                     | 1.5                       | 4.5  | 10  | μA    |

| Input Capacitance                      | C <sub>IN</sub>      |                                          |                                                     |                           | 2    |     | pF    |

## **Electrical Characteristics (continued)**

( $V_{DDA}$  = 3.0V to 5.5V,  $V_{DDB}$  = 4.5V to 5.5V, POL =GNDA, I.C. = GNDB,  $T_A$  = -40°C to +125°C. Typical values are at  $V_{DDA}$  = 3.3V,  $V_{DDB}$  = 5V, GNDA = GNDB, and  $T_A$  = +25°C, unless otherwise noted. (Notes 1, 2) )

| PARAMETER                                                 | SYMBOL                  | CO                                                                      | NDITIONS                                                                  | MIN  | TYP  | MAX              | UNITS          |

|-----------------------------------------------------------|-------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------|------|------|------------------|----------------|

| PROTECTION                                                |                         |                                                                         |                                                                           |      | -    | ,                |                |

| Fault Protection Range                                    |                         | CANH, CANL to GN                                                        | IDB                                                                       | -54  |      | +54              | V              |

|                                                           |                         | IEC 61000-4-2 Air-0                                                     |                                                                           | ±10  |      |                  |                |

| ESD Protection (CANH and CANL to GNDB)                    |                         | IEC 61000-4-2 Contact Discharge                                         |                                                                           |      | ±5   |                  | kV             |

| (CAINH and CAINE to GINDB)                                |                         | Human Body Model                                                        | (HBM)                                                                     |      | ±15  |                  | 1              |

|                                                           |                         | IEC 61000-4-2 Con                                                       | tact Discharge                                                            |      | ±3   |                  |                |

| ESD Protection<br>(CANH and CANL to GNDA)                 |                         | IEC 61000-4-2 Air G<br>470pF capacitor cor<br>and GNDB                  | Gap Discharge.<br>nnected between GNDA                                    |      | ±10  |                  | kV             |

| ESD Protection<br>(All Other Pins)                        |                         | Human Body Model                                                        | (HBM)                                                                     |      | ±2   |                  | kV             |

| Thermal Shutdown                                          | T <sub>SHDN</sub>       | Junction temperatur                                                     | e rising                                                                  |      | +160 |                  | °C             |

| Thermal Shutdown Hysteresis                               | T <sub>SH_HYST</sub>    |                                                                         |                                                                           |      | 13   |                  | °C             |

| SWITCHING CHARACTERIS                                     | TICS                    |                                                                         |                                                                           |      |      |                  |                |

| Common-Mode Transient<br>Immunity                         | CMTI                    | (Note 6)                                                                |                                                                           |      | 35   |                  | kV/µs          |

| Driver Rise Time                                          | $t_{R}$                 | R <sub>CM</sub> is open, R <sub>L</sub> = 6                             |                                                                           |      | 23   | ns               |                |

| Driver Fall Time                                          | t <sub>F</sub>          | R <sub>CM</sub> is open, R <sub>L</sub> = 6<br>10% of transition on     |                                                                           |      | 31   | ns               |                |

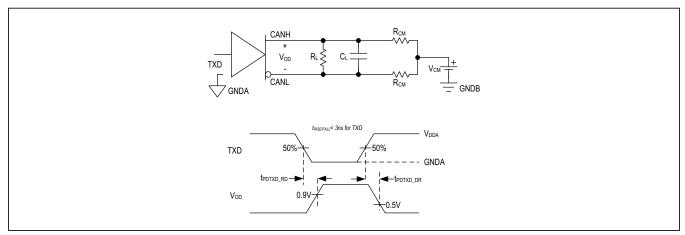

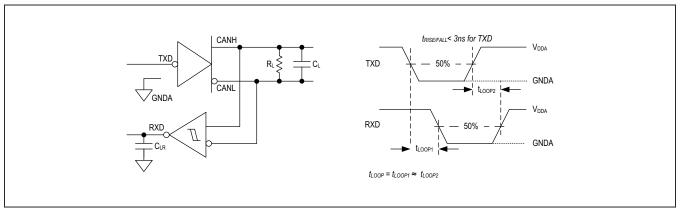

| TXD to RXD Loop Delay                                     | t <sub>LOOP</sub>       | Dominant to recession dominant, R <sub>L</sub> = 60Ω Figure 2           | ive and recessive to<br>, C <sub>L</sub> = 100pF, C <sub>LR</sub> = 15pF, |      |      | 215              | ns             |

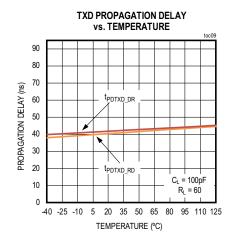

|                                                           | t <sub>PDTXD_RD</sub> , | R <sub>CM</sub> is open, R <sub>L</sub> =                               | Recessive to dominant                                                     |      |      | 80               |                |

| TXD Propagation Delay                                     | t <sub>PDTXD_DR</sub>   | $60\Omega$ , C <sub>L</sub> = 100pF,<br>Figure 1                        | Dominant to recessive                                                     |      |      | 80               | ns             |

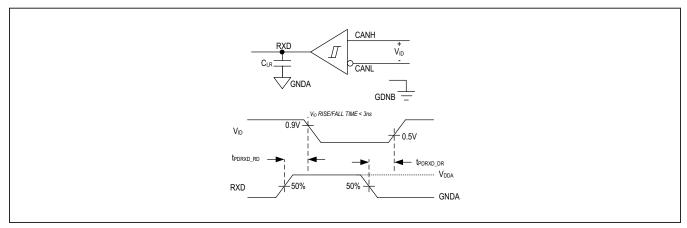

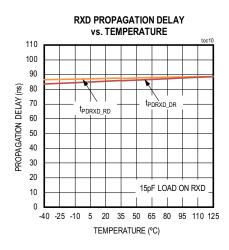

| RXD Propagation Delay                                     | t <sub>PDRXD</sub> RD,  | $C_{LR} = 15pF$ ,                                                       | Recessive to dominant                                                     |      |      | 135              | ns             |

| TOOD I Topagation Delay                                   | t <sub>PDRXD_DR</sub>   | Figure 3                                                                | Dominant to recessive                                                     |      |      | 135              | 113            |

| TXD Dominant Timeout                                      | t <sub>DOM</sub>        | (Note 7)                                                                |                                                                           | 1.4  | ·    | 4.8              | ms             |

| Undervoltage Threshold Detection Time to Normal Operation |                         |                                                                         |                                                                           |      |      | 120              | μs             |

| INSULATION CHARACTERIS                                    | STICS                   |                                                                         |                                                                           |      |      |                  |                |

| Partial Discharge Voltage                                 | $V_{PR}$                | Method B1 = V <sub>IORM</sub> x 1.875 (t = 1s, partial discharge < 5pC) |                                                                           |      | 2250 |                  | V <sub>P</sub> |

| Maximum Repetitive Peak Isolation Voltage                 | V <sub>IORM</sub>       | (Note 8)                                                                |                                                                           | 1200 |      | V <sub>P</sub>   |                |

| Maximum Working Isolation Voltage                         | V <sub>IOWM</sub>       | (Note 8)                                                                |                                                                           | 848  |      | V <sub>RMS</sub> |                |

| Maximum Transient Isolation Voltage                       | V <sub>IOTM</sub>       | t = 1s                                                                  |                                                                           |      | 8400 |                  | V <sub>P</sub> |

### **Electrical Characteristics (continued)**

$(V_{DDA} = 3.0V \text{ to } 5.5V, V_{DDB} = 4.5V \text{ to } 5.5V, POL = GNDA, I.C. = GNDB, T_A = -40^{\circ}C \text{ to } +125^{\circ}C.$  Typical values are at  $V_{DDA} = 3.3V$ ,  $V_{DDB}$  = 5V, GNDA = GNDB, and  $T_A$  = +25°C, unless otherwise noted. (Notes 1, 2)

| PARAMETER                                   | SYMBOL            | CONDITIONS                                      | MIN TYP MAX | UNITS            |

|---------------------------------------------|-------------------|-------------------------------------------------|-------------|------------------|

| Maximum Withstand Isolation Voltage         | V <sub>ISO</sub>  | t = 60s, f = 60Hz (Notes 8, 9)                  | 5000        | V <sub>RMS</sub> |

| Maximum Surge Isolation<br>Voltage          | V <sub>IOSM</sub> | Basic Insulation                                | 10          | kV               |

| Insulation Resistance                       | R <sub>S</sub>    | T <sub>A</sub> = +150°C, V <sub>IO</sub> = 500V | >109        | Ω                |

| Barrier Capacitance<br>Input-to-Output      | CIO               | f = 1MHz                                        | 2           | pF               |

| Minimum Creepage<br>Distance                | CPG               | Wide SOIC                                       | 8           | mm               |

| Minimum Clearance<br>Distance               | CLR               | Wide SOIC                                       | 8           | mm               |

| Internal Clearance                          |                   | Distance through insulation                     | 0.015       | mm               |

| Comparative Tracking<br>Resistance Index    | СТІ               | Material Group II (IEC 60112)                   | 575         |                  |

| Climatic Category                           |                   |                                                 | 40/125/21   |                  |

| Pollution Degree<br>(DIN VDE 0110, Table 1) |                   |                                                 | 2           |                  |

- Note 1: All devices 100% production tested at  $T_A = +25$ °C. Specifications over temperature are guaranteed by design. Specifications marked "GBD" are guaranteed by design and not production tested.

- Note 2: All currents into the device are positive. All currents out of the device are negative. All voltages referenced to their respective ground (GNDA or GNDB), unless otherwise noted.

- Note 3: The maximum V<sub>LDO</sub> voltage listed in the *Electrical Characteristics* table indicates the voltage capability of the MAX14882. Ambient temperature and power dissipation requirements of a given circuit may limit the allowable maximum V<sub>I DO</sub> to a lower value during operation.

- Note 4: Not production tested. Guaranteed by design (GBD) and characterization.

- Note 5: Capacitance range for a stable output. Values are nominal and allow for normal capacitor tolerance.

- Note 6: CMTI is the maximum sustainable common-mode voltage slew rate while maintaining the correct output states. CMTI applies to both rising and falling common-mode voltage edges. Tested with the transient generator connected between GNDA and GNDB.

- Note 7: The dominant timeout feature releases the bus when TXD is held low longer than t<sub>DOM</sub>. CAN protocol guarantees a maximum of 11 successive dominant bits in any transmission. The minimum data rate allowed by the dominant timeout, then, is 11/t<sub>DOM</sub>(min)

- Note 8:  $V_{IORM}$ ,  $V_{IOWM}$ , and  $V_{ISO}$  are defined by the IEC 60747-5-5 standard Note 9: Product is qualified  $V_{ISO}$  for 60 seconds. 100% production tested at 120% of  $V_{ISO}$  for 1 second.

## **Test Circuits and Timing Diagrams**

Figure 1. Transmitter Test Circuit and Timing Diagram

Figure 2. Loop Delay Timing Diagram

Figure 3. Receiver Timing Diagram

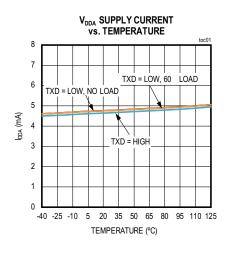

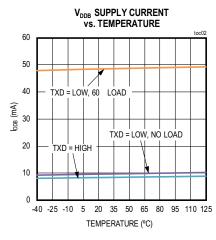

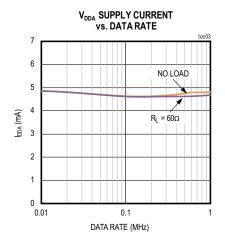

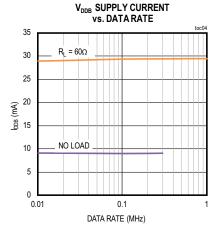

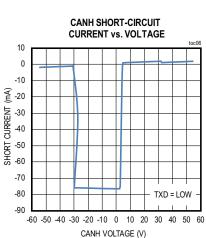

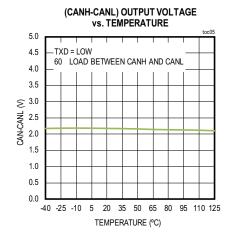

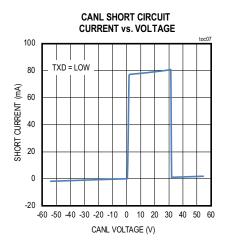

## **Typical Operating Characteristics**

$V_{DDA}$  = 3.3V to GNDA,  $60\Omega$  load between CANH and CANL, GNDA = GNDB,  $T_A$  = 25°C, unless otherwise noted.

## **Typical Operating Characteristics (continued)**

$V_{DDA}$  = 3.3V to GNDA,  $60\Omega$  load between CANH and CANL, GNDA = GNDB,  $T_A$  = 25°C, unless otherwise noted.

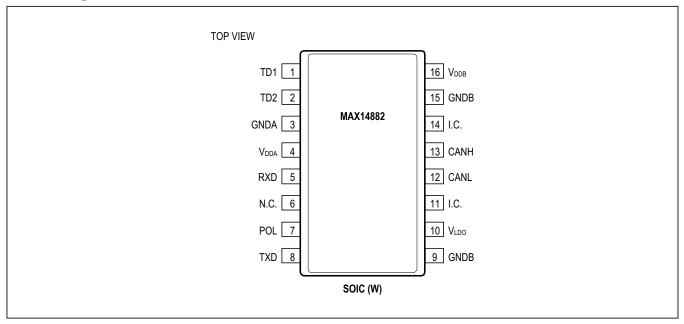

## **Pin Configuration**

## **Pin Description**

| PIN   | NAME             | FUNCTION                                                                                                                                                                                                                                                                        | REF<br>SUPPLY | TYPE              |

|-------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------|

| CONTR | OLLER-S          | DE (A-SIDE)                                                                                                                                                                                                                                                                     |               |                   |

| 1     | TD1              | Transformer Driver Output 1                                                                                                                                                                                                                                                     | GNDA          | Analog            |

| 2     | TD2              | Transformer Driver Output 2                                                                                                                                                                                                                                                     | GNDA          | Analog            |

| 3     | GNDA             | Controller-Side/A-Side Ground. GNDA is the ground reference for POL, TXD, and RXD.                                                                                                                                                                                              | _             | Ground            |

| 4     | V <sub>DDA</sub> | Power Supply Input for the Controller-Side/A-Side. Bypass $V_{DDA}$ to GNDA with both a 0.1 $\mu$ F and a 1 $\mu$ F capacitor as close to the device as possible.                                                                                                               | GNDA          | Power             |

| 5     | RXD              | Receiver Output. RXD is high when the bus is in the recessive state. RXD is low when the bus is in the dominant state.                                                                                                                                                          | GNDA          | Digital<br>Output |

| 6     | N.C.             | No Connection. Not internally connected. Connect to GNDA, V <sub>DDA</sub> , or leave unconnected.                                                                                                                                                                              | GNDA          |                   |

| 7     | POL              | Polarity Set Input. Drive POL low for normal CANH, CANL operation (CANH is high and CANL is low when TXD is low). Drive POL high to swap the functions of CANH and CANL (CANH is low and CANL is high when TXD is low). See <a href="Table 1">Table 1</a> for more information. | GNDA          | Digital<br>Input  |

| 8     | TXD              | Transmit Data Input. CANH and CANL are in the dominant state when TXD is low. CANH and CANL are in the recessive state when TXD is high.                                                                                                                                        | GNDA          | Digital<br>Input  |

### **Pin Description (continued)**

| PIN    | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                 | REF<br>SUPPLY | TYPE                |

|--------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------|

| CAN BU | IS-SIDE (I       | B-SIDE)                                                                                                                                                                                                                                                                                                                                                                                  |               |                     |

| 9, 15  | GNDB             | Bus-Side/B-Side Ground. GNDB is the ground reference for V <sub>LDO</sub> , V <sub>DDB</sub> , CANH, and CANL.                                                                                                                                                                                                                                                                           | _             | Ground              |

| 10     | V <sub>LDO</sub> | LDO Power Input. Connect a minimum voltage of 4.68V to $V_{LDO}$ to power the bus-side of the transceiver. Bypass $V_{LDO}$ to GNDB with both 0.1 $\mu$ F and 1 $\mu$ F capacitors as close as possible to the device. To disable the internal LDO, leave $V_{LDO}$ unconnected or connect to GNDB.                                                                                      | GNDB          | Power<br>Input      |

| 11, 14 | I.C.             | Internally Connected. Connect to GNDB.                                                                                                                                                                                                                                                                                                                                                   | GNDB          |                     |

| 12     | CANL             | Low-Level CAN Differential Bus Line                                                                                                                                                                                                                                                                                                                                                      | GNDB          | Differential I/O    |

| 13     | CANH             | High-Level CAN Differential Bus Line                                                                                                                                                                                                                                                                                                                                                     | GNDB          | Differential<br>I/O |

| 16     | V <sub>DDB</sub> | Bus-Side Power Input/LDO Power Output. Bypass $V_{DDB}$ to GNDB with both $0.1\mu F$ and $1\mu F$ capacitors as close as possible to the device. $V_{DDB}$ is the output of the internal LDO when power is applied to $V_{LDO}$ . When the internal LDO is not used ( $V_{LDO}$ is unconnected or connected to GNDB), $V_{DDB}$ is the positive supply input for the bus-side of the IC. | GNDB          | Power               |

### **Detailed Description**

The MAX14882 isolated controller area network (CAN) transceiver provides 5000V<sub>RMS</sub> (60s) of galvanic isolation between the cable-side (B-side) of the transceiver and the controller-side (A-side). This device allows up to 1Mbps communication across the isolation barrier when a large potential exists between grounds on each side of the barrier. CANH and CANL outputs are short-circuit current-limited and are protected against excessive power dissipation by thermal shutdown circuitry that places the driver outputs in a high-impedance state.

#### Isolation

Both data and power can be transmitted across the isolation barrier. Data isolation is achieved using integrated capacitive isolation that allows data transmission between the controller-side and the cable-side of the transceiver.

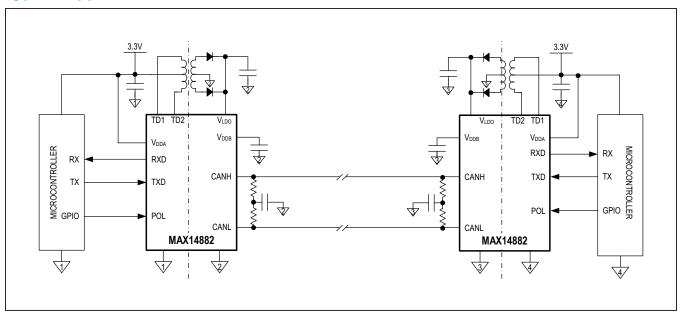

To achieve power isolation, the MAX14882 features an integrated transformer driver to drive an external center-tapped transformer, allowing the transfer of operating power from the controller-side, across the isolation barrier, to the cable-side. Connect the primary side of the external transformer to the MAX14882's transformer driver outputs (TD1 and TD2).

#### **Fault Protection**

The MAX14882 features ±54V fault protection on the CANH and CANL bus lines. When CANH or CANL is pulled above +30V (typ) or below -30V (typ), the I/O is set to high-impedance. This wide fault protection range simplifies selecting external TVS components for surge protection.

#### **Transmitter**

The transmitter converts a single-ended input signal (TXD) from the CAN controller to differential outputs for the bus lines (CANH, CANL). The truth table for the transmitter and receiver is given in Table 1.

#### **Transmitter Dominant Timeout**

The MAX14882 features a transmitter-dominant timeout ( $t_{DOM}$ ) that prevents erroneous CAN controllers from clamping the bus to a dominant level by maintaining a continuous low TXD signal. When TXD remains in the dominant state (low) for greater than  $t_{DOM}$ , the transmitter is disabled, releasing the bus to a recessive state (Table 1).

After a dominant timeout fault, normal transmitter function is re-enabled on the rising edge of a TXD. The transmitter-dominant timeout limits the minimum possible data rate to 7.86kbps for standard CAN protocol.

#### Transmitter and Receiver Functionality When Not Connected to the Bus

Table 1. Transmitter and Receiver Functionality when Not Connected to the Bus

| POL            | TXD | TXD LOW TIME       | CANH                | CANL                | BUS STATE | RXD |

|----------------|-----|--------------------|---------------------|---------------------|-----------|-----|

| L              | L   | < t <sub>DOM</sub> | Н                   | L                   | Dominant  | L   |

| L              | L   | ≥ t <sub>DOM</sub> | V <sub>DDB</sub> /2 | V <sub>DDB</sub> /2 | Recessive | Н   |

| L              | Н   | X                  | V <sub>DDB</sub> /2 | V <sub>DDB</sub> /2 | Recessive | Н   |

| Н              | L   | < t <sub>DOM</sub> | L                   | Н                   | Dominant  | L   |

| Н              | L   | ≥ t <sub>DOM</sub> | V <sub>DDB</sub> /2 | V <sub>DDB</sub> /2 | Recessive | Н   |

| Н              | Н   | X                  | V <sub>DDB</sub> /2 | V <sub>DDB</sub> /2 | Recessive | Н   |

| X = Don't care |     |                    |                     |                     |           |     |

### **Driver Output Protection**

The MAX14882 features integrated circuitry to protect the transmitter output stage against a short-circuit to a positive or negative voltage by limiting the driver current. The transmitter returns to normal operation once the short is removed.

Thermal shutdown further protects the transceiver from excessive temperatures that may result from a short by setting the transmitter outputs to high impedance when the junction temperature exceeds +160°C (typ). The transmitter returns to normal operation when the junction temperature falls below the thermal shutdown hysteresis.

### Receiver

The receiver reads the differential input from the bus (CANH, CANL) and transfers this data as a single-ended output (RXD) to the CAN controller. During normal operation, a comparator senses the difference between CANH and CANL,  $V_{DIFF} = |V_{CANH} - V_{CANL}|$ , with respect to an internal threshold of 0.7V (typ). If  $V_{DIFF} > 0.9$ V, a logic-low is present on RXD. If  $V_{DIFF} < 0.5$ V, a logic-high is present.

The CANH and CANL common-mode range is ±25V. RXD is logic-high when CANH and CANL are shorted or terminated and undriven.

#### **Transformer Driver**

### **Overcurrent Limiting**

The MAX14882 features overcurrent limiting to protect the integrated transformer driver from excessive currents when charging large capacitive loads or driving into shortcircuits. Current limiting is achieved in two stages: internal circuitry monitors the output current and detects when the peak current rises above 1.2A.

When the 1.2A threshold is exceeded, internal circuitry reduces the output current to the 730mA current-limit. The MAX14882 monitor the driver current on a cycle-by-cycle basis and limit the current until the short is removed.

The transformer driver on the MAX14882 can dissipate large amounts of power during overcurrent limiting, causing the IC to enter thermal shutdown. When the junction temperature exceeds the thermal shutdown threshold, the TD1 and TD2 driver outputs are disabled. The driver resumes normal operation when the temperature falls below the thermal shutdown temperature minus the hysteresis.

### MAX14882

## with Integrated Transformer Driver

#### **Transformer Selection**

The integrated push-pull transformer driver allows the transmission of operating power from the logic side, across the isolation barrier, to the isolated field side of the device. The 450kHz (typ) transformer driver operates with center-tapped primary transformers. Select a transformer with an ET product greater than or equal to the ET of the driver to ensure that the transformer does not enter saturation. E is the voltage applied to the transformer and T is the maximum time it is applied during any one cycle. Calculate the minimum ET product for the transformer primary as:

$$ET = V_{MAX}/(2 \times f_{MIN})$$

where  $V_{MAX}$  is the worst-case maximum supply voltage on  $V_{DDA}$  and  $f_{MIN}$  is the minimum frequency at that supply voltage. For example, using 5.5V and 350kHz, the required minimum ET product is 7.9V $\mu$ s.

<u>Table 2</u> shows a list of recommended transformers to use with the MAX14882.

### **Applications Information**

#### **Reduced EMI and Reflections**

In multidrop CAN applications, it is important to maintain a single linear bus, of uniform impedance, that is properly terminated at each end. Do not use a star configuration.

5kV<sub>RMS</sub> Isolated CAN Transceiver

Any deviation from the end-to-end wiring scheme creates a stub. High-speed data edges on a stub can create reflections back down the bus and can cause data errors, by eroding the noise margin of the system. Although stubs are unavoidable in a multidrop system, care should be taken to keep these stubs as short as possible, especially when operating with high data rates.

### **Recommended Transformers**

**Table 2. Recommended Transformers**

| MANUFACTURER | PART<br>NUMBER | APPLICATION | TURNS<br>RATIO | ISOLATION<br>(V <sub>RMS</sub> ) | OPERATING<br>TEMP | ET CONSTANT<br>(V x µs, MIN) | OPERATING<br>CURRENT<br>(mA) | DIMENSIONS<br>(L x W x H) (mm) |

|--------------|----------------|-------------|----------------|----------------------------------|-------------------|------------------------------|------------------------------|--------------------------------|

| Wurth        | 750315225      | 5V to 5V    | 1CT:1.1CT      | 2750                             |                   | 9.44                         | 200                          | 6.73 x 7.14 x 4.19             |

| Wurth        | 750315226      | 5V to 5V    | 1CT:1.3CT      | 2750                             | -40°C to          | 9.44                         | 200                          | 6.73 x 7.14 x 4.19             |

| Wurth        | 750315227      | 3.3V to 5V  | 1CT:1.7CT      | 2750                             | +125°C            | 9.44                         | 200                          | 6.73 x 7.14 x 4.19             |

| Wurth        | 750315228      | 3.3V to 5V  | 1CT:2CT        | 2750                             |                   | 9.44                         | 160                          | 6.73 x 7.14 x 4.19             |

| Wurth        | 750315229      | 5V to 5V    | 1CT:1.13CT     | 5000                             | -40°C to          | 10.7                         | 200                          | 9.14 x 8.00 x 7.62             |

| Wurth        | 750315230      | 5V to 5V    | 1CT:1.38CT     | 5000                             | +125°C            | 10.7                         | 150                          | 9.14 x 8.00 x 7.62             |

## **Typical Application Circuit**

## **Ordering Information**

| PART          | ISOLATION<br>RATING | V <sub>DDA</sub> SUPPLY | POL | V <sub>DDB</sub> LDO<br>VOLTAGE | TRANSFORMER<br>DRIVER | PACKAGE     |

|---------------|---------------------|-------------------------|-----|---------------------------------|-----------------------|-------------|

| MAX14882AWE+  | 5kV <sub>RMS</sub>  | 3.0V to 5.5V            | YES | 5V                              | YES                   | 16 SOIC (W) |

| MAX14882AWE+T | 5kV <sub>RMS</sub>  | 3.0V to 5.5V            | YES | 5V                              | YES                   | 16 SOIC (W) |

<sup>+</sup>Denotes a lead (Pb)-free/RoHS-compliant package

T = Tape and Reel