#### MAX14915

# Compact Industrial Octal High-Side Switch with Diagnostics

# **General Description**

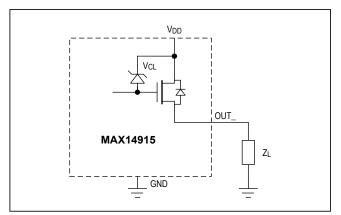

The MAX14915 has eight high-side switches specified to deliver up to 700mA continuous current. The high-side switches have on-resistance of  $250m\Omega$  (max) at  $125^{\circ}\text{C}$  ambient temperature.

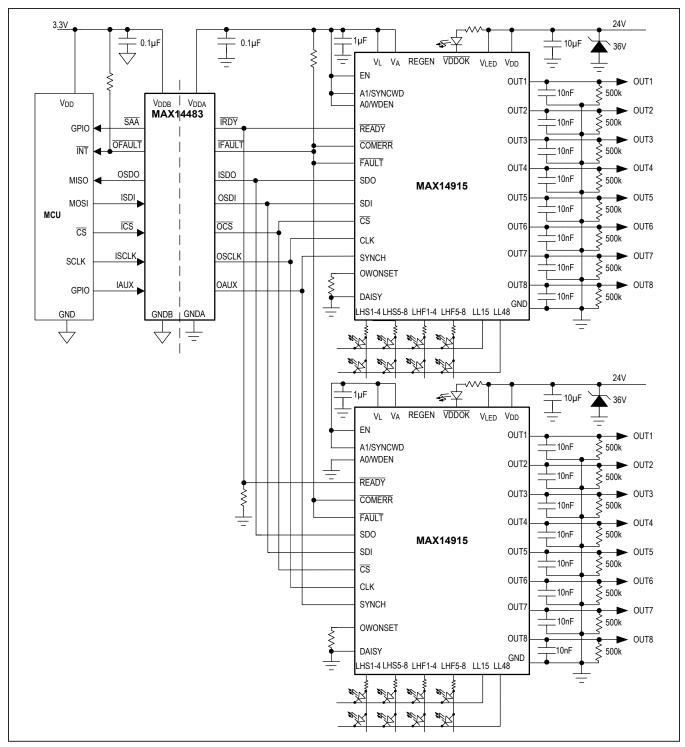

The SPI interface has a built-in chip addressing decoder, allowing communication with multiple MAX14915s utilizing a common SPI chip select (CS).

The SPI interface provides flexibility for global and per-channel configuration and diagnostic, including over and undervoltage detection, open wire/load detection, overload and current limiting reporting, thermal conditions reporting, and more.

Open load detection detects both open-wire/open-load conditions with switches in the on and off states. LED drivers provide indication of per-channel fault, status, and supply undervoltage conditions. Internal active clamps allow for fast turn-off of inductive loads.

Integrated line-to-ground and line-to-line surge protection only requires a TVS on  $V_{DD}$ .

The MAX14915 is available in a compact 48-pin 6mm x 6mm QFN package.

# **Applications**

- Industrial Digital Outputs

- PLC Systems

#### **Benefits and Features**

- Robustness and Smart Diagnostics

- 65V Absolute Maximum Supply Range

- Internal Clamps for Fast Inductive Load Demagnetization

- · CRC Error Checking on the SPI Interface

- · Watchdog Timer for Diagnostics Checking

- · Open-Wire Detection, Both with Switches On and Off

- Undervoltage Detection with UVLO

- Loss of V<sub>DD</sub> or GND Protection

- · Thermal Shutdown Protection

- Integrated ±1kV/42Ω IEC61000-4-5 Surge Protection

- -40°C to +125°C Operating Ambient Temperature

- Reduces Power and Heat Dissipation

- 250mΩ (Max) On-Resistance at T<sub>A</sub> = 125°C

- 2mA (typ) Supply Current

- · Accurate Output Current Limiting

- Flexibility

- · Addressable SPI Interface Reduces Isolation Cost

- SYNCH Input for Simultaneous Update of Switches

- LED Driver Matrix for 16 LEDs, Powered by 24V, 5V. or 3.3V

- Flexible Logic Voltage Interface from 2.5V to 5.5V

- Compact 6mm x 6mm QFN Package

Ordering Information appears at end of data sheet.

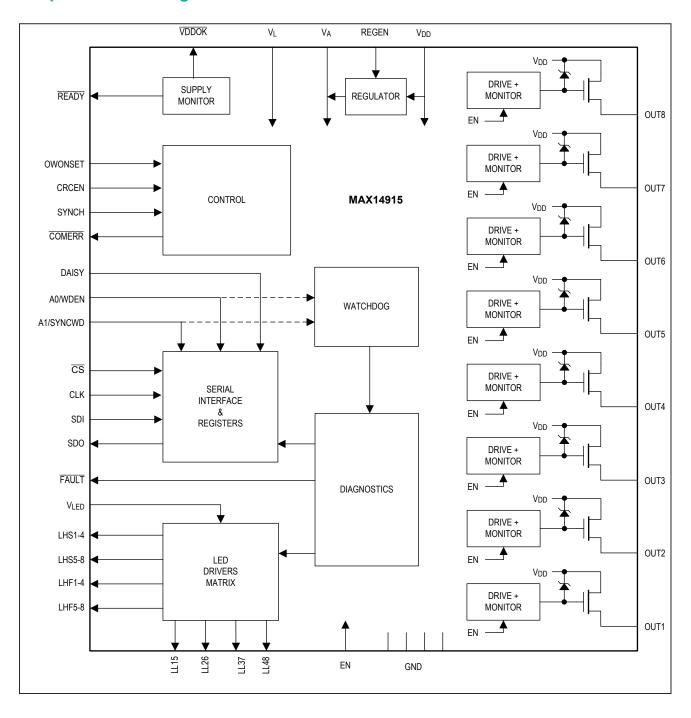

# **Simplified Block Diagram**

# MAX14915

# Compact Industrial Octal High-Side Switch with Diagnostics

# **Absolute Maximum Ratings**

| V <sub>DD</sub> 0.3V to +65V                           | LH_, LL_, VDDOK0.3V to (V <sub>LED</sub> + 0.3)V |

|--------------------------------------------------------|--------------------------------------------------|

| OUT(V <sub>DD</sub> - 49)V to (V <sub>DD</sub> + 0.3)V | OUT_ Load CurrentInternally Limited              |

| V <sub>A</sub> , V <sub>L</sub> 0.3V to +6V            | Continuous Power Dissipation                     |

| SDO, READY, COMERR0.3V to (V <sub>L</sub> + 0.3)V      | (Multilayer Board) (T <sub>A</sub> = +70°C,      |

| REGEN, OWONSET0.3V to +6V                              | derate 50mW/°C above +70°C)3900mW                |

| FAULT0.3V to 6V                                        | Operating Temperature Range40°C to +125°C        |

| SDI, CS, CLK, EN, ADDO/WDEN, ADD1, SYNCH, CRCEN,       | Junction Temperature+150°C                       |

| DAISY0.3V to 6V                                        | Storage Temperature Range65°C to +150°C          |

| V <sub>LED</sub> 0.3V to +70V                          | Soldering Temperature (reflow)260°C              |

Note 1: All voltages relative to GND.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **Package Information**

# Flip Chip QFN

| Package Code                           | F486A6F-1         |  |  |  |

|----------------------------------------|-------------------|--|--|--|

| Outline Number                         | 21-100232         |  |  |  |

| Outline Number                         | 21-100232         |  |  |  |

| Land Pattern Number                    | <u>90-100077</u>  |  |  |  |

| Thermal Resistance, Four-Layer Board:  |                   |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 20.5°C/W          |  |  |  |

| Junction to Case $(\theta_{JC})$       | 0.39°C/W (bottom) |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

# **Electrical Characteristics**

$(V_{DD} = +10 \text{V to } +36 \text{V}, V_{LED} = +3.0 \text{V to } 36 \text{V}, V_{A} = +3.0 \text{V to } +5.5 \text{V}, V_{L} = +2.5 \text{V to } +5.5 \text{V}, T_{A} = -40 ^{\circ}\text{C} \text{ to } +125 ^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{DD} = V_{LED} = 24 \text{V}, V_{A} = 3.3 \text{V}, T_{A} = +25 ^{\circ}\text{C}.)$  (Note 2)

| PARAMETER                                         | SYMBOL                      | CONDITIONS                                                                                  | MIN  | TYP  | MAX  | UNITS |

|---------------------------------------------------|-----------------------------|---------------------------------------------------------------------------------------------|------|------|------|-------|

| DC CHARACTERIST                                   | ICS/SUPPLY                  |                                                                                             |      |      |      |       |

| V <sub>DD</sub> Supply Voltage                    | V <sub>DD</sub>             |                                                                                             | 10   |      | 36   | V     |

| V <sub>DD</sub> Supply Current                    | I <sub>DD</sub>             | EN = high, OUT_ switches on, no load, V <sub>A</sub> and V <sub>L</sub> supplied externally |      | 2    | 3    | mA    |

| 117                                               |                             | EN = low                                                                                    |      | 3    |      |       |

| V <sub>DD</sub> UVLO Rise<br>Threshold            | V <sub>DD_UVLO_R</sub>      | V <sub>DD</sub> rising                                                                      |      |      | 9.6  | V     |

| V <sub>DD</sub> UVLO Fall<br>Threshold            | V <sub>DD_UVLO_F</sub>      | V <sub>DD</sub> falling, OUT_ disabled, VddUvlo bit set                                     | 7.9  |      |      | V     |

| V <sub>DD</sub> UVLO<br>Hysteresis                | V <sub>DD_UVLO_H</sub>      |                                                                                             |      | 0.35 |      | V     |

| V <sub>DD</sub> Warn Rise<br>Threshold            | V <sub>DD</sub> _<br>WARN_R | V <sub>DD</sub> rising                                                                      |      |      | 14   | V     |

| V <sub>DD</sub> Warn Fall<br>Threshold            | V <sub>DD_WARN_F</sub>      | V <sub>DD</sub> falling, VddWarn bit set, <del>VDDOK</del> pin set HiZ                      | 12   |      |      | V     |

| V <sub>DD</sub> Warn<br>Hysteresis                | V <sub>DD</sub> _<br>WARN_H |                                                                                             |      | 0.4  |      | V     |

| V <sub>DD</sub> Good Rise<br>Threshold            | V <sub>DD</sub> _<br>GOOD_R | V <sub>DD</sub> rising, VddNotGood bit set, VDDOK pin set HiZ                               |      |      | 17   | V     |

| V <sub>DD</sub> Good Fall<br>Threshold            | V <sub>DD_GOOD_F</sub>      | V <sub>DD</sub> falling                                                                     | 15   |      |      | V     |

| V <sub>DD</sub> Good<br>Hysteresis                | V <sub>DD</sub> _<br>GOOD_H |                                                                                             |      | 0.4  |      | V     |

| V <sub>DD</sub> POR Rise<br>Threshold             | V <sub>DD_POR_R</sub>       | V <sub>DD</sub> rising                                                                      |      |      | 6.8  | V     |

| V <sub>DD</sub> POR Falling<br>Threshold          | V <sub>DD_POR_F</sub>       | V <sub>DD</sub> falling                                                                     | 5.6  |      |      | V     |

| V <sub>A</sub> Supply Voltage                     | V <sub>VA</sub>             | When $V_A$ is supplied externally; REGEN = GND.                                             | 3.0  |      | 5.5  | V     |

| V <sub>A</sub> Supply Current                     | I <sub>VA</sub>             | EN = high, OUT_ are turned on, no load, no LEDs connected                                   |      | 0.5  | 0.85 | mA    |

| V <sub>A</sub> Undervoltage<br>Lockout Threshold  | V <sub>VA_UV</sub>          | V <sub>DD</sub> = 24V, VA falling                                                           | 2.35 |      | 2.8  | V     |

| V <sub>A</sub> Undervoltage<br>Lockout Hysteresis | Vva_uvhyst                  | V <sub>DD</sub> = 24V                                                                       |      | 0.1  |      | V     |

| V <sub>L</sub> Supply Voltage                     | V <sub>VL</sub>             |                                                                                             | 2.5  |      | 5.5  | V     |

| V <sub>L</sub> Supply Current                     | I <sub>VL</sub>             | All logic inputs high or low                                                                |      | 13   | 34   | μA    |

| V <sub>L</sub> POR Threshold                      | V <sub>L POR</sub>          | V <sub>L</sub> falling                                                                      | 0.87 | 1.32 | 1.5  | V     |

| DC CHARACTERIST                                   |                             | JTPUTs (OUT_)                                                                               |      |      |      |       |

| On-Resistance                                     | R <sub>OUT_HS</sub>         | I <sub>OUT</sub> = -600mA                                                                   |      | 120  | 250  | mΩ    |

| Current Limit                                     | I <sub>LIM</sub>            |                                                                                             | 0.7  | 1    | 1.3  | А     |

| Off Leakage Current                               | I <sub>LKG</sub>            | OL detect = off, switch off, OUT_ = 0V                                                      | -10  |      | 10   | μA    |

# **Electrical Characteristics (continued)**

$(V_{DD} = +10 \text{V to } +36 \text{V}, V_{LED} = +3.0 \text{V to } 36 \text{V}, V_{A} = +3.0 \text{V to } +5.5 \text{V}, V_{L} = +2.5 \text{V to } +5.5 \text{V}, T_{A} = -40 ^{\circ}\text{C} \text{ to } +125 ^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{DD} = V_{LED} = 24 \text{V}, V_{A} = 3.3 \text{V}, T_{A} = +25 ^{\circ}\text{C}.)$  (Note 2)

| PARAMETER                            | SYMBOL                 | CONDITIONS                                                        | MIN                  | TYP                 | MAX                | UNITS |

|--------------------------------------|------------------------|-------------------------------------------------------------------|----------------------|---------------------|--------------------|-------|

| DC CHARACTERIST                      | CS/LINEAR RE           | GULATOR                                                           |                      |                     |                    |       |

| Output Voltage                       | V <sub>VA</sub>        | REGEN open, Cload = 1µF, 0mA < I <sub>VA</sub> < 20mA             | 3.0                  | 3.3                 | 3.6                | V     |

| Current Limit                        | I <sub>CL</sub> VA     | REGEN open                                                        | 25                   |                     |                    | mA    |

| Short Current                        | I <sub>SHRT_VA</sub>   | REGEN open, V <sub>A</sub> = 0V                                   |                      |                     | 60                 | mA    |

| Load Regulation                      |                        | 0mA < I <sub>VA</sub> < 20mA                                      |                      | 0.1                 |                    | mV/mA |

| REGEN Threshold                      | VT <sub>REGEN</sub>    |                                                                   | 0.2                  |                     |                    | V     |

| REGEN Leakage<br>Current             | I <sub>LK_REGEN</sub>  | REGEN = 0V                                                        | -50                  |                     |                    | μA    |

| DC CHARACTERIST                      | ICS/OFF STATE          | DIAGNOSTICS (OUT_)                                                |                      |                     |                    |       |

|                                      | I <sub>PU_OWOFF1</sub> | OWOff_ = 1, V <sub>OUT_</sub> < 5V, OffCurr1 = 0,<br>OffCurr0 = 0 | 10                   | 20                  | 32                 |       |

| Pullup Current,                      | I <sub>PU_OWOFF2</sub> | OWOff_ = 1, V <sub>OUT_</sub> < 5V, OffCurr1 = 0,<br>OffCurr0 = 1 | 65                   | 100                 | 135                | μA    |

| OWOFF                                | I <sub>PU_OWOFF3</sub> | OWOff_ = 1, V <sub>OUT_</sub> < 5V, OffCurr1 = 1,<br>OffCurr0 = 0 | 230                  | 300                 | 370                |       |

|                                      | I <sub>PU_OWOFF4</sub> | OWOff_ = 1, V <sub>OUT_</sub> < 5V, OffCurr1 = 1,<br>OffCurr0 = 1 | 480                  | 600                 | 720                |       |

| OUT_ Voltage,<br>OWOFF               | V <sub>OUT_OFF</sub>   | OWOff_ = 1, I <sub>OUT_</sub> = 0mA                               | 5.7                  | 6.7                 | 7.8                | V     |

| Open Wire Detect<br>Threshold, OWOFF | V <sub>TH_OWOFF</sub>  | OWOff_ = 1                                                        | 5                    |                     | 5.8                | V     |

|                                      |                        | ShVddEn_ = 1, ShrtVddThr1 = 0, ShrtVddThr0 = 0                    | 8.2                  | 9.0                 | 10.0               |       |

| Short to V <sub>DD</sub> Detect      | V=                     | ShVddEn_ = 1, ShrtVddThr1 = 0, ShrtVddThr0 = 1                    | 9.1                  | 10                  | 10.9               | V     |

| Threshold                            | V <sub>TH</sub> SHVDD  | ShVddEn_ = 1, ShrtVddThr1 = 1, ShrtVddThr0 = 0                    | 11                   | 12                  | 13                 |       |

|                                      |                        | ShVddEn_ = 1, ShrtVddThr1 = 1, ShrtVddThr0 = 1                    | 13                   | 14                  | 15                 |       |

| DC CHARACTERIST                      | ICS/ON STATE           | DIAGNOSTICS                                                       |                      |                     |                    |       |

| Open Wire Detect                     |                        | OWOn_ = 1, $R_{OWONSET}$ = 500k $\Omega$                          | 0.05                 | 0.13                | 0.2                |       |

| Threshold Current,                   | I <sub>TH</sub> OWON   | OWOn_ = 1, $R_{OWONSET}$ = 160k $\Omega$                          | 0.25                 | 0.35                | 0.55               | mA    |

| On                                   |                        | OWON_ = 1, $R_{OWONSET}$ = $30k\Omega$                            | 1.8                  | 2.4                 | 2.9                |       |

| DC CHARACTERIST                      | ICS/LOGIC I/O          |                                                                   |                      |                     |                    |       |

| Input Voltage High                   | V <sub>IH</sub>        |                                                                   | 0.7xV <sub>L</sub>   |                     |                    | V     |

| Input Voltage Low                    | V <sub>IL</sub>        |                                                                   |                      |                     | 0.3xV <sub>L</sub> | V     |

| Input Threshold<br>Hysteresis        | V <sub>IHYS</sub>      |                                                                   |                      | 0.11xV <sub>L</sub> |                    | V     |

| Input Pulldown<br>Resistor           | R <sub>IN_PD</sub>     | See logic pin descriptions for applicable pins                    |                      | 200                 |                    | kW    |

| Input Pullup Resistor                | R <sub>IN_PU</sub>     | See logic pin descriptions for applicable pins                    |                      | 200                 |                    | kW    |

| Output Logic-High (SDO)              | V <sub>OH</sub>        | I <sub>LOAD</sub> = -5mA                                          | V <sub>L</sub> - 0.6 |                     |                    | V     |

# **Electrical Characteristics (continued)**

$(V_{DD} = +10 \text{V to } +36 \text{V}, V_{LED} = +3.0 \text{V to } 36 \text{V}, V_{A} = +3.0 \text{V to } +5.5 \text{V}, V_{L} = +2.5 \text{V to } +5.5 \text{V}, T_{A} = -40 ^{\circ}\text{C} \text{ to } +125 ^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{DD} = V_{LED} = 24 \text{V}, V_{A} = 3.3 \text{V}, T_{A} = +25 ^{\circ}\text{C}.)$  (Note 2)

| PARAMETER                                  | SYMBOL                       | CONDITIONS                                                                                                                    | MIN                    | TYP | MAX             | UNITS |

|--------------------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|-----------------|-------|

| Output Logic-Low                           | V <sub>OL</sub>              | I <sub>LOAD</sub> = +5mA                                                                                                      |                        |     | 0.33            | V     |

| SDO Output Tristate<br>Leakage             | I <sub>L_SDO</sub>           | CS = high                                                                                                                     | -1                     |     | +1              | μA    |

| DC CHARACTERISTI                           | CS/OPEN-DRA                  | IN OUTPUT (FAULT, COMERR, READY)                                                                                              |                        |     |                 |       |

| READY Output<br>Logic-High                 | V <sub>ODH</sub>             | I <sub>LOAD</sub> = -5mA                                                                                                      | V <sub>L</sub> - 0.6   |     |                 | V     |

| Output Logic-Low                           | V <sub>ODL</sub>             | I <sub>LOAD</sub> = +5mA                                                                                                      |                        |     | 0.33            | V     |

| Leakage                                    | I <sub>ODL</sub>             | Open-drain output off, V = 5.5V                                                                                               | -1                     |     | +1              | μA    |

| DC CHARACTERISTI                           | CS/LED Driver                | s (LH_, LL_, <del>VDDOK</del> )                                                                                               |                        |     |                 |       |

| LED Supply Voltage                         | V <sub>LED</sub>             |                                                                                                                               | 3.0                    |     | V <sub>DD</sub> | V     |

| LH Voltage High                            | V <sub>OH_LH</sub>           | LH = on, I <sub>LEDH</sub> = -5mA                                                                                             | V <sub>LED</sub> - 0.3 |     |                 | V     |

| LH Off Leakage<br>Current                  | I <sub>L_LH</sub>            | LH_ = off, V <sub>LEDH</sub> = 0V                                                                                             |                        |     | 5               | μA    |

| LL Output Voltage<br>Low                   | V <sub>OH_LL</sub>           | LL = on, I <sub>LDL</sub> = 5mA                                                                                               |                        |     | 0.3             | V     |

| LL Off Leakage<br>Current                  | IL_LL                        | LL = off, V <sub>LL</sub> = VLED                                                                                              | -1                     |     | +1              | μA    |

| DC CHARACTERISTI                           | CS/PROTECTION                | ON                                                                                                                            |                        |     |                 |       |

| OUT_ Clamp Voltage                         | V <sub>CL</sub>              | V <sub>CL</sub> = V <sub>DD</sub> - OUT, I <sub>OUT</sub> = -500mA, OUT_ is off                                               | 49                     | 56  |                 | V     |

| Channel Thermal<br>Shutdown<br>Temperature | T <sub>JSHDN</sub>           | Junction temperature rising. Per channel.                                                                                     |                        | 150 |                 | °C    |

| Channel Thermal<br>Shutdown Hysteresis     | T <sub>JSHDN</sub> _<br>HYST |                                                                                                                               |                        | 15  |                 | °C    |

| Chip Thermal<br>Shutdown                   | T <sub>CSHDN</sub>           | Temperature rising.                                                                                                           |                        | 150 |                 | °C    |

| Chip Thermal<br>Shutdown Hysteresis        | T <sub>CSHDN</sub> _<br>HYST |                                                                                                                               |                        | 10  |                 | °C    |

| TIMING CHARACTER                           |                              |                                                                                                                               |                        |     |                 | ,     |

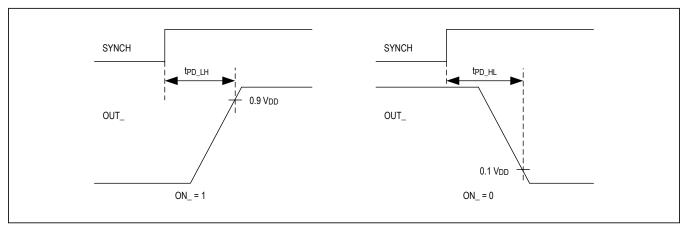

| Prop Delay LH                              | t <sub>PD_LH</sub>           | Delay from rising SYNCH edge to OUT_ rising to 90%. $R_L = 48\Omega$ . $V_{DD} = 24V$ . Figure 2                              |                        | 11  | 30              | μs    |

| Prop Delay HL                              | t <sub>PD_HL</sub>           | Delay from rising SYNCH edge to OUT_falling to 10% of V <sub>DD</sub> , V <sub>DD</sub> = 24V, R <sub>L</sub> = 48Ω, Figure 2 |                        | 11  | 30              | μs    |

| Rise-Time                                  | t <sub>R</sub>               | 20% to 80% $V_{DD}$ , $V_{DD}$ = 24V, $R_L$ = 48Ω, Figure 2                                                                   |                        | 8   |                 | μs    |

| Fall-Time                                  | t <sub>F</sub>               | 80% to 20% $V_{DD}$ , $V_{DD}$ = 24V, $R_L$ = 48 $\Omega$ , Figure 2                                                          |                        | 8   |                 | μs    |

# **Electrical Characteristics (continued)**

$(V_{DD}$  = +10V to +36V,  $V_{LED}$  = +3.0V to 36V,  $V_A$  = +3.0V to +5.5V,  $V_L$  = +2.5V to +5.5V,  $T_A$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $V_{DD}$  =  $V_{LED}$  = 24V,  $V_A$  = 3.3V,  $T_A$  = +25°C.) (Note 2)

| PARAMETER                     | SYMBOL             | CONDITIONS                                                                     | MIN | TYP  | MAX | UNITS |

|-------------------------------|--------------------|--------------------------------------------------------------------------------|-----|------|-----|-------|

| TIMING CHARACTER              | ISTICS/WATC        | HDOG                                                                           |     |      |     |       |

|                               |                    | WDTo[1:0] = 01b                                                                |     | 200  |     |       |

| Watchdog Timeout              | $t_{WD}$           | WDTo[1:0] = 10b                                                                |     | 600  |     | ms    |

|                               |                    | WDTo[1:0] = 11b                                                                |     | 1200 |     |       |

| Watchdogs Timeout<br>Accuracy | twd_acc            | WDEN = 1, SynchWDEn = 1, see Config2 register for watchdog timeout             | -30 |      | +30 | %     |

| TIMING CHARACTER              | ISTICS/LED M       | atrix                                                                          |     |      |     |       |

| LED Driver Scan rate          | FLED               | Update rate for each LED                                                       |     | 1    |     | kHz   |

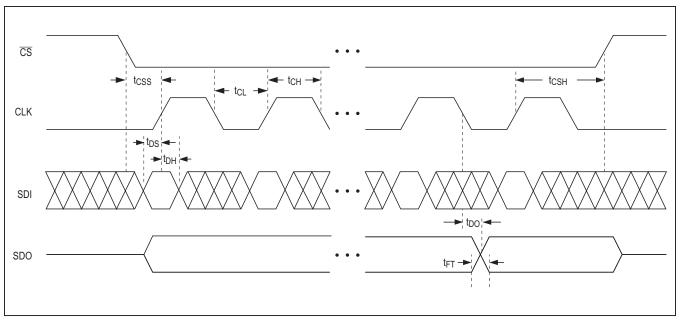

| TIMING CHARACTER              | ISTICS/SPI Fig     | gure 1                                                                         |     |      |     |       |

| CLK Clock Period              | t <sub>CH+CL</sub> |                                                                                | 100 |      |     | ns    |

| CLK Pulse Width High          | t <sub>CH</sub>    |                                                                                | 40  |      |     | ns    |

| CLK Pulse Width Low           | t <sub>CL</sub>    |                                                                                | 40  |      |     | ns    |

| CSFall to CLK Rise<br>Time    | t <sub>CSS</sub>   |                                                                                | 40  |      |     | ns    |

| SDI Hold Time                 | t <sub>DH</sub>    |                                                                                | 10  |      |     | ns    |

| SDI Setup Time                | t <sub>DS</sub>    |                                                                                | 10  |      |     | ns    |

| SDO Propagation<br>Delay      | t <sub>DO</sub>    | Cload = 10pF, CLK falling edge to SDO stable                                   |     |      | 30  | ns    |

| SDO Rise and Fall<br>Times    | t <sub>FT</sub>    |                                                                                |     | 1    |     | ns    |

| CSHold Time                   | tcsh               |                                                                                | 40  |      |     | ns    |

| CSPulse Width High            | t <sub>CSPW</sub>  | Note 3                                                                         | 40  |      |     | ns    |

| EMC                           |                    |                                                                                |     |      |     | ,     |

| ESD IEC Contact<br>Discharge  | V <sub>ESD_C</sub> | OUT_ to GND, IEC61000-4-2                                                      |     | ±7   |     | kV    |

| ESD IEC Air<br>Discharge      | V <sub>ESD_A</sub> | OUT_ to GND, IEC61000-4-2                                                      |     | ±30  |     | kV    |

| ESD                           | V <sub>ESD</sub>   | All other pins. Human Body Model (Note 4)                                      |     | ±2   |     | kV    |

| Surge Tolerance               | V <sub>SURGE</sub> | OUT_ to GND, IEC61000-4-5 with 42 $\Omega$ , TVS on V <sub>DD</sub> . (Note 5) |     | ±1   |     | kV    |

Note 2: All units are production tested at  $T_A$  = +25°C. Specifications over temperature are guaranteed by design.

Note 3: All logic input pins except CS have a pulldown resistor. CS has a pullup resistor.

Note 4: Bypass V<sub>DD</sub> pin to GND with 1µF capacitor as close as possible to the device for high ESD protection.

**Note 5:** At typical application value of  $V_{DD}$  = 24V, with a TVS proection on  $V_{DD}$  to GND.

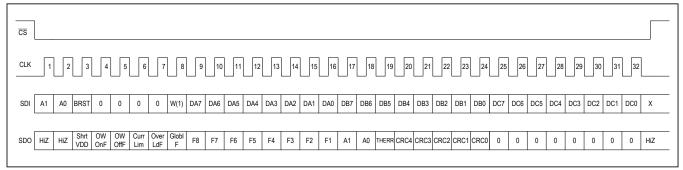

Figure 1. SPI Timing Diagram.

Figure 2. Propagation Delay Timing Characteristics

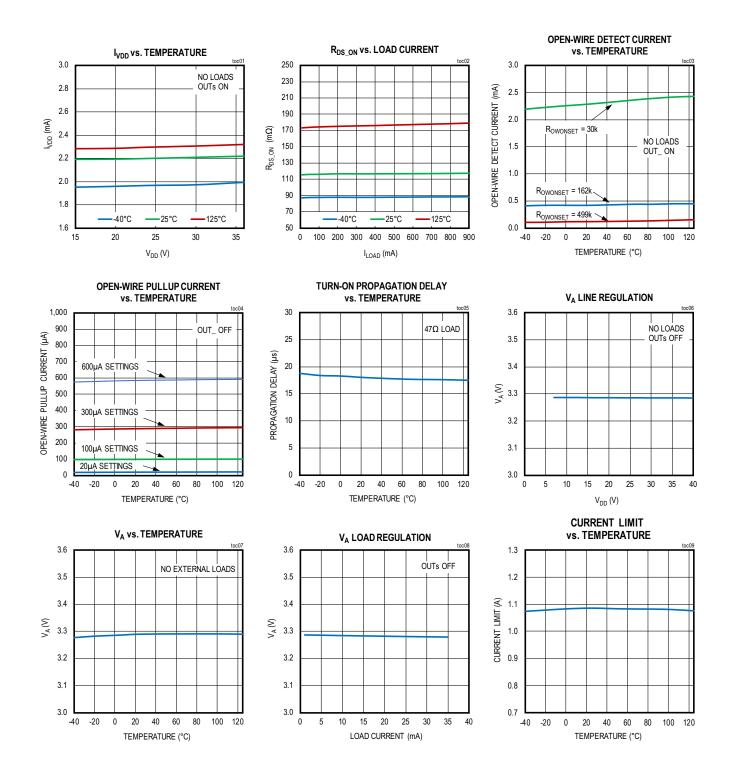

# **Typical Operating Characteristics**

$(V_{DD} = +24V, REGEN = open, V_L = +3.3V, T_A = +25$ °C, unless otherwise noted)

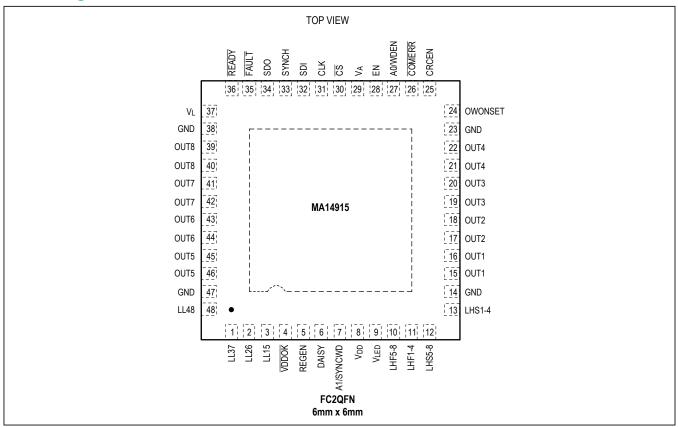

# **Pin Configuration**

# **Pin Description**

| PIN               | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                | REF SUPPLY | TYPE   |  |  |

|-------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|--|--|

| POWER SUPPLY      |                 |                                                                                                                                                                                                                                                                                                                                                         |            |        |  |  |

| EP, 8             | V <sub>DD</sub> | Supply Voltage, Nominally 24V. Connect all $V_{DD}$ together. Bypass $V_{DD}$ to GND through a $1\mu F$ capacitor.                                                                                                                                                                                                                                      | GND        | Supply |  |  |

| 29                | V <sub>A</sub>  | Analog Supply Input. Connect an external 3.0V to 5.5V supply to $V_A$ or use the internal linear regulator by leaving REGEN open. Bypass $V_A$ to GND through a $1\mu F$ ceramic capacitor.                                                                                                                                                             | GND        | Supply |  |  |

| 5                 | REGEN           | $V_A$ Regulator Enable Input. Connect REGEN to GND to disable $V_A$ regulator. Leave REGEN open to enable $V_A$ regulator, which internally supplies $V_A$ with 3.3V.                                                                                                                                                                                   | GND        | Supply |  |  |

| 14, 23, 38,<br>47 | GND             | Ground. Connect all GND pins together.                                                                                                                                                                                                                                                                                                                  | GND        | GND    |  |  |

| 37                | V <sub>L</sub>  | Logic Supply Input. V <sub>L</sub> defines the logic levels on all logic interface pins. Bypass V <sub>L</sub> to GND through a 100nF ceramic capacitor.                                                                                                                                                                                                | GND        | Supply |  |  |

| 4                 | VDDOK           | $\overline{\text{VDDOK}}$ is an active-low, open-drain logic output that indicates when the V <sub>DD</sub> supply is OK. $\overline{\text{VDDOK}}$ turns on low when V <sub>DD</sub> rises to > 16V(typ) and turns off when V <sub>DD</sub> falls to < 13V (typ). Connect a LED with a pullup resistor to a voltage between 3.3V and V <sub>DD</sub> . | GND        | Logic  |  |  |

# **Pin Description (continued)**

| PIN      | NAME         | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | REF SUPPLY      | TYPE   |

|----------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------|

| SWITCH O | UTPUTS       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |        |

| 15, 16   | OUT1         | High-Side Switch Output 1                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V <sub>DD</sub> | Power  |

| 17, 18   | OUT2         | High-Side Switch Output 2                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $V_{DD}$        | Power  |

| 19, 20   | OUT3         | High-Side Switch Output 3                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $V_{DD}$        | Power  |

| 21, 22   | OUT4         | High-Side Switch Output 4                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $V_{DD}$        | Power  |

| 45, 46   | OUT5         | High-Side Switch Output 5                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V <sub>DD</sub> | Power  |

| 43, 44   | OUT6         | High-Side Switch Output 6                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V <sub>DD</sub> | Power  |

| 41, 42   | OUT7         | High-Side Switch Output 7                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V <sub>DD</sub> | Power  |

| 39, 40   | OUT8         | High-Side Switch Output 8                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $V_{DD}$        | Power  |

| DIAGNOST | TIC SETTING  | ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                 |        |

| 24       | OWON-<br>SET | Open-Wire Detection Threshold Current Set. Connect a resistor between OWONSET and GND to define the threshold current for open-wire detection when the OUT_ switches are closed.                                                                                                                                                                                                                                                                                          | VA              | Analog |

|          |              | Control Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                 |        |

| 28       | EN           | Enable Logic Input. Drive EN high for normal operation. Drive EN low to disable/three-state all OUT_ drivers. Internal weak pulldown.                                                                                                                                                                                                                                                                                                                                     | VL              | Logic  |

| 35       | FAULT        | FAULTGlobal Diagnostics Open-Drain Output. The FAULT transistor turns on low under conditions defined in the Interrupt register. Connect a pullup resistor to V <sub>L</sub> .                                                                                                                                                                                                                                                                                            | V <sub>L</sub>  | Logic  |

| 33       | SYNCH        | SYNCH Input. All eight output switches are updated simultaneously on the rising edge of SYNCH, as determined by the contents of the SPI register. The OUT_ states do not change when SYNCH is held low. When SYNCH is high, the output states change immediately when a new value is written into the SetOUT register. Internal weak pullup.                                                                                                                              | VL              | Logic  |

| 25       | CRCEN        | CRC Enable Select Input. Drive CRCEN high to enable CRC generation and error detection on the serial data. CRC has a weak pulldown.                                                                                                                                                                                                                                                                                                                                       | VL              | Logic  |

| 36       | READY        | $\overline{\text{READY}}$ is an open-drain output that is passive low when the internal logic chip supply and V <sub>L</sub> I/O supply are both higher than their respective UVLO thresholds, indicating that the part is ready for SPI communication. When the internal register supply falls below the UVLO threshold the register contents are lost and $\overline{\text{READY}}$ transitions active-high. Connect a pulldown resistor to $\overline{\text{READY}}$ . | VL              | Logic  |

| 26       | COMERR       | SPI Error Open-Drain Output. The $\overline{\text{COMERR}}$ transistor turns on low when an error occurs during a SPI transaction. Connect a pullup resistor to V <sub>L</sub> .                                                                                                                                                                                                                                                                                          | VL              | Logic  |

# **Pin Description (continued)**

| PIN       | NAME             | FUNCTION                                                                                                                  | REF SUPPLY     | TYPE  |

|-----------|------------------|---------------------------------------------------------------------------------------------------------------------------|----------------|-------|

| SERIAL IN | ITERFACE         |                                                                                                                           |                |       |

| 32        | SDI              | Serial Data Input. SPI MOSI data from controller. SDI has a weak pulldown.                                                | V <sub>L</sub> | Logic |

| 34        | SDO              | Serial Data Output. SPI MISO data output to controller.                                                                   | VL             | Logic |

| 31        | CLK              | Serial Clock Input from SPI Controller. CLK has a weak pulldown.                                                          | VL             | Logic |

| 30        | CS               | Chip Select Input from Controller. $\overline{\text{CS}}$ has a weak pullup.                                              | VL             | Logic |

| 27        | A0/WDEN          | Chip address LSB for addressable SPI or SPI watchdog enable input for daisy-chain SPI. AO/WDEN has a weak pulldown.       | VL             | Logic |

| 7         | A1/SYN-<br>CWD   | Chip Address MSB for Addressable SPI. SYNCH pin watchdog enable input for daisy-chain SPI. A1/SYNCWD has a weak pulldown. | VL             | Logic |

| 6         | DAISY            | Daisy-Chain Enable Select Input. Drive DAISY high to enable daisy-chained SPI mode. DAISY has a weak pulldown.            | VL             | Logic |

| LED DRIVE | R MATRIX         |                                                                                                                           |                |       |

| 9         | V <sub>LED</sub> | Supply for LED Drivers. Apply supply voltage of 3.0V to V <sub>DD</sub> .                                                 |                |       |

| 3         | LL15             | OUTs 1, 5 Status/Fault LED Cathode Output (Open-Drain Low-Side). Connect a resistor in series to set the LED current.     |                |       |

| 2         | LL26             | OUTs 2, 6 Status/Fault LED Cathode Output (Open-Drain Low-Side). Connect a resistor in series to set the LED current.     |                |       |

| 1         | LL37             | OUTs 3, 7 Status/Fault LED Cathode Output (Open-Drain Low-Side). Connect a resistor in series to set the LED current.     |                |       |

| 48        | LL48             | OUTs 4, 8 Status/Fault LED Cathode Output (Open-Drain Low-Side). Connect a resistor in series to set the LED current.     |                |       |

| 13        | LHS1-4           | OUTs 1-4 Status LED Anode Outputs (Open-Drain High-Side). Connect a resistor in series to set the LED current.            |                |       |

| 12        | LHS5-8           | OUTs 5-8 Status LED Anode Outputs (Open-Drain High-Side). Connect a resistor in series to set the LED current.            |                |       |

| 11        | LHF1-4           | OUTs 1-4 Fault LED Anode Connections (Open-Drain High-Side). Connect a resistor in series to set the LED current          |                |       |

| 10        | LHF5-8           | OUTs 5-8 Fault LED Anode Connections (Open-Drain High-Side). Connect a resistor in series to set the LED current.         |                |       |

# **Detailed Description**

The MAX14915 is an octal high-side switch. The OUT\_high-side switches have  $250 m\Omega$  (max) on-resistance at 600 mA and  $T_A$  =  $125^{\circ}C.$  Extensive diagnostics can be enabled through SPI to indicate wire-break, overload, current limiting, output short to  $V_{DD}$ , low supply voltage, and high chip temperature conditions. Active clamping limits the negative OUT\_ voltage to ( $V_{DD}$  -  $V_{CL}$ ) and allows for freewheeling currents to demagnetize the inductive loads quickly. A watchdog timer monitors SPI activity and automatically switches the OUT\_ switches off in case of missing SPI activity.

#### **Synchronization**

On the rising edge of the SYNCH logic input, all OUT\_switches change to the new state previously programmed into the SetOUT register. If SYNCH is held high, then the OUT\_change state immediately when the SetOUT register is written to (transparent mode).

When EN pin is low, all OUT\_ are off independent of the SYNCH pin state and the SetOUT register value.

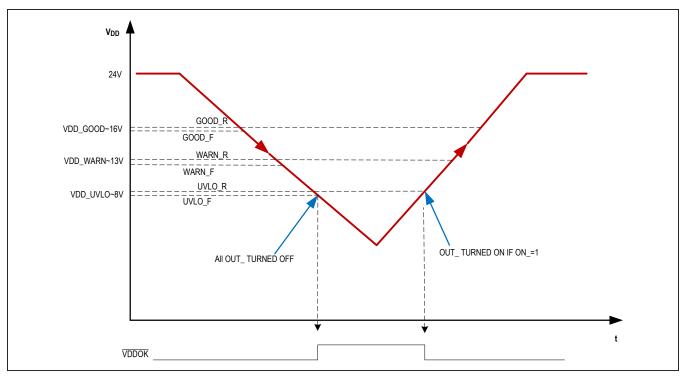

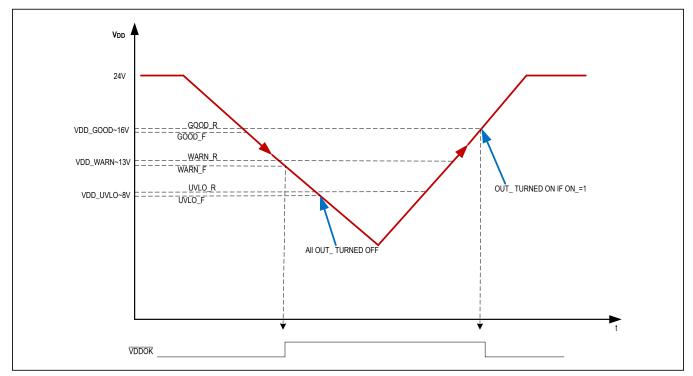

#### Power-Up and Undervoltage Lockout

When the  $V_{DD}$ ,  $V_A$ ,  $V_L$ , or  $V_{INT}$  supply voltages are under their respective UVLO thresholds, all OUT\_ switches are off and the open wire detect current sources are turned off.  $V_{INT}$  is an internal supply for the registers and logic that is derived from the  $V_A$  or  $V_{DD}$  supply.

When the  $V_{DD}$  supply or  $V_A$  supply rises, the internal logic supply,  $V_{INT}$ , rises. If  $V_L$  and  $V_{INT}$  are both above their UVLO thresholds, the chip is ready for communication and the  $\overline{READY}$  pin becomes passive low to indicate that the part is ready to communicate through the SPI interface.

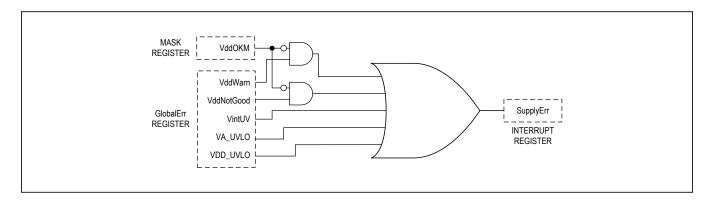

In addressed SPI mode (DAISY pin is low) the VddUvlo, VddNotGood, VddWarn, Vint\_UV, and VA\_UVLO bits are set = 1 and the FAULT output is set active-low. These bits and the FAULT pin only clear once the GlobalErr register is read.

The register contents are lost when both  $V_A$  and  $V_{DD}$  drop low and the internal register supply,  $V_{INT}$ , falls below its undervoltage lockout threshold.

The Vint\_UV bit = 1 signals that the register contents are in power-on-reset state and any custom configuration can be programmed or needs to be reprogrammed after a power reset event.

When  $V_{DD}$  rises above  $V_{DD\_UVLO\_R}$  (with VDDOnTh = 0) or above  $V_{DD\_GOOD\_R}$  (with VDDOnThr = 1) the  $\overline{VDDOK}$  pin is turned active-low, indicating that the  $V_{DD}$  supply is high enough so the OUT\_ switches can be operated normally.

When  $V_{DD}$  falls below  $V_{DD\_WARN\_F}$  (~13V), the VDDWarn bit (if VddOKM = 0) and, thus, FAULT are set but the OUT switches continue operating normally.

When V<sub>DD</sub> falls further below V<sub>DD</sub> UVLO\_F, the VDD\_UVLO bit is set and the OUT switches are turned off.

In daisy-chain mode (DAISY pin high), the READY and VDDOK pins are active, but the FAULT pin does not signal supply conditions.

#### **Chip Thermal Protection**

When the chip temperature rises to above the thermal shutdown threshold of  $150^{\circ}$ C, the chip enters shutdown protection and all overloaded OUT switches are kept off until chip temperature drops below  $140^{\circ}$ C. The ThrmShut bit and  $\overline{FAULT}$  output are set.

If the chip temperature rises above 165°C due to a short, an overload on the  $V_A$  regulator, or LED matrix, the internal  $V_A$  linear regulator, all OUT switches, and the LED matrix are shutdown to prevent part damage. In this condition, the ThrmShut bit and  $\overline{FAULT}$  output are already set and in daisy-chain mode the F-bits in SDO are all set to 1. The register contents are not lost in thermal shutdown if  $V_{DD}$  supply is present.

When the chip temperature then falls by the hysteresis amount, the  $V_A$  regulator turns on, LED matrix and OUT switches are restored to normal operation.

Figure 3.  $V_{DD}$  Monitoring with VDDOnThr = 0

Figure 4.  $V_{DD}$  Monitoring with VDDOnThr = 1

## **Channel Thermal Management**

Every driver's temperature is constantly monitored. If the temperature of a driver rises above the thermal shutdown threshold of 150°C (typ), that channel is automatically turned off for protection. After the temperature drops by 15°C, the driver will be turned on again.

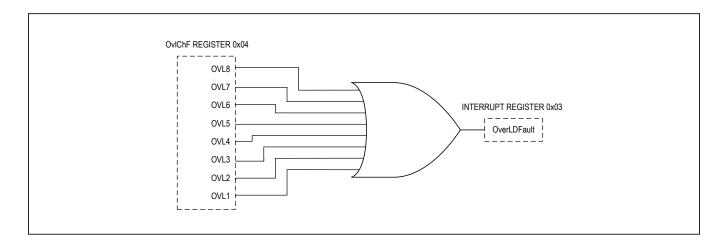

When a driver turns off due to thermal shutdown, the per-channel overload bits, OVL\_, the interrupt OverLdFault bit and FAULT pin indicate this condition, if enabled. See *Register Map*.

### **Current Limiting**

Each high-side switch features active current limiting. When the load current exceeds 1A (typ), the load current is limited by the high-side switch. If the load impedance tries to draw higher current, the voltage across the high-side FET switch increases and the temperature of the FET increases in accordance with the FET's power

dissipation. When an OUT\_ channel shows an overcurrent, the CL bit is set in the CurrLimF register.

### **Lamp Load Turn On**

Incandescent lamps initially draw high currents while their filament is cold, and this turn-on current reduces as the filament heats up. The MAX14915 has a scheme that automatically detects the presence of a lamps loads. When a lamp load is detected the overtemperature and overload messages are avoided for a duration of 200ms. The lamp load detection is transparent to the user and is not signaled to the user.

# **Diagnostics**

<u>Table 2</u> lists the per channel diagnostics made available by the MAX14915. The state of the high-side switch for which diagnostics are determined is shown in the <u>Table 1</u>. Table 2 summarizes the global diagnostics.

**Table 1. Per-Channel Diagnostics**

| PER CHANNEL DIAGNOSTIC | SWITCH STATE | ENABLED     | INTERRUPT MASK ENABLED |

|------------------------|--------------|-------------|------------------------|

| Overload               | Closed       | By default  | By OverldM             |

| Overcurrent            | Closed       | By default  | By CurrLimM            |

| Open Wire On           | Closed       | Per channel | By OWOnM               |

| Open Wire Off          | Open         | Per channel | By OWOffM              |

| Short to VDD           | Open         | Per channel | By ShtVddM             |

# **Table 2. Global Diagnostics**

| GLOBAL DIAGNOSTICS | FUNCTION                                                  | ENABLED                                                        | FAULT INTERRUPT MASK |

|--------------------|-----------------------------------------------------------|----------------------------------------------------------------|----------------------|

| ThrmShut           | Chip thermal shutdown                                     | Always On                                                      | None                 |

| Vint_UV            | Undervoltage on the internal supply for the SPI registers | Always On                                                      | None                 |

| VA_UVLO            | VA was in undervoltage                                    | Always On                                                      | SupplyErrM           |

| VDD_Warn           | Low VDD warning                                           | Always On                                                      | VddOKM               |

| VddUvlo            | VDD supply in UVLO, all OUT_ switches turned off          | Always On                                                      | SupplyErrM           |

| VddNotGood         | Not Good VDD warning                                      | Always On                                                      | VddOKM               |

| WDErr              | SPI has no activity for the timeout period                | by WDTo[1:0] (DAISY = Low)<br>by A0/WDEN (DAISY = High)        | ComErrM              |

| SynchErr           | SYNCH input stuck low for the timeout period              | by SynchWDEn<br>(DAISY = Low)<br>by A1/SWDEN<br>(DAISY = High) | ComErrM              |

| ComErr             | SPI CRC or Communication error                            | by CRCEN pin                                                   | ComErrM              |

## Diagnostics Filtering

Open-wire detection and short-to- $V_{\mbox{\scriptsize DD}}$  detection, in conjunction with reactive loads, can take many milliseconds to settle to stable conditions after a change of high-side switch state. During this time, diagnostic detection would not generate reliable results. Therefore, after the OUT switching instant, a blanking period of 4ms (optionally 8ms through register bit) is observed, during which these diagnostics are not evaluated. After this 4ms blanking time, an averaging filter is engaged for 4ms, after which the short-to-V<sub>DD</sub> and open-wire diagnostics are determined and updated as per channel diagnostics in the OwOffChF, OwOnChF, and ShtVDDChF registers. Consequentially, the Interrupt register, FLEDs (if FLEDSet = 0), and diagnostic bits in the SDO data (if read).

When an OUT switch changes On/Off state, the diagnostic state for the previous state is cleared internally. The registers diagnostic bits are cleared if FLatchEn = 0. If FLatchEn = 1, the diagnostic bits are cleared by an SPI read command.

For the overload and overcurrent diagnostics detection, a 54µs filter time is employed and there is no blanking time. If a lamp load is detected on an OUT, this is seen as a normal load and, therefore, overload and overcurrent diagnostics are not set during the lamp-load detect time.

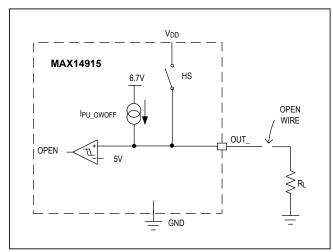

### **Open-Wire Detection**

Monitoring of an open wire/open load condition can be enabled on a per-channel basis through serial configuration. Open-wire detection can be selected for either, or both. of the cases with a high-side switch in the on or/and the off state.

Figure 5. Open Wire Detection Scheme

#### Open-Wire Detection with Switch On

Open load detection can be enabled on any OUT switch through the OwOnEN\_ bits. When the HS switch is on, the load current flowing out of the high-side switch is monitored. If this current drops to below a threshold value set through the resistor connected to the OWONSET, an open load detection fault is reported.

The OWONSET resistor allows selecting a load current threshold in the range of 0.35mA (typ) to 2.5mA (typ)

#### **Open-Wire Detection with Switch Off**

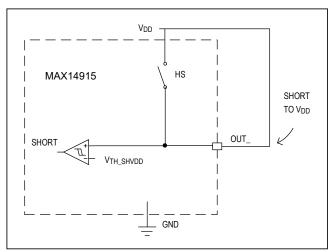

Monitoring of an open-wire condition in the switch offstate can be enabled on individual channels through the OWOffEn\_ bits. When the HS switch is off, a weak current source, IOL, is enabled that pulls OUT\_ to 6.7V during a wire break. If the OUT\_ voltage is above 5V(min) and below the  $V_{TH\ SHVDD}$  (9V-14V) voltage threshold, an open load is signaled.

## Short to V<sub>DD</sub> Detection

The MAX14915 can detect shorts to VDD, if enabled through SPI. This only operates when an OUT switch is off. If the OUT\_ voltage is higher than the threshold voltage set by the ShrtVddThr0 and ShrtVddThr1 bits, a ShtVddFault is indicated in the GloblErr and ShtVddChF registers, as well as the FAULT output pin (if not masked). The bits allow setting a V<sub>TH SHVDD</sub> threshold in the range of 9V to 14V when  $V_{DD}$  is above VDD\_GOOD threshold. For VDD below 16V (typ), the V<sub>TH</sub> SHVDD is always set to 9V independently by the ShtVddChF bits.

Figure 6. Short to V<sub>DD</sub> Detection Scheme

## **Diagnostic Bit Behavior**

The per channel diagnostic bits (OVL\_, CL\_, OWOff\_, OWOn\_, SHVDD\_) can be configured to be latched or real-time through the FLatchEn bit in the Config1 register. When latched diagnostics are enabled (FLatchEn = 1), the diagnostic bits are set = 1 when a fault is detected and remains = 1, even if the fault disappears. This bit is only reset to = 0 when the cause of the fault has disappeared AND the relevant fault register is read through SPI — in address SPI mode. If the cause of the fault has not disappeared, the diagnostic bit remains = 1.

In daisy-chain mode, the FAULT pin and the F-bits in SDO are cleared on the following SPI cycle if the fault condition was removed.

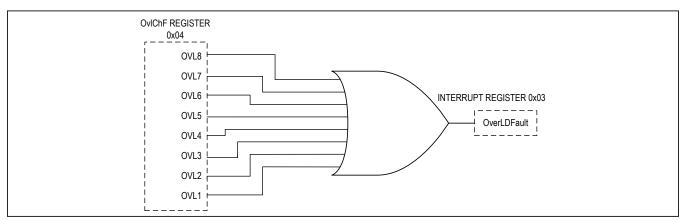

The per-channel faults in each of the five error registers are logically or'ed together to produce the fault bits in the Interrupt register. This is shown in the following diagram on the basis of overload diagnostics.

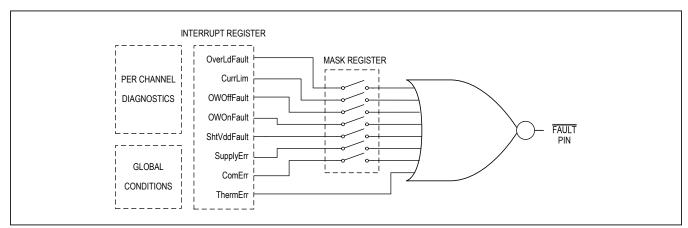

# **FAULT** Pin Signalling

The FAULTpin is an open-drain logic output that transitions active low when a fault condition is detected. The source of faults are the eight bits in the Interrupt register: per-channel faults and global faults. The source of FAULT can be masked through the Mask register.

In addressed SPI mode, the diagnostics can be latched (FLatchEn = 1), in which case the FAULTpin can only be cleared by reading the Interrupt register AND the corresponding fault register(s), whose fault is latched in the Interrupt register. In latched diagnostics mode, FAULTcannot be cleared by only reading the Interrupt register. If FLatch = 0, then the diagnostic bits, the Interrupt register bits and the FAULTpin are not latched, so are real time.

In daisy-chain mode, the FAULTpin is latched, so is cleared on the next SPI cycle, if the cause of the fault has disappeared.

Figure 7. Overload Interrupt Diagnostic Scheme

Figure 8. FAULT Signaling Scheme

#### Watchdog

MAX14915 provides two watchdog timers to allow monitoring activity on the SPI interface and on SYNCH pin. In daisy-chain SPI mode, drive A0/WDEN and/or A1/SYNCWD high to enable the watchdog for SPI and/or SYNCH pin. In addressed SPI mode, the watchdog timer is enabled through the WDTo\_ bits. If enabled, it will monitor and expect clock activity on the CLK and  $\overline{\text{CS}}$  inputs. At least one valid SPI cycle must be detected in the WD-timeout period. This means that the CLK input must have a multiple of 8 clock cycles during a  $\overline{\text{CS}}$  low period.

The SYNCH pin watchdog can be enabled by SynchWDEn bit and it will monitor the SYNCH pin if it is not stuck low. At least a 1µs SYNCH pin high must be detected in the WD-timeout period to avoid SYNCH pin watchdog error.

If the watchdog criterion is not met, all OUT\_ switches are automatically turned off and the FAULT pin is set active-low. In addressed SPI mode, the WDErr and ComErr bits are set to 1.

In addresses SPI mode, SYNCH and SPI watchdog timeout can be selected through the WDTo\_ bits in the Config2 register. In daisy-chain SPI mode, the watchdog timeout for both SPI and SYNCH pin is 1.2s.

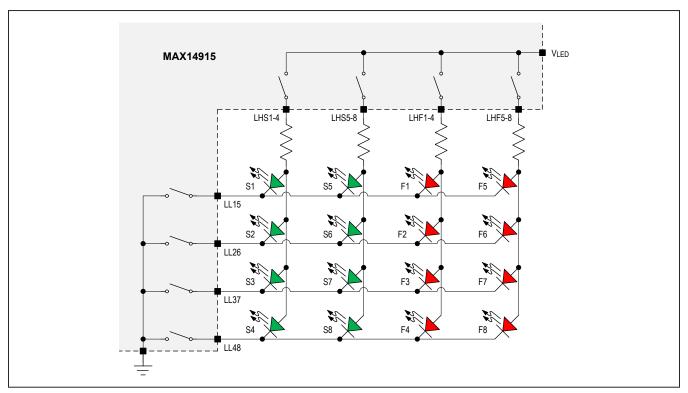

#### **LED Drivers**

The 4x4 LED driver crossbar matrix offers an efficient configuration for driving up to 16 LEDs. The LEDs can either be turned on/off by the SPI master by setting the SetSLED and/or SetFLED register bits in addressed SPI mode, or can be controlled by the MAX14915 autonomously to indicate per-channel status and fault conditions, depending on configuration in the Config1 register.

If controlled internally (SLEDSet = 0 or FLEDSet = 0), a channel's status LED will automatically be turned on when the corresponding OUT\_ switch is on and there is no fault condition. If diagnostics detection is enabled on any OUT\_ switch and a fault is detected, its associated fault LED (FLED) is turned on and its associated status LED (SLED) is automatically turned off. This means that for any OUT\_ channel, its SLED and its FLED will never be on simultaneously.

If FLEDSet = 0, diagnostics that are enabled (ShtVdd, OWOnCh, OWOff, CL, OVL) will result in FLEDs turning on when a fault is detected. Only overcurrent detection can be masked from driving the FLEDs through the LEDCurrLim bit.

Figure 9. LED Matrix Scheme

When a lamp load is detected during OUT\_ turn-on, its SLED is turned on and its FLED stays off.

If the FLEDs are controlled internally, they are always filtered, both in daisy chain and addressed SPI modes. When controlled internally, the FLED minimum on-time can be programmed through the two FLEDStretch\_ bits. The SLEDs are real-time when controlled internally.

The LED matrix is powered through the  $V_{LED}$  supply input, which can be in the range of the 3.0V (min) up to the  $V_{DD}$  field supply voltage.

If daisy-chain mode is selected (DAISY pin high) the LED matrix is always controlled by MAX14915. FAULT LEDs signal only OVL faults and they are stretched by 2s.

For every current limiting resistor, R, each of the four LEDs in a column string is pulsed for a quarter of the time, so that current only flows through one LED and resistor at any one time. Thus the resistors, R, determine the LED current through one LED during the pulse. Each LED is pulsed on at a rate of 1kHz (typ) and is on for 25% of the 1ms period. Thus the average current flowing through a LED that is turned on, is about 0.25 x ( $V_{LED} - V_F$ )/R.  $V_F$  is the forward voltage of the LED. The resistor value should be chosen according to the LED's current/light intensity requirements.

## **Serial Interface**

The MAX14915 communicates with the host controller through a high-speed SPI serial interface. The interface has three logic inputs: clock (CLK), chip select ( $\overline{CS}$ ), serial data in (SDI), and one data out (SDO). The SDO is three-stated when  $\overline{CS}$  is high. The maximum SPI clock rate is 10MHz. The SPI interface logic complies with SPI clock polarity CPOL = 0 and clock phase CPHA = 0.

The MAX14915 SPI can either be operated in addressed SPI mode or in daisy-chain mode. Addressed SPI (DAISY = low) allows direct communication with up to four MAX14915 on a shared SPI using a single, shared CSsignal. Addressed SPI offers the advantage direct chip access and getting global diagnostics in the same SPI

cycle. Addressed SPI supports both single cycle and burst mode read/writing.

Daisy chained SPI is enabled by driving DAISY = high. In daisy-chain mode, the first SDO byte provides the channel diagnostics based only on driver overload. Daisy-chain mode provides limited features like reduced diagnostics and configuration.

Since the power-on default configuration is different in daisy-chain mode versus addressed SPI modes, the MAX14915 does not support dynamic switching between daisy-chain and addressed SPI modes during operation.

# Addressed SPI Chip Addressing (A1, A0)

In addressed SPI mode, a SPI master can communicate with up to four MAX14915 devices on a shared, non-daisy-chained SPI bus with one single/shared  $\overline{CS}$  through chip addressing. Each chip on the shared SPI is assigned an individual chip address through the logic input pins A1 and A0, see Table 3.

The SPI master addresses a specific chip by sending the appropriate A1, A0 logic in the first and second bits of the SPI read/write command. The MAX14915 monitors the SPI-address in each SPI read/write cycle and responds appropriately when the address matches the programmed address for that IC.

# Addressed SPI In-Band Diagnostic Fault Signaling

In every addressed SPI cycle, the MAX14915 returns six bits in SDO within the first eight SPI CLK cycles. These six bits include the global short-to-V<sub>DD</sub>, wire-break-on, wire-break-off, overload, overcurrent as well as a global diagnostics bit. The global fault bit, GlobIF, is the logic OR of the ComErr, SupplyErr and ThErr bits. These five diagnostic bits allows for fast identification of the specific channel in fault or global fault condition.

During an SPI write cycle, the second SDO byte returns eight fault bits, one bit associated with each OUT channel. These bits are the logic OR of the diagnostic faults.

**Table 3. SPI Device Address Selection**

| A1   | Α0   | DEVICE ADDRESS |

|------|------|----------------|

| LOW  | LOW  | 00             |

| LOW  | HIGH | 01             |

| HIGH | LOW  | 10             |

| HIGH | HIGH | 11             |

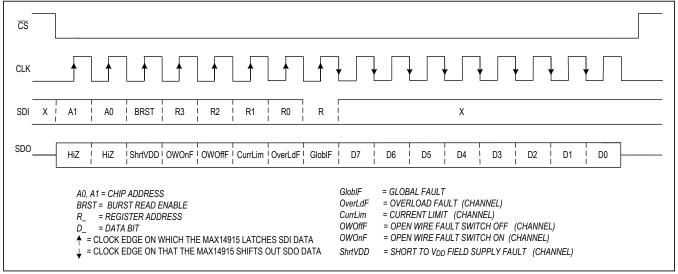

# Single-Cycle Addressed SPI Read

The following shows the SPI read command in addressed SPI mode (DAISY = low).

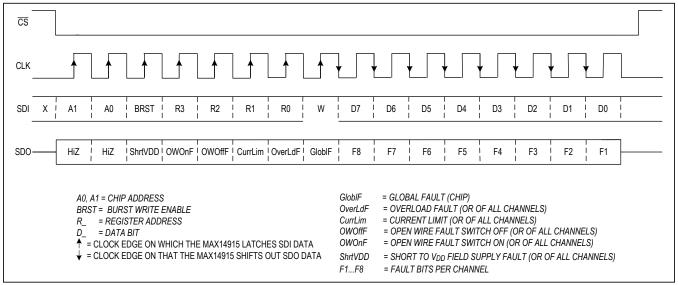

## Single-Cycle Addressed SPI Write

The following shows the SPI write command in SPI addressed mode (DAISY = low):

The F\_ bits in the second byte of SDO write cycle are the per-channel fault bits. These are the logic OR of the channel fault bits in the OvlChF, CurrLimChF, OwOffChF, OwOnChF and ShtVDDChF registers. If only one OUT channel has diagnostic fault(s), then an SPI Write command provides full diagnostic information: the channel and the all faults. The only reason to subsequently read the diagnostic registers is to reset the diagnostic bits.

Figure 10. Addressed SPI Single Read Command

Figure 11. Addressed SPI Single Cycle Write Command

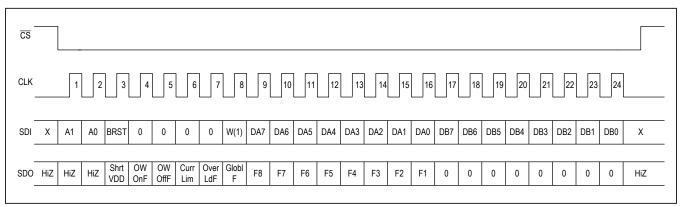

#### **SPI Burst Write**

In addressed SPI mode (DAISY = low), burst SPI writing is supported. This allows efficient writing of registers that are commonly accessed: SetOUT, SetSLED and SetFLED. Burst SPI uses one SPI cycle and one register address to write to multiple consecutive registers. A burst write is enabled through the BRST bit in the SDI command byte. If the BRST bit is set, the MAX14915 expects an SPI write cycle writing to 2 or 3 registers. The chip-select input  $\overline{(CS)}$  must be held low during the entire burst write cycle. The

SPI clock continues clocking throughout the burst cycle. Only the initial register address (0x00) is specified in the SDI command byte, followed by two or three bytes of data. The burst length is defined by the number of CLK clocks in the SPI cycle: for a 2 register burst write, 24 clocks are needed if CRC is not used, and 32 clocks are needed with CRC. For a 3 register burst write, 32 SPI clocks are needed without CRC enabled, and 40 clocks with CRC. The burst cycle ends when the  $\overline{\text{CS}}$  is driven high.

Figure 12. Addressed SPI Single Cycle Write Command

Figure 13. Addressed SPI Three Bytes Burst Write Command

Figure 14. Addressed SPI Two Bytes Burst Write Command with CRC

(\*) CRC\_ bit are calculated on all the data send before CRC\_ bits.

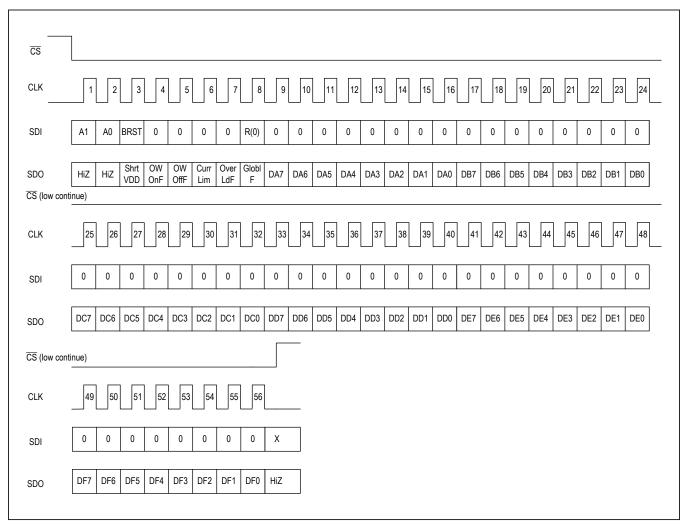

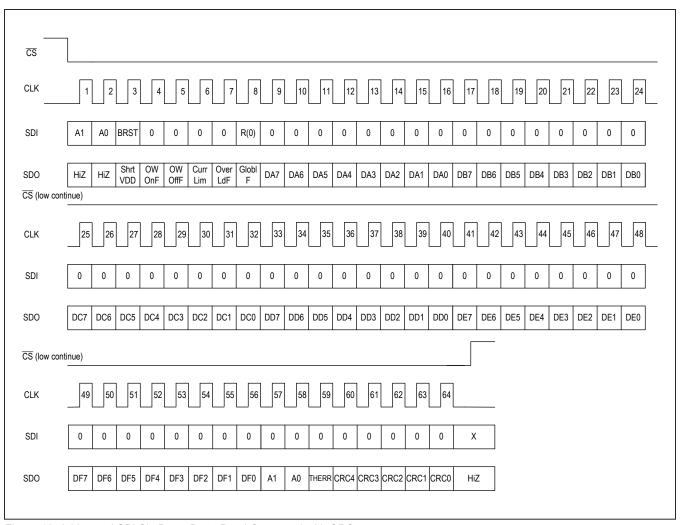

#### **SPI Burst Read**

In addressed SPI mode (DAISY = low), burst SPI reading is supported. Burst SPI reading allows efficient reading of multiple registers in one SPI cycle. The MAX14915 only supports burst reading of the diagnostic registers OvlChF, CurrLimF, OwOffChF, OwOnChF, ShtVDDChF, GloblErr.

Set the BRST bit in the SDI command byte to signal a burst SPI cycle. The first register address must be 0x04 (OvlChF register) and it must end with the register 0x09 (GloblErr register). Total of six consecutive registers can be read within the burst read cycle. If the burst read command ends before the GloblErr register, a communication error is signaled on  $\overline{\text{COMERR}}$  pin.

Figure 15. Addressed SPI Six Bytes Burst Read Command

Figure 16. Addressed SPI Six Bytes Burst Read Command with CRC

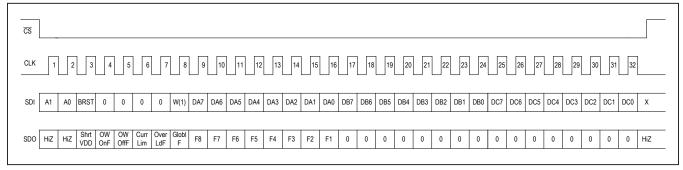

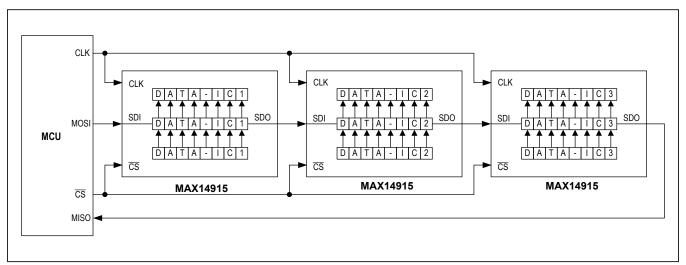

# **Daisy-Chained SPI**

Daisy-chained SPI mode (DAISY = high) allows communication with multiple MAX14915 with one  $\overline{\text{CS}}$ signal in one SPI cycle. In daisy-chain mode, register access is not possible. Switching between daisy chain and addressed modes is not supported. Daisy-chain mode only allows turning the OUT\_ switches on/off and reading per channel thermal overload diagnostics as well as chip thermal shutdown.

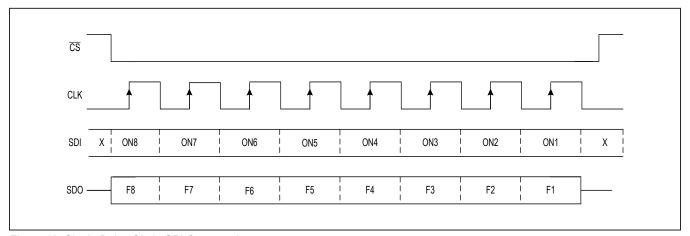

The following shows a single daisy chain mode SPI cycle without CRC enabled (CRCEN = low), based on only one device in the SPI chain:

The ON\_ bits turn the OUT\_ switches on. The F\_ bits are per-channel diagnostics, and are the same as the OVL\_ bits in the OvlChF register. The F\_ bits are latched and are, therefore, only cleared on the following SPI cycle if the fault has disappeared before the following SPI cycle. The F\_ bits are filtered, so do not go active when a lamp load is detected. In thermal chip shutdown, all F\_ bits are set to 1.

Daisy-chain SPI mode also supports CRC error detection/correction, which lengthens the minimum SPI cycle to 16 CLK clocks per MAX14915.

Figure 17. Daisy-Chaining Diagram of Three MAX14915

Figure 18. Single Daisy-Chain SPI Command

# **Checking of Clocks on the Serial Interface**

In addressed SPI and daisy-chain SPI modes, the MAX14915 checks that the number of clock cycles in one SPI cycle (from falling edge of  $\overline{CS}$  to rising edge of  $\overline{CS}$ ) is a multiple of 8, with 8 clocks minimum for daisy-chain mode and 16 clocks minimum for addressed SPI modes. The expected number of clocks is scaled according to CRCEN setting and Burst mode settings. If the number of clock cycles differs from the expected, then the SPI command is not executed and an SPI error is signaled through the COMERR pin.

#### **CRC Error Detection on the Serial Interface**

CRC error detection of the serial data can be enabled to minimize incorrect operation/misinformation due to data corruption of the SDI/SDO signals. If error detection is enabled, then the MAX14915:

- 1) Performs error detection on the SDI data that it receives from the controller, and

- 2) Calculates a CRC on the SDO data and appends a check byte to the SDO diagnostics/status data that it sends to the controller.

This ensures that both the data that it receives from the controller (setting/configuration) and the data that it sends to the controller (diagnostics/status) have a low likelihood of undetected errors.

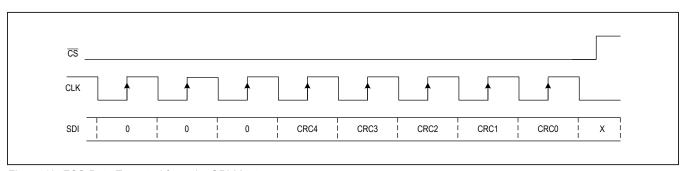

Setting the CRCEN input high enables CRC error detection. A CRC Frame Check Sequence (FCS) is then sent along with each serial transaction. The 5-bit FCS is based on the generator polynomial X5 + X4 + X2 + 1 with CRC starting value = 11111.

When CRC is enabled, the MAX14915 expects a check byte appended to the SDI program/configure data that it receives. The check byte has the following format:

|          |       | _    |        |

|----------|-------|------|--------|

| Table 4. | Valid | Data | Lenath |

| DAISY | CRCEN | R/W BIT | BRST BIT | VALID DATA LENGTH (*) |

|-------|-------|---------|----------|-----------------------|

| 0     | 0     | 1       | 0        | 16                    |

| 0     | 0     | 1       | 1        | 24 or 32              |

| 0     | 1     | 1       | 0        | 24                    |

| 0     | 1     | 1       | 1        | 32 or 40              |

| 0     | 0     | 0       | 0        | 16                    |

| 0     | 0     | 0       | 1        | 56                    |

| 0     | 1     | 0       | 0        | 24                    |

| 0     | 1     | 0       | 1        | 64                    |

| 1     | 0     | х       | х        | 8xN (**)              |

| 1     | 1     | Х       | Х        | 16xN (**)             |

<sup>(\*)</sup> This is the number of CLK rising edges between  $\overline{CS}$  falling and rising edges

<sup>(\*\*)</sup> N is an integer number of daisy-chained devices

Figure 19. FCS Byte Expected from the SPI Master

The five FCS bits (CR\_) are calculated on all the data sent in one SPI command including the three "0" in the MSBs of the check byte. Therefore, the CRC is calculated from 8 + 3 bits up to 56 + 3 bits in case of burst command. CR0 is the LSB of the FCS.

The MAX14915 verifies the received FCS. If no error is detected, the MAX14915 sets the OUT\_ output switches and/or changes configuration per the SDI data. If a CRC error is detected, then the MAX14915 does not change the OUT\_ outputs and/or does not change its configuration. Instead, the MAX14915 sets the COMERR logic output low (i.e., the open-drain COMERR NMOS output transistor is turned on).

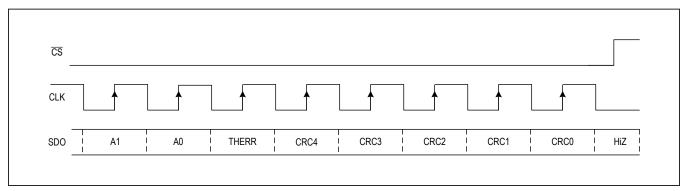

The check byte that the MAX14915 appends to the SDO data has the format seen in <u>Figure 20</u> when the DAISY pin is low.

A1 and A0 are the level for A1/A0 pins while THERR bit is set when a chip thermal shutdown event has occurred.

CR\_ are the CRC bits that the MAX14915 calculates on the SDO data, including the A1, A0, and THERR bits. This allows the controller to check for errors on the SDO data received from the MAX14915.

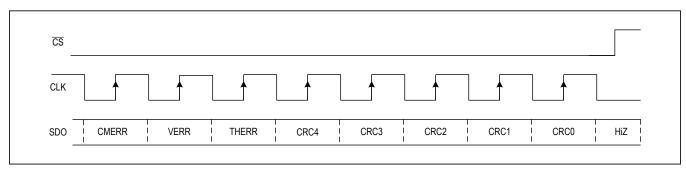

The CMERR is set when either a SPI or SYNCH pin WatchDog event has occurred.

The THERR bit is set when either the thermal warning or the thermal shutdown occurs. The VERR bit in FCS byte corresponds to the SupplyErr bit in the Interrupt register.

Figure 20. FCS Byte Sent by the MAX14915 to SPI Master (SPI Addressed Mode)

Figure 21. FCS Byte Sent by the MAX14915 to SPI Master in Daisy-Chain Mode

# **Register Map**

|                | REGIS-<br>TER<br>ADDRESS | ACCESS<br>TYPE | BIT 7           | BIT 6           | BIT 5         | BIT 4            | BIT 3            | BIT 2            | BIT 1          | BIT 0            |

|----------------|--------------------------|----------------|-----------------|-----------------|---------------|------------------|------------------|------------------|----------------|------------------|

| SetOUT         | 0x00                     | R/W            | On8             | On7             | On6           | On5              | On4              | On3              | On2            | On1              |

| SetFLED        | 0x01                     | R/W            | FLED8           | FLED7           | FLED6         | FLED5            | FLED4            | FLED3            | FLED2          | FLED1            |

| SetSLED        | 0x02                     | R/W            | SLED8           | SLED7           | SLED6         | SLED5            | SLED4            | SLED3            | SLED2          | SLED1            |

| Interrupt      | 0x03                     | R              | ComErr          | SupplyErr       | ThErr         | ShtVdd-<br>Fault | OWOn-<br>Fault   | OWOff-<br>Fault  | CurrLim        | OverLd-<br>Fault |

| OvlChF         | 0x04                     | R              | OVL8            | OVL7            | OVL6          | OVL5             | OVL4             | OVL3             | OVL2           | OVL1             |