# Dual ORing, Single Hot-Swap Controller with Accurate Current Monitoring

### **General Description**

The MAX15068 offers ORing function and hot-swap features for two input-supply-rail applications requiring the safe insertion and removal of circuit line cards from a live backplane. The device integrates dual ORing MOSFET controllers, a single hot-swap controller, electronic circuit-breaker protection, and power monitoring in a single package. The device operates on 2.9V to 18V supply voltages.

The device regulates the forward voltage drop across the ORing MOSFETs to ensure smooth current transfer from one supply to the other without oscillation. The ORing MOSFET turns on quickly to reduce the load voltage drop during supply switchover. If the input supply fails or is shorted, a fast turn-off minimizes reverse-current transients.

The device implements a foldback current limit during hotswap startup in order to control inrush current, thereby keeping the hot-swap MOSFET under safe operating area (SOA). After the hot-swap startup cycle is completed, onchip comparators provide active current-limit protection against short-circuit and overcurrent faults. The load is disconnected from the input quickly in the event of a fault condition.

The device provides a current-sense amplifier output. A voltage proportional to the current delivered to the system can be read directly at the IPMON pin.

The device is factory-calibrated to deliver accurate overcurrent protection with  $\pm 5\%$  accuracy. During an overcurrent-fault condition, the device enters an autoretry mode. The device features an adjustable slew-rate control during startup. Additional features include power-good and fault-indicator outputs.

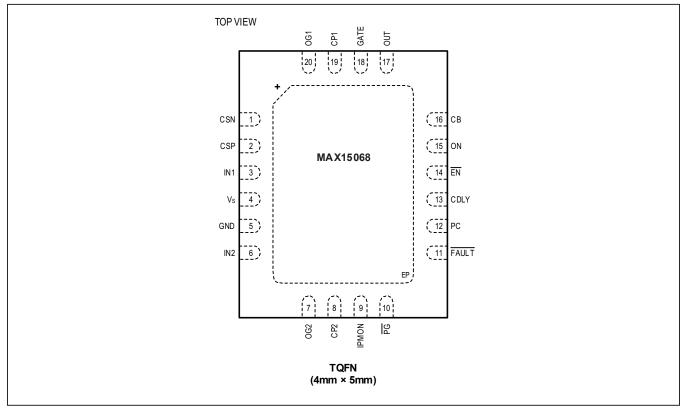

The MAX15068 is available in a 20-pin, (4mm x 5mm) TQFN package and is specified from a -40°C to +125°C operating temperature range.

### **Benefits and Features**

- 2.9V to 18V Operating Voltage Range (ORing and Hot Swap)

- Seamless Power Transition of Redundant Supplies

- Controls n-Channel MOSFETs

- < 0.5µs Reverse Turn-Off Time</li>

- Precision Current Monitoring

- Adjustable Slew-Rate Control

- Adjustable Current-Limit Fault Delay

- Adjustable Circuit-Breaker Current Threshold

- Inrush Current Regulated at Startup

- Adjustable Undervoltage Lockout

- Small (4mm x 5mm) TQFN Package

### **Applications**

- Baseband Station

- Redundant Power Supplies

- Supply Holdup

- Computer Systems and Servers

- Telecom Networks

- Storage Bridge Bay

Ordering Information appears at end of data sheet.

# Dual ORing, Single Hot-Swap Controller with Accurate Current Monitoring

### **Absolute Maximum Ratings**

| IN1, IN2 to GND                | 1V to +24V                            |

|--------------------------------|---------------------------------------|

| PG, EN, FAULT, CSN to GND      | 0.3V to +24V                          |

| CSP to GNDMax (-               | 0.3V, V <sub>IN</sub> - 0.6V) to +24V |

| V <sub>S</sub> to GND          | -0.3V to +6V                          |

| ON, PC, IPMON, CB, CDLY to GND | 0.3V to (V <sub>S</sub> + 0.3V)       |

| CSP to CSN                     | -0.3V to +0.3V                        |

| OUT to GND                     | 0.3V to +24V                          |

| GATE to GND                    | 0.3V to +36V                          |

| GATE to OUT                    | 0.3V to +20V                          |

| CP1 to GND                     | -0.3V to +36V                         |

| CP1 to IN1                     | -0.3V to +14V                         |

| CP2 to GND                     | -0.3V to +36V                         |

| $\begin{array}{c} \text{CP2 to IN2} & -0.3 \text{V to } +14 \text{V} \\ \text{OG1} & (\text{V}_{\text{IN1}} - 0.3 \text{V}) \text{ to } (\text{V}_{\text{CP1}} + 0.3 \text{V}) \\ \text{OG2} & (\text{V}_{\text{IN2}} - 0.3 \text{V}) \text{ to } (\text{V}_{\text{CP2}} + 0.3 \text{V}) \\ \text{Current into } \overline{\text{EN}}, \overline{\text{PG}}, \overline{\text{FAULT}} & 20 \text{mA} \end{array}$ |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)                                                                                                                                                                                                                                                                                                                                                            |

| 20-Pin TQFN (derate 30mW/ºC above +70°C)2400mW                                                                                                                                                                                                                                                                                                                                                                   |

| Operating Temperature Range40°C to +125°C                                                                                                                                                                                                                                                                                                                                                                        |

| Junction Temperature+150°C                                                                                                                                                                                                                                                                                                                                                                                       |

| Storage Temperature Range65°C to +150°C                                                                                                                                                                                                                                                                                                                                                                          |

| Lead Temperature (soldering, 10s)+300°C                                                                                                                                                                                                                                                                                                                                                                          |

| Soldering Temperature (reflow)+260°C                                                                                                                                                                                                                                                                                                                                                                             |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

| PACKAGE TYPE: 20-PIN TQFN            |           |  |  |  |  |

|--------------------------------------|-----------|--|--|--|--|

| Package Code                         | T2045+1C  |  |  |  |  |

| Outline Number                       | 21-0726   |  |  |  |  |

| Land Pattern Number                  | 90-100091 |  |  |  |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD |           |  |  |  |  |

| Junction to Ambient $(\theta_{JA})$  | 33.5°C/W  |  |  |  |  |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/thermal-tutorial</u>.

### **Electrical Characteristics**

$(V_{IN1} = V_{IN2} = 12V, C_{IN1} = C_{IN2} = C_{VS} = 1\mu\text{F}, T_A = -40^{\circ}\text{C to} + 125^{\circ}\text{C}. Typical values are at T_A = +25^{\circ}\text{C}, unless otherwise noted.) (Note 1)$

| PARAMETER                                         | SYMBOL                | CONDITIONS               | MIN  | ТҮР  | MAX  | UNITS |  |  |  |

|---------------------------------------------------|-----------------------|--------------------------|------|------|------|-------|--|--|--|

| SUPPLY VOLTAGE                                    |                       |                          |      |      |      |       |  |  |  |

| Input Supply Voltage                              | N/                    | Hot swap and ORing       | 2.9  |      | 18   |       |  |  |  |

|                                                   | V <sub>IN</sub>       | Current monitor          | 4.8  |      | 18   | V     |  |  |  |

| Input Supply Current                              | I <sub>IN</sub>       |                          |      | 4    |      | mA    |  |  |  |

| Internal LDO Output Voltage                       | V <sub>S</sub>        |                          | 4.8  | 5    | 5.25 | V     |  |  |  |

| V <sub>S</sub> Undervoltage Lockout               | V <sub>UVLO</sub>     | V <sub>S</sub> rising    | 2.5  | 2.65 | 2.8  | V     |  |  |  |

| V <sub>S</sub> Undervoltage-Lockout<br>Hysteresis | V <sub>UVLO_HYS</sub> |                          |      | 0.07 |      | V     |  |  |  |

| CSP Undervoltage Lockout                          |                       | V <sub>CSP</sub> rising  | 2.4  | 2.49 | 2.58 | V     |  |  |  |

|                                                   | V <sub>CSP_UVLO</sub> | V <sub>CSP</sub> falling | 2.25 | 2.35 | 2.42 | V     |  |  |  |

# Dual ORing, Single Hot-Swap Controller with Accurate Current Monitoring

## **Electrical Characteristics (continued)**

$(V_{IN1} = V_{IN2} = 12V, C_{IN1} = C_{IN2} = C_{VS} = 1\mu\text{F}, T_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}. \text{ Typical values are at } T_A = +25^{\circ}\text{C}, \text{ unless otherwise noted.}) (Note 1)$

| PARAMETER                                                                        | SYMBOL                | CON                                                                                    | DITIONS                                                              | MIN  | TYP                         | MAX  | UNITS |  |

|----------------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------|------|-----------------------------|------|-------|--|

| ORING                                                                            | I                     | J                                                                                      |                                                                      | L    |                             |      | 1     |  |

| ORing MOSFET Forward<br>Regulation Voltage (V <sub>IN</sub> - V <sub>CSP</sub> ) | V <sub>FWD_REG</sub>  |                                                                                        |                                                                      | 7.5  | 10                          | 12.5 | mV    |  |

| ORing MOSFET Reverse Bias<br>Turn-Off Voltage                                    | V <sub>REV_OFF</sub>  | $V_{IN\_}$ - $V_{CSP}$ , $V_{CSP}$ r $V_{OG\_}$ goes low                               | ising ( $V_{CSP} > V_{IN}$ ),                                        | -25  | -20                         | -15  | mV    |  |

| ORing MOSFET Reverse Bias<br>Turn-On Voltage                                     | V <sub>REV_ON</sub>   | V <sub>IN</sub> V <sub>CSP</sub> , V <sub>CSP</sub><br>V <sub>OG</sub> _ goes to forwa | falling, (V <sub>IN</sub> _ > V <sub>CSP</sub> _),<br>ird regulation | -20  | -15                         | -10  | mV    |  |

| ORing MOSFET Reverse Bias<br>Hysteresis Voltage                                  | V <sub>REV_HYS</sub>  | V <sub>REV_OFF</sub> - V <sub>REV_</sub>                                               | ON                                                                   |      | 5                           |      | mV    |  |

| Turn-Off Switch Resistance                                                       | R <sub>DS_OFF</sub>   | V <sub>IN_</sub> - V <sub>CSP</sub> = -50m                                             | V, I = 50mA                                                          |      | 0.8                         |      | Ω     |  |

| Turn-On Switch Resistance                                                        | R <sub>DS_ON</sub>    | $V_{IN} - V_{CSP} = 120r$                                                              | mV, I = 70mA                                                         |      | 2                           |      | Ω     |  |

| ORing MOSFET Gate Drive<br>(V <sub>OG</sub> V <sub>IN</sub> _)                   | V <sub>OG</sub> _     | 2.9V < V <sub>IN</sub> _< 18V                                                          |                                                                      | 5.2  | 11                          | 12   | V     |  |

| ORing MOSFET Fast Turn-On<br>Threshold                                           | V <sub>FWD_ON</sub>   | V <sub>IN</sub> V <sub>CSP</sub> rising                                                |                                                                      |      | 80                          |      | mV    |  |

| ORing MOSFET Fast Turn-Off                                                       | V <sub>FWD_OFF</sub>  | V <sub>IN</sub> V <sub>CSP</sub> falling,<br>regulation                                | V <sub>OG</sub> _goes to forward                                     |      | 40                          |      | mV    |  |

| ORing MOSFET Turn-On Delay                                                       | <sup>t</sup> ON_OG_   | C <sub>GATE</sub> = 10nF, V <sub>IN</sub> - V <sub>CSP</sub> = +0.05V                  |                                                                      |      | 20                          |      | μs    |  |

| ORing MOSFET Turn-Off Delay                                                      | <sup>t</sup> OFF_OG_  | $C_{GATE} = 10nF, V_{IN} - V_{CSP} = -0.05V, V_{OG} = 0.1 x (V_{CP} - V_{IN})$         |                                                                      |      | 300                         | 500  | ns    |  |

| PC to OG2 Delay                                                                  | <sup>t</sup> LH_DLY   | V <sub>PC</sub> falling edge to                                                        | V <sub>OG2</sub> going high                                          |      | 40                          | 65   | μs    |  |

| HOT SWAP                                                                         |                       |                                                                                        |                                                                      |      |                             |      |       |  |

|                                                                                  |                       |                                                                                        | V <sub>CB</sub> = 0V                                                 | 32.9 | 35                          | 37.1 |       |  |

| Circuit-Breaker Accuracy                                                         | V <sub>CB_TH</sub>    | V <sub>CSP</sub> - V <sub>CSN</sub>                                                    | V <sub>CB</sub> = open                                               | 47.5 | 50                          | 52.5 | mV    |  |

|                                                                                  |                       |                                                                                        | V <sub>CB</sub> = V <sub>S</sub>                                     | 61.1 | 65                          | 68.9 |       |  |

| Active Current-Limit Sense<br>Voltage                                            | V <sub>ACL</sub>      |                                                                                        |                                                                      |      | 1.3 х<br>V <sub>CB_TH</sub> |      | mV    |  |

| Fast Comparator Threshold                                                        | V <sub>FC_TH</sub>    | V <sub>CSP</sub> - V <sub>CSN</sub>                                                    |                                                                      |      | 3 х<br>V <sub>CB_TH</sub>   |      | mV    |  |

| Fast Comparator Response<br>Time                                                 | <sup>t</sup> FC_DLY   | V <sub>CSP</sub> - V <sub>CSN</sub> = 300<br>(Note 3)                                  | mV, C <sub>GATE</sub> = 10nF                                         |      | 160                         |      | ns    |  |

|                                                                                  |                       | $V_{\overline{EN}}$ high to $V_{GATE}$                                                 | low                                                                  |      | 20                          | 40   | — μs  |  |

| GATE Off Delay                                                                   | <sup>t</sup> OFF_GATE | V <sub>ON</sub> low to V <sub>GATE</sub> I                                             | ow                                                                   |      | 10                          | 20   |       |  |

| GATE Propagation Delay                                                           | tON_GATE_PD           | V <sub>ON</sub> = step 0.8V to                                                         | 2V                                                                   |      | 10                          | 20   | μs    |  |

| GATE Drive Voltage<br>(V <sub>GATE</sub> - V <sub>OUT</sub> )                    | V <sub>GATE</sub>     | 2.9V < V <sub>IN</sub> _< 18V                                                          |                                                                      | 6    | 11                          |      | V     |  |

| GATE Pullup Current                                                              | IGATE_ON              | V <sub>GATE</sub> - V <sub>OUT</sub> = 0V                                              | ,                                                                    | -13  | -10                         | -7   | μA    |  |

# Dual ORing, Single Hot-Swap Controller with Accurate Current Monitoring

## **Electrical Characteristics (continued)**

$(V_{IN1} = V_{IN2} = 12V, C_{IN1} = C_{IN2} = C_{VS} = 1\mu$ F, T<sub>A</sub> = -40°C to +125°C. Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                          | SYMBOL                                           | CONDITIONS                                                                       | MIN                | TYP                    | MAX  | UNITS                   |

|------------------------------------|--------------------------------------------------|----------------------------------------------------------------------------------|--------------------|------------------------|------|-------------------------|

| GATE Pulldown Current<br>(Timeout) | IGATE_OFF                                        | V <sub>OUT</sub> = 12V, V <sub>GATE</sub> = V <sub>OUT</sub> + 5V                | 350                | 500                    | 650  | μA                      |

| GATE Fast Pulldown Current         | IGATE_FAST_<br>OFF                               | V <sub>OUT</sub> = 12V, V <sub>GATE</sub> = V <sub>OUT</sub> + 5V                | 75                 | 200                    | 260  | mA                      |

| HOT-SWAP FOLDBACK                  |                                                  |                                                                                  |                    |                        |      |                         |

| Minimum CB Voltage                 | V <sub>CB_FBMAX</sub>                            | (V <sub>CSP</sub> - V <sub>CSN</sub> ) = 12V                                     | 3                  | 6.7                    | 10.7 | %<br>V <sub>CB_TH</sub> |

| Minimum Foldback Voltage           | V <sub>FBMIN</sub>                               | V <sub>CSP</sub> - V <sub>OUT</sub> , at V <sub>CB</sub> = V <sub>CB_FBMAX</sub> | 1                  | 2.1                    | 3.2  | V                       |

| Maximum Foldback Voltage           | V <sub>FBMAX</sub>                               | V <sub>CSP</sub> - V <sub>OUT</sub> , at V <sub>CB</sub> = V <sub>CB_TH</sub>    | 9                  | 10                     | 11   | V                       |

| CURRENT-SENSING INPUT              |                                                  |                                                                                  |                    |                        |      |                         |

| CSP Input Current                  | I <sub>CSP</sub>                                 | V <sub>CSP</sub> = 12V                                                           |                    | 0.5                    | 1.0  | mA                      |

| CSN Input Current                  | I <sub>CSN</sub>                                 | V <sub>CSN</sub> = 12V                                                           | 100                | 200                    | 400  | μA                      |

| CDLY                               |                                                  |                                                                                  |                    |                        |      |                         |

| CDLY Upper Threshold               | V <sub>CDLY_U</sub>                              | V <sub>CDLY</sub> rising                                                         | 1.1                | 1.2                    | 1.3  | V                       |

| CDLY Lower Threshold<br>Hysteresis | V <sub>CDLY_L</sub>                              | V <sub>CDLY</sub> falling                                                        |                    | 0.2                    |      | V                       |

| CDLY Pullup Current                | ICDLY_UP                                         |                                                                                  | -135               | -100                   | -65  | μA                      |

| CDLY Pulldown Current              | ICDLY_DOWN                                       |                                                                                  | 1.1                | 2                      | 2.8  | μA                      |

| CDLY Ratio                         | I <sub>CDLY_DOWN</sub> /<br>I <sub>CDLY_UP</sub> |                                                                                  | 1.2                | 2                      | 3.2  | %                       |

| POWER-GOOD (PG)                    |                                                  |                                                                                  |                    |                        |      |                         |

| PG Threshold OUT                   | V <sub>PG_OUT</sub>                              | V <sub>GATE</sub> > (5V + V <sub>OUT</sub> )                                     |                    | 0.9 x V <sub>CSP</sub> |      | V                       |

| PG Threshold GATE                  | VPG_GATE                                         | V <sub>GATE</sub> - V <sub>OUT</sub>                                             |                    | 4.2                    |      | V                       |

| PG Detection Timeout               | tpg_startup                                      |                                                                                  | 55                 | 70                     | 85   | ms                      |

| PG Assertion Delay                 |                                                  |                                                                                  | 13                 | 16                     | 19   | ms                      |

| OUTPUTS (FAULT, PG)                |                                                  | I                                                                                | 1                  |                        |      | 1                       |

| FAULT, PG Output Voltage Low       | V <sub>OL</sub>                                  | I <del>PG</del> = I <del>FAULT</del> = 1mA                                       |                    |                        | 0.4  | V                       |

| FAULT, PG Output Voltage High      | V <sub>OH</sub>                                  | IPG = IFAULT = 1µA                                                               | V <sub>S</sub> - 1 | V <sub>S</sub> - 0.6   |      | V                       |

| FAULT, PG Leakage Current          | ІОН                                              | V <sub>PG</sub> = V <sub>FAULT</sub> = 18V                                       | -1                 |                        | +20  | μA                      |

| FAULT, PG Pullup Current           | I <sub>PU</sub>                                  | V <sub>PG</sub> = V <sub>FAULT</sub> = 1.5V                                      | -13                | -10                    | -7   | μA                      |

# Dual ORing, Single Hot-Swap Controller with Accurate Current Monitoring

## **Electrical Characteristics (continued)**

$(V_{IN1} = V_{IN2} = 12V, C_{IN1} = C_{IN2} = C_{VS} = 1\mu\text{F}, T_A = -40^{\circ}\text{C to} + 125^{\circ}\text{C}. Typical values are at T_A = +25^{\circ}\text{C}, unless otherwise noted.) (Note 1)$

| PARAMETER                                  | SYMBOL                |                                                                        | CONDITIONS                                                                           | MIN    | TYP    | MAX                  | UNITS |

|--------------------------------------------|-----------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------|--------|----------------------|-------|

| INPUTS                                     |                       | ·                                                                      |                                                                                      |        |        |                      |       |

| ON, PC, EN Turn-On Threshold               | V <sub>ON_TH</sub>    | $V_{ON}, V_{PC}, V_{\overline{EI}}$                                    | $V_{ON}$ , $V_{PC}$ , $V_{\overline{EN}}$ rising                                     |        | 1.22   | 1.32                 | V     |

| ON, PC, EN Turn-On Threshold<br>Hysteresis | V <sub>ON_HYS</sub>   | V <sub>ON</sub> , V <sub>PC</sub> , V <sub>EI</sub>                    | $\overline{{}_{\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ | 70     | 123    | 180                  | mV    |

| ON Fault Reset Threshold<br>Voltage        | V <sub>ON_RESET</sub> | V <sub>ON</sub> falling                                                |                                                                                      | 0.5    | 0.6    | 0.7                  | V     |

| ON, PC Input Leakage Current               | I <sub>LEAK</sub>     | $V_{ON}, V_{PC} = 0$                                                   | to 2.5V                                                                              | -1     |        | +1                   | μA    |

| ON, PC Clamp Voltage                       |                       | I <sub>SINK</sub> = 1µA                                                |                                                                                      |        | 3      |                      | V     |

| ON, PC Clamp Sink                          |                       | V <sub>ON</sub> , V <sub>PC</sub> = 5\                                 | /                                                                                    |        | 300    |                      | μA    |

| EN Pullup Current                          | I <sub>PU</sub>       | $V_{\overline{EN}} = 0V$                                               |                                                                                      | -13    | -10    | -7                   | μA    |

| CB THREE-STATE INPUT                       | 1                     | 1                                                                      |                                                                                      |        |        |                      |       |

| CB Input Low Current                       | IIN LOW               | V <sub>CB</sub> = 0.4V                                                 |                                                                                      | -75    |        |                      | μA    |

| CB Input High Current                      | I <sub>IN_HIGH</sub>  | V <sub>CB</sub> = V <sub>S</sub> - 0.2                                 | V                                                                                    |        |        | +75                  | μA    |

| CB Input Open-Current Voltage              | V <sub>CB_OPEN</sub>  | Force ±4µA into unconnected CB pin; then measure voltage on the CB pin |                                                                                      | 1.0    |        | V <sub>S</sub> - 1   | V     |

| CB Low Voltage                             | VIL                   | V <sub>CB</sub> rising                                                 |                                                                                      | 0.4    |        |                      | V     |

| CB High Voltage                            | VIH                   | V <sub>CB</sub> falling, rel                                           | ative to V <sub>S</sub>                                                              |        |        | V <sub>S</sub> - 0.2 |       |

| CURRENT MONITORING                         | 1                     | 1                                                                      |                                                                                      | -      |        |                      |       |

| Current Monitor vs.                        | Viewen                | V <sub>S</sub> rising                                                  |                                                                                      | 4.1    | 4.16   | 4.23                 | V     |

| Undervoltage Lockout                       | VIPMON_UVLO           | Hysteresis                                                             | 1                                                                                    |        | 0.1    |                      | v     |

|                                            |                       |                                                                        | T <sub>A</sub> = +25°C                                                               | -80    |        | +80                  | μV    |

|                                            |                       | V <sub>CSP</sub> = 12V                                                 | $T_A = 0^{\circ}C$ to +85°C                                                          | -200   |        | +200                 |       |

| IPMON Offset (Note 2)                      | V <sub>IPMON_0</sub>  |                                                                        | T <sub>A</sub> = -40°C to +125°C                                                     | -240   |        | +240                 |       |

|                                            |                       | V <sub>CSP</sub> = 4.8V<br>to 18V                                      | $T_{A} = -40^{\circ}C \text{ to } +125^{\circ}C$                                     | -300   |        | +300                 |       |

|                                            |                       |                                                                        | T <sub>A</sub> = +25°C                                                               | 71.315 | 71.565 | 71.815               | V/V   |

|                                            |                       | V <sub>CSP</sub> = 12V                                                 | $T_A = 0^{\circ}C$ to +85°C                                                          | 71.136 | 71.565 | 71.994               |       |

| IPMON Gain (Note 2)                        | G <sub>IM</sub>       |                                                                        | T <sub>A</sub> = -40°C to +125°C                                                     | 70.992 | 71.565 | 72.138               |       |

|                                            |                       | V <sub>CSP</sub> = 4.8V<br>to 18V                                      | $T_{A} = -40^{\circ}C \text{ to } +125^{\circ}C$                                     | 70.992 | 71.565 | 72.138               |       |

# Dual ORing, Single Hot-Swap Controller with Accurate Current Monitoring

### **Electrical Characteristics (continued)**

(V<sub>IN1</sub> = V<sub>IN2</sub> = 12V, C<sub>IN1</sub> = C<sub>IN2</sub> = C<sub>VS</sub> = 1µF, T<sub>A</sub> = -40°C to +125°C. Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                     | SYMBOL              | CONDITIONS                                                                                                                                                                       | MIN   | TYP       | MAX  | UNITS |

|-----------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|------|-------|

| Current Monitoring Total<br>Accuracy (Note 3) | VIPMON_<br>ACCURACY |                                                                                                                                                                                  | -3    |           | %    |       |

|                                               |                     |                                                                                                                                                                                  | -1    |           |      | +1    |

|                                               |                     | $V_{CSP} = 12V, R_{SENSE} = 3m\Omega, I_{LOAD} = 5A, (V_{CSP} - V_{CSN}) = 15mV, T_A = +25^{\circ}C, V_{IPMON} - ACCURACY = ((V_{IPMON} - 1.073V) / 1.073V) x 100$               | -0.65 | .65 +0.65 |      |       |

|                                               |                     | $V_{CSP} = 12V, R_{SENSE} = 3m\Omega, I_{LOAD} = 8A,$<br>$(V_{CSP} - V_{CSN}) = 24mV, T_A = +25^{\circ}C,$<br>$V_{IPMON\_ACCURACY} = ((V_{IPMON} - 1.7175V)/1.7175V) \times 100$ | -0.5  |           | +0.5 |       |

| CMRR (Note 4)                                 | IPMON_CMRR          | V <sub>CSP</sub> = 4.8V to 18V                                                                                                                                                   | 102   |           |      | dB    |

| Output Voltage Range                          | VIPMONMAX           | $V_{CSP} = 4.8V$ to 18V, -40°C $\leq T_A \leq +125$ °C                                                                                                                           | 1.72  |           |      | V     |

| IPMON Voltage Clamp                           | VIPMON_CLMP         | $V_{CSP}$ - $V_{CSN}$ ≥ 36mV, $V_{CSP}$ = 4.8V to 18V,<br>-40°C ≤ $T_A$ ≤ +125°C                                                                                                 | 2.1   | 2.3       | 2.5  | V     |

**Note 1:** All devices are 100% production tested at  $T_A = +25$ °C. Limits over temperature are guaranteed by design.

Note 2: Gain and offset are defined as V<sub>IPMON1</sub> = V<sub>IPMON</sub> with Vi<sub>1</sub> = (V<sub>CSP</sub> - V<sub>CSN</sub>) = 3mV, V<sub>IPMON2</sub> = V<sub>IPMON</sub> with Vi<sub>2</sub> = (V<sub>CSP</sub> - V<sub>CSN</sub>) = 24mV, G<sub>IM</sub> = (V<sub>IPMON2</sub> - V<sub>IPMON1</sub>)/(Vi<sub>2</sub> - Vi<sub>1</sub>), V<sub>IPMON\_OS</sub> = V<sub>IPMON1</sub> - G<sub>IM</sub> x Vi<sub>1</sub>.

Note 3: Accuracy over the entire operating range can be determined combining the specified value of the related offset and gain in the range.

Note 4: CMRR is calculated as:

$V_{REF} = V_{IPMON}$  with  $V_{CSP} - V_{CSN} = 3mV$  at  $V_{REF} = V_{CSP} = 12V$ ,  $V_{CM} = V_{IPMON}$  with  $V_{CSP} - V_{CSN} = 3mV$  at  $4.8V < V_{CSP} < 18V$ ,

$$CMRR = 20 \times LOG(ABS((12 - V_{CSP})/(V_{REF} - V_{CM})) \times G_{IM}),$$

where GIM is the differential gain defined in the Electrical Characteristics table.

# Dual ORing, Single Hot-Swap Controller with Accurate Current Monitoring

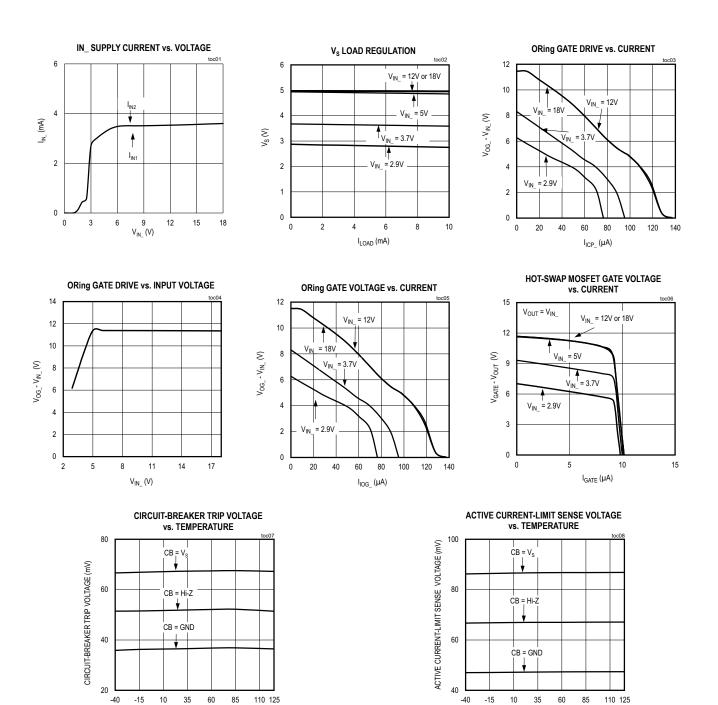

## **Typical Operating Characteristics**

(V<sub>IN1</sub> = V<sub>IN2</sub> = 12V, C<sub>IN1</sub> = C<sub>IN2</sub> = C<sub>VS</sub> = 1 $\mu$ F, R<sub>SENSE</sub> = 3m $\Omega$ , unless otherwise noted.)

TEMPERATURE (°C)

TEMPERATURE (°C)

# Dual ORing, Single Hot-Swap Controller with Accurate Current Monitoring

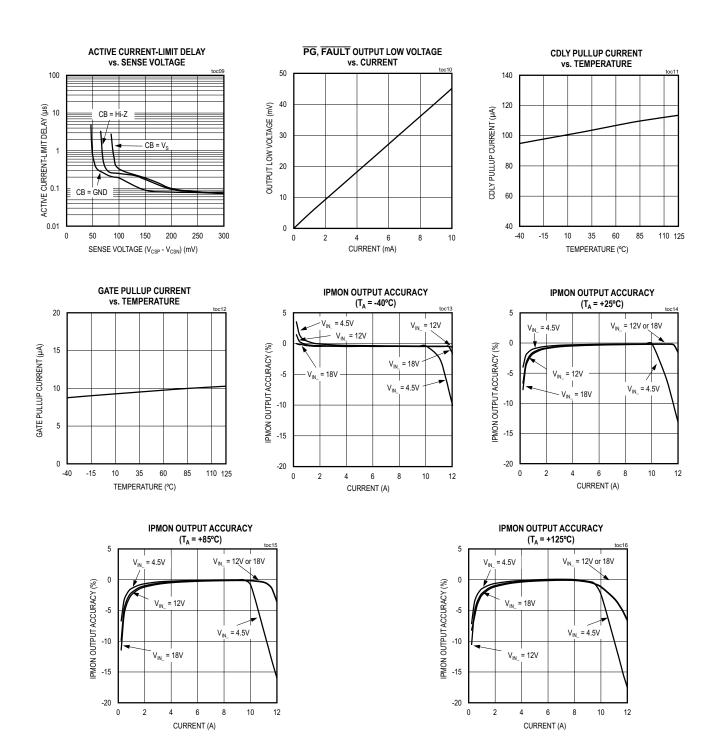

## **Typical Operating Characteristics (continued)**

(V<sub>IN1</sub> = V<sub>IN2</sub> = 12V, C<sub>IN1</sub> = C<sub>IN2</sub> = C<sub>VS</sub> = 1 $\mu$ F, R<sub>SENSE</sub> = 3m $\Omega$ , unless otherwise noted.)

# Dual ORing, Single Hot-Swap Controller with Accurate Current Monitoring

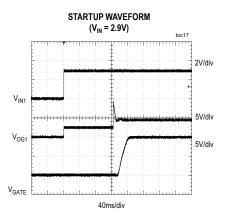

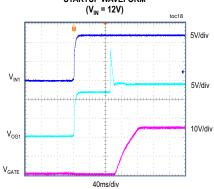

## **Typical Operating Characteristics (continued)**

(V<sub>IN1</sub> = V<sub>IN2</sub> = 12V, C<sub>IN1</sub> = C<sub>IN2</sub> = C<sub>VS</sub> = 1 $\mu$ F, R<sub>SENSE</sub> = 3m $\Omega$ , unless otherwise noted.)

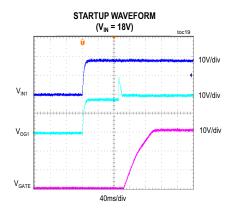

STARTUP WAVEFORM

# Dual ORing, Single Hot-Swap Controller with Accurate Current Monitoring

## **Pin Configuration**

## **Pin Description**

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                        |

|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | CSN   | Input Current Sense Negative Input                                                                                                                                                                                                                                                                                                              |

| 2   | CSP   | Input Current Sense Positive Input                                                                                                                                                                                                                                                                                                              |

| 3   | IN1   | Positive Supply 1 Input and MOSFET Gate Drive Return                                                                                                                                                                                                                                                                                            |

| 4   | Vs    | Internal Regulator Output. Bypass $V_S$ to GND with a 1µF capacitor.                                                                                                                                                                                                                                                                            |

| 5   | GND   | Ground                                                                                                                                                                                                                                                                                                                                          |

| 6   | IN2   | Positive Supply 2 Input and MOSFET Gate Drive Return                                                                                                                                                                                                                                                                                            |

| 7   | OG2   | ORing MOSFET 2 Gate Control Output. Connect this pin to the gate of an external n-channel MOSFET for ideal diode control. The gate voltage is limited to approximately 11V above and a diode voltage below IN2. During fast turn-on, a 1A pullup switch charges OG2 from CP2. During fast turn-off, a 3A pulldown switch discharges OG2 to IN2. |

| 8   | CP2   | Charge Pump 2 Output. Connect a capacitor from CP2 to IN2 pin. The value of this capacitor should be approximately 10x the gate capacitance (CISS) of the external MOSFET for ORing diode control. The charge stored on this capacitor is used to pull up the gate during a fast turn-on.                                                       |

| 9   | IPMON | Analog Current Monitor Output Signal. Connect a 560pF/6.3V ceramic capacitor from IPMON to GND.                                                                                                                                                                                                                                                 |

# Dual ORing, Single Hot-Swap Controller with Accurate Current Monitoring

## **Pin Description (continued)**

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10  | PG    | Power Status Output. Open-drain output that is normally pulled high by a 10µA current source to a diode below V <sub>S</sub> . $\overline{PG}$ can be pulled above V <sub>S</sub> using an external pullup. $\overline{PG}$ pulls low when the MOSFET gate drive between GATE and OUT exceeds the gate-to-source voltage of 4.2V and V <sub>OUT</sub> is greater than 90% of V <sub>CSP</sub> . Leave $\overline{PG}$ unconnected if unused. |

| 11  | FAULT | Fault Status Output. Open-drain output that is normally pulled high by a 10 $\mu$ A current source to a diode below V <sub>S</sub> . FAULT can be pulled above V <sub>S</sub> using an external pullup. FAULT pulls low when the circuit breaker is tripped after an overcurrent fault timeout. Leave FAULT unconnected if unused.                                                                                                           |

| 12  | PC    | Priority Control Input. When low, it enables the external ideal diode MOSFET in the IN2 supply path and a high turns it off. Connect PC to an external resistive divider from IN1 to make IN1 the higher priority input supply when IN1 and IN2 are equal. Connect PC to GND if not used.                                                                                                                                                    |

| 13  | CDLY  | Timer Capacitor Terminal. Connect a capacitor between CDLY and GND to set $12ms/\mu F$ duration for current limit before the external hot-swap MOSFET is turned off. The duration of the off-time is $600ms/\mu F$ , resulting in a 2% duty cycle.                                                                                                                                                                                           |

| 14  | ĒN    | Enable Input. Connect $\overline{EN}$ to GND to enable hot-swap control. If $\overline{EN}$ is pulled high, the hot-swap MOSFET is not allowed to turn on. A 10µA current source pulls up $\overline{EN}$ to a diode below V <sub>S</sub> . Upon $\overline{EN}$ going low when ON is high, an internal timer provides a 100ms startup delay for debounce, after which the fault is cleared.                                                 |

| 15  | ON    | On Control Input. When above 1.2V, it turns on the external hot-swap MOSFET and when below 1.1V, it turns it off. Connect ON to an external resistive divider from CSP to monitor the supply undervoltage condition. Pulling voltage of ON pin below 0.6V resets the electronic circuit breaker.                                                                                                                                             |

| 16  | СВ    | Current-Limit Threshold Setting. Connect the CB pin to $V_S$ , GND, or leave CB unconnected to set the circuit-breaker threshold. See Table 1 for details.                                                                                                                                                                                                                                                                                   |

| 17  | OUT   | Load Output. Connect OUT to the source of the external hot-swap MOSFET.                                                                                                                                                                                                                                                                                                                                                                      |

| 18  | GATE  | Hot-Swap MOSFET Gate Drive Output. Connect this pin to the gate of the external n-channel MOSFET for hot-swap control. An internal 10µA current source charges the MOSFET gate. An internal clamp limits the gate voltage to 11V above OUT and a diode voltage below OUT. During turn-off, a 500µA pulldown current discharges GATE to ground. During an output short to ground, a fast 200mA pulldown current discharges GATE to OUT.       |

| 19  | CP1   | Charge Pump 1 Output. Connect a capacitor from CP1 to IN1 pin. The value of this capacitor should be 10x or greater than the gate capacitance of the external MOSFET for ideal diode control. The charge stored on this capacitor is used to pull up the gate during a fast turn-on.                                                                                                                                                         |

| 20  | OG1   | ORing MOSFET 1 Gate Control Output. Connect OG1 to the gate of an external n-channel MOSFET for ideal diode control. The gate voltage is set to approximately 11V above and a diode voltage below IN1. During fast turn-on, a 1A pullup switch charges OG1 from CP1. During fast turn-off, a 3A pulldown switch discharges OG1 to IN1.                                                                                                       |

| _   | EP    | Exposed Pad. Connect EP to the ground plane to provide a low thermal resistance path from the IC junction to the PCB. Do not use EP as the only electrical connection to GND.                                                                                                                                                                                                                                                                |

# Dual ORing, Single Hot-Swap Controller with Accurate Current Monitoring

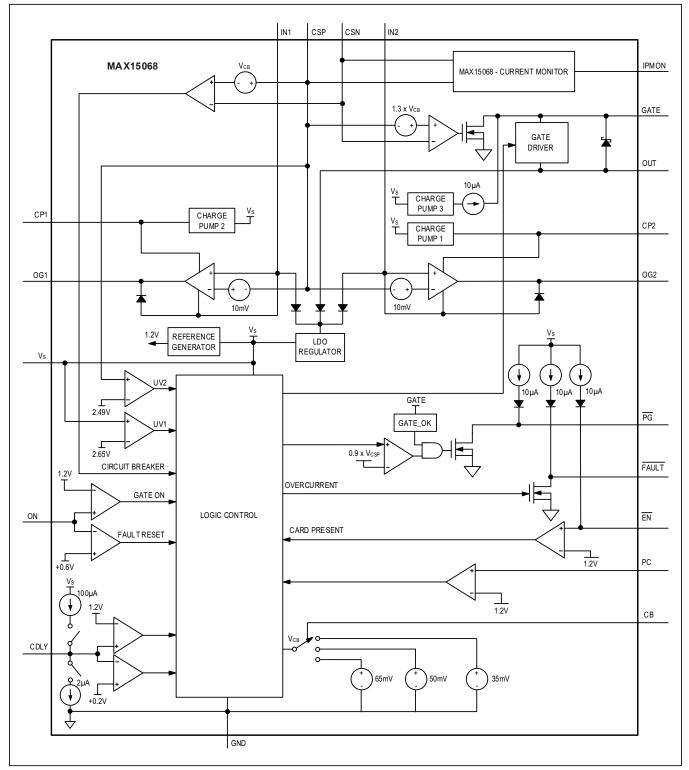

## **Functional Diagram**

# Dual ORing, Single Hot-Swap Controller with Accurate Current Monitoring

### **Detailed Description**

#### Startup

When input voltage is applied to IN\_, CSP comes up to one diode below the higher of IN1 or IN2. The internal LDO regulator powers  $V_S$  from the higher of two inputs as well. When both  $V_S$  and CSP reach their respective UVLO thresholds, the internal charge pumps (CP1 or CP2) for the ORing controller start operating. An internal time starts when both ON is above its threshold and  $\overline{EN}$  is below its threshold. After the timer counts 85ms, the ORing control (OG1 or OG2) begins operating. After another 15ms have elapsed, the hot-swap control (GATE) also starts operating.

### **ORing Control**

#### **ORing Control in Startup**

As soon as the internally generated supply,  $V_S$ , rises above its undervoltage lockout threshold, the internal charge pump is allowed to charge up the CP\_ pins. Because the ideal diode MOSFETs are connected in parallel as a diode-OR, the CSP pin voltage selects the highest of the supplies at the IN1 and IN2 pins. The MOSFET associated with the lower input supply voltage is turned off by the corresponding gate drive amplifier.

At power-up the CP\_ and OG\_ pin voltages are at the IN\_ voltage level. CP\_ starts ramping up after VS clears its undervoltage lockout level.

If the amplifier senses a forward voltage drop greater than 80mV between IN and CSP then the OG\_ pin is pulled to CP\_ to quickly turn on the MOSFET. If the amplifier senses a reverse voltage drop greater than 10mV between CSP and IN\_, then the OG\_pin is pulled to IN\_ to quickly turn off the MOSFET. With the ideal diode MOSFETs acting as an input supply diode-OR, the CSP pin voltage rises to the highest of the supplies at the IN1 and IN2 pins. The stored charge in an external capacitor connected between the CP\_ and IN\_ pins provides the charge needed to quickly turn on and off the ideal diode MOSFET. An internal charge pump charges the external capacitors at the CP\_ pins. The OG\_ pin sources current from the CP\_ pin and sinks current into the IN\_ and GND pins.

### **ORing MOSFET Regulation Mode**

When the ideal diode MOSFET is turned on, the gate drive amplifier controls OG\_ to servo the forward voltage drop (V<sub>IN</sub> - V<sub>CSP</sub>) across the MOSFET to 10mV. If the load current causes more than 10mV of voltage drop, across the FET, then the OG\_ voltage rises to 11V (typ) above IN\_ to fully enhance the MOSFET. For large output

currents, the MOSFET's gate is driven fully on and the voltage drop is equal to  $I_{LOAD} \times R_{DS(ON)}$  of the MOSFET.

#### **Hot-Swap Control**

#### Hot-Swap in Startup

Once the output is enabled, the device provides controlled application of power to the load.

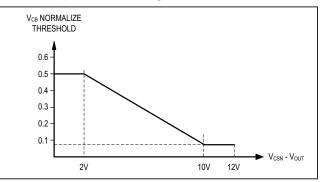

An external capacitor connected to the GATE pin allows the user to program the slew rate to a value lower than the default. During startup, a foldback current limit is active to protect the external hot-swap MOSFET to operate within the SOA (Figure 1).

An internal timer is activated to count for 70ms, which is the maximum time duration for the startup phase. The startup phase is completed when the voltage at OUT rises above the power-good threshold (0.9 x VCSP typical) and hot-swap GATE to OUT voltage exceeds 4.2V even though the 70ms timeout has not yet elapsed. Once the power-good threshold is achieved, the normalized circuitbreaker threshold goes to its full value.

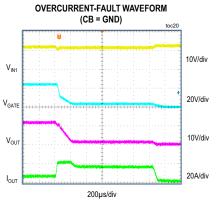

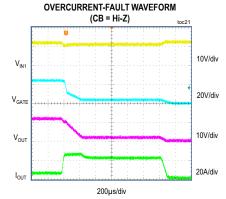

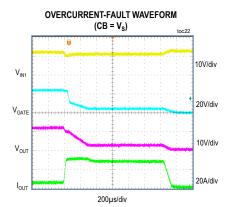

# Programmable Speed Circuit-Breaker Response on Hot-Swap MOSFET

The device features an adjustable current limit with circuit-breaker function that protects the external MOSFETs against short circuits or excessive load current. The voltage across the external sense resistor (R<sub>SENSE</sub>) is monitored by an electronic circuit breaker and active current limit amplifier (ACL). The electronic circuit breaker turns off the hot-swap MOSFET with a 500 $\mu$ A current from GATE to OUT if the voltage across the sense resistor exceeds V<sub>CB\_TH</sub> for longer than the fault filter delay configured at the CDLY pin. Active current limiting begins when the sense voltage exceeds the ACL threshold V<sub>ACL</sub> (ACL) (which is 1.3x V<sub>CB\_TH</sub>). The gate of the hot-swap MOSFET is brought under control by the ACL amplifier and the output current is regulated to maintain the ACL

Figure 1. Inrush Current vs. Voltage Drop Across the Hot-Swap Switch During Startup Period

# Dual ORing, Single Hot-Swap Controller with Accurate Current Monitoring

threshold across the sense resistor. At this point, the fault filter starts the timeout with a 100 $\mu$ A current charging the CDLY pin capacitor. If the CDLY pin voltage exceeds its threshold (1.2V), the external MOSFET is turned off and the FAULT pin pulls low.

After the hot-swap MOSFET turns off, the CDLY pin capacitor is discharged with a  $2\mu$ A pulldown current until it reaches 0.2V. This is followed by a cool-off period of 14 timing cycles at the CDLY pin. At the end of the cool-off period and the GATE pin restarts charging up the gate of the MOSFET.

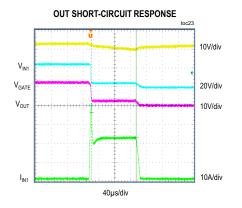

In the event of a severe short-circuit fault on the 12V output, the output current can surge very high. The device responds within 1 $\mu$ s to bring the current under control by pulling the GATE to OUT voltage down with a 200mA current. Almost immediately, the gate of the hot-swap MOSFET recovers rapidly due to the R<sub>GATE</sub> and C<sub>GATE</sub> network, and load current is actively limited until the electronic circuit breaker times out. Due to parasitic supply lead inductance, an input supply without any bypass capacitor may collapse during the high current surge and then spike upwards when the current is interrupted.

#### Programmable Circuit-Breaker Current Threshold

The device features a programmable current limit with circuit-breaker function that protects the external MOSFETs against short circuits or excessive load current. The voltage across the external sense resistor, ( $R_{SENSE}$ ) is monitored by an electronic circuit breaker and active current limit (ACL) amplifier. Connect the CB pin to GND,  $V_S$ , or leave unconnected to select the circuit-breaker threshold (Table 1).

### Timer (CDLY)

An external capacitor connected from the CDLY pin to GND serves as fault filtering when the supply output is in active current limit. When the voltage across the sense resistor exceeds the circuit-breaker trip threshold, CDLY pulls up with 100 $\mu$ A. Otherwise, it pulls down with 2 $\mu$ A. The fault filter times out when the 1.2V CDLY threshold is exceeded, causing the FAULT pin to pull low. The fault filter delay or circuit-breaker time delay is:

#### $t_{CB} = C_{CDLY} \times 12[ms/\mu F]$

After the circuit-breaker timeout, the CDLY pin capacitor pulls down with  $2\mu$ A from the 1.2V CDLY threshold until it reaches 0.2V. Then it completes 14 cooling cycles consisting of the CDLY pin capacitor charging to 1.2V with a 100 $\mu$ A current and discharging to 0.2V with a 2 $\mu$ A current. At that point, the GATE pin voltage is allowed to start up and the  $\overline{FAULT}$  pin pulls high. The total cool-off time for the MOSFET after an overcurrent fault is:

$t_{COOL} = C_{CDLY} \times 7.13[s/\mu F]$

### **ORing Response in Overload Condition**

During the fault condition, the ORing MOSFET remains on.

#### **Control Inputs**

### **ON Input**

The device drives the OG\_ as soon as the V<sub>IN1</sub> - V<sub>F1</sub> (V<sub>F1</sub> is the forward voltage drop of ORing MOSFET connected to IN1) or V<sub>IN2</sub> - V<sub>F2</sub> (V<sub>F2</sub> is the forward voltage drop of the ORing MOSFET connected to IN2) supply voltage generates a V<sub>ON</sub> above the threshold voltage. An external resistive divider from CSP to ON and ground is used to set the turn-on voltage to any desired voltage from 2.9V to 5.5V. The IC turns on the corresponding ORing MOSFET and then turns on the hotswap MOSFET when V<sub>ON</sub> > 1.22V.

The device turns off the output when V<sub>ON</sub> falls below V<sub>UV\_REF</sub> (1.22V - V<sub>ON\_HYS</sub>). An external resistive divider from CSP to ON and ground is used to set the undervoltage-lockout threshold to any desired level between V<sub>UVLO</sub> and 18V.

### Monitoring

### **Analog Current Monitor Output**

IPMON monitors the system input current and provides the best accuracy when  $V_{IPMON}$  is less than 1.7V, or  $V_{SENSE}$  is less than 23.75mV. The IPMON signal is clamped at 2.3V, or  $V_{SENSE}$  = 32mv. For best performance, add a 560pF/6.3V ceramic capacitor between IPMON and GND.

The voltage at IPMON ( $V_{IPMON}$ ) is proportional to the input current ( $I_{SYS}$ ) given by the following equation:

#### $V_{IPMON} = G_{IM} \times I_{SYS} \times R_{SENSE}$

where  $G_{IM}$  = 71.565, a fixed voltage gain.

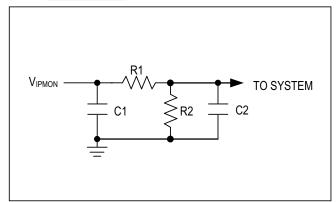

Adding a resistive voltage divider at the IPMON output (Figure 2) allows the overall  $V_{IPMON}$  gain (G) to be adjusted per the following equation:

$$G = G_{IM} \times R2/(R1+R2)$$

where R1 =  $20k\Omega$ , C1 = 560pF, and C2 = 1nF. The resistive-divider equivalent resistance R1||R2 needs to be carefully selected, as it affects accuracy due to the input bias current of the system readout.

# Dual ORing, Single Hot-Swap Controller with Accurate Current Monitoring

### **Output Signals**

#### Fault Status Output (FAULT)

$\overline{FAULT}$  is an open-drain output that is internally pulled high by a 10µA current source to a diode below V<sub>S</sub>, and can be pulled above V<sub>S</sub> using an external pullup.  $\overline{FAULT}$  asserts low when the circuit breaker is tripped after an overcurrent fault timeout. Leave  $\overline{FAULT}$  unconnected if unused.

### Power-Good Output (PG)

Internal circuitry monitors the hot-swap MOSFET gate overdrive between the GATE and OUT pins and the voltage at the OUT pin. The power-good status for the supply is reported by the  $\overline{PG}$  open-drain output. It is pulled high by an external pullup resistor or the internal 10µA pullup. The power-good output asserts low when the gate overdrive exceeds 4.2V during the GATE startup and the voltage at the OUT pin exceeds (0.9 x V<sub>CSP</sub>). The  $\overline{PG}$  signal is delayed by 16ms once conditions for power-good are met.

### Fault Management

#### Autoretry

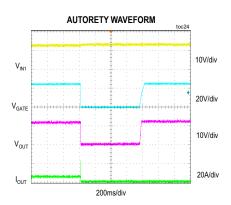

When an overcurrent fault is latched after tripping the circuit breaker, the  $\overline{FAULT}$  pin is asserted low. Only the hot-swap MOSFET is turned off, and the ideal diode MOSFETs are not affected. The latched fault is reset automatically after a cool-off timing cycle as described in the *Timer (CDLY)* section. At the end of the cool-off

period, the fault latch is cleared and  $\overline{FAULT}$  pulls high. The GATE pin voltage is allowed to start up and turn on the hot-swap MOSFET. If the output short persists, the supply powers up into a short with active current limiting until the circuit breaker times out and  $\overline{FAULT}$  again pulls low. A new cool-off cycle begins with CDLY ramping down with a 2µA current. The whole process repeats itself until the output short is removed. Since t<sub>CB</sub> and t<sub>COOL</sub> are a function of CDLY capacitance, C<sub>CDLY</sub>, the autoretry duty cycle is equal to 0.1%, irrespective of C<sub>CDLY</sub>.

### **Applications Information**

### **Prioritizing Supplies with PC**

Figure 2 shows an ORing application where a resistive divider connected from IN1 at the PC pin controls the turnon of the ORing MOSFET, MD2, in the IN2 supply path. When the IN1 supply voltage falls below 4.5V, it turns on the ORing MOSFET, MD2, causing the ORing output to be switched from the main 5.0V supply at IN1 to the auxiliary 5.0V supply at IN2. This configuration permits the load to be supplied from a lower IN1 supply as compared to IN2 until IN1 falls below the MD2 turn-on threshold. The threshold value used should not allow the IN1 supply to be operated at more than one diode voltage below IN2. Otherwise, MD2 conducts through the MOSFET's body diode. The resistive divider connected from CSP at the ON pin provides the undervoltage threshold of 2.6V for the ORing output supply.

Figure 2. External RC Network to Adjust VIPMON

### Table 1. Circuit-Breaker Threshold Programming

| CB PIN CONNECTION       | CIRCUIT-BREAKER THRESHOLD (V <sub>CSP</sub> - V <sub>CSN</sub> ) [mV] |

|-------------------------|-----------------------------------------------------------------------|

| CB = GND                | 35                                                                    |

| CB = Hi-Z (unconnected) | 50                                                                    |

| CB = V <sub>S</sub>     | 65                                                                    |

# Dual ORing, Single Hot-Swap Controller with Accurate Current Monitoring

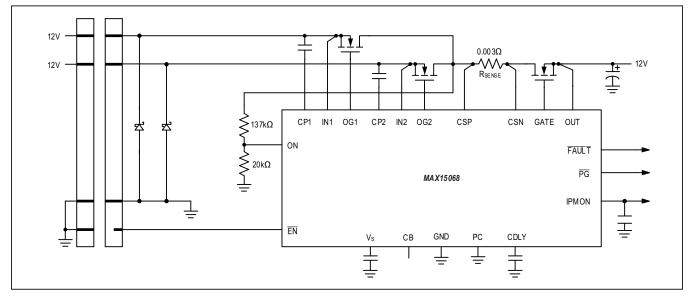

Figure 3. Plug-in Card IN1 Supply Controls the IN2 Supply Turn-On Through the PC Pin

# Dual ORing, Single Hot-Swap Controller with Accurate Current Monitoring

## **Typical Application Circuit**

## **Ordering Information**

| PART         | OPERATING RANGE | FUNCTION                   | TEMP RANGE      | PIN-PACKAGE |

|--------------|-----------------|----------------------------|-----------------|-------------|

| MAX15068ATP+ | 2.9V to 18V     | Autoretry, Current Monitor | -40°C to +125°C | 20 TQFN-EP* |

+Denotes a lead(Pb)-free/RoHS-compliant package.

\*EP = Exposed pad.

## **Chip Information**

PROCESS: BICMOS