#### MAX15090B/MAX15090C

## 2.7V to 18V, 12A, Hot-Swap Solution with Current Report Output

#### **General Description**

The MAX15090B/MAX15090C ICs are integrated solutions for hot-swap applications requiring the safe insertion and removal of circuit line cards from a live backplane. The devices integrate a hot-swap controller,  $6m\Omega$  power MOSFET, and an electronic circuit-breaker protection in a single package.

The devices integrate an accurate current-sense circuitry and provide  $220\mu\text{A/A}$  of proportional output current. The devices are designed for protection of 2.7V to 18V supply voltages.

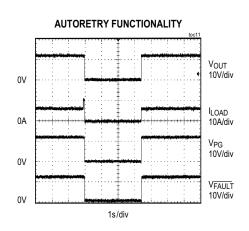

These devices implement a foldback current limit during startup to control inrush current lowering di/dt and keep the MOSFET operating under safe operating area (SOA) conditions. After the startup cycle is complete, on-chip comparators provide VariableSpeed/BiLevel™ protection against short-circuit and overcurrent faults, and immunity against system noise and load transients. The load is disconnected in the event of a fault condition. The devices are factory calibrated to deliver accurate overcurrent protection with ±10% accuracy. During a fault condition, the MAX15090B latches off, while the MAX15090C enters autoretry mode.

The devices feature an IN-to-OUT short-circuit detection before startup. The devices provide a power-MOSFET GATE pin to program the slew rate during startup by adding an external capacitor. The devices have overvoltage/undervoltage input pins that can detect an overvoltage/undervoltage fault and disconnect the IN from the OUT. Additional features include internal overtemperature protection, power-good output, and fault-indicator output.

The MAX15090B/MAX15090C ICs are available in a 28-bump, 2.07mm x 3.53mm, power wafer-level package (WLP) and are rated over the -40°C to +85°C extended temperature range.

#### **Applications**

- RAID Systems

- Storage Bridge Bay

- Disk Drive Power

- Server I/O Cards

- Industrial

VariableSpeed/BiLevel is a trademark of Maxim Integrated Products, Inc.

#### **Benefits and Features**

- Integration Reduces Solution Size for Blade Servers and Other Space-Constrained Designs

- Integrated  $6m\Omega$  (typ) Internal Power MOSFET Overvoltage Protection

- · Power-Good and Fault Outputs

- · Programmable Undervoltage Lockout

- Current Reporting Without Need for External RSENSE

- · Thermal Protection

- Flexibility Enables Use in Many Unique Designs

- 2.7V to 18V Operating Voltage Range

- Adjustable Circuit-Breaker Current/Current-Limit Threshold

- Programmable Slew-Rate Control

- Variable-Speed Circuit-Breaker Response

- · Latchoff or Automatic Retry Options

- Safety Features Ensure Accurate, Robust Protection

- 12A (max) Load Current Capability

- ±10% Circuit-Breaker Threshold Accuracy

- Inrush Current Regulated at Startup with Foldback

- Implementation for di/dt Control

- IN-to-OUT Short-Circuit Detection

Ordering Information and Recommended Application Circuit for Hot-Swap Applications appear at end of data sheet.

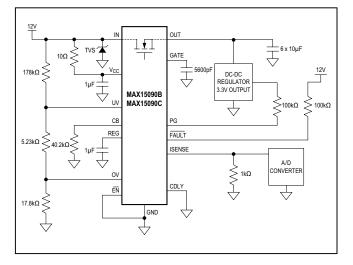

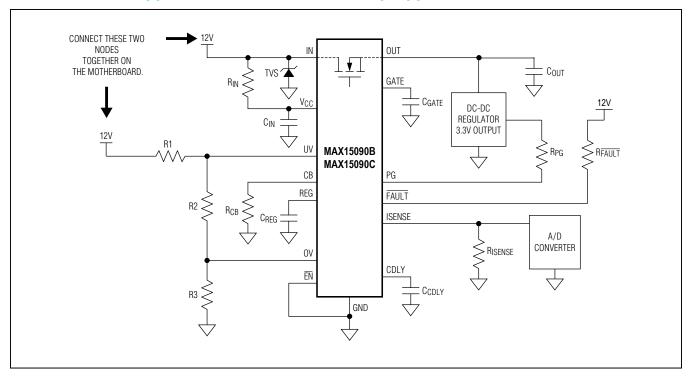

## **Typical Application Circuit**

#### **Absolute Maximum Ratings**

| V <sub>CC</sub> to GND | 0.3V to +20V                          |

|------------------------|---------------------------------------|

| IN to GND              | 0.3V to +20V                          |

| OUT to GND             | 0.3V to (V <sub>IN</sub> + 0.3V)      |

| GATE to OUT            | 0.3V to +6V                           |

| CDLY, ISENSE to GND    | 0.3V to (V <sub>REG</sub> + 0.3V)     |

| EN, CB, UV, OV to GND  | 0.3V to +6V                           |

| REG to GND             | 0.3V to min (+6V, $(V_{CC} + 0.3V)$ ) |

| PG, FAULT to GND       | 0.3V to +20V                          |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

|-------------------------------------------------------|----------------|

| WLP (derate 23.8mW/°C above +70°C)                    | 1500mW         |

| Operating Temperature Range                           | 40°C to +85°C  |

| Junction Temperature                                  | +150°C         |

| Storage Temperature Range                             | 60°C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C         |

| Soldering Temperature (reflow)                        | +260°C         |

|                                                       |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Package Thermal Characteristics (Note 1)**

Junction-to-Ambient Thermal Resistance (θ,JA).....42°C/W

Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )......7°C/W

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>. Thermal resistance can be lowered with improved board design.

#### **Electrical Characteristics**

$(V_{IN} = V_{CC} = 2.7V \text{ to } 18V, T_A = T_J = -40^{\circ}\text{C to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{IN} = 12V, R_{CB} = 33.2k\Omega, \text{ and } T_A = +25^{\circ}\text{C}.)$  (Note 2)

| PARAMETER                                                   | SYMBOL                | CONDITIONS                    | MIN  | TYP  | MAX  | UNITS |

|-------------------------------------------------------------|-----------------------|-------------------------------|------|------|------|-------|

| POWER SUPPLIES                                              |                       |                               | •    |      |      |       |

| V <sub>CC</sub> Operating Range                             | Vcc                   |                               | 2.7  |      | 18   | V     |

| IN Operating Range                                          | V <sub>IN</sub>       |                               | 2.7  |      | 18   | V     |

| V <sub>CC</sub> Supply Current                              | I <sub>CC</sub>       | V <sub>IN</sub> = 3V          |      | 0.5  | 0.75 | mA    |

| IN Cumply Current                                           | L                     | $R_{CB}$ = 40.2kΩ, no load    |      | 5.25 | 6.2  | mA    |

| IN Supply Current                                           | liN                   | $R_{CB}$ = 10kΩ, no load      |      | 1.5  | 2.4  | IIIA  |

| V <sub>CC</sub> Default Undervoltage<br>Lockout             | V <sub>UVLO</sub>     | V <sub>CC</sub> rising        | 2.35 | 2.5  | 2.65 | V     |

| V <sub>CC</sub> Default Undervoltage-<br>Lockout Hysteresis | V <sub>UVLO_HYS</sub> |                               |      | 0.1  |      | V     |

| REG Regulator Voltage                                       | V <sub>REG</sub>      | No load, V <sub>CC</sub> > 4V | 3.15 | 3.35 | 3.55 | V     |

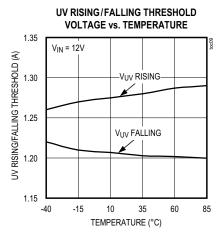

| UV Turn-On Threshold                                        | V <sub>UV_TH</sub>    | V <sub>UV</sub> rising        | 1.21 | 1.23 | 1.25 | V     |

| UV Turn-On Threshold<br>Hysteresis                          | V <sub>UV_HYS</sub>   | V <sub>UV</sub> falling       |      | 0.1  |      | V     |

| OV Turn-On Threshold                                        | V <sub>OV_TH</sub>    | V <sub>OV</sub> rising        | 1.21 | 1.23 | 1.25 | V     |

| OV Turn-On Threshold<br>Hysteresis                          | V <sub>OV_HYS</sub>   | V <sub>OV</sub> falling       |      | 0.1  |      | V     |

| EN Threshold                                                | V <sub>EN_TH</sub>    | V <sub>EN</sub> rising        | 0.95 | 1    | 1.05 | V     |

| EN Threshold Hysteresis                                     | V <sub>EN_HYS</sub>   | V <sub>EN</sub> falling       |      | 0.1  |      | V     |

## **Electrical Characteristics (continued)**

$(V_{IN} = V_{CC} = 2.7V \text{ to } 18V, T_A = T_J = -40^{\circ}\text{C to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{IN} = 12V, R_{CB} = 33.2k\Omega,$  and  $T_A = +25^{\circ}\text{C}.)$  (Note 2)

| PARAMETER                                                | SYMBOL                | CONDITIONS                                                         |                        | MIN                      | TYP   | MAX  | UNITS |

|----------------------------------------------------------|-----------------------|--------------------------------------------------------------------|------------------------|--------------------------|-------|------|-------|

| OV, UV, EN Input Leakage<br>Current                      | I <sub>LEAK</sub>     | $V_{OV} = V_{UV} = V_{\overline{EN}} = 0 \text{ to 5V}$            |                        | -1                       |       | +1   | μA    |

| CB Source Current                                        | ITHCB_NORM            | Power-on mode                                                      |                        |                          | 12    |      | μA    |

| CURRENT LIMIT                                            |                       |                                                                    |                        | •                        |       |      |       |

| Circuit-Breaker Accuracy                                 | 1                     | $R_{CB} = 40.2k\Omega$                                             | 10.85                  | 12.06                    | 13.27 | _    |       |

| (Note 3)                                                 | I <sub>CB,TH</sub>    | V <sub>IN</sub> = 12V                                              | R <sub>CB</sub> = 10kΩ | 2.7                      | 3     | 3.3  | Α     |

| Circuit-Breaker Accuracy<br>Deviation                    |                       | R <sub>CB</sub> = 10kΩ to 40.2kΩ nominal current-limit v           |                        | -10                      |       | +10  | %     |

| Slow-Comparator Response                                 | 1                     | 0.6% overcurrent                                                   |                        |                          | 1.5   |      | ms    |

| Time (Note 4)                                            | t <sub>SCD</sub>      | 30% overcurrent                                                    |                        |                          | 200   |      | μs    |

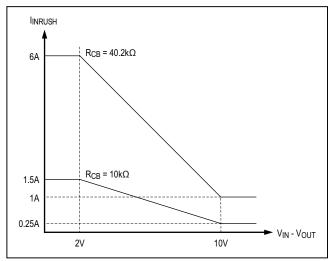

| Maximum Current Limit During Startup                     | ILIM_MAX              | (see Figure 2)                                                     |                        | 0.5 x I <sub>CB,TH</sub> |       | Н    | А     |

| Fast-Comparator Threshold                                | I <sub>FC_TH</sub>    |                                                                    |                        | 1.5 x I <sub>CB,TH</sub> |       | Α    |       |

| Minimum CB Voltage Reference<br>During Foldback (Note 5) | V <sub>THCB_MIN</sub> | V <sub>IN</sub> - V <sub>OUT</sub> > 10V, R <sub>CB</sub> = 40.2kΩ |                        | 60                       |       |      | mV    |

| Maximum CB Voltage Reference<br>During Foldback (Note 5) | V <sub>THCB_MAX</sub> | $V_{IN}$ - $V_{OUT}$ < 2V, $R_{CB}$ = 40.2k $\Omega$               |                        |                          | 240   |      | mV    |

| TIMING                                                   | 1                     |                                                                    |                        | ,                        | ,     |      |       |

| Startup Maximum Time Duration                            | t <sub>SU</sub>       |                                                                    |                        | 43                       | 48    | 53   | ms    |

| Autorestart Delay Time                                   | t <sub>RESTART</sub>  |                                                                    |                        |                          | 3.2   |      | s     |

| Time Delay Comparator High<br>Threshold                  | V <sub>DLY_TH</sub>   |                                                                    |                        | 1.85                     | 2     | 2.18 | V     |

| Time Delay Pullup Current                                | I <sub>DLY</sub>      |                                                                    |                        | 1.6                      | 1.9   | 2.3  | μA    |

| Output Short Detection at Startup                        | tshort                |                                                                    |                        | 10.8                     | 13    | 14.4 | ms    |

| MOSFET                                                   |                       |                                                                    |                        |                          |       |      |       |

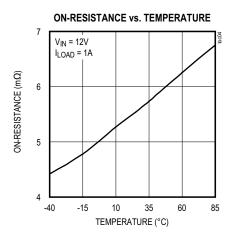

| Total On Desistance                                      | D                     | T <sub>A</sub> = +25°C                                             |                        |                          | 5.5   | 7.5  |       |

| Total On-Resistance                                      | R <sub>ON</sub>       | T <sub>A</sub> = -40°C to +85°C                                    |                        |                          |       | 9    | mΩ    |

| GATE Charge Current                                      | I <sub>GATE</sub>     |                                                                    |                        | 4.4                      | 5.7   | 7.5  | μA    |

|                                                          |                       |                                                                    |                        |                          |       |      |       |

#### **Electrical Characteristics (continued)**

$(V_{IN} = V_{CC} = 2.7V \text{ to } 18V, T_A = T_J = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{IN} = 12V, R_{CB} = 33.2k\Omega, \text{ and } T_A = +25^{\circ}\text{C}.)$  (Note 2)

| PARAMETER                                      | SYMBOL              | CONDITIONS                                                                                                   | MIN  | TYP                   | MAX  | UNITS |

|------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------|------|-----------------------|------|-------|

| OUTPUTS                                        | OUTPUTS             |                                                                                                              |      |                       |      |       |

| FAULT, PG Output Low Voltage                   | V <sub>OL</sub>     | Low-impedance state,<br>I <sub>FAULT</sub> = +5mA, I <sub>PG</sub> = +5mA                                    |      |                       | 0.4  | V     |

| FAULT, PG Output High<br>Leakage Current       | Іон                 | High-impedance state,<br>V <sub>FAULT</sub> = 16V, V <sub>PG</sub> = 16V                                     |      |                       | 1    | μA    |

| CURRENT REPORT                                 |                     |                                                                                                              |      |                       |      |       |

| ISENSE Full-Scale Current                      | I <sub>ISENSE</sub> |                                                                                                              |      | 2.64                  |      | mA    |

| ISENSE Gain Ratio                              |                     | I <sub>SENSE</sub> /I <sub>OUT</sub>                                                                         |      | 220                   |      | μΑ/Α  |

| ISENSE Voltage Range                           | V <sub>ISENSE</sub> | V <sub>IN</sub> = 12V                                                                                        | 0    |                       | 2.5  | V     |

| ICENICE Off t E                                |                     | T <sub>A</sub> = +25°C                                                                                       | -30  |                       | +30  |       |

| ISENSE Offset Error                            | lisense_off         | T <sub>A</sub> = -40°C to +85°C                                                                              | -65  |                       | +65  | μA    |

|                                                |                     | T <sub>A</sub> = +25°C, I <sub>OUT</sub> = 1A,<br>ΔI <sub>OUT</sub> = 100mA                                  | -2.5 |                       | +2.5 |       |

| ISENSE Differential Gain Error                 | ISENSE_ERROR        | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}, I_{OUT} = 1\text{A},$<br>$\Delta I_{OUT} = 100\text{mA}$ | -4   | +4                    | - %  |       |

| PG THRESHOLD                                   |                     |                                                                                                              |      |                       |      | ,     |

| PG Threshold                                   | V <sub>PG</sub>     | Measured at V <sub>OUT</sub>                                                                                 |      | 0.9 x V <sub>IN</sub> |      | V     |

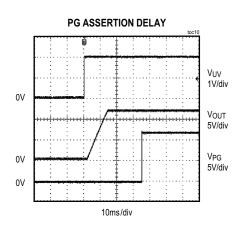

| PG Assertion Delay t <sub>PG</sub>             |                     | From V <sub>OUT</sub> > V <sub>PG</sub> and (V <sub>GATE</sub> - V <sub>IN</sub> ) > 3V                      | 12   | 16                    | 20   | ms    |

| OUT to IN Short-Circuit<br>Detection Threshold | V <sub>IOSHT</sub>  | Measured at V <sub>OUT</sub>                                                                                 |      | 0.9 x V <sub>IN</sub> |      |       |

| OUT Precharge Threshold V <sub>PC</sub>        |                     | Measured at V <sub>OUT</sub>                                                                                 |      | 0.5 x V <sub>IN</sub> |      | V     |

| THERMAL SHUTDOWN                               | •                   |                                                                                                              | '    |                       |      |       |

| Thermal Shutdown                               | T <sub>SD</sub>     | T <sub>J</sub> rising                                                                                        |      | +150                  |      | °C    |

| Thermal-Shutdown Hysteresis                    |                     | T <sub>J</sub> falling                                                                                       |      | 20                    |      | °C    |

- Note 2: All devices are 100% production tested at  $T_A = +25$ °C. Limits over temperature are guaranteed by design.

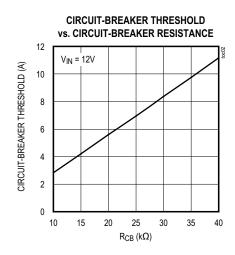

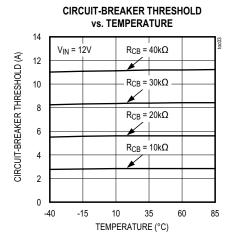

- Note 3:  $40.2k\Omega$  is the maximum allowed external resistance value to be connected at CB pin to GND for safe operation. All devices are tested with 10kΩ, the parameter specified at  $R_{CB} = 40.2k\Omega$  is guaranteed by bench characterization and correlation, with respect to the tested parameter at  $R_{CB} = 10k\Omega$ . The formula that describes the relationship between  $R_{CB}$  and the circuit-breaker current threshold is:  $I_{CB} = R_{CB}/3333.3$ .

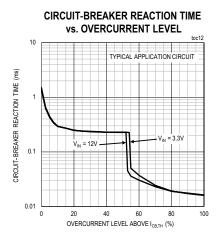

- **Note 4:** The current-limit slow-comparator response time is weighed against the amount of overcurrent so the higher the overcurrent condition, the faster the response time.

- Note 5: Foldback is active during the startup phase so the internal power MOSFET operates within SOA.

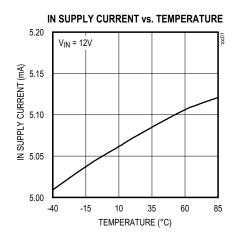

## **Typical Operating Characteristics**

$(V_{IN} = V_{CC} = 2.7V \text{ to } 18V, T_J = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{IN} = 12V, R_{CB} = 33.2k\Omega, \text{ and } T_J = +25^{\circ}\text{C.})$  (Note 3)

## **Typical Operating Characteristics (continued)**

$(V_{IN} = V_{CC} = 2.7V \text{ to } 18V, T_J = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{IN} = 12V, R_{CB} = 33.2k\Omega, \text{ and } T_J = +25^{\circ}\text{C}.)$  (Note 3)

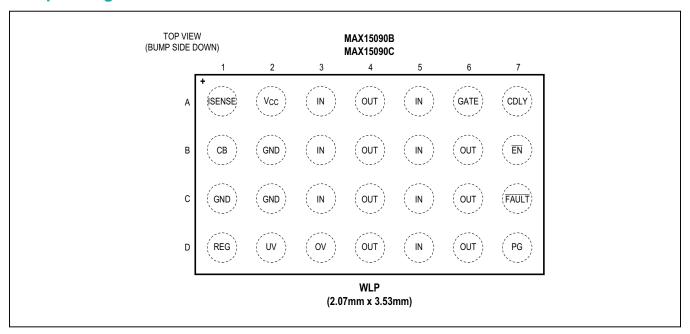

## **Bump Configuration**

## **Bump Description**

| BUMP                             | NAME            | FUNCTION                                                                                                                                                                                                                                                                                |

|----------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1                               | ISENSE          | Current-Sense Output. The ISENSE output sources a current that is proportional to the output current. Connect a resistor between ISENSE and GND to produce a scaled voltage.                                                                                                            |

| A2                               | V <sub>CC</sub> | Power-Supply Input. Connect $V_{CC}$ to a voltage between 2.7V and 18V. Connect a Schottky diode (or $6\Omega$ resistor) from IN to $V_{CC}$ and a 1 $\mu$ F bypass capacitor to GND to guarantee full operation in the event $V_{IN}$ collapses during a strong short from OUT to GND. |

| A3, A5, B3,<br>B5, C3,<br>C5, D5 | IN              | Supply Voltage Input. IN is connected to the drain of the internal $6m\Omega$ MOSFET. Bypass IN with a transient voltage-suppressor diode to GND for clamping inductive kick transients in the case of fast output short-circuit to GND.                                                |

| A4, B4, B6,<br>C4, C6,<br>D4, D6 | OUT             | Load Output. Source of the internal power MOSFET.                                                                                                                                                                                                                                       |

## MAX15090B/MAX15090C

# 2.7V to 18V, 12A, Hot-Swap Solution with Current Report Output

## **Bump Description (continued)**

| BUMP       | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A6         | GATE  | GATE of Internal MOSFET. During startup, a 5.7µA current is sourced to enhance the internal MOSFET with a 10V/ms slew rate. Connect an external capacitance from GATE to GND to reduce the output slew rate during startup.                                                                                                                                                                                                                                                                                                                                                            |

| A7         | CDLY  | Enable Timer Input. Connect a capacitor between CDLY and GND to set a 1s/µF duration timeout delay. The $\overline{\text{EN}}$ input has to be pulled low before the timeout delay elapses, to prevent internal MOSFET shutdown after power-up. Minimum required capacitor for CDLY is 1000pF; short to GND if not needed.                                                                                                                                                                                                                                                             |

| B1         | СВ    | Current-Limit Threshold Set. Connect a resistor from CB to GND to set the circuit-breaker threshold. Maximum value of $40.2k\Omega$ can be accepted for safe operation. Having the CB pin connected to GND sets the circuit-breaker threshold at 0A.                                                                                                                                                                                                                                                                                                                                   |

| B2, C1, C2 | GND   | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| В7         | ĒN    | Enable Input. This input does not function like a traditional enable input (see UV description). Externally pulled up to logic-high state through a resistor normally connected to REG. The $\overline{EN}$ input must be pulled down (for at least 1ms) by the external circuit before a programmable timeout delay has elapsed, otherwise a shutdown occurs. The timeout timer starts counting when the internal MOSFET is turned on. Connect a capacitor between CDLY and GND to program the duration of the timeout delay. Connect $\overline{EN}$ to GND to disable this feature. |

| C7         | FAULT | Fault Status Output. FAULT is an open-drain, active-low output. See the Fault-Status Output (FAULT) section for conditions that make FAULT assert low. FAULT is disabled during startup.                                                                                                                                                                                                                                                                                                                                                                                               |

| D1         | REG   | Internal Regulator Output. Bypass to ground with a 1 $\mu$ F capacitor. Do not power external circuitry using the REG output (except a resistor > 50k $\Omega$ connected from REG to $\overline{\text{EN}}$ ). Optional: For V <sub>CC</sub> values lower than V <sub>REG_MAX</sub> , REG can be connected to V <sub>CC</sub> to maximize the voltage on the REG pin (see the <i>Electrical Characteristics</i> table).                                                                                                                                                                |

| D2         | UV    | Active-High Enable Comparator Input. Pulling UV high enables the internal MOSFET to turn on. UV also sets the undervoltage threshold. See the Setting the Undervoltage Threshold section.                                                                                                                                                                                                                                                                                                                                                                                              |

| D3         | OV    | Overvoltage Enable Input. Pull OV high to turn off the internal MOSFET. Connect OV to an external resistive divider to set the overvoltage-disable threshold. See the Setting the Overvoltage Threshold section.                                                                                                                                                                                                                                                                                                                                                                       |

| D7         | PG    | Power-Good Output. PG is an open-drain, active-high output. PG pulls low until the internal power MOSFET is fully enhanced.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

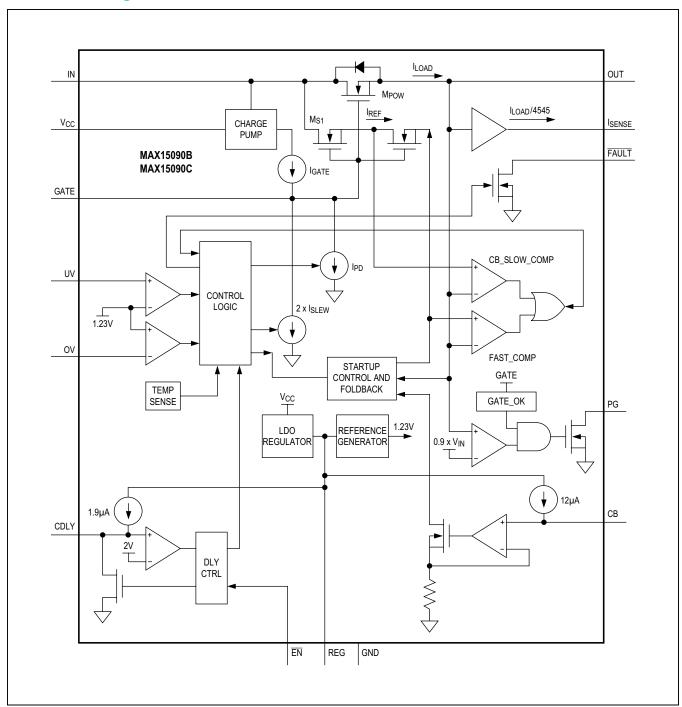

## **Functional Diagram**

#### **Detailed Description**

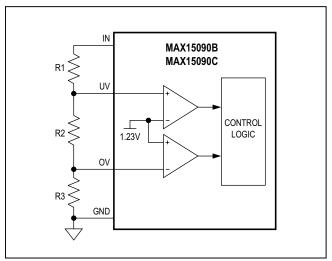

#### Enable Logic and Undervoltage/Overvoltage-**Lockout Threshold**

The MAX15090B/MAX15090C ICs enable the output, as shown in Table 1. The devices are ready to drive the output when the V<sub>CC</sub> supply rises above the V<sub>UVLO</sub> threshold. The devices turn on the output when  $V_{CC} > V_{UVLO}$ ,  $V_{UV}$  is high ( $V_{UV} > 1.23V$ ) and  $V_{OV}$  is low ( $V_{OV} < 1.23V$ ). The devices turn off the output when V<sub>LIV</sub> falls below (1.23V - V<sub>UV HYS</sub>) or V<sub>OV</sub> rises above 1.23V. An external resistive divider from IN to UV, OV, and ground provide the flexibility to set the undervoltage/overvoltage-lockout threshold to any desired level between V<sub>UVLO</sub> and 18V. See Figure 1 and the Setting the Undervoltage Threshold and Setting the Overvoltage Threshold sections.

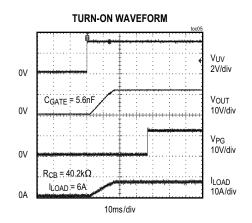

#### Startup

Once the device output is enabled, the device provides controlled application of power to the load. The voltage at OUT begins to rise at approximately 10V/ms default until the programmed circuit-breaker current level is reached, while the devices actively limit the inrush current at the circuit-breaker setting. An external capacitor connected to the GATE pin allows the user to program the slew rate to a value lower than the default. The inrush current can be programmed by selecting the appropriate value of RCB. During startup, a foldback current limit is active to protect the internal MOSFET to operate within the SOA (Figure 2).

An internal 48ms timer (t<sub>SU</sub>) starts counting when the devices enter the startup phase. The devices complete the startup phase and enter normal operation mode if the voltage at OUT rises above the precharge threshold (0.9 x V<sub>IN</sub>) and (V<sub>GATE</sub> - V<sub>OLIT</sub>) > 3V. An open-drain power-good output (PG) goes high-impedance 16ms after the startup successfully completes. Device enters fault mode if startup does not complete before t<sub>SU</sub> expires. Startup time is nominally VOLIT ramp time plus 6ms, including the time it takes for GATE to get to VOUT +3V.

The thermal-protection circuit is always active and the internal MOSFET immediately turned off when the thermal-shutdown threshold condition is reached.

**Table 1. Output Enable Truth Table**

| POWER SUPPLY                        | PRECISION AN                                                  | PRECISION ANALOG INPUTS              |     |  |

|-------------------------------------|---------------------------------------------------------------|--------------------------------------|-----|--|

| V <sub>CC</sub>                     | UV                                                            | ov                                   | OUT |  |

| V <sub>CC</sub> > V <sub>UVLO</sub> | V <sub>UV</sub> > V <sub>UV_TH</sub>                          | V <sub>OV</sub> < V <sub>OV_TH</sub> | On  |  |

| V <sub>CC</sub> < V <sub>UVLO</sub> | X                                                             | X                                    | Off |  |

| X                                   | V <sub>UV</sub> < (V <sub>UV_TH</sub> - V <sub>UV_HYS</sub> ) | X                                    | Off |  |

| X                                   | X                                                             | V <sub>OV</sub> > V <sub>OV</sub> TH | Off |  |

X = Don't care.

$V_{UV}$  TH and  $V_{OV}$  TH = 1.23V (typ).

Figure 1. Undervoltage/Overvoltage-Threshold Setting

Figure 2. Startup Inrush Current Foldback Characteristics

#### VariableSpeed/BiLevel Fault Protection

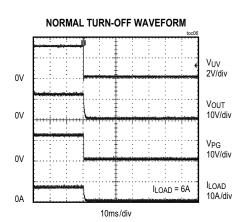

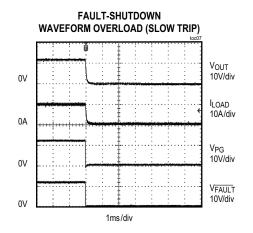

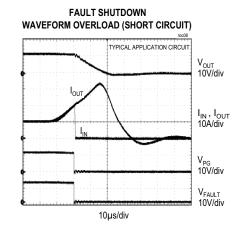

VariableSpeed/BiLevel fault protection incorporates comparators with different thresholds and response times to monitor the load current (see the <u>Typical Operating Characteristics</u> section). Protection is provided in normal operation (after the startup period has expired) by discharging the MOSFET gate in response to a fault condition. During a fault condition, the MAX15090C enters autoretry mode, while the MAX15090B latches off (see the <u>Autoretry and Latchoff Fault Management</u> section).

#### **Enable Input (EN)**

After a startup phase is successfully completed and the power-good output asserted, the  $\overline{EN}$  input has to be pulled low (for at least 1ms) before the  $t_{DLY}$  delay elapses. If the  $\overline{EN}$  input is not pulled low before the  $t_{DLY}$  elapses, then the devices turn off the internal MOSFET immediately and a new cycle is required for entering power-up mode. Connect a capacitor between CDLY and GND to set a 1s/µF duration timeout delay. If this function in is not implemented, connect  $\overline{EN}$  to GND for proper operation.

#### **Charge Pump**

An integrated charge pump provides the gate-drive voltage for the internal power MOSFET. The charge pump generates the proper gate drive voltage above  $V_{IN}$  to fully enhance the internal power MOSFET and guarantee low  $R_{ON}$  operation during normal state conditions.

During startup, the internal charge pump drives the GATE of the MOSFET with a fixed 5.7 $\mu$ A current to enhance the internal MOSFET with 10V/ms slew rate (typ). Connect an external capacitor (C<sub>GATE</sub>) from GATE to GND to reduce the output slew rate during startup. C<sub>GATE</sub> can be calculated according to the following formula:

where  $I_{GATE}$  is 5.7µA (typ),  $t_{ON}$  is the desired output ramp-up time, and  $V_{OUT}$  is assumed to start from zero.

The slew rate of the OUT pin during startup can be controlled by I<sub>GATE</sub>/C<sub>GATE</sub> under light-load driving conditions, or by the limited inrush current and the external capacitive load, whichever is less.

$$(\Delta V_{OUT}/\Delta t) = I_{LIM}/C_{LOAD}$$

$I_{LIM}$  varies during startup as  $V_{OUT}$  ramps up. See the  $\underline{\mbox{Electrical Characteristics}}$  table and  $\underline{\mbox{Figure 2}}.$

#### **Circuit-Breaker Comparator and Current Limit**

The current that passes through the internal power MOSFET is compared to a circuit-breaker threshold. An external resistor between CB and GND sets this threshold according to the following formula:

$$I_{CB} = R_{CB}/3333.3$$

where  $I_{CB}$  is load current in amps and  $R_{CB}$  (the resistor between CB and GND) is in ohms.

The circuit-breaker comparator is designed so the load current can exceed the threshold for some amount of time before tripping. The time delay varies inversely with the overdrive above the threshold. The greater the overcurrent condition, the faster the response time, allowing the devices to tolerate load transients and noise near the circuit-breaker threshold. The maximum allowed external resistor value is  $40.2k\Omega$ , which corresponds to a 12A CB threshold setting. Programming the CB threshold to a value higher than 12A could cause unsafe operating conditions, resulting in damage to the devices.

The devices also feature catastrophic short-circuit protection. During normal operation, if OUT is shorted directly to GND, a fast protection circuit forces the gate of the internal MOSFET to discharge quickly and disconnect the output from the input.

#### **Autoretry and Latchoff Fault Management**

During a fault condition, the devices turn off the internal MOSFET, disconnecting the output from the input. The MAX15090C enters autoretry mode and restarts after a  $t_{RESTART}$  time delay has elapsed. The MAX15090B latches off and remains off until the UV input is cycled off and on after a  $t_{RESTART}$  delay. The delay prevents the latchoff device to restart and operate with an unsafe power-dissipation duty cycle.

#### **Fault-Status Output (FAULT)**

FAULT is an open-drain output that asserts low when the following conditions occur: Current limit, overtemperature, IN-to-OUT short at startup (see the "IN-to-OUT Short-Circuit Protection" section), and if device does not complete startup before the t<sub>SU</sub> timer expires (see the <u>Startup</u> section). FAULT remains low until the next startup cycle. FAULT is capable of sinking up to 5mA current when asserted.

#### MAX15090B/MAX15090C

# 2.7V to 18V, 12A, Hot-Swap Solution with Current Report Output

#### Power-Good (PG) Delay

The devices feature an open-drain, power-good output that asserts after a  $t_{PG}$  delay, indicating that the OUT voltage has reached (0.9 x  $V_{IN}$ ) voltage and ( $V_{GATE} - V_{OUT}$ ) > 3V.

#### Internal Regulator Output (REG)

The devices include a linear regulator that outputs 3.3V at REG. REG provides power to the internal circuit blocks of the devices and must not be loaded externally (except for a resistor >  $50 k\Omega$  connected from REG to  $\overline{\text{EN}}$ ). REG requires at least a 1µF capacitor to ground for proper operation.

#### **Current Report Output (ISENSE)**

The ISENSE pin is the output of an accurate current-sense amplifier and provides a source current that is proportional to the load current flowing into the main switch. The factory-trimmed current ratio is set to 220µA/A. This produces a scaled voltage by connecting a resistor between ISENSE and ground. This voltage signal then goes to an ADC and provides digitized information of the current supplied to the powered system.

#### **Thermal Protection**

The devices enter a thermal-shutdown mode in the event of overheating caused by excessive power dissipation or high ambient temperature. When the junction temperature exceeds  $T_J = +150^{\circ}\text{C}$  (typ), the internal thermal-protection circuitry turns off the internal power MOSFET. The devices recover from thermal-shutdown mode once the junction temperature drops by  $20^{\circ}\text{C}$  (typ).

#### **IN-to-OUT Short-Circuit Protection**

At startup, after all the input conditions are satisfied (UV, OV,  $V_{UVLO}$ ), the devices immediately check for an IN-to-OUT short-circuit fault. If  $V_{OUT}$  is greater than 90% of  $V_{IN}$ , the internal MOSFET cannot be turned on so  $\overline{FAULT}$  is asserted and the MAX15090C enters autoretry mode in 3.2s, while the MAX15090B latches off.

If  $V_{OUT}$  is lower than 90% of  $V_{IN}$  but greater than 50% of  $V_{IN}$ , the internal MOSFET still cannot be turned on. No fault is asserted and the MOSFET can turn on as soon as  $V_{OUT}$  is lower than 50% of  $V_{IN}$ .

### **Applications Information**

#### Setting the Undervoltage Threshold

The devices feature an independent on/off control (UV) for the internal MOSFET. The devices operate with a 2.7V to 18V input voltage range and have a default 2.5V (typ) undervoltage-lockout threshold.

The internal MOSFET remains off as long as  $V_{CC} < 2.5V$  or  $V_{UV} < V_{UV\_TH}$ . The undervoltage-lockout threshold is programmable using a resistive divider from IN to UV, OV, and GND (Figure 1). When  $V_{CC}$  is greater than 2.7V and  $V_{UV}$  exceeds the 1.23V (typ) threshold, the internal MOSFET turns on and goes into normal operation. Use the following equation to calculate the resistor values for the desired undervoltage threshold:

$$R1 = \left(\frac{V_{1N}}{V_{UV\_TH}} - 1\right) \times \left(R2 + R3\right)$$

where  $V_{IN}$  is the desired turn-on voltage for the output and  $V_{UV\_TH}$  is 1.23V. R1 and (R2 + R3) create a resistive divider from IN to UV. During normal operating conditions,  $V_{UV}$  must remain above its 1.23V (typ) threshold. If  $V_{UV}$  falls 100mV ( $V_{UV\_HYS}$ ) below the threshold, the internal MOSFET turns off, disconnecting the load from the input.

#### **Setting the Overvoltage Threshold**

The devices also feature an independent overvoltageenable control (OV) for the internal MOSFET.

When  $V_{\mbox{OV}}$  exceeds the 1.23V (typ) threshold, the internal MOSFET turns off.

The overvoltage-lockout threshold is programmable using a resistive divider from IN to UV, OV, and GND (Figure 1). Use the following equation to calculate the resistor values for the desired overvoltage threshold:

$$(R1 + R2) = \left(\frac{V_{IN}}{V_{OV\_TH}} - 1\right) \times R3$$

where  $V_{IN}$  is the desired turn-off voltage for the output and  $V_{OV\_TH}$  is 1.23V. R1 and (R2 + R3) create a resistive divider from IN to OV. During normal operating conditions,  $V_{OV}$  must remain below its 1.23V (typ) threshold. If  $V_{OV}$  rises above the  $V_{OV\_TH}$  threshold, the internal MOSFET turns off and disconnects the load from the input.

## Wafer-Level Packaging (WLP) Applications Information

For the latest application details on WLP construction, dimensions, tape carrier information, PCB techniques, bump-pad layout, recommended reflow temperature profile, as well as the latest information on reliability testing results, refer to Application Note 1891: <u>Wafer-Level Packaging (WLP) and its Applications.</u>

## **Recommended Application Circuit for Hot-Swap Applications**

## **Chip Information**

PROCESS: BICMOS

## **Ordering Information**

| PART           | TEMP<br>RANGE     | PIN-<br>PACKAGE | FAULT       |

|----------------|-------------------|-----------------|-------------|

| MAX15090BEWI+T | -40°C to<br>+85°C | 28 WLP          | Latched Off |

| MAX15090CEWI+T | -40°C to<br>+85°C | 28 WLP          | Autoretry   |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

## **Package Information**

For the latest package outline information and land patterns (foot-prints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

|        | PACKAGE<br>CODE |                | LAND PATTERN<br>NO.            |

|--------|-----------------|----------------|--------------------------------|

| 28 WLP | W282B3Z+1       | <u>21-0577</u> | Refer to Application note 1891 |

T = Tape and reel.