Click here to ask an associate for production status of specific part numbers.

# Integrated, Step-Down Switching Regulator with Selectable Applications Configurations

# MAX16425/MAX16425A

### **General Description**

The MAX16425/MAX16425A are fully-integrated, highly efficient switching regulators for applications operating from 4.5V to 16V input supplies that require up to 25A maximum load. These single-chip regulators provide a compact high-efficiency, power-delivery solution for precision outputs that demand fast transient response.

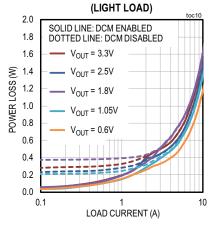

The two devices have different programmability options (see <u>Table 3a</u> and <u>3b</u> for details) to enable a wide range of configurations. The programmable features include: internal/external reference voltage, output voltage set-point, switching frequency, overcurrent protection level (OCP), and soft-start timing. Discontinuous current mode (DCM) operation can be enabled through pin-strapping to improve light-load efficiency.

The MAX16425/MAX16425A include multiple protection and measurement features. Positive and negative cycleby-cycle OCP, short-circuit protection and overtemperature protection (OTP) ensure robust design. Input undervoltage and overvoltage lockout shut down the regulator to prevent damage when the input voltage is out of specification. Regulation is halted in case of an output overvoltage (OVP) event. A status pin indicates that the output voltage is within range and the output voltage is in regulation. The device has an analog output that can be configured to report output current or junction temperature with  $\pm 5\%$ and  $\pm 8^{\circ}$ C accuracy, respectively.

The devices are available in a 27-bump (2.2mm x 3.8mm) WLCSP package that provides low thermal resistance and minimizes the PCB area.

### **Applications**

- Servers/µServers

- I/O and Chipset Supplies

- GPU Core Supply

- DDR Memory: V<sub>DDQ</sub>, V<sub>PP</sub> and V<sub>TT</sub>

- Point-of-Load (PoL) Applications

| DEVICE<br>TYPE | CURRENT<br>RATING | INPUT<br>VOLTAGE | OUTPUT<br>VOLTAGE |  |

|----------------|-------------------|------------------|-------------------|--|

| MAX16425       | 25 4              | 4.5V to 16V      | 0.6V to 3.3V      |  |

| MAX16425A      | 25A               | 4.50 10 100      | 0.00 10 3.30      |  |

Quick-PWM is a trademark of Maxim Integrated Products, Inc.

### **Benefits and Features**

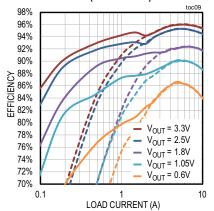

- High-Efficiency Solution

- Up to 97% Peak

- Up to 87% Full-Load

- Up to 96% Light-Load Efficiency at 1A with DCM Enabled

- Flexible Design Allows Early PCB Definition

- Footprint Compatible with VT2491 (15A) and Related Scalable Products

- Programmable Switching Frequency Up to 1MHz

- Programmable Soft-Start and STAT Delay Timings

- Programmable Reference Voltage with External Input Option

- Programmable Positive and Negative OCP Limit

- Advanced Architecture, Protection and Reporting Guarantees Reliable Designs

- Analog Current or Temperature Reporting

- Differential Remote Sense with Open-Circuit

Detection

- Fast Transient Response with Quick-PWM™ Architecture

- · Percentage-Based Output Power Good and OVP

- Open-Drain Status Indicator (STAT) Pin

- Input Undervoltage and Overvoltage Lockout

- Adaptive Dead Time Control

- Saves Board Space

- Integrated Boost Switch

- 27-Bump WLCSP (2.2mm x 3.8mm) Footprint

- Operation Using Ceramic Input and Output Capacitors

#### Ordering Information appears at end of data sheet.

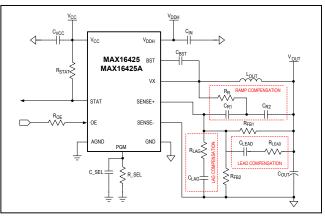

### **Basic Application Circuit**

<sup>19-100471;</sup> Rev 0; 1/19

© 2019 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. One Analog Way, Wilmington, MA 01887 U.S.A. | Tel: 781.329.4700 | © 2019 Analog Devices, Inc. All rights reserved.

# Integrated, Step-Down Switching Regulator with Selectable Applications Configurations

### **Absolute Maximum Rating**

| VDDH to GND (Note 1)         | 0.3V to +23V   |

|------------------------------|----------------|

| VX to GND (DC)               | 0.3V to +23V   |

| VX to GND (AC) (Notes 1, 2)  | 10V to +23V    |

| VDDH to VX (DC)              | 0.3V to +23V   |

| VDDH to VX (AC) (Notes 1, 2) | 10V to +23V    |

| BST to GND (DC)              | 0.3V to +25.5V |

| BST to GND (AC) (Notes 1, 2) | 7V to +25.5V   |

| BST to VX Differential       | 0.3V to +2.5V  |

| VCC to AGND                       | 0.3V to +2.5V     |

|-----------------------------------|-------------------|

| OE to GND                         | 0.3V to +2.5V     |

| PGM, SENSE+, SENSE- to GND        | 0.3V to VCC +0.3V |

| STAT to AGND                      | 0.3V to +4V       |

| Junction Temperature (TJ)         | +150°C            |

| Storage Temperature Range         | 65°C to +150°C    |

| Peak Reflow Temperature Lead-Free | +260°C            |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Operating Ratings**

| Input Voltage (V <sub>DDH</sub> )      |                |

|----------------------------------------|----------------|

| Bias-Supply Voltage (V <sub>CC</sub> ) | 1.71V to 1.89V |

| Output Current (I <sub>OUT</sub> )     | 25A            |

| Junction Temperature (T <sub>J</sub> ) | 0°C to 125°C |

|----------------------------------------|--------------|

| Peak Output Current (IPK+,MAX)         |              |

### Package Information

| 27 WLCSP                              |                                |

|---------------------------------------|--------------------------------|

| Package Code                          | C272C3+1                       |

| Outline Number                        | <u>21-0928</u>                 |

| Land Pattern Number                   | Refer to Application Note 1891 |

| THERMAL RESISTANCE, FOUR-LAYER BOARD  |                                |

| Junction to Ambient ( $\theta_{JA}$ ) | 19°C/W (Note 3)                |

| Junction to Case ( $\theta_{JC}$ )    | 0.75°C/W                       |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

**Note 1:** Input HF capacitors placed not more than 60 mils away from the V<sub>DDH</sub> pin are required to keep inductive voltage spikes within Absolute Maximum Ratings limits.

Note 2: AC is limited to 25ns.

Note 3: Data taken using Analog Devices' evaluation kit with no air flow and no heatsink.

# Integrated, Step-Down Switching Regulator with Selectable Applications Configurations

### **Electrical Characteristics**

$(V_{CC} = 1.8V \pm 5\%, V_{DDH} = 12V$  unless otherwise specified. The \* symbol denotes specifications that apply over the temperature range of  $T_J = 0^{\circ}C$  to 125°C. Otherwise, specifications are for  $T_J = 32^{\circ}C$ . The # denotes parameters that are programmable. Limits are 100% tested at  $T_A = +32^{\circ}C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

| PARAMETER                                                                        | SYMBOL                               | CONDITIONS                                                                                                                         | MIN  | TYP  | MAX    | UNITS |

|----------------------------------------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------|------|--------|-------|

| SUPPLY VOLTAGES, SUPPLY CUR                                                      | RENT, TEMPEI                         | RATURE RANGE                                                                                                                       | ·    |      |        |       |

| 12V Supply Voltage Range                                                         | VDDH                                 | *                                                                                                                                  | 4.5  |      | 16     | V     |

| 1.8V Supply Voltage Range                                                        | Vcc                                  | *                                                                                                                                  | 1.71 | 1.8  | 1.89   | V     |

|                                                                                  |                                      | CCM *                                                                                                                              |      |      | 35     |       |

| V <sub>CC</sub> Supply Current                                                   | Supply Current I <sub>CC</sub> DCM * | DCM *                                                                                                                              |      |      | 25     | mA    |

|                                                                                  |                                      | Shutdown *                                                                                                                         |      | 32   | 132    | μA    |

| V <sub>REF</sub>                                                                 |                                      |                                                                                                                                    |      |      |        |       |

| Programmable Deference Veltage                                                   |                                      | # (See Table 2)                                                                                                                    |      | 0.6  |        | V     |

| Programmable Reference Voltage                                                   |                                      | # (See Table 3)                                                                                                                    |      | 0.95 |        | v     |

| V <sub>REF</sub> Tolerance (V <sub>REF_TOL</sub> )                               | V <sub>REF</sub>                     | T = 35°C (Note 4)                                                                                                                  | -0.5 |      | +0.5   | %     |

| V <sub>REF</sub> Tolerance Temperature<br>Coefficient (V <sub>REFT_COEFF</sub> ) |                                      | 0°C < T <sub>J</sub> < 100°C (Note 4)                                                                                              |      |      | 0.0106 | %/°C  |

| FEEDBACK LOOP                                                                    |                                      |                                                                                                                                    | ·    |      |        |       |

|                                                                                  |                                      | # (See Table 3)                                                                                                                    |      | 1.4  |        |       |

| R <sub>SENSE</sub> GAIN                                                          | Gain                                 |                                                                                                                                    |      | 2.8  |        | mV/A  |

|                                                                                  |                                      |                                                                                                                                    |      | 5.4  |        |       |

| SWITCHING FREQUENCY                                                              |                                      | ·                                                                                                                                  |      |      |        |       |

| Switching Frequency Accuracy                                                     |                                      | Relative to the nominal value (see Figure 4).<br>0A < I <sub>LOAD</sub> < Full Load V <sub>CC</sub> , V <sub>DDH</sub> $\pm$ 10% * | -20  |      | +20    | %     |

| Low f <sub>SW</sub> Threshold                                                    | fsw                                  | DCM enabled                                                                                                                        |      | 30   |        | kHz   |

| Forced Minimum f <sub>SW</sub>                                                   |                                      | DCM enabled. The low f <sub>SW</sub> threshold has been crossed.                                                                   |      | 60   |        | kHz   |

| INPUT PROTECTION                                                                 |                                      |                                                                                                                                    |      |      |        |       |

| Rising V <sub>DDH</sub> UVLO Threshold                                           |                                      |                                                                                                                                    | 3.85 | 4.15 | 4.40   | V     |

| Falling V <sub>DDH</sub> UVLO Threshold                                          | LO Threshold *                       | 3.70                                                                                                                               | 3.98 | 4.25 | V      |       |

| Rising V <sub>DDH</sub> OVLO Threshold                                           | ng V <sub>DDH</sub> OVLO Threshold   |                                                                                                                                    | 16.6 | 17.3 | 17.8   | V     |

| Falling V <sub>DDH</sub> OVLO Threshold                                          | V <sub>DDH</sub> OVLO                |                                                                                                                                    | 16.1 | 16.7 | 17.3   | V     |

| Rising $V_{CC}$ UVLO Threshold                                                   |                                      | *                                                                                                                                  | 1.49 | 1.62 | 1.70   | V     |

| Falling V <sub>CC</sub> UVLO Threshold                                           | V <sub>CC</sub> UVLO                 |                                                                                                                                    | 1.46 | 1.57 | 1.65   | V     |

| Rising VBST UVLO Threshold                                                       | \/ IN // O                           | *                                                                                                                                  | 1.48 | 1.57 | 1.70   | V     |

| Falling V <sub>BST</sub> UVLO Threshold                                          | V <sub>BST</sub> UVLO                |                                                                                                                                    | 1.33 | 1.52 | 1.65   | V     |

# Integrated, Step-Down Switching Regulator with Selectable Applications Configurations

### **Electrical Characteristics (continued)**

$(V_{CC} = 1.8V \pm 5\%, V_{DDH} = 12V$  unless otherwise specified. The \* symbol denotes specifications that apply over the temperature range of T<sub>J</sub> = 0°C to 125°C. Otherwise, specifications are for T<sub>J</sub> = 32°C. The # denotes parameters that are programmable. Limits are 100% tested at T<sub>A</sub> = +32°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

| PARAMETER                                           | SYMBOL  | CONDITIONS                              | MIN | TYP | MAX  | UNITS |  |

|-----------------------------------------------------|---------|-----------------------------------------|-----|-----|------|-------|--|

| OUTPUT VOLTAGE PROTECTION (                         | OVP)    |                                         |     |     |      |       |  |

| Overvoltage-Protection Rising<br>Threshold          | OVP     | (Note 5)                                | 9.5 | 13  | 16.5 | %     |  |

| Overvoltage-Protection Deglitch Filter<br>Time      | OVP     |                                         | 25  | 30  | 36   | μs    |  |

| Power Good Protection Falling<br>Threshold          |         | (Note 5)                                | -12 | -9  | -4.5 | %     |  |

| Power Good Protection Rising<br>Threshold           | PWRGD   | (Note 5)                                | -9  | -6  | -2   | %     |  |

| Power Good Deglitch Filter Time                     |         |                                         | 25  | 30  | 36   | μs    |  |

| OVERCURRENT PROTECTION (OC                          | ;P)     |                                         |     |     |      |       |  |

|                                                     |         |                                         |     | 16  |      |       |  |

| Positive Overcurrent-Protection<br>Threshold (POCP) |         |                                         |     | 20  |      | A     |  |

|                                                     |         |                                         |     | 24  |      |       |  |

| Negative Overcurrent-Protection<br>Threshold (NOCP) | OCP     | Valley current #                        |     | -16 |      |       |  |

|                                                     |         |                                         |     | -20 |      | A     |  |

|                                                     |         |                                         |     | -24 |      |       |  |

| POCP Threshold Tolerance                            |         | Referenced to nominal value (Note 5) *  | -20 |     | 20   | %     |  |

| Hysteresis (Note 6)                                 |         | Referenced to inception value (Note 5)* | 12  | 15  | 18   | %     |  |

| OVERTEMPERATURE PROTECTIO                           | N (OTP) |                                         |     |     |      |       |  |

| Overtemperature-Protection Inception<br>Threshold   | OTP     | *                                       | 130 | 140 | 150  | °C    |  |

| Hysteresis                                          |         |                                         | -30 |     | -10  | °C    |  |

| TEMPERATURE REPORTING                               |         | 1                                       |     |     |      |       |  |

| Temperature-Reporting Range                         |         |                                         | 0   |     | 125  | °C    |  |

| Temperature-Reporting Tolerance                     | TJ      | *                                       | -4  |     | +4   | °C    |  |

| CURRENT REPORTING                                   | 1       | 1                                       |     |     |      |       |  |

| Current-Reporting Range                             |         |                                         | 0   |     | 25   | A     |  |

|                                                     | LOAD    | From no load to full load *             | -2  |     | +2   | A     |  |

| Current-Reporting Tolerance                         |         | Full load *                             | -8  |     | +8   | %     |  |

# Integrated, Step-Down Switching Regulator with Selectable Applications Configurations

### **Electrical Characteristics (continued)**

$(V_{CC} = 1.8V \pm 5\%, V_{DDH} = 12V$  unless otherwise specified. The \* symbol denotes specifications that apply over the temperature range of T<sub>J</sub> = 0°C to 125°C. Otherwise, specifications are for T<sub>J</sub> = 32°C. The # denotes parameters that are programmable. Limits are 100% tested at T<sub>A</sub> = +32°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

| PARAMETER                                           | SYMBOL              | CONDITIONS                                                                                   | MIN  | ТҮР  | MAX  | UNITS |

|-----------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------|------|------|------|-------|

| OE PIN                                              |                     |                                                                                              |      |      |      |       |

| Input Range                                         | -                   | *                                                                                            | 0    |      | 1.89 | V     |

| Rising Threshold                                    | VOE(H)              | Full V <sub>CC</sub> supply range. Measured at                                               | 0.89 | 1.09 | 1.3  | V     |

| Falling Threshold                                   | V <sub>OE(L)</sub>  | OE Pin *                                                                                     | 0.44 | 0.65 | 0.83 | V     |

| Hysteresis                                          |                     | *                                                                                            | 0.34 | 0.44 | 0.61 | V     |

| Deglitch Filter Time                                | _                   |                                                                                              | 230  |      | 520  | ns    |

| OE Pin Input Resistance                             |                     | UVLO < V <sub>CC</sub> < OVLO *                                                              | 250  | 435  | 490  | kΩ    |

| STARTUP TIMING                                      |                     |                                                                                              |      |      |      |       |

| Enable Time from OE Rise to Start of Regulation     | <sup>t</sup> EN     |                                                                                              | 200  | 300  | 500  | μs    |

|                                                     |                     |                                                                                              |      | 1.5  |      |       |

| Soft-Start Ramp Time                                | tss                 | # (see Table 3)                                                                              |      | 3    |      | ms    |

|                                                     |                     |                                                                                              |      | 6    |      | 1     |

| Dwell Time at V <sub>OUT</sub><br>(DCM Not Allowed) | <sup>t</sup> SETTLE |                                                                                              | 14   |      | 35   | μs    |

| Timing to Charge Boost Capacitor                    | <sup>t</sup> BST    |                                                                                              |      | 8    |      | μs    |

| STAT PIN                                            | 1                   |                                                                                              | !    |      |      | 1     |

| Pullup Voltage                                      | VOHSTAT             |                                                                                              |      |      | 3.6  | V     |

|                                                     |                     | I <sub>STAT</sub> = 4mA *                                                                    |      |      | 0.4  |       |

| Status Output Low                                   | VOLSTAT             | I <sub>STAT</sub> = 0.2mA, 0V < V <sub>CC</sub> < UVLO and<br>0V < V <sub>DDH</sub> < UVLO * |      |      | 0.67 | V     |

|                                                     |                     | I <sub>STAT</sub> = 1.3mA, 0V < V <sub>CC</sub> < UVLO and<br>0V < V <sub>DDH</sub> < UVLO * |      |      | 0.76 |       |

| Status Output High Leakage Current                  | ISTAT               | STAT pull to 3.3V through 20kΩ *                                                             |      |      | 7    | μA    |

| Time from V <sub>OUT</sub> Ramp Completion to       |                     |                                                                                              |      | 128  |      |       |

| STAT Pin Released                                   | <sup>t</sup> STAT   | STAT output low to high # (See Table 3)                                                      |      | 2000 |      | – µs  |

| Fault Clearing                                      |                     | Bad-to-good delay                                                                            | 1.8  | 2    | 2.2  | ms    |

# Integrated, Step-Down Switching Regulator with Selectable Applications Configurations

### **Electrical Characteristics (continued)**

$(V_{CC} = 1.8V \pm 5\%, V_{DDH} = 12V$  unless otherwise specified. The \* symbol denotes specifications that apply over the temperature range of  $T_J = 0^{\circ}C$  to 125°C. Otherwise, specifications are for  $T_J = 32^{\circ}C$ . The # denotes parameters that are programmable. Limits are 100% tested at  $T_A = +32^{\circ}C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

| PARAMETER                                           | SYMBOL    | CONDITIONS                                                                                                                    | MIN  | ТҮР | MAX  | UNITS |

|-----------------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------|------|-----|------|-------|

| PGM PIN                                             |           |                                                                                                                               | •    |     |      |       |

| Reporting Voltage Range                             | VPGM      | System regulating                                                                                                             | 0.5  |     | 1    | V     |

| Resistor Range                                      |           | Twelve options                                                                                                                | 1.78 |     | 162  | kΩ    |

| Resistor Accuracy                                   | R_SEL     | EIA standard resistor values only                                                                                             | -1   |     | +1   | %     |

| Capacitor Range                                     |           | Three options                                                                                                                 | 0    |     | 820  | pF    |

| C_SEL Capacitor Accuracy                            |           |                                                                                                                               | -20  |     | +20  | %     |

| External Capacitance                                | C_SEL     | Load and stray capacitance in addition to C_SEL                                                                               |      |     | 20   | pF    |

| SYSTEM SPECIFICATIONS (Note 6)                      |           |                                                                                                                               |      |     |      | •     |

| Peak-to-Peak Output Ripple Voltage,<br>DCM Disabled | VOUT-RIPL |                                                                                                                               | -1   |     | +1   | %     |

| Peak-to-Peak Input Ripple Voltage                   | VIN-RIPL  | V <sub>DDH</sub> = 10.8V - 13.2V                                                                                              | -1   |     | +1   | %     |

| Line Regulation                                     |           | V <sub>DDH</sub> = 10.8V - 13.2V                                                                                              |      |     | 0.15 | %     |

| Load Regulation (Static)                            |           | IOUT = 0A - I <sub>MAX</sub>                                                                                                  | -0.5 |     | +0.5 | %     |

| Load Regulation (Dynamic)                           | VOUT      | V <sub>DDH</sub> = 10.8V - 13.2V, I <sub>OUT</sub> step 6A at<br>36A/µs, 1kHz - 1MHz repetition rate,<br>10% - 90% duty cycle | -3   |     | +3   | %     |

Note 4: To calculate the total V<sub>REF</sub> tolerance over a temperature variation of  $\Delta T$ :

### $V_{REF_TOL_TOT} = V_{REF_TOL} + |\Delta T| \times V_{REF_T_COEFF}$

**Note 5:** Min/max limits are  $\ge 4\sigma$  about the mean.

Note 6: The OCP hysteresis is for positive current OCP only, negative current OCP hysteresis is always 0.

**Note 7:** Tested using circuit of Reference Schematic (Figure 9) with C<sub>OUT</sub> = 15 x 22µF. V<sub>OUT</sub> = 1.05V. Not guaranteed; for reference only.

# Integrated, Step-Down Switching Regulator with Selectable Applications Configurations

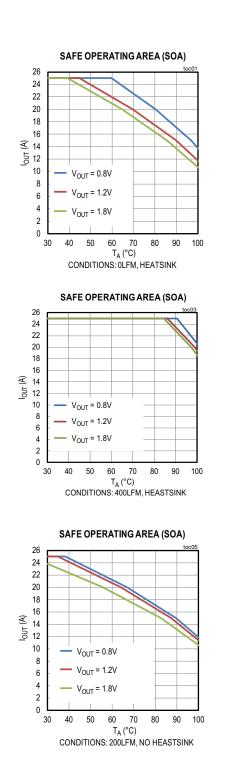

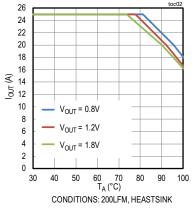

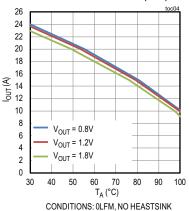

### **Typical Operating Characteristics**

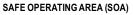

(V<sub>DDH</sub> = 12V, V<sub>CC</sub> = 1.8V. Curve indicates T<sub>CASE</sub> = 125°C or I<sub>OUT</sub> = I<sub>MAX</sub>, whichever happens first.)

#### SAFE OPERATING AREA (SOA)

SAFE OPERATING AREA (SOA)

-

# Integrated, Step-Down Switching Regulator with Selectable Applications Configurations

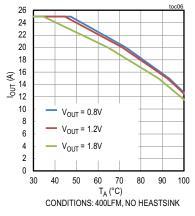

### **Typical Operating Characteristics (continued)**

$(V_{DDH} = 12V, V_{CC} = 1.8V, f_{SW}$  Setting #6,  $C_{OUT} = 5 \times 22\mu F + 4 \times 47\mu F$ ,  $L_{OUT} = 680nH$  for  $V_{OUT} \ge 2.5V$ ,  $L_{OUT} = 200nH$  for  $V_{OUT} \le 1.8V$ )

#### POWER DISSIPATION vs. LOAD CURRENT

# Integrated, Step-Down Switching Regulator with Selectable Applications Configurations

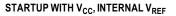

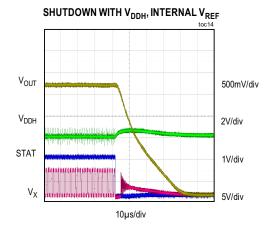

**Typical Operating Characteristics (continued)** ( $V_{DDH} = 12V$ ,  $V_{CC} = 1.8V$ ,  $V_{OUT} = 2.5V$ , Circuit of Figure 3, R\_SEL = 6.04k $\Omega$ , R<sub>FB1</sub> = 4.32k $\Omega$ , R<sub>FB2</sub> = 2.61k $\Omega$ , No heatsink, I<sub>LOAD</sub> = 15A, unless otherwise noted.)

SHUTDOWN WITH OE, INTERNAL VREF toc12 VOUT 500mV/div OE 500mV/div STAT 1V/div V<sub>X</sub> 5V/div 10µs/div

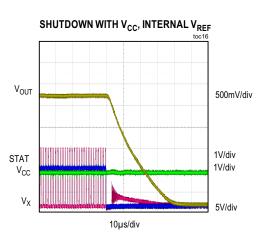

# Integrated, Step-Down Switching Regulator with Selectable Applications Configurations

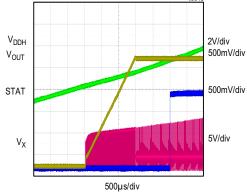

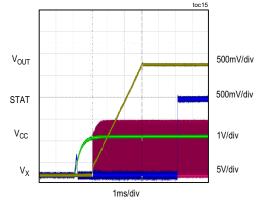

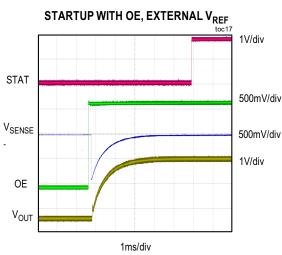

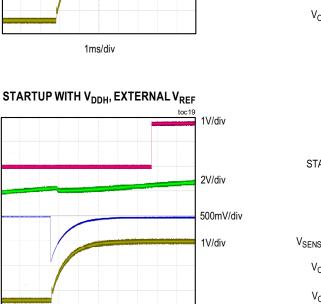

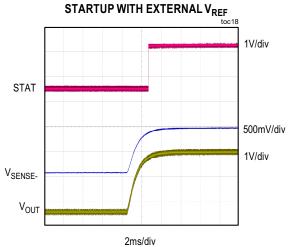

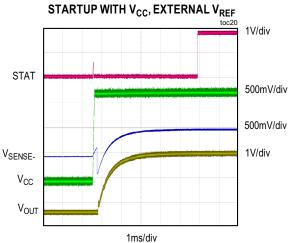

**Typical Operating Characteristics (continued)** ( $V_{DDH} = 12V$ ,  $V_{CC} = 1.8V$ ,  $V_{OUT} = 2.5V$ , Circuit of Figure 6, R\_SEL = 9.09k $\Omega$ , R<sub>FB1</sub> = 4.32k $\Omega$ , R<sub>FB2</sub> = 2.61k $\Omega$ , External V<sub>REF</sub> = 0.95V. No heatsink, unless otherwise noted.)

1ms/div

STAT

V<sub>DDH</sub>

V<sub>SENSE-</sub>

V<sub>OUT</sub>

# Integrated, Step-Down Switching Regulator with Selectable Applications Configurations

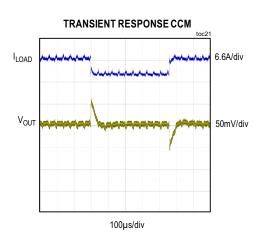

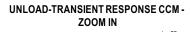

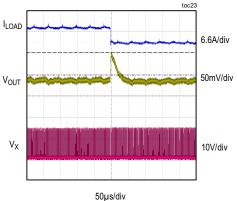

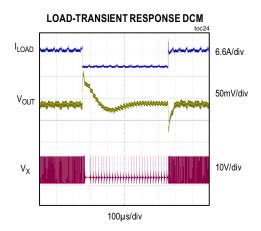

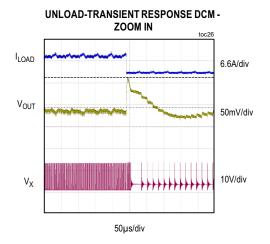

**Typical Operating Characteristics (continued)** (V<sub>DDH</sub> = 12V, V<sub>CC</sub> = 1.8V, V<sub>OUT</sub> = 2.5V, Circuit of Figure 3, C<sub>OUT</sub> = 5 x 22µF + 4 x 47µF, L = 680nH, f<sub>SW</sub> Setting #6, Load Step = 6A at 36A/µs.)

#### www.analog.com

# Integrated, Step-Down Switching Regulator with Selectable Applications Configurations

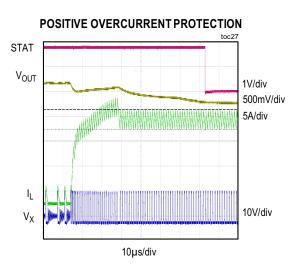

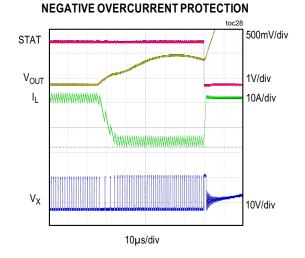

**Typical Operating Characteristics (continued)** (V<sub>DDH</sub> = 12V, V<sub>CC</sub> = 1.8V, V<sub>OUT</sub> = 2.5V, Circuit of Figure 3, C<sub>OUT</sub> = 5 x 22µF + 4 x 47µF, L = 680nH, f<sub>SW</sub> Setting #6, OCP = 16A. No heatsink, unless otherwise noted.)

#### www.analog.com

# Integrated, Step-Down Switching Regulator with Selectable Applications Configurations

#### (TOP VIEW) (BOTTOM VIEW) 3 2 2 3 4 4 1 1 ( ( $\left( \right)$ (G ( G GND GND GND GND GND GND GND GND ( $\bigcirc$ F ( (( F VX VX VX VX VX VX VX VX . Е ( ( Е GND GND GND GND GND GND GND () VX (D (D VX VX VX VX VX VX VX (С ( С VDDH BST VDDH VDDH VDDH BST VDDH VDDH В В ( ( 0E VSENSE+ PGM PGM VSENSE+ OE Vcc Vcc ( А ( ( ( А Agnd STAT STAT VSENSE-AGND VSENSE-

# Pin Configuration

# Integrated, Step-Down Switching Regulator with Selectable Applications Configurations

# **Pin Description**

| PIN          | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                                      |

|--------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1           | SENSE- | Negative Remote-Sense/External-Reference Input. Connect the SENSE- pin to ground at the load with a Kelvin connection to use the internal voltage reference, or connect the pin to an external reference voltage as shown in Figure 6.                                                                                                                        |

| A2           | AGND   | Analog/Signal Ground. Connect to ground plane following the recommendations mentioned in the <i>Printed Circuit Board Layout</i> section.                                                                                                                                                                                                                     |

| A4           | STAT   | Open-Drain Status Output. This pin is pulled low to indicate a fault or output-undervoltage and output-overvoltage events.                                                                                                                                                                                                                                    |

| B1           | PGM    | Programming Input/Telemetry Output. Connect PGM to analog ground using a programming resistor and capacitor. The resistance and capacitance values are measured at startup to determine the desired regulator settings (see Table 3a and 3b). Refer to the <i>Current/Temperature Reporting</i> and <i>Programming Options</i> sections for more information. |

| В2           | SENSE+ | Positive Remote-Sense Input. Connect SENSE+ to V <sub>OUT</sub> at the load using a Kelvin connection. A resistive voltage-divider can be inserted between the output and SENSE+ to regulate the output above the reference voltage.                                                                                                                          |

| B3           | OE     | Output-Enable Input. Connect to enable signal through a $20k\Omega$ resistor. When OE is low, the VX node is high-impedance. Toggle OE to clear the fault-protection latch.                                                                                                                                                                                   |

| В4           | Vcc    | Supply-Voltage Input. Use this pin for the regulator's analog, digital and gate drive circuits. Connect $V_{CC}$ to 1.8V and closely bypass the pin to power ground with a 1µF or greater ceramic capacitor.                                                                                                                                                  |

| C1–C3        | VDDH   | Power-Input Voltage. Connect V <sub>DDH</sub> to the input power supply source. High-frequency ceramic decoupling capacitors must be placed in close proximity to the pin. Refer to Table 4 for decoupling recommendations.                                                                                                                                   |

| C4           | BST    | Bootstrap Supply Input. Connect a 0.47µF ceramic capacitor in close proximity to the IC between BST and VX, as specified in Table 4 and the <i>Printed Circuit Board Layout</i> section.                                                                                                                                                                      |

| D1–D4, F1–F4 | VX     | Switching Node. Connect to the switching node of the power inductor.                                                                                                                                                                                                                                                                                          |

| E1–E4, G1–G4 | GND    | Power Ground. Connect to the return path of the output load.                                                                                                                                                                                                                                                                                                  |

# Integrated, Step-Down Switching Regulator with Selectable Applications Configurations

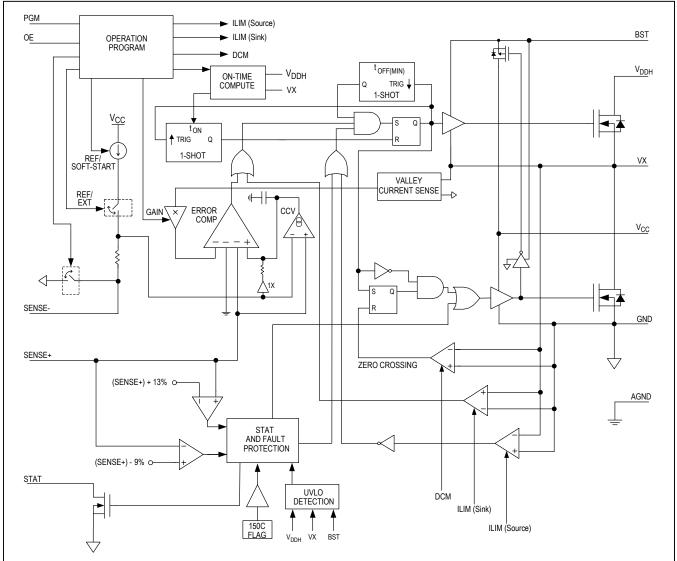

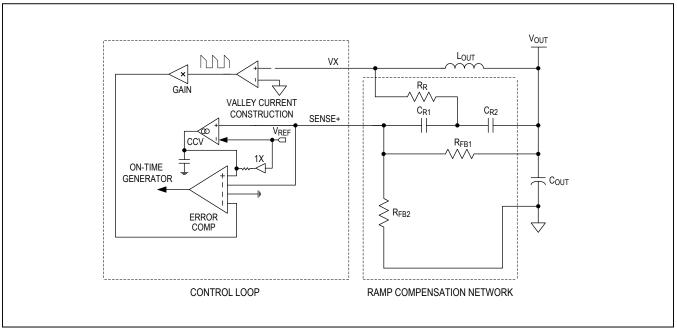

### Block Diagram

### **Detailed Description**

### **Control Architecture**

The MAX16425/MAX16425A step-down regulators are ideal for low-duty cycle (high-input voltage to low-out-put voltage) applications. Analog Devices' proprietary Quick-PWM pulse-width modulator in the MAX16425/MAX16425A is a pseudo-fixed frequency, constant on-time, current-mode regulator with voltage feed-forward (*Block Diagram*). The architecture is specifically designed for handling fast load steps while maintaining a relatively constant operating frequency and inductor operating

point over a wide range of input voltages. This approach circumvents the poor load-transient timing problems of fixed-frequency, current-mode PWMs while also avoiding the problems caused by widely varying switching frequencies in conventional constant-on-time pulse-frequency modulation control schemes, regardless of input voltage.

Traditional constant on-time architectures require an output capacitor with a specified minimum ESR to ensure stable operation. This restriction does not apply to the MAX16425/MAX16425A because the inductor valley current is added to the feedback signal using a proprietary current-sense method, which improves stability.

# Integrated, Step-Down Switching Regulator with Selectable Applications Configurations

The control algorithm is simple: the high-side switch on-time is determined solely by a one-shot whose pulse width is inversely proportional to input voltage and directly proportional to output voltage (Equation 1). Another oneshot sets a minimum off-time of 100ns (typ).

Under normal operating conditions, the on-time one-shot is triggered if the sum of the feedback voltage and the valley current-sense signal falls below the control voltage, and the minimum off-time one-shot has timed out. The  $t_{ON}$  pulse width is clamped to a maximum of 2.5µs.

#### **Equation 1**

$$t_{ON} = \frac{VX_{AVE}}{f_{SW} \times V_{DDH}}$$

where:

$f_{SW} = Switching frequency (MHz)$  $t_{ON} = On-time period for high-side switch (<math>\mu$ s) VX<sub>AVE</sub> = Average VX voltage (V) V<sub>DDH</sub> = Input voltage (V)

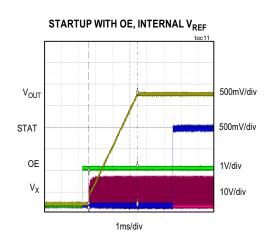

### Voltage Regulator Enable and Turn-On Sequencing

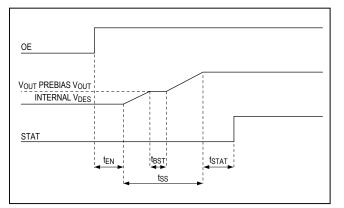

The startup sequence is shown in Figure 1. Once the OE pin rises above the  $V_{OE(H)}$  threshold, the control circuits wait for a 300µs t<sub>EN</sub> time to allow the bias circuits, analog blocks, and other circuits to settle to their proper states before beginning the regulation.

The OE pin has a voltage rating of 1.8V. For control signal voltages higher than 1.8V, a resistor-divider network must be used to drive the OE pin.

In addition, the impedance of the OE pin is reduced when the V<sub>CC</sub> is below UVLO. To prevent any damage to the part due to lowering the impedance, a resistor is used to limit the current. For 1.8V control signals, this resistor has a value of 20k $\Omega$  and it is placed in series with the OE pin. For higher drive voltages to OE that require a resistive voltage-divider, choose 20k $\Omega$  for the bottom resistor to ground. The top resistor is given by Equation 2. Use closest higher resistor value available.

#### **Equation 2**

$$R_{TOP} = 20k\Omega \times \left[ \left( \frac{V_{SIG}}{1.8V} \right) - 1 \right]$$

Output enable delay timing can be added using an RC network connected between control signal and OE pin. R-C delay networks are designed based on desired turn on/off timings and the  $V_{OE(H)}/V_{OE(L)}$  thresholds.

The OE pin has nominal input impedance, which should be included in calculations for the divider network (see the *Electrical Characteristics* table for nominal impedance).

When the system pulls OE low, the MAX16425/ MAX16425A enter low-power shutdown mode. STAT is pulled low immediately. The MAX16425/MAX16425A discharge the inductor by keeping the low-side FET enabled until the current reaches zero. Under these conditions, both power FETs are in high-impedance and the regulator enters shutdown.

#### Soft-Start Control

Once the OE reaches its threshold and the  $t_{EN}$  has elapsed, the regulator performs the bootstrap capacitor charging sequence. After bootstrap capacitor is fully charged, the internal reference voltage starts ramping to the target voltage with the appropriate soft-start time (t<sub>SS</sub>). Both soft-start timing, and target voltage can be programmed (see the <u>Programming Options</u> section, and <u>Table 3a</u> and <u>3b</u>).

If the regulator is enabled with a prebiased output voltage, the system does not regulate until the reference voltage ramps above the SENSE+ node voltage. Upon reaching the SENSE+ voltage, the regulator performs the C<sub>BST</sub> charging sequence and starts normal operation. If, at the end of t<sub>SS</sub>, the SENSE+ pin voltage is still higher than the internal reference, continuous conduction mode (CCM) operation is forced for a short period of time (t<sub>SETTLE</sub>) to discharge the output to the desired voltage. After this period, discontinuous conduction mode (DCM) is allowed, if selected, and the OVP/UVP circuitry becomes active.

# Integrated, Step-Down Switching Regulator with Selectable Applications Configurations

#### **Remote Output Voltage Sensing**

Remote output-voltage sensing is implemented to improve output-voltage regulation accuracy at the load. This technique reduces errors due to voltage drops in the plane impedance between the load and the MAX16425/MAX16425A, particularly in cases where the load is placed away from the MAX16425/MAX16425A. Remote output-voltage sensing is implemented by using the SENSE- node as a reference for the internal voltage reference  $V_{\text{REF}}$ .

#### **Switching Operation Modes**

The MAX16425/MAX16425A support both CCM and DCM. The mode of operation can be programmed as indicated in the *Programming Options* section, and Table 3a and 3b.

If DCM is enabled, MAX16425/MAX16425A transition seamlessly to DCM at light loads to improve efficiency. Once in DCM, the switching frequency decreases as load decreases until a minimum frequency of 30kHz is reached. The purpose of this minimum switching frequency limitation is to prevent operation in the audible frequency range to reduce audible noise.

If the load is such that no  $t_{ON}$  pulse is generated for ~33µs (1/30kHz) since the last pulse was issued, the low-side FET is turned ON until the error comparator commutates, and a  $t_{ON}$  pulse is issued. Once this minimum frequency mode is entered, the IC operates with a minimum switching frequency of 60kHz, to provide proper hysteresis and prevent the IC from moving in and out of this mode.

Figure 1. Startup Timing

### **Protection And Status Features**

#### **Output Voltage Protection (OVP)**

The SENSE+ pin is continuously monitored for both undervoltage and overvoltage conditions. If the output voltage falls below the PWRGD threshold (9% of programmed output voltage) for more than 30µs (typ), the STAT pin is driven low while the MAX16425/MAX16425A continue to operate, attempting to maintain regulation. If the output voltage rises above the overvoltage protection threshold (13% of programmed output voltage) for more than 30µs (typ), the STAT pin is driven low and the MAX16425/MAX16425A latch off (high-side and low-side FETs turn off). Toggle OE or cycling V<sub>CC</sub> supply is required to clear fault conditions.

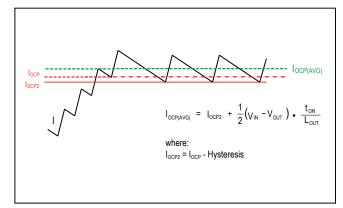

#### **Current Limiting**

The MAX16425/MAX16425A have a current limit that can be programmed using the appropriate R\_SEL value (see Table 3a and 3b). The overcurrent protection (OCP) monitors and limits the low-side FET current on a cycle-by-cycle basis. If the minimum instantaneous "valley" low-side switch current level exceeds the OCP (source) level, the IC delays the next on-time pulse until the current falls below the threshold level (Figure 2). Since the regulator responds to the inductor valley current, the DC current delivered during positive (source) current limit is the programmed valley current (I<sub>OCP</sub> - hysteresis) plus half of the inductor ripple. During the current limit event (source), the output voltage drops and if the voltage reaches the PWRGD threshold, the STAT pin is driven low.

Figure 2. Inductor Current During Current Limit Event

# Integrated, Step-Down Switching Regulator with Selectable Applications Configurations

The MAX16425/MAX16425A also have negative OCP limits (Sink). When this threshold is reached, the IC issues an on-time pulse to limit the negative current. This on-time pulse is issued regardless of the error comparator state. Therefore, it is possible to cause an overvoltage protection (OVP) event if the negative load exceeds the negative current limit.

#### **UVLO and OVLO Protection**

The regulator monitors V<sub>DDH</sub> with both undervoltage lockout (UVLO) and overvoltage lockout (OVLO) circuits. UVLO protection is also present on BST and V<sub>CC</sub> supplies. When any of the supply voltages is below the UVLO threshold or V<sub>DDH</sub> is above the OVLO threshold, the regulator stops switching, and the STAT pin is driven low (refer to the *Electrical Characteristics* table for UVLO and OVLO levels).

#### **Overtemperature Protection (OTP)**

If the die temperature exceeds the overtemperature threshold during operation, the MAX16425/MAX16425A stop regulation and the STAT pin is driven low. Regulation starts again once the die temperature falls below the new overtemperature threshold (overtemperature threshold - hysteresis) value. The STAT pin eventually goes high again once the output voltage reaches the expected value.

#### **Regulator Status**

The regulator status (STAT) signal provides an opendrain output (4V max, refer to the <u>Absolute Maximum</u> <u>Rating</u> section) that indicates whether the MAX16425/ MAX16425A are functioning properly. An external pullup resistor is required.

After the startup ramp is completed ( $t_{STAT}$ ), if the output voltage is within the PWRGD/OVP regulation window, the STAT pin goes high impedance. The STAT pin is driven low when one or more of the following conditions exist:

#### • OE is low

- V<sub>DDH</sub> or V<sub>CC</sub> are not present or below/above the respective UVLO/OVLO thresholds.

- A PWRGD fault is present (see the <u>Output Voltage</u> <u>Protection (OVP)</u> section).

- The SENSE- or SENSE+ pin is left unconnected at startup.

- The die temperature is above the maximum allowed temperature.

- The OVP circuit has detected that the output voltage is above the tolerance limit.

- UVLO is detected on bootstrap supply (BST-VX), indicating possible short or open bootstrap capacitor.

#### **Current/Temperature Reporting**

During regulation, an analog voltage is produced on the PGM pin that represents either average output current or chip temperature (see <u>Table 3a</u> and <u>3b</u> for proper settings). The PGM pin has an output-voltage range of 0.5V to 1V. The PGM output is designed to drive the R\_SEL/C\_SEL network with an additional 20pF external load (including parasitics), which allows this node to be connected to external circuitry, such as a voltage buffer or ADC.

The conversion equations for temperature and current reporting are shown in Equation 3 and Equation 4.

#### **Equation 3**

$$T_{REPORTED} = (V_{PGM} - Tr_{OFFSET}) \times Tr_{SLOPE}$$

$$Tr_{OFFSET} = 0.592V$$

$$Tr_{SLOPE} = 611 \frac{C}{V}$$

#### **Equation 4**

$I_{REPORTED} = (V_{PGM} - I_{rOFFSET}) \times I_{rSLOPE}$  $I_{rOFFSET} = 0.495V$

$$Ir_{SLOPE} = 86.2 \frac{A}{V}$$

| FAULT TYPE                       | REGULATOR RESPONSE    | STAT                       | DESCRIPTION                                       |

|----------------------------------|-----------------------|----------------------------|---------------------------------------------------|

| Power Good (PWRGD)               | Continue Operation    | LOW                        | V <sub>OUT</sub> < (1 - 9%) V <sub>OUTNOM</sub>   |

| Overvoltage Protection (OVP)     | Shutdown and Latchoff | LOW                        | V <sub>OUT</sub> > (1 + 13%) V <sub>OUTNOM</sub>  |

| Overtemperature Protection (OTP) | Shutdown              | LOW                        | T <sub>J</sub> > 140°C                            |

| Overcurrent Protection (OCP)     | Clamping              | V <sub>OUT</sub> Drop, LOW | Valley current higher than selected limit         |

| Boost Undervoltage               | Shutdown              | LOW                        | (BST - VX ) < 1.52V                               |

| V <sub>DDH</sub> Supply          | Shutdown              | LOW                        | V <sub>DDH</sub> < 4.5V or V <sub>DDH</sub> > 16V |

| V <sub>CC</sub> Supply           | Shutdown              | LOW                        | V <sub>CC</sub> < 1.57V                           |

| SENSE-/SENSE+ Disconnected       | Do Not Start          | LOW                        | Open Sense Lines                                  |

### **Table 1. Summary of Fault Actions**

# Integrated, Step-Down Switching Regulator with Selectable Applications Configurations

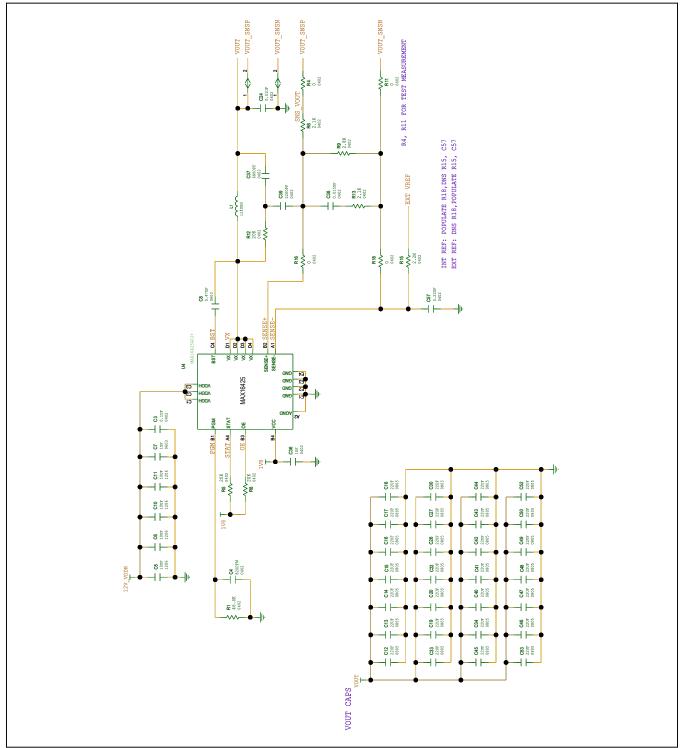

### **Reference Design**

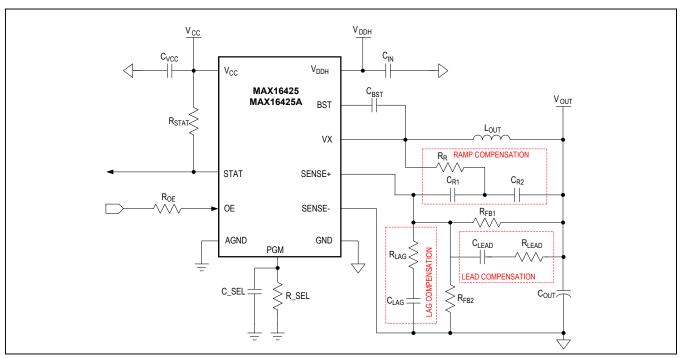

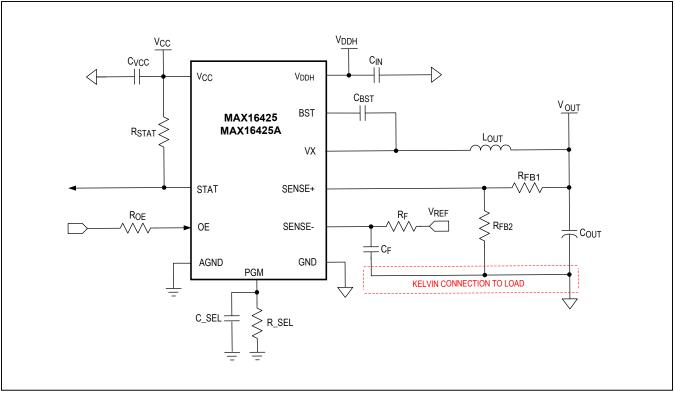

The typical application circuit is shown in Figure 3.

#### **Programming Options**

The MAX16425/MAX16425A allow programming of several key parameters to allow optimization for specific applications. The parameters that are programmable are shown in <u>Table 2</u>. A resistor and capacitor connected from the programming pin to ground select a set of parameters.

By selecting the appropriate values of resistor and capacitor, the desired set of parameters (scenario) can be programmed, as shown in Table 3a and 3b.

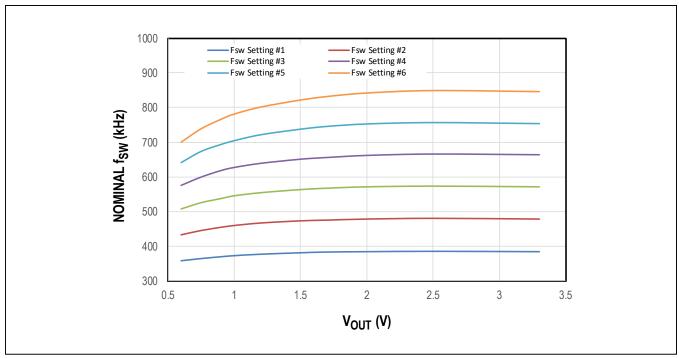

C\_SEL selects the  $f_{SW}$  setting. There are six options available (from #1 to #6), indicating six different nominal switching frequencies, from lowest to highest. Since the actual value of  $f_{SW}$  also depends on  $V_{OUT}$ , refer to Figure 4 to select the proper  $f_{SW}$  setting for a specific application.

The MAX16425/MAX16425A feature two different configuration tables to provide a wider range of options. <u>Table 3a</u> and <u>3b</u> show the scenario options for the MAX16425/MAX16425A, respectively.

Figure 3. Typical Application Circuit

### Table 2. Programmable Options

| PARAMETER               | DESCRIPTION                                                                                                   |

|-------------------------|---------------------------------------------------------------------------------------------------------------|

| V <sub>REF</sub>        | Selects internal or external voltage reference. For internal V <sub>REF</sub> two values are available.       |

| Soft-Start Time         | The time required to ramp the reference voltage to its final value                                            |

| OCP Inception           | The valley current at which the overcurrent protection is tripped (see the Current Limiting section).         |

| Operation Modes         | Selects whether DCM is allowed. If allowed the IC transitions to DCM mode for light loads                     |

| Reporting               | Selects the parameter reported through the analog output voltage on the PGM pin during regulation.            |

| R <sub>SENSE</sub> Gain | Selects the sense loop gain. By changing this value, the operation and components selection can be optimized. |

| fsw                     | Switching frequency setting.                                                                                  |

| <sup>t</sup> STAT       | Time delay between the completion of the soft-start ramp and the STAT pin output is valid.                    |

# Integrated, Step-Down Switching Regulator with Selectable Applications Configurations

|               |                         | SOFT-START              | VALLEY OCP |                    |                             | R <sub>SENSE</sub> | f                  | SW SETTIN          | G                  |                           |

|---------------|-------------------------|-------------------------|------------|--------------------|-----------------------------|--------------------|--------------------|--------------------|--------------------|---------------------------|

| R_SEL<br>(kΩ) | V <sub>REF</sub><br>(V) | TIME (t <sub>SS</sub> ) | INCEPTION  | OPERATION<br>MODES | REPORTING<br>(CURRENT/TEMP) | (GAIN)<br>(mΩ)     |                    |                    |                    | t <sub>STAT</sub><br>(μs) |

| ()            |                         | (ms)                    | (A)        | medice             | (00111211177211177          |                    | 0pF                | 200pF              | 820pF              | (µ3)                      |

| 1.78          | 0.95                    | 6                       |            | CCM                |                             |                    |                    |                    |                    |                           |

| 2.67          |                         | 0                       |            | CCM/DCM            |                             |                    |                    |                    |                    |                           |

| 4.02          |                         | CCM                     |            |                    |                             |                    |                    |                    |                    |                           |

| 6.04          |                         | 3                       | 16         | CCM/DCM            | Current                     | 2.8                | f <sub>SW</sub> #4 | f <sub>SW</sub> #5 | f <sub>SW</sub> #6 |                           |

| 9.09          | Ext.                    |                         |            | CCM                |                             |                    |                    |                    |                    | 2000                      |

| 13.3          | <b>∠</b> XI.            | 1.5                     |            |                    |                             | 2.0                |                    |                    |                    |                           |

| 20            |                         | 24                      | CCM/DCM    |                    |                             |                    |                    |                    |                    |                           |

| 30.9          |                         |                         | 24         | ССМ                |                             |                    |                    |                    |                    |                           |

| 46.4          | 0.6                     | 6                       |            | CCIM               |                             |                    |                    |                    |                    |                           |

| 71.5          |                         |                         | 16         |                    | Temp                        |                    |                    |                    |                    |                           |

| 107           |                         |                         |            | CCM/DCM            | Current                     | 1.1                |                    |                    |                    |                           |

| 162           | Ext.                    | 1.5                     | 20         | CCM                | Temp                        | 1.4                | f <sub>SW</sub> #1 | f <sub>SW</sub> #2 | f <sub>SW</sub> #3 | 128                       |

# Table 3a. MAX16425 Configuration Table

# Table 3b. MAX16425A Configuration Table

| D. 051        |                         | SOFT-START              | VALLEY OCP |                                  | DEDODTINO | RSENSE FSW SETTING |                    |                    | G                  | tSTAT |  |

|---------------|-------------------------|-------------------------|------------|----------------------------------|-----------|--------------------|--------------------|--------------------|--------------------|-------|--|

| R_SEL<br>(kΩ) | V <sub>REF</sub><br>(V) | TIME (t <sub>SS</sub> ) | INCEPTION  | I OPERATION REPORTING (          | MODES     | REPORTING          | (GAIN)             |                    | C_SEL              |       |  |

| ()            |                         | (ms)                    | (A)        |                                  | (,        | (mΩ)               | 0pF                | 200pF              | 820pF              | (µs)  |  |

| 1.78          |                         | 1.5                     |            | CCM                              |           |                    |                    |                    | f <sub>SW</sub> #6 |       |  |

| 2.67          | 0.95                    | 1.5                     |            | CCM/DCM                          |           | 2.8                |                    |                    |                    |       |  |

| 4.02          | 0.95                    |                         | 16         | CCM                              |           |                    | f <sub>SW</sub> #4 | f <sub>SW</sub> #5 |                    |       |  |

| 6.04          |                         |                         | 10         | CCM/DCM                          | Current   |                    |                    |                    |                    |       |  |

| 9.09          | Ext.                    |                         |            | CCM<br>CCM/DCM<br>CCM<br>CCM/DCM |           | 5.4                |                    |                    |                    |       |  |

| 13.3          |                         |                         |            |                                  |           |                    |                    |                    |                    | 2000  |  |

| 20            |                         | 3                       | 24         |                                  |           |                    | 2.0                |                    |                    |       |  |

| 30.9          | 0.6                     |                         | 24         |                                  |           | 2.8                |                    |                    |                    |       |  |

| 46.4          | 0.0                     |                         | 16         |                                  |           |                    | <b>E</b> 4         | ]                  |                    |       |  |

| 71.5          |                         |                         | 16         |                                  |           | 5.4                |                    |                    |                    |       |  |

| 107           | Ext.                    |                         | 20         | ССМ                              | Temp      |                    |                    |                    |                    |       |  |

| 162           |                         | 1.5                     | 20         | CCIVI                            |           | 1.4                | f <sub>SW</sub> #1 | f <sub>SW</sub> #2 | f <sub>SW</sub> #3 | 128   |  |

# Integrated, Step-Down Switching Regulator with Selectable Applications Configurations

Figure 4. Nominal Switching Frequency vs.  $V_{\mbox{OUT}}$  and  $f_{\mbox{SW}}$  Setting

### Setting the Output Voltage

The output voltage of the MAX16425/MAX16425A is set by selecting a reference voltage and using an appropriate resistive voltage-divider, as shown in Equation 5.

The reference voltage is selected using R\_SEL (see Table 3a and 3b) and can be either internal or external (refer to the *Operation with External V<sub>REF</sub>* section for more details). In order to improve the DC output voltage accuracy, use the highest V<sub>REF</sub> value available and suitable for the application.

For instance, use V<sub>REF</sub> = 0.6V for 0.6V  $\leq$  V<sub>OUT</sub> < 0.95V and V<sub>REF</sub> = 0.95V for 0.95V  $\leq$  V<sub>OUT</sub> < 3.3V.

To optimize the common-mode rejection of the error amplifier, choose the voltage-divider resistors so that their parallel resistance is as close as possible to  $2k\Omega$  (Equation 6).

#### **Equation 5**

$$V_{OUT} = V_{REF} \times \left(1 + \frac{R_{FB1}}{R_{FB2}}\right)$$

Refer to Table 3a and 3b for V<sub>REF</sub> values.

#### **Equation 6**

$$R_{FB1} = V_{OUT} \times \left(\frac{R_{PAR}}{V_{REF}}\right)$$

$$R_{FB2} = R_{FB1} \times \left(\frac{R_{PAR}}{R_{FB1} - R_{PAR}}\right)$$

where:

- R<sub>FB1</sub> = Top voltage-divider resistor

- R<sub>FB2</sub> = Bottom voltage-divider resistor

- $R_{PAR}$  = Desired parallel resistance of  $R_{FB1}$  and  $R_{FB2}$

- V<sub>OUT</sub> = Output voltage

- VREF = Reference voltage

# The Effect of Resistor Selection on DC Output Voltage Accuracy

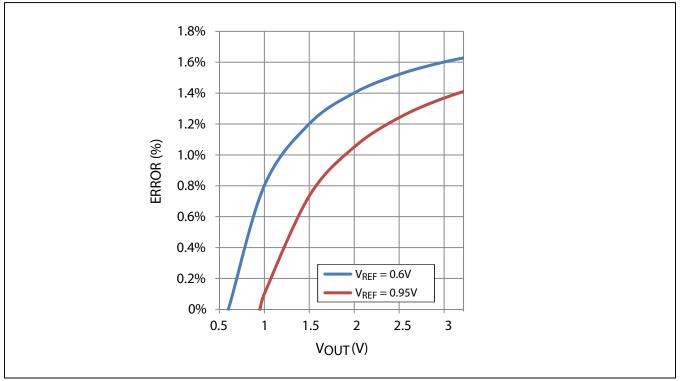

$R_{FB1}$  and  $R_{FB2}$  set the output voltage as described in Equation 5. The tolerance of these resistors affects the accuracy of the programmed output voltage.

#### Equation 7

$$\varepsilon_{\mathsf{RV}_{\mathsf{OUT}}} = \frac{2\varepsilon_{\mathsf{R}}}{1 - \varepsilon_{\mathsf{R}}} \left( \frac{\mathsf{V}_{\mathsf{OUT}} - \mathsf{V}_{\mathsf{REF}}}{\mathsf{V}_{\mathsf{OUT}}} \right)$$

# Integrated, Step-Down Switching Regulator with Selectable Applications Configurations

Figure 5 shows the effect of 1% tolerance resistors over a range of output voltages. To ensure accuracy over temperature, the temperature coefficients must also be included in the error calculation (i.e., for 25ppm/°C resistors over a 50°C excursion, add 0.125% to the 25°C tolerance).

The error due to the voltage-feedback resistors' tolerance,  $R_{FB1}$  and  $R_{FB2}$  should be added to the output voltage tolerance due to the IC's  $V_{REF}$  tolerance listed in the *Electrical Characteristics* table.

#### **Equation 8**

$$\varepsilon_{V_{OUT}} = \varepsilon_{V_{REF}} + \varepsilon_{RV_{OUT}}$$

#### **Voltage Margining**

Voltage margining can be implemented by changing the effective feedback divider ratio. FET switches can be used to introduce or remove parallel resistors to  $R_{FB2}$ , to increase or decrease the output voltage respectively. In order to avoid triggering OVP or UVP faults, the circuits used to introduce resistive divider changes should have switching time constants greater than the response time of the MAX16425/MAX16425A.

#### Operation with External VREF

When using an external reference, adopt the configuration shown in Figure 6. The MAX16425/MAX16425A employ a specialized soft-start sequence. Once OE is asserted, the regulator briefly discharges the SENSE- node and releases it as regulation begins. The resulting soft-start ramp timing is determined by the external low-pass filter time constant. The external filter time constant needs to be lower than  $t_{SS}/3$  in order to avoid premature assertion of the STAT pin while the output voltage is still ramping.

The external reference voltage should be limited between 0.8V and 1.1V and can be applied prior to enabling the regulator, or ramped up right after enable is asserted. In both cases, the low-pass filtered reference voltage at the SENSE- pin must reach its final value within  $t_{SS}$ .

Typical values for the filter components are:

- R<sub>F</sub> = 2.2kΩ

- C<sub>F</sub> = 0.22µF

When changing the external reference voltage during normal operation (after the part has powered up, and reached regulation level), the regulator must be able to

Figure 5. Contribution of 1% Tolerance Resistors on V<sub>OUT</sub> Error

# Integrated, Step-Down Switching Regulator with Selectable Applications Configurations

Figure 6. Electrical Connections to Use the External Voltage Reference Feature

follow the reference-voltage change fast enough as to avoid OVP and PWRGD faults. Please make sure that reference-voltage change timing from the initial to the final value does not exceed 1/(2×BW), where BW is the bandwidth of the regulator in Hertz (Hz).

#### **Control Loop**

The MAX16425/MAX16425A use Quick PWM architecture with current-sense signal added to feedback. Hence, without additional compensation, the voltage-loop gain consists of the following terms:

- The IC's current-mode control scheme has an effective transconductance gain of 1/R<sub>SENSE(GAIN)</sub>. See <u>Table</u> <u>3a</u> and <u>3b</u> for correct R<sub>SENSE(GAIN)</sub> values.

- The output capacitors contribute an impedance gain of 1/(2 × π × C<sub>OUT</sub> × f).

- The feedback divider contributes an attenuation of K<sub>DIV</sub> = R<sub>FB2</sub>/(R<sub>FB1</sub> + R<sub>FB2</sub>).

Thus, when the ramp injection components (R<sub>R</sub>, C<sub>R1</sub>, C<sub>R2</sub>), lead compensation components (C<sub>LEAD</sub>, R<sub>LEAD</sub>) and lag compensation components (R<sub>LAG</sub>, C<sub>LAG</sub>) are not used, the approximate loop gain and bandwidth (BW) are given by the following equations.

#### **Equation 9**

$$|\text{Loop}_Gain(f)| = \frac{K_{DIV}}{2 \times \pi \times R_{SENSE(GAIN)} \times C_{OUT} \times f}$$

$$BW = \frac{K_{DIV}}{2 \times \pi \times R_{SENSE(GAIN)} \times C_{OUT}}$$

or

$$BW = \frac{1}{2 \times \pi \times R_{GAIN} \text{ EFF} \times C_{OUT}}$$

where, R<sub>GAIN\_EFF</sub> equals R<sub>SENSE(GAIN)</sub>/K<sub>DIV.</sub>

For stability,  $C_{OUT}$  should be chosen so that BW <  $f_{SW}/3$ . Designing with no loop compensation can result in fairly large  $C_{OUT}$ ; compensation schemes such as Lead, Lag and Ramp Injection can be used to allow  $C_{OUT}$  reduction.

# Integrated, Step-Down Switching Regulator with Selectable Applications Configurations

These compensations impact the transient performance as they change the BW of the system. This should be included in design analysis.

#### Integrator

The IC has an integrator included in its error amplifier to improve load regulation. The integrator only adds gain at low frequencies, so it does not affect the loop BW; therefore, it was not considered in previous equations. With the integrator, the loop gain from Equation 9 is multiplied by a factor of

$$(1/\tau_{REC} + s)/s$$

where,  $\tau_{REC}$  = 20µs.

#### **Step Response**

$R_{GAIN\_EFF}$  determines the small-signal transient response of the regulator. When a load step is applied that does not exceed the slew rate capability of the inductor current, the regulator responds linearly and  $V_{OUT}$  temporarily changes by the amount of  $V_{OUT\_ERROR}$  (Equation 10a). If the load step applied exceeds the slew rate capability of the inductor current, the voltage deviation ( $V_{OUT\_ERROR}$ ) is solely determined by output filter values (Equation 10a).

The actual voltage deviation (V\_OUT\_ERROR) is given by the largest of the values calculated using Equation 10a and Equation 10b

#### Equation 10.

a)

$$V_{OUT\_ERROR} = I_{STEP} \times R_{GAIN\_EFF}$$

b)  $V_{OUT\_ERROR} \approx \frac{(I_{STEP} \times L)}{2 \times V_{OUT} \times C_{OUT}}$

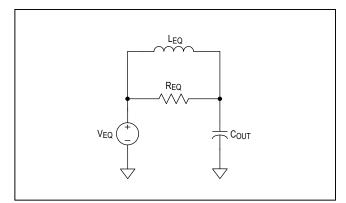

After a transient event, V<sub>OUT</sub> returns to the nominal value with a 20µs time constant, due to the integrator circuit. A first order average small-signal model of the regulator is shown in Figure 7. V<sub>EQ</sub> is an ideal voltage source equal to V<sub>OUT</sub>, R<sub>EQ</sub>. (R<sub>GAIN\_EFF</sub>) is an emulated lossless resistance created by the control-loop action and L<sub>EQ</sub> ( $\tau_{REC} \times R_{GAIN\_EFF}$ ) is an emulated inductance. Note that L<sub>EQ</sub> is not the same as the actual L<sub>OUT</sub> inductor, which has been absorbed into the model. C<sub>OUT</sub> is the actual output capacitance.

Figure 7. Averaged Small-Signal Equivalent Circuit of Regulator

#### Lag Compensation

In cases where the response is faster than desired, the lag compensation network (R<sub>LAG</sub>, C<sub>LAG</sub>) can be used to decrease the BW. This has the effect of lowering the gain contribution of the feedback network at higher frequencies, by effectively placing R<sub>LAG</sub> in parallel with R<sub>FB2</sub>. For the lag network to be effective and to achieve optimal phase margin, the zero at 1/(2 x  $\pi$  x R<sub>LAG</sub> x C<sub>LAG</sub>) should be placed at least a decade below the crossover frequency (BW/10). With lag, K<sub>DIV</sub> near the crossover frequency becomes Equation 11.

#### **Equation 11**

$$K_{\text{DIV}\_\text{LAG}} = \frac{(R_{\text{FB2}} \square R_{\text{LAG}})}{(R_{\text{FB1}} + R_{\text{FB2}} \square R_{\text{LAG}})}$$

$$R_{\text{GAIN}\_\text{EFF}} = \frac{R_{\text{GAIN}}}{K_{\text{DIV}} \square R_{\text{GAIN}}}$$

Lag compensation increases R<sub>GAIN\_EFF</sub> and V<sub>OUT\_ERROR</sub> while decreasing BW. An increase in V<sub>OUT\_ERROR</sub> can also result in higher overshoot at startup especially when the system recovers after hitting OCP. To avoid this, make sure that Equation 12 is satisfied.

#### Equation 12

$$C_{LAG} < \frac{V_{OUT} \times C_{OUT}}{I_{OCP} \times (R_{LAG} + R_{FB1} \square R_{FB2}) \times 3}$$

#### Lead Compensation

In cases where the response is slower than desired, the lead compensation network (R<sub>LEAD</sub>, C<sub>LEAD</sub>) can be used to increase the bandwidth. This has the effect of increasing the gain contribution of the feedback network at higher frequencies, by effectively placing R<sub>LEAD</sub> in parallel with R<sub>FB1</sub>.

# Integrated, Step-Down Switching Regulator with Selectable Applications Configurations

For the lead network to be effective and to achieve optimal phase margin, the zero at  $1/(2 \times \pi \times R_{LEAD} \times C_{LEAD})$  should be placed below the crossover frequency (BW/10 < fz < BW).

With lead compensation,  $K_{\mbox{DIV}}$  near the crossover frequency becomes Equation 13.

#### **Equation 13**

$$K_{DIV\_LEAD} = \frac{R_{FB2}}{(R_{FB1} \square R_{LEAD} + R_{FB2})}$$

$$R_{GAIN\_EFF} = \frac{R_{GAIN}}{K_{DIV\_LEAD}}$$

Lead compensation decreases  $\mathsf{R}_{GAIN\_EFF}$  and  $\mathsf{V}_{OUT\_}$   $_{ERROR}$  while increasing BW accordingly.

#### **External Ramp**

The ramp compensation stabilizes the converter if the ESR of the output capacitor bank is low. The ramp is added to the internal current-sense signal at the error comparator inputs, which improves the signal-to-noise ratio and reduces the offtime jitter.

The amplitude of the external ramp is determined by  $R_R$  and  $C_{R2}$  (Figure 8). A voltage signal, which approximates the inductor current appears across  $C_{R2}$  and it is injected to the feedback node through  $C_{R1}$ .

Values of ramp compensation network are selected as follows:

1) C<sub>R1</sub> is chosen to maximize the coupling of the ramp signal on the feedback node:

C<sub>R1</sub> x R<sub>FB1</sub> || R<sub>FB2</sub> || R<sub>LEAD</sub> || R<sub>LAG</sub> ≈ 10 x t<sub>SW</sub>

- 2)  $C_{R2}$  is chosen such that the ramp signal is unaffected by the value of  $C_{R1}$ :  $C_{R2} \approx 10 \times C_{R1}$ .

- R<sub>R</sub> is chosen to achieve the desired ramp injection signal. Use Equation 14 to calculate proper R<sub>R</sub> value.

The approximate amplitude of the external ramp at the SENSE+ pin is given by Equation 14.

**Equation 14**

V

$$\mathsf{RAMP}_\mathsf{EXT} = \frac{\mathsf{V}_\mathsf{OUT} \times (\mathsf{V}_\mathsf{IN} - \mathsf{V}_\mathsf{OUT})}{(\mathsf{V}_\mathsf{IN} \times \mathsf{R}_\mathsf{R} \times \mathsf{C}_\mathsf{R2} \times \mathsf{f}_\mathsf{SW})}$$

The sensed inductor current ramp at the comparator input is given in Equation 15.

#### Equation 15

$$V_{RAMP\_IND} = \frac{R_{GAIN} \times V_{OUT} \times (V_{IN} - V_{OUT})}{(V_{IN} \times L_{OUT} \times f_{SW})}$$

where, R<sub>GAIN</sub> equals the internal current sense gain (see <u>Electrical Characteristics</u> table)

Figure 8. Ramp Compensation Diagram

The high-frequency gain from SENSE+ to the comparator input is unity. Therefore, with the external ramp, the comparator sees an effective ramp given in Equation 16.

#### **Equation 16**

V<sub>RAMP\_EFF</sub> = V<sub>RAMP\_IND</sub> + V<sub>RAMP\_EXT</sub>

$$= V_{OUT} \times \frac{(V_{IN} - V_{OUT})}{(V_{IN} \times L_{OUT} \times f_{SW})} \times \left[ R_{GAIN} + \frac{L_{OUT}}{(R_R \times C_{R2})} \right]$$

For best results, it is recommended that  $\mathsf{V}_{RAMP\_EFF}$  be at least 15mV.

The effective  $R_{GAIN}$  with external ramp is given in Equation 17.

#### **Equation 17**

$$R_{GAIN\_EFF} = R_{GAIN} + \frac{L_{OUT}}{(R_R \times C_{R2})}$$

The ramp injection capacitors effectively bypass the divider near the cross-over frequency, so in this case  $K_{DIV}$  is approximately 1 and drops out of the loop gain equation.

Similar to lag compensation, ramp injection increases  $R_{GAIN\ EFF}$  and  $V_{OUT\ ERR}.$

#### **Inductor Selection**

The inductor value is selected based on the switching frequency and the percentage ratio of the inductor ripple to the peak load current (LIR - inductor current ratio).

#### **Equation 18**

$$L = \left[\frac{(V_{IN} - V_{OUT})}{f_{SW} \times I_{LOAD}(MAX) \times LIR}\right] \times \frac{V_{OUT}}{V_{IN}}$$

where:

| LIR                    | = Inductor current ratio |

|------------------------|--------------------------|

| I <sub>LOAD(MAX)</sub> | = Peak load current      |

# Integrated, Step-Down Switching Regulator with Selectable Applications Configurations

A lower LIR results in lower RMS losses in passive and active components, which improves the regulator efficiency. A higher LIR results in faster inductor current slew rate, better transient performance and lower inductor value/ size. Optimal inductor selection is performed by evaluating these trade-offs according to design requirements.

The inductor must have a saturation current higher than the peak current during OCP event. The highest peak current is reached when a hard  $V_{OUT}$  short circuit is applied during operation (See Equation 19). In addition, the application circuit design must ensure that the peak current never exceeds the maximum operating current (I<sub>PK</sub>) listed in the *Operating Ratings* section.

#### Equation 19

$$I_{SAT} > I_{PK(MAX)} = I_{OCP} + \frac{V_{OUT}}{L \times f_{SW}}$$

where:

I<sub>SAT</sub> = Inductor saturation current

I<sub>OCP</sub> = Overcurrent protection threshold (see <u>Table 3a</u> and <u>3b</u>)

#### **Output Capacitor Selection**

Output capacitor selection is based on output-ripple and load-transient requirements. Low ESR capacitors (MLCCs) are recommended to minimize ripple.