## Integrated TFT Power Supplies and LED Backlight Drivers

#### **General Description**

The MAX20070/MAX20070B are highly integrated power supplies and LED backlight drivers for automotive TFT-LCD applications. The devices integrate one buckboost converter, one boost converter, two gate-driver supplies, and a boost/SEPIC converter that can power one to two strings of LEDs in the display backlight.

The source-driver power supplies consist of a boost converter and an inverting buck-boost converter that can generate voltages up to +15V and -15V. Both source-driver power supplies can deliver up to 100mA. The positive source-driver supply regulation voltage ( $V_{POS}$ ) is set by connecting an external resistor-divider on FBP. Connecting the FBP pin to ground sets the regulation voltage ( $V_{POS}$ ) to +6.5V. The negative source-driver supply voltage ( $V_{NEG}$ ) is always tightly regulated to - $V_{POS}$  within ±50mV. The source-driver supplies use an input voltage from 2.7V to 5.5V to generate the output voltages.

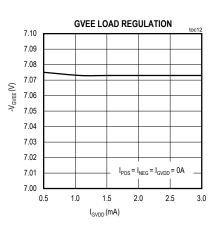

The gate-driver power supplies consist of regulated charge pumps that generate up to +22V and -22V and can deliver up to 3mA each. The regulation voltage ( $V_{GVDD}$ ) on the positive charge pump is set by a resistor-divider on FBPG; the regulation voltage ( $V_{GVEE}$ ) on the negative charge pump is set by a resistor-divider on FBNG.

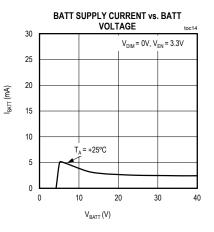

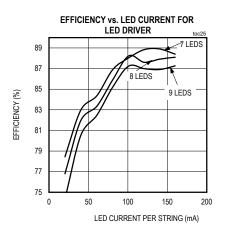

The ICs feature a dual-string LED driver that operates off a separate input voltage ( $V_{BATT}$ ) and can power up to two strings of LEDs with 160mA (max) of current per string.

The startup and shutdown sequences for all power domains are controlled using one of the seven preset modes that are selectable through a resistor on SEQ.

The MAX20070/MAX20070B are available in a 32-pin, 5mm x 5mm TQFN package with an exposed pad, and operate over the -40°C to +105°C ambient temperature range.

### **Applications**

- Automotive Dashboards

- Automotive Central Information Displays

- Automotive Head-Up Displays

- Automotive Navigation Systems

#### **Benefits and Features**

- Integrates Both TFT Power Supplies and LED Backlight Driver in One IC, Reducing Component Count

- Alleviates EMI Due to Spread Spectrum on Both Source Driver Supplies and LED Driver

- 10000:1 Dimming Ratio at 200Hz Dimming Frequency

- Available in a 32-Pin (5mm x 5mm) TQFN with an Exposed Pad for Heat Dissipation and Operates Over the -40°C to +105°C Ambient Temperature Range

Ordering Information appears at end of data sheet.

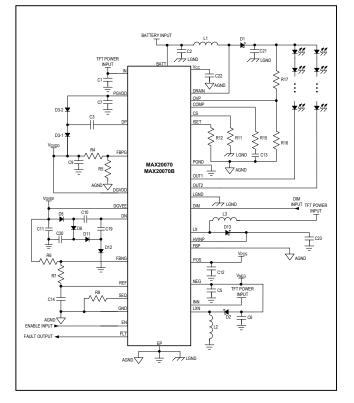

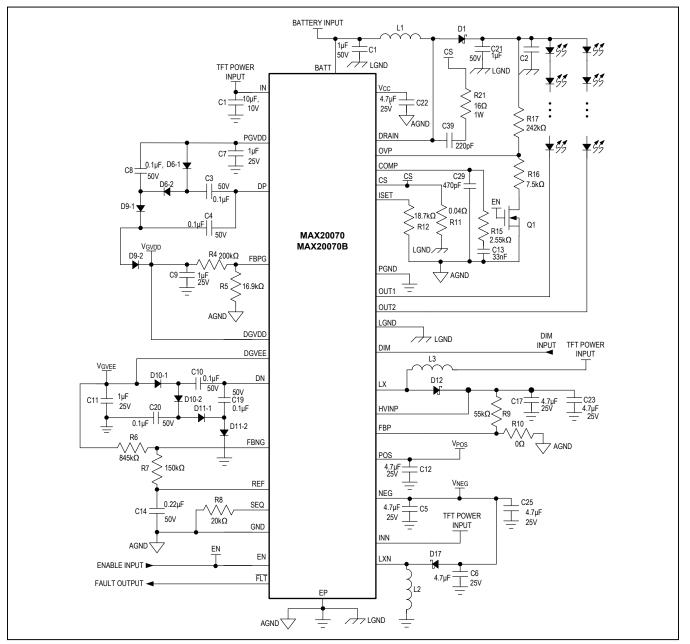

## **Simplified Operating Circuit**

## Integrated TFT Power Supplies and LED Backlight Drivers

#### **Absolute Maximum Ratings**

| BATT to GND0.3V to +52V                                          |

|------------------------------------------------------------------|

| OUT_, DRAIN, OVP to GND0.3V to +52V                              |

| IN, INN, V <sub>CC</sub> , FLT, DIM, CS, EN to GND0.3V to +6V    |

| COMP, ISET to GND0.3V to $(V_{CC} + 0.3V)$                       |

| DRAIN and CS Continuous Current2.4A                              |

| FBPG, FBNG, REF, FBP, SEQ to GND0.3V to (V <sub>IN</sub> + 0.3V) |

| LXP, HVINP to GND0.3V to +22V                                    |

| PGVDD, POS to GND0.3V to V <sub>HVINP</sub> + 0.3V               |

| NEG to GND24V to +0.3V                                           |

| LXN to INN24V to +0.3V                                           |

| DP, DN to PGND0.3V to (V <sub>HVINP</sub> + 0.3V)                |

| DGVDD to GND0.3V to +24V                                         |

| DGVEE to GND                                          | 24V to +0.3V   |

|-------------------------------------------------------|----------------|

| GND to PGND                                           | 0.3V to +0.3V  |

| GND to LGND                                           | 0.3V to +0.3V  |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

| TQFN (derate 34.5mW/°C above +70°C),                  |                |

| Multilayer Board                                      |                |

| Operating Temperature Range                           | 40°C to +105°C |

| Junction Temperature                                  | +150°C         |

| Storage Temperature Range                             | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C         |

| Soldering Temperature (reflow)                        | 260°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### Package Thermal Characteristics (Note 1)

#### TQFN

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

#### **Electrical Characteristics**

(V<sub>IN</sub> = 3.6V, V<sub>BATT</sub> = 12V, Typical operating circuit as <u>Figure 5</u>, = -40°C to +105°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                 | SYMBOL              | CONDITIONS                                                  | MIN   | TYP    | MAX   | UNITS |

|---------------------------|---------------------|-------------------------------------------------------------|-------|--------|-------|-------|

| INPUT SUPPLY              | L                   |                                                             |       |        |       |       |

| IN Voltage Range          |                     |                                                             | 2.7   |        | 5.5   | V     |

| IN UVLO Threshold         |                     | Rising                                                      | 2.45  | 2.55   | 2.65  | V     |

| IN UVLO Hysteresis        |                     |                                                             |       | 100    |       | mV    |

| IN Quiescent Current      |                     | V <sub>EN</sub> = V <sub>GND</sub> , V <sub>IN</sub> = 3.6V |       | 4      | 10    | μA    |

| IN Quiescent Current      |                     | $V_{EN} = V_{IN} = 3.6V$ , no switching                     |       | 2.2    |       | mA    |

| REFERENCE                 | ·                   |                                                             |       |        |       |       |

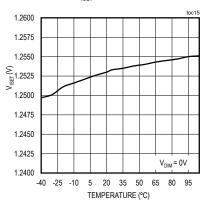

| Reference Output Voltage  |                     | No load                                                     | 1.234 | 1.25   | 1.266 | V     |

| Reference UVLO Threshold  |                     | REF rising                                                  |       | 1      | 1.2   | V     |

| Reference UVLO Hysteresis |                     |                                                             |       | 100    |       | mV    |

| Reference Load Regulation |                     | 0 < I <sub>REF</sub> < 100μA                                |       | 10     | 20    | mV    |

| Reference Line Regulation |                     | 2.7V < V <sub>IN</sub> < 5.5V                               |       | 2      | 5     | mV    |

| BOOST REGULATOR           | ·                   |                                                             |       |        |       |       |

| Output Valtage Denge      | V <sub>HVINP</sub>  |                                                             | VIN   |        | 15    | V     |

| Output Voltage Range      | V <sub>POS</sub>    |                                                             | 5     |        | 15    | v     |

| POS Output Regulation     | S Output Regulation |                                                             | 6.37  | 6.5    | 6.63  | V     |

| Operating Frequency       |                     | Dither disabled                                             | 850   | 1000   | 1150  | kHz   |

| Frequency Dither          |                     |                                                             |       | +0/-12 |       | %     |

# Integrated TFT Power Supplies and LED Backlight Drivers

### **Electrical Characteristics (continued)**

(V<sub>IN</sub> = 3.6V, V<sub>BATT</sub> = 12V, Typical operating circuit as Figure 5, = -40°C to +105°C, unless otherwise noted. Typical values are at  $T_A = +25$ °C.) (Note 2)

| PARAMETER                                              | SYMBOL | CONDITIONS                                                                                                                                                    | MIN   | TYP    | MAX   | UNITS |

|--------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|-------|-------|

| Oscillator Maximum Duty Cycle                          |        |                                                                                                                                                               | 90    | 94     | 98    | %     |

| FBP Regulation Voltage                                 |        |                                                                                                                                                               | 1.236 | 1.25   | 1.264 | V     |

| FBP Load Regulation                                    |        | 1mA < I <sub>POS</sub> < 100mA                                                                                                                                |       | -1     |       | %     |

| FBP Line Regulation                                    |        | V <sub>IN</sub> = 2.7V to 5.5V                                                                                                                                | -0.4  | 0      | +0.4  | %     |

|                                                        |        | V <sub>IN</sub> = 2.7V, V <sub>POS</sub> = 15V                                                                                                                |       | 50     |       |       |

| Maximum Load Current                                   |        | V <sub>IN</sub> = 3V, V <sub>POS</sub> = 15V                                                                                                                  |       | 70     |       | mA    |

| FBP Input Bias Current                                 |        | V <sub>FBP</sub> = 1.25V, T <sub>A</sub> = +25°C                                                                                                              | 50    | 120    | 200   | nA    |

| FBP Internal-Divider Enable<br>Threshold               |        | FBP rising, hysteresis = 10mV                                                                                                                                 |       | 35     | 100   | mV    |

| LXP On-Resistance                                      |        | I <sub>LXP</sub> = 0.1A                                                                                                                                       |       | 0.5    | 1.0   | Ω     |

| LXP Leakage Current                                    |        | EN = GND, $V_{LXP}$ = 15V                                                                                                                                     |       |        | 20    | μA    |

| LXP Current Limit                                      |        | Duty cycle = 80%                                                                                                                                              | 1.0   | 1.2    | 1.4   | А     |

| Soft-Start Period                                      |        | I <sub>LIM</sub> ramp                                                                                                                                         |       | 5      |       | ms    |

| INVERTING REGULATOR                                    | ·      |                                                                                                                                                               |       |        |       | •     |

| INN Voltage Range                                      |        |                                                                                                                                                               | 2.7   |        | 5.5   | V     |

| INN Quiescent Current                                  |        | EN = GND, V <sub>INN</sub> = 3.6V                                                                                                                             |       |        | 1     | μA    |

| INN Quiescent Current                                  |        | V <sub>EN</sub> = V <sub>INN</sub> = 3.6V                                                                                                                     |       | 1      |       | mA    |

| Operating Frequency                                    |        | Dither disabled (test mode only)                                                                                                                              | 850   | 1000   | 1150  | kHz   |

| Frequency Dither                                       |        |                                                                                                                                                               |       | +0/-12 |       | %     |

| Oscillator Maximum Duty Cycle                          |        |                                                                                                                                                               | 90    | 94     | 98    | %     |

|                                                        |        | V <sub>INN</sub> = 2.7V to 5.5V, V <sub>POS</sub> =<br>6.5V, 1mA < I <sub>NEG</sub> < 100mA,<br>I <sub>POS</sub> = no load, T <sub>A</sub> = 0°C to<br>+105°C | -50   |        | +50   |       |

|                                                        |        | $V_{INN} = 2.7V \text{ to } 5.5V, V_{POS} = 6.5V, 1mA < I_{NEG} < 100mA, I_{POS} = no load, T_A = -40^{\circ}C \text{ to} +105^{\circ}C$                      | -60   |        | +60   |       |

| V <sub>POS</sub> + V <sub>NEG</sub> Regulation Voltage |        | $V_{INN} = 2.7V \text{ to } 5.5V, V_{POS} >$<br>6.5V, 1mA < I <sub>NEG</sub> < 100mA,<br>I <sub>POS</sub> = no load, T <sub>A</sub> = 0°C to<br>+105°C        | -80   |        | +80   | mV    |

|                                                        |        | $V_{INN} = 2.7V \text{ to } 5.5V, V_{POS} >$<br>6.5V, 1mA < I <sub>NEG</sub> < 100mA,<br>I <sub>POS</sub> = no load, T <sub>A</sub> = -40°C to<br>+105°C      | -100  |        | +100  |       |

| Maximum Load Current                                   |        | V <sub>IN</sub> = 2.7V, V <sub>NEG</sub> = -15V                                                                                                               |       | 50     |       | mA    |

|                                                        |        | V <sub>IN</sub> = 3V, V <sub>NEG</sub> = -15V                                                                                                                 |       | 70     |       |       |

| LXN On-Resistance                                      |        | INN to LXN, V <sub>LXN</sub> = 0.1A                                                                                                                           |       | 0.6    | 1.2   | Ω     |

# Integrated TFT Power Supplies and LED Backlight Drivers

### **Electrical Characteristics (continued)**

(V<sub>IN</sub> = 3.6V, V<sub>BATT</sub> = 12V, Typical operating circuit as Figure 5, = -40°C to +105°C, unless otherwise noted. Typical values are at  $T_A = +25$ °C.) (Note 2)

| PARAMETER                     | SYMBOL             | CONDITIONS                                                                                    | MIN             | TYP  | MAX                | UNITS |

|-------------------------------|--------------------|-----------------------------------------------------------------------------------------------|-----------------|------|--------------------|-------|

| LXN Leakage Current           |                    | V <sub>IN</sub> = 3.6V, V <sub>LXN</sub> = V <sub>NEG</sub> =<br>-15V, T <sub>A</sub> = +25°C |                 |      | 20                 | μA    |

| LXN Current Limit             |                    | Duty cycle = 80%                                                                              | 1.2             | 1.5  | 1.8                | А     |

| Soft-Start Period             |                    | I <sub>LIM</sub> ramp                                                                         |                 | 5    |                    | ms    |

| POSITIVE CHARGE-PUMP REGUL    | ATOR               |                                                                                               |                 |      |                    |       |

| PGVDD Operating Voltage Range | V <sub>PGVDD</sub> |                                                                                               | 6               |      | V <sub>HVINP</sub> | V     |

| HVINP-DP Current Limit        |                    |                                                                                               | 15              |      |                    | mA    |

| Oscillator Frequency          |                    |                                                                                               | 300             | 400  | 500                | kHz   |

| FBPG Regulation Voltage       |                    |                                                                                               | 1.236           | 1.25 | 1.264              | V     |

| FBPG Line Regulation          |                    | V <sub>HVINP</sub> = 11 to 15V                                                                |                 | 0    | 0.2                | %/V   |

| FBPG Input Bias Current       |                    | V <sub>FBPG</sub> = 1.25V, T <sub>A</sub> = +25°C                                             | -100            |      | +100               | nA    |

| DP On-Resistance High         |                    | I <sub>DP</sub> = 10mA                                                                        |                 | 30   | 60                 | Ω     |

| DP On-Resistance Low          |                    | I <sub>DP</sub> = -10mA                                                                       |                 | 15   | 30                 | Ω     |

| NEGATIVE CHARGE-PUMP REGUI    | ATOR               |                                                                                               |                 |      |                    |       |

| HVINP-DN Current Limit        |                    |                                                                                               | 15              |      |                    | mA    |

| Oscillator Frequency          |                    |                                                                                               | 300             | 400  | 500                | kHz   |

| FBNG Regulation Voltage       |                    |                                                                                               | -12             | 0    | +12                | mV    |

| FBNG Line Regulation          |                    | V <sub>HVINP</sub> = 11V to 15V                                                               |                 | 0    | 0.2                | %/V   |

| FBNG Input Bias Current       |                    | V <sub>FBNG</sub> = 0V, T <sub>A</sub> = +25°C                                                | -100            |      | +100               | nA    |

| DN On-Resistance High         |                    | I <sub>DN</sub> = 10mA                                                                        |                 | 30   | 60                 | Ω     |

| DN On-Resistance Low          |                    | I <sub>DN</sub> = -10mA                                                                       |                 | 15   | 30                 | Ω     |

| SEQUENCE SWITCHES             |                    |                                                                                               |                 |      |                    |       |

| POS Output Range              | V <sub>POS</sub>   | Tracks HVINP                                                                                  | V <sub>IN</sub> |      | 15                 | V     |

|                               |                    | (HVINP-POS), I <sub>POS</sub> = 100mA                                                         |                 | 0.8  | 1.5                | Ω     |

| POS On-Resistance             |                    | (HVINP-POS), I <sub>POS</sub> = 100mA<br>(MAX20070GTJA/V+ and<br>MAX200700BGTJA/V+ only)      |                 | 1.6  | 2.8                | Ω     |

|                               |                    | Expires after soft-start period                                                               | 120             |      |                    | mA    |

| POS Charge Current Limit      |                    | (MAX20070GTJA/V+ and<br>MAX200700BGTJA/V+ only)                                               | 130             |      | 260                | mA    |

| POS Discharge Resistance      |                    |                                                                                               | 2               | 3.4  | 6                  | kΩ    |

| POS Soft-Start Charge Time    |                    | Current mode (0A to full current limit)                                                       |                 | 5    |                    | ms    |

| NEG Output Range              | V <sub>NEG</sub>   |                                                                                               | -15             |      |                    | V     |

| NEG Discharge Resistance      |                    |                                                                                               | 2               | 3.4  | 6                  | kΩ    |

# Integrated TFT Power Supplies and LED Backlight Drivers

### **Electrical Characteristics (continued)**

$(V_{IN} = 3.6V, V_{BATT} = 12V, Typical operating circuit as Figure 5, = -40°C to +105°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 2)$

| PARAMETER                             | SYMBOL | CONDITIONS                                                                                                     | MIN  | TYP  | MAX  | UNITS |

|---------------------------------------|--------|----------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| PGVDD On-Resistance                   |        | (HVINP-PGVDD),<br>I <sub>PGVDD</sub> = 3mA                                                                     |      | 30   | 60   | Ω     |

| PGVDD Current Limit                   |        | Expires when PGVDD charging is completed                                                                       | 15   | 50   |      | mA    |

| DGVDD Input Voltage Range             |        |                                                                                                                | 6    |      | 22   | V     |

| DGVDD Discharge Resistance            |        |                                                                                                                | 7    | 12   | 17   | kΩ    |

| DGVEE Input Voltage Range             |        |                                                                                                                | -22  |      | -6   | V     |

| DGVEE Discharge Resistance            |        |                                                                                                                | 7    | 12   | 17   | kΩ    |

| SEQ Bias Current                      |        | V <sub>SEQ</sub> = 1V                                                                                          | 4.75 | 5    | 5.25 | μA    |

| TFT FAULT PROTECTION                  |        |                                                                                                                |      |      |      |       |

| POS Undervoltage-Fault Threshold      |        | FBP = GND, after POS<br>soft-start, V <sub>POS</sub> falling<br>(MAX20070GTJA/V+ and<br>MAX20070BGTJA/V+ only) | 75   | 80   | 85   | %     |

| HVINP Undervoltage-Fault<br>Threshold |        | Before end of POS soft-<br>start, V <sub>HVINP</sub> falling<br>(MAX20070GTJA/V+ and<br>MAX20070BGTJA/V+ only) | 75   | 80   | 85   | %     |

|                                       |        | V <sub>HVINP</sub> falling                                                                                     | 75   | 80   | 85   | %     |

| NEG Undervoltage-Fault Threshold      |        | V <sub>NEG</sub> rising (% of POS setting)                                                                     | 75   | 80   | 85   | %     |

| FBP Undervoltage-Fault Threshold      |        | V <sub>FBP</sub> falling                                                                                       | 0.95 | 1.00 | 1.05 | V     |

| FBPG Undervoltage-Fault Threshold     |        | V <sub>FBPG</sub> falling                                                                                      | 0.95 | 1.00 | 1.05 | V     |

| FBNG Undervoltage-Fault<br>Threshold  |        | V <sub>FBNG</sub> rising                                                                                       | 200  | 250  | 300  | mV    |

| Undervoltage-Fault Timer              |        |                                                                                                                |      | 50   |      | ms    |

| FBP Short-Circuit Fault Threshold     |        | V <sub>FBP</sub> falling                                                                                       | 30   | 40   | 50   | %     |

| POS Short-Circuit Fault Threshold     |        | POS falling (% of V <sub>HVINP</sub> )<br>(MAX20070GTJA/V+ and<br>MAX20070BGTJA/V+ only)                       | 70   | 73   | 76   | %     |

| NEG Short-Circuit Fault Threshold     |        | V <sub>NEG</sub> rising                                                                                        | 30   | 40   | 50   | %     |

| Short-Circuit Fault Timer             |        |                                                                                                                |      | 10   |      | μs    |

# Integrated TFT Power Supplies and LED Backlight Drivers

## **Electrical Characteristics (continued)**

$(V_{IN} = 3.6V, V_{BATT} = 12V, Typical operating circuit as Figure 5, = -40°C to +105°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 2)$

| PARAMETER                                 | SYMBOL               | CONDITIONS                                                                                  | MIN  | TYP    | MAX  | UNITS |

|-------------------------------------------|----------------------|---------------------------------------------------------------------------------------------|------|--------|------|-------|

| BATT INPUT                                |                      |                                                                                             |      |        |      |       |

|                                           |                      | (Note 3)                                                                                    | 4.75 |        | 40   |       |

| Input Voltage Range                       | V <sub>BATT</sub>    | V <sub>BATT</sub> = V <sub>CC</sub>                                                         | 4.5  |        | 5.5  | V     |

| Quiescent Supply Current                  | Ι <sub>Q</sub>       | V <sub>DIM</sub> = 5V, V <sub>OVP</sub> = 1.3V;<br>OUT1, OUT2 open                          |      | 2.6    | 5.2  | mA    |

| Standby Supply Current                    | I <sub>SH</sub>      | EN = GND                                                                                    |      | 15     | 30   | μA    |

| Undervoltage Lockout                      | UVLO <sub>BATT</sub> | V <sub>BATT</sub> rising                                                                    | 4.0  | 4.2    | 4.4  | V     |

| Undervoltage-Lockout Hysteresis           |                      |                                                                                             |      | 170    |      | mV    |

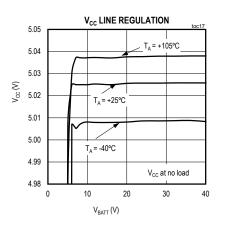

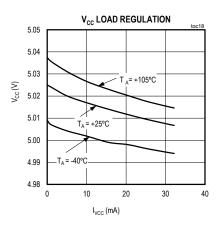

| V <sub>CC</sub> REGULATOR                 |                      |                                                                                             |      |        |      |       |

| Output Voltage                            |                      | 5.75V < V <sub>BATT</sub> < 40V; I <sub>LOAD</sub> =<br>0 to 30mA; C <sub>VCC</sub> = 2.2µF | 4.75 | 5      | 5.25 | V     |

| Dropout Voltage                           |                      | V <sub>BATT</sub> = 4.75V, I <sub>VCC</sub> = 30mA                                          |      | 0.25   | 0.5  | V     |

| V <sub>CC</sub> Undervoltage Lockout      | UVLOVCC              | V <sub>CC</sub> rising                                                                      | 3.8  | 4      | 4.2  | V     |

| V <sub>CC</sub> UVLO Hysteresis           |                      |                                                                                             |      | 150    |      | mV    |

| Short-Circuit Current Limit               |                      | V <sub>CC</sub> shorted to GND                                                              |      | 80     |      | mA    |

| BOOST/SEPIC CONTROLLER                    |                      |                                                                                             |      |        |      |       |

| Switching Frequency (MAX20070)            |                      | Dither disabled                                                                             | 900  | 1000   | 1100 | kHz   |

| Maximum Duty Cycle (MAX20070)             | D <sub>MAX</sub>     |                                                                                             | 88   | 92     | 96   | %     |

| Switching Frequency (MAX20070B)           |                      | Dither disabled                                                                             | 1800 | 2000   | 2200 | kHz   |

| Maximum Duty Cycle (MAX20070B)            |                      |                                                                                             | 90   | 94     | 98   | %     |

| Frequency Dither                          |                      |                                                                                             |      | +0/-12 |      | %     |

| SLOPE COMPENSATION                        |                      |                                                                                             |      |        |      | •     |

| Slope-Compensation Peak Voltage per Cycle |                      | Voltage ramp added to CS                                                                    |      | 0.23   |      | V     |

| CS LIMIT COMPARATOR                       |                      |                                                                                             |      |        |      |       |

| CS Threshold Voltage                      | V <sub>CS_MAX</sub>  |                                                                                             | 250  | 270    | 290  | mV    |

| CS Input Current                          |                      | 0 < V <sub>CS</sub> < 0.35 (drain switch on)                                                | -1.3 |        | +0.5 | μA    |

| ERROR AMPLIFIER                           |                      |                                                                                             |      |        |      |       |

| OUT_ Regulation Voltage                   |                      | V <sub>DIM</sub> = 5V                                                                       |      | 0.75   |      | V     |

| Transconductance                          | Ям                   |                                                                                             | 340  | 600    | 880  | μS    |

| COMP Sink Current                         |                      | V <sub>OUT</sub> _ = 2.25V, V <sub>COMP</sub> = 2V                                          | 160  | 400    | 900  | μA    |

| COMP Source Current                       |                      | <br>V <sub>OUT</sub> = 0V, V <sub>COMP</sub> = 1V                                           | 160  | 400    | 900  | μA    |

# Integrated TFT Power Supplies and LED Backlight Drivers

### **Electrical Characteristics (continued)**

(V<sub>IN</sub> = 3.6V, V<sub>BATT</sub> = 12V, Typical operating circuit as Figure 5, = -40°C to +105°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C.) (Note 2)

| PARAMETER                            | SYMBOL | CONDITIONS                                                                                                              | MIN   | TYP  | MAX   | UNITS |

|--------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| POWER MOSFET                         |        |                                                                                                                         |       |      |       |       |

| Power Switch On-Resistance           |        |                                                                                                                         |       | 0.15 | 0.35  | Ω     |

| Switch Leakage Current               |        | V <sub>BATT</sub> = V <sub>DRAIN</sub> = 40V,<br>V <sub>DIM</sub> = 0V                                                  |       |      | 10    | μA    |

| LED CURRENT SINK                     |        |                                                                                                                         |       |      |       |       |

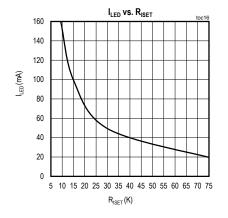

| ISET Resistance Range                |        |                                                                                                                         | 9.37  |      | 75    | kΩ    |

|                                      |        | R <sub>ISET</sub> = 9.37kΩ                                                                                              | 153   | 160  | 167   | mA    |

| Full Soolo OLIT Output Current       |        | $R_{ISET} = 15k\Omega$                                                                                                  | 95    | 100  | 105   | mA    |

| Full-Scale OUT_ Output Current       |        | R <sub>ISET</sub> = 30kΩ                                                                                                | 47.5  | 50   | 52.5  | mA    |

|                                      |        | $R_{ISET} = 75k\Omega$                                                                                                  |       | 20   |       | mA    |

| ISET Output Voltage                  |        |                                                                                                                         | 1.225 | 1.25 | 1.275 | V     |

|                                      |        | I <sub>OUT</sub> _ = 160mA                                                                                              | -1.5  |      | +1.5  | %     |

| Current Regulation Between Strings   |        | I <sub>OUT</sub> = 100mA                                                                                                | -2    |      | +2    | %     |

|                                      |        | <br>I <sub>OUT</sub> _= 50mA                                                                                            | -2.5  |      | +2.5  | %     |

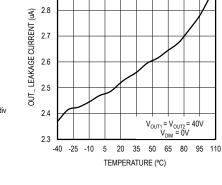

| OUT_ Leakage Current                 |        | V <sub>BATT</sub> = 12V , V <sub>OUT1</sub> = V <sub>OUT2</sub><br>= 40V, V <sub>DIM</sub> = 0V, T <sub>A</sub> = +25°C |       | 2.5  |       | μA    |

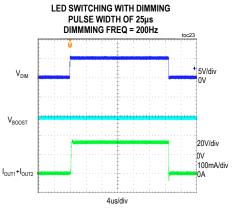

| DIM to Led Turn-On Delay             |        | DIM rising edge to 10% rise                                                                                             |       | 150  |       | ns    |

| DIM to Led Turn-Off Delay            |        | DIM falling edge to 10% fall                                                                                            |       | 50   |       | ns    |

| I <sub>OUT_</sub> Rise Time          |        | 10% to 90% I <sub>OUT</sub> _                                                                                           |       | 200  |       | ns    |

| I <sub>OUT_</sub> Fall Time          |        | 90% to 10% I <sub>OUT_</sub>                                                                                            |       | 50   |       | ns    |

| LOGIC INPUTS AND OUTPUTS             |        |                                                                                                                         |       |      |       |       |

| DIM Input High Level                 |        |                                                                                                                         | 2.1   |      |       | V     |

| DIM Input Low Level                  |        |                                                                                                                         |       |      | 0.8   | V     |

| DIM Hysteresis                       |        |                                                                                                                         |       | 350  |       | mV    |

| DIM On-Time to Enter LODIM Mode      |        |                                                                                                                         |       | 25   |       | μs    |

| DIM Low Delay to Enter LODIM<br>Mode |        | DIM = 0                                                                                                                 |       | 40   |       | ms    |

| DIM Pullup Current                   |        |                                                                                                                         |       | 5    |       | μA    |

| EN Input Logic High                  |        |                                                                                                                         | 2.1   |      |       | V     |

| EN Input Logic Low                   |        |                                                                                                                         |       |      | 0.8   | V     |

| EN Hysteresis                        |        |                                                                                                                         |       | 125  |       | mV    |

| EN Input Current                     |        |                                                                                                                         | -1    |      | +1    | μA    |

| EN Blanking Time                     |        | V <sub>IN</sub> = 3.6V                                                                                                  |       | 7    |       | μs    |

## Integrated TFT Power Supplies and LED Backlight Drivers

### **Electrical Characteristics (continued)**

$(V_{IN} = 3.6V, V_{BATT} = 12V, Typical operating circuit as Figure 5, = -40°C to +105°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 2)$

| PARAMETER                                            | SYMBOL | CONDITIONS                                                                     | MIN   | ТҮР  | MAX  | UNITS |

|------------------------------------------------------|--------|--------------------------------------------------------------------------------|-------|------|------|-------|

| FLT Output Low Voltage                               |        | I <sub>SINK</sub> = 5mA                                                        |       |      | 0.4  | V     |

| FLT Output Leakage current                           |        | V <sub>FLT</sub> = 5.5V                                                        | -1    |      | +1   | μA    |

| FLT Frequency for Fault Detection                    |        |                                                                                | 0.88  | 1    | 1.12 | kHz   |

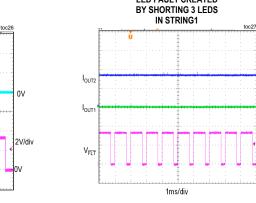

| FLT Pin Duty Cycle on LED String Fault               |        |                                                                                |       | 25   |      | %     |

| FLT Pin Duty Cycle on TFT Rail Fault                 |        | Fault on at least one of POS,<br>NEG, V <sub>GVDD</sub> , or V <sub>GVEE</sub> |       | 50   |      | %     |

| FLT Pin Duty Cycle on LED String and TFT Rail Fault  |        | Fault on at least one of POS, NEG, $V_{GVDD}$ , or $V_{GVEE}$ , and LED driver | 75    |      |      | %     |

| FLT Switching Frequency on<br>Thermal-Shutdown Event |        | FLT is forced low                                                              |       | 0    |      | Hz    |

| <b>OVERVOLTAGE PROTECTION (OV</b>                    | P)     |                                                                                |       |      |      |       |

| Overvoltage Trip Threshold                           |        | V <sub>OVP</sub> rising                                                        | 1.20  | 1.25 | 1.30 | V     |

| Overvoltage Hysteresis                               |        |                                                                                |       | 70   |      | mV    |

| OVP Input Bias Current                               |        | 0 < V <sub>OVP</sub> < 1.3V                                                    | -500  |      | +500 | nA    |

| THERMAL SHUTDOWN                                     |        |                                                                                |       |      |      |       |

| Thermal-Shutdown Threshold                           |        |                                                                                |       | 160  |      | °C    |

| Thermal-Shutdown Hysteresis                          |        |                                                                                |       | 15   |      | °C    |

| LED FAULT DETECTION                                  |        |                                                                                |       |      |      |       |

| LED-Shorted Fault-Indicator<br>Threshold             |        | Other string in regulation                                                     | 3.1   |      | 5.5  | V     |

| LED String Shorted-Shutoff<br>Threshold              |        | Other string in regulation                                                     | 6 9.5 |      | 9.5  | V     |

| Shorted LED-Detection Delay                          |        |                                                                                |       | 6    |      | μs    |

Note 2: 100% tested at T<sub>A</sub> = +25°C. All limits over temperature are guaranteed by design, not production tested.

Note 3: The MAX20070/MAX20070B are designed for use in applications with continuous 14V operation, and meet the *Electrical Characteristics* table up to the maximum supply voltage.

## Integrated TFT Power Supplies and LED Backlight Drivers

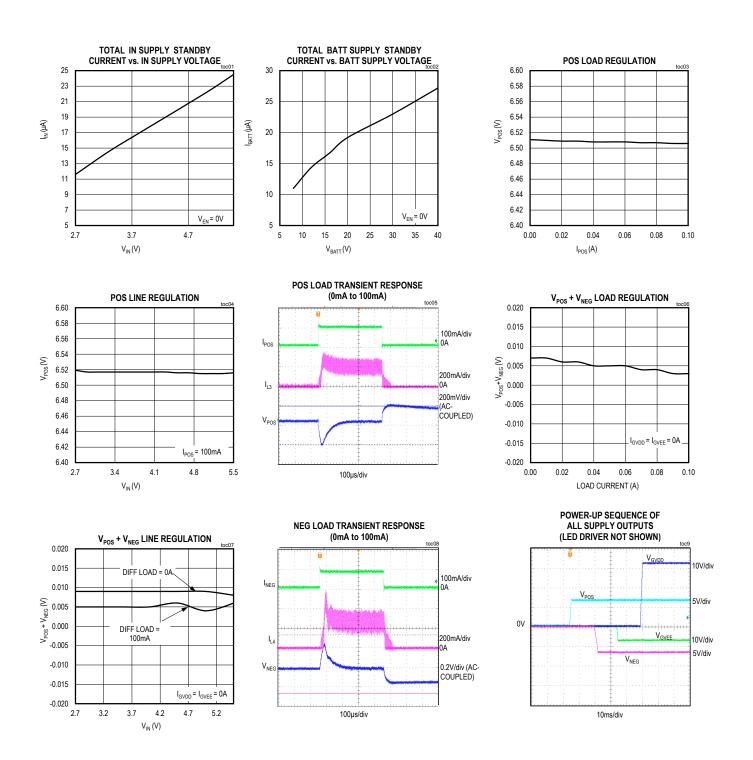

## **Typical Operating Characteristics**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

## Integrated TFT Power Supplies and LED Backlight Drivers

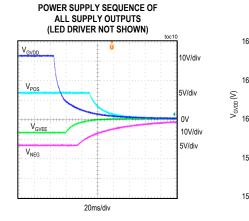

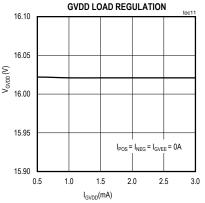

## **Typical Operating Characteristics (continued)**

(T<sub>A</sub> = +25°C, unless otherwise noted.)

EFFICIENCY WITH DIFF LOAD FROM  $V_{POS}$  TO  $V_{NEG}$

## Integrated TFT Power Supplies and LED Backlight Drivers

V<sub>BAT</sub>

0V

V<sub>DI</sub>

2.9

## **Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C, unless otherwise noted.)$

TFT FAULT

POS SHORTED TO GROUND

1ms/div

V<sub>POS</sub>

V<sub>FL1</sub>

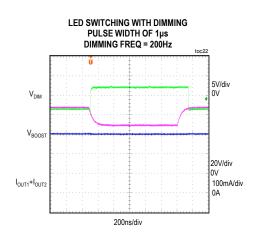

WITH DIM DUTY = 25% (DIM FREQ = 200Hz) toc21 100mA/div I<sub>OUT1</sub>+I<sub>OU</sub> 10A 10V/div VoL 0٧ 5V/div

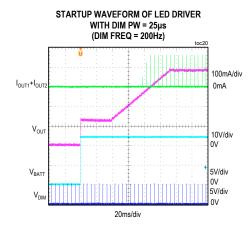

STARTUP WAVEFORM OF LED DRIVER

OUT\_ LEAKAGE CURRENT

vs. TEMPERATURE

5V/div

50mA/div

0A/0A

2V/div

0V

# Integrated TFT Power Supplies and LED Backlight Drivers

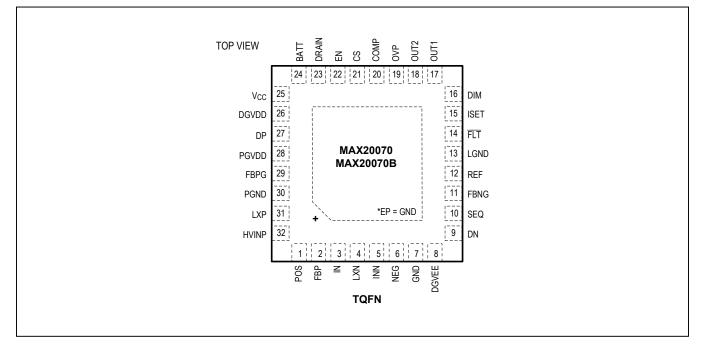

## **Pin Configuration**

### **Pin Description**

| PIN | NAME  | FUNCTION                                                                                                                                                                       |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | POS   | Positive Source-Driver Output Voltage                                                                                                                                          |

| 2   | FBP   | Feedback Input for HVINP. Connect a resistor from this pin to ground to set the HVINP voltage.                                                                                 |

| 3   | IN    | Supply Input. Connect a 1µF ceramic capacitor from this pin to ground for proper operation.                                                                                    |

| 4   | LXN   | DC-DC Inverting Converter Inductor/Diode Connection                                                                                                                            |

| 5   | INN   | Buck-Boost Converter Input. Connect a 1µF ceramic capacitor from this pin to ground for proper operation.                                                                      |

| 6   | NEG   | Negative Source-Driver Output Voltage                                                                                                                                          |

| 7   | GND   | Ground Connection                                                                                                                                                              |

| 8   | DGVEE | Connects directly to $V_{GVEE}$ charge-pump output such that during $V_{GVEE}$ discharge, $V_{GVEE}$ is discharged through an internal switch connected between DGVEE and GND. |

| 9   | DN    | Regulated Charge-Pump Driver for V <sub>GVEE</sub> . Connect to flying capacitor.                                                                                              |

| 10  | SEQ   | Sequencing Programming Pin. Connect appropriate resistor to ground to program desired sequencing.                                                                              |

| 11  | FBNG  | Feedback Input for V <sub>GVEE</sub>                                                                                                                                           |

| 12  | REF   | 1.25V Reference Output                                                                                                                                                         |

| 13  | LGND  | Power-Ground Connection for LED Driver                                                                                                                                         |

| 14  | FLT   | Active-Low Fault-Indicating Output                                                                                                                                             |

| 15  | ISET  | Full-Scale LED Current-Adjustment Pin. The resistance from ISET to GND controls the current in each LED string.                                                                |

| 16  | DIM   | PWM Dimming Input                                                                                                                                                              |

| 17  | OUT1  | LED String 1 Cathode Connection. Connect to ground if not used.                                                                                                                |

## Integrated TFT Power Supplies and LED Backlight Drivers

#### PIN NAME FUNCTION 18 OUT2 LED String 2 Cathode Connection. Connect to ground if not used. OVP 19 LED Driver Output-Voltage-Sensing Input. This voltage is used for overvoltage protection. LED Driver Switching-Converter Compensation Input. Connect an RC network from COMP to GND for 20 COMP compensation. LED Driver Switching-MOSFET Source Connection. Connect a sense resistor from CS to PGND to set the 21 CS switching MOSFET current limit. 22 EN Enable Input 23 DRAIN Internal LED Driver Switching-MOSFET Drain LED Driver Supply Input Connected to a 4.75V to 40V Supply. Bypass BATT to ground with a ceramic BATT 24 capacitor. 5V Regulator Output. Place a $1\mu$ F ceramic capacitor as close as possible to V<sub>CC</sub> and GND. 25 V<sub>CC</sub> Connects directly to $V_{GVDD}$ charge-pump output, such that during $V_{GVDD}$ discharge, $V_{GVDD}$ is discharged 26 DGVDD through an internal switch connected between DGVDD and GND. DP 27 Regulated Charge-Pump Driver for $V_{GVDD}$ . Connect to flying capacitor. Slowly switches out the HVINP voltage to the positive charge pump to provide soft-start control of the V<sub>GVDD</sub> 28 PGVDD output. 29 FBPG Feedback Input for V<sub>GVDD</sub>. Connect a resistor from this pin to ground to set the V<sub>GVDD</sub> voltage. PGND 30 **Power-Ground Connection** Boost HVINP Converter Internal-Drain MOSFET Connection. Connect to external inductor and boost diode LXP 31 anode. 32 **HVINP** Input Power for the POS Voltage Rail Exposed Pad. Connect to a large contiguous copper-ground plane for optimal heat dissipation. Do not use EP FP \_\_\_\_ as the only electrical ground connection.

### **Pin Description (continued)**

## Integrated TFT Power Supplies and LED Backlight Drivers

## **Typical Operating Circuits**

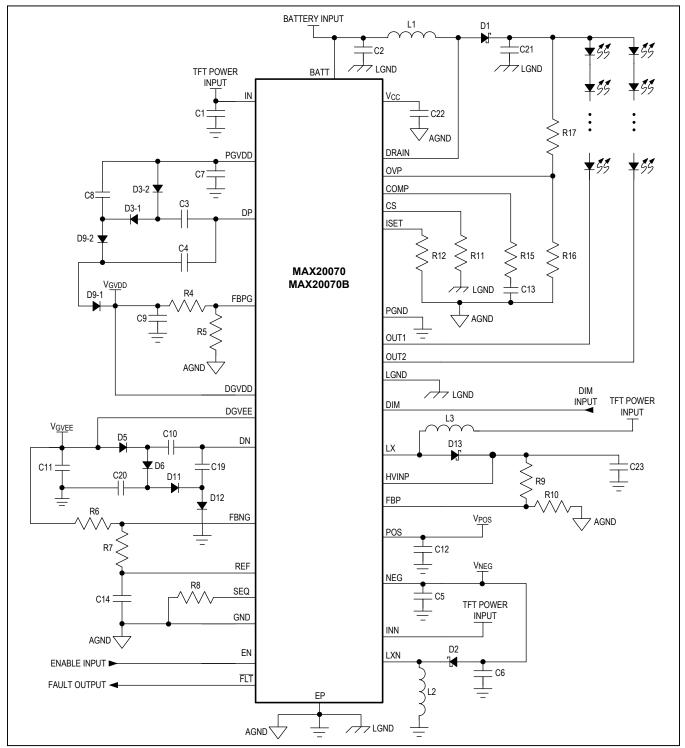

Figure 1. Simplified Operating Circuit for Boost LED Driver

## Integrated TFT Power Supplies and LED Backlight Drivers

## **Typical Operating Circuits (continued)**

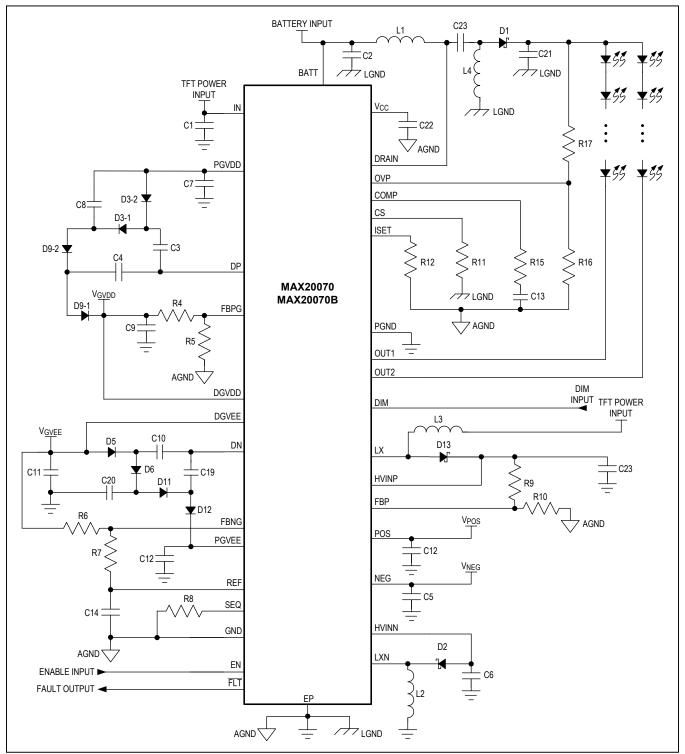

Figure 2. Simplified Operating Circuit for SEPIC LED Driver

## Integrated TFT Power Supplies and LED Backlight Drivers

## **Typical Operating Circuits (continued)**

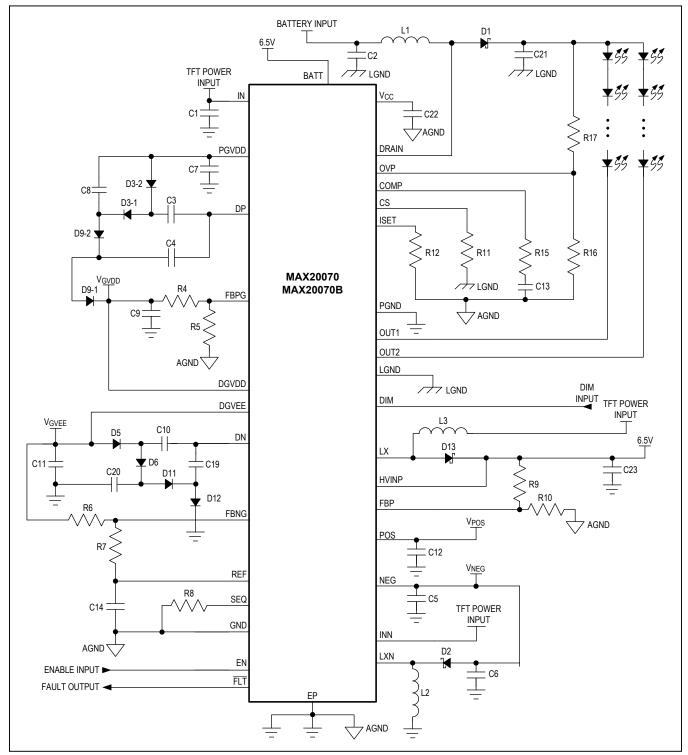

Figure 3. Simplified Operating Circuit for Coldcrank Below 4.5V

## Integrated TFT Power Supplies and LED Backlight Drivers

## **Typical Operating Circuits (continued)**

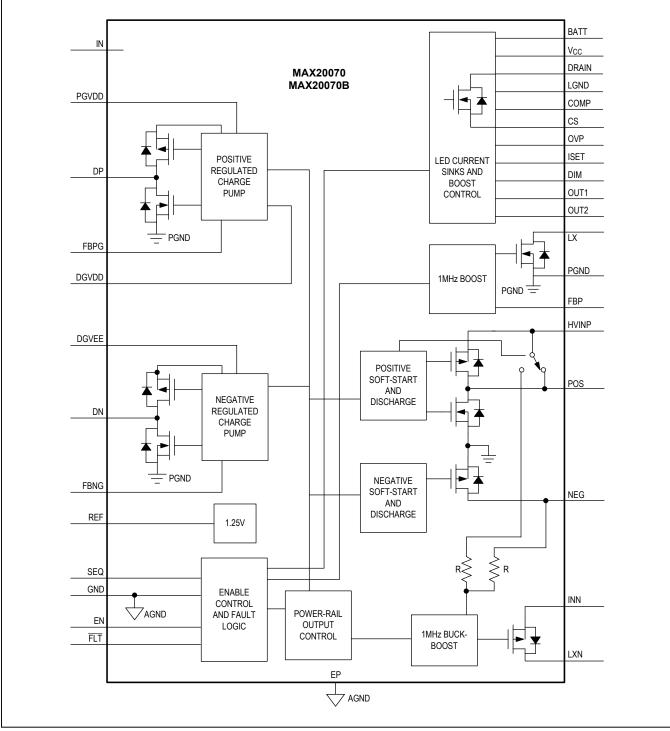

Figure 4. Functional Block Diagram

## Integrated TFT Power Supplies and LED Backlight Drivers

#### **Typical Operating Circuit Schematic**

The MAX20070/MAX20070B's typical operating circuit schematic shown in Figure 5 generates  $\pm 6.5V$  source-driver supplies at 100mA each and also generates  $\pm 16V$  and -7V for gate-driver supplies. The current rating for the gate-driver supplies is 3mA (max) on each output. The input voltage for the TFT power section is 2.7V to 5.5V. The LED driver is a boost LED driver that operates from a 4.75V to 18V input and can withstand a 40V load dump. The LED current per string is set at 160mA and can power two strings with a 34V (max) output voltage. Table 1 lists recommended critical components and Table 2 lists contact information for the component suppliers.

Figure 5. Typical Operating Circuit Schematic

## Integrated TFT Power Supplies and LED Backlight Drivers

#### DESIGNATION QTY DESCRIPTION 33µF, 50V hybrid conductive-C2 1 polymer capacitor SUNCON 50HVH33M 3A, 60V Schottky diode (SMB) D1 1 Diodes Inc. B360B 30V, 200mA dual in-series D6, D9–D11 4 Schottky diodes (SOT323) Central Semi CBAT54SW 30V, 0.5A Schottky diodes 2 D12, D17 (SOD323) Diodes Inc. B0530WS 4.7µH inductor L1 1 Coilcraft MSS1048-472 10µH inductors L2, L3 2 Coilcraft LPS4018-103 60V, 115mA n-channel MOSFET 1 Q1 2N7002

#### Table 1. Component List

**Note:** Other capacitors are surface-mount ceramic capacitors of X7R dielectric.

#### **Detailed Description**

The MAX20070/MAX20070B are highly integrated power supplies and LED backlight drivers for automotive TFT-LCD applications. The devices integrate one buck-boost converter, one boost converter, two gate-driver supplies, and a boost/SEPIC converter that power a two-string LED driver.

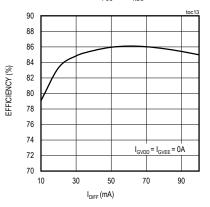

The main power-supply section, consisting of the buckboost converter, boost converter, and gate-driver supplies, operates from an available 2.7V to 5.5V supply. The boost/ SEPIC converter that powers the LED drivers operates from a separate 4.75V and 40V supply voltage, making the devices ideal for automotive TFT-LCD applications. Both the buck-boost and boost converter and the LED driver have built-in spread spectrum for reducing EMI.

The boost converter provides an output voltage adjustable up to 15V (max), with a 100mA (max) output current. The buck-boost converter provides a negative output voltage that tracks the positive voltage from the boost converter.

#### Table 2. Component Suppliers

| SUPPLIER                        | WEBSITE                |

|---------------------------------|------------------------|

| Central Semiconductor           | www.centralsemi.com    |

| Coilcraft, Inc.                 | www.coilcraft.com      |

| Diodes Inc.                     | www.diodes.com         |

| Murata Americas                 | www.murataamericas.com |

| TDK Corp.                       | www.component.tdk.com  |

| SUN Electronic Industries Corp. | www.sunelec.co.jp      |

There are two switching-frequency options (400kHz and 1MHz) for the boost and buck-boost converter. Both boost and buck-boost converters share a common clock. The buck-boost converter uses an internal p-channel MOSFET as the switching element, with a 100mA (max) output current. The boost converter uses an internal n-channel switching MOSFET as the switching element. With an appropriate resistor (140k $\Omega$  or 180k $\Omega$ ) on the SEQ pin, the buck-boost converter can turn off completely.

The switching frequency for the LED boost/SEPIC converter is fixed at an internal clock frequency. There are three frequency options available: 400kHz, 1MHz, and 2MHz. The LED boost/SEPIC converter also has built-in spread spectrum for reduced EMI.

The LED-string channel current is adjustable from 20mA to 160mA using an external resistor. The external resistor sets all the channel currents to the same value. The devices facilitate connecting multiple strings in parallel to increase the current capability of the current sinks and also features pulsed dimming control with a minimum pulse width as low as 0.5µs through a logic-control input (DIM).

The devices provide gate-driver supplies using positive and negative charge-pump regulators, with a maximum current capability of 3mA each. Output voltage is adjustable with a maximum output of +22V on the positive charge pump and -22V on the negative charge pump.

The startup and shutdown sequences for all power domains, controlled by using one of the seven preset modes, is selectable through a resistor on the SEQ pin.

The MAX20070/MAX20070B are available in a 32-pin (5mm x 5mm) TQFN package with an exposed pad and operate over the  $-40^{\circ}$ C to  $+105^{\circ}$ C ambient temperature range.

#### Features

Additional features of the MAX20070/MAX20070B include:

- 2.7V to 5.5V input for TFT power

- 4.75V to 40V input for backlight LED driver

- Integrated 1MHz/400kHz boost and buck-boost converters for TFT power

- Integrated boost/SEPIC converter with two x 160mA LED drivers

- Adaptive voltage optimization on LED driver to reduce power dissipation in the LED current sinks

- Spread spectrum on LED driver and TFT for reduced EMI

- EN input to shut down all the converters and place part in low-quiescent-current standby mode

- Positive and negative 3mA gate-voltage regulators with adjustable output voltage

- Resistor-programmable flexible sequencing through SEQ pin

#### **TFT Power Section**

#### **Source-Driver Power Supplies**

The source-driver power supplies consist of a boost converter and an inverting buck-boost converter that generate +15V (max) and -15V (max), respectively, and can deliver

Integrated TFT Power Supplies and LED Backlight Drivers

up to +100mA on the positive regulator and -100mA on the negative regulator. The positive source-driver power supply's regulation voltage (VPOS) can be set by a resistor-divider on FBP, as shown in Figure 6, or provide 6.5V if the FBP pin is connected to ground at power-up. The positive source driver uses constant-frequency peakcurrent-mode control with internal fixed-slope compensation. Internal compensation stabilizes the control loop. When FBP is connected to ground, the POS regulation voltage is sensed in an internal resistor-divider from POS to ground inside the device. This determination occurs at power-up. If the resistance to ground is not zero at powerup, the device senses the FBP pin voltage and regulates this voltage to 1.25V. The negative source-driver supply voltage (V<sub>NEG</sub>) is automatically tightly regulated to -V<sub>POS</sub> within ±50mV. V<sub>NFG</sub> cannot be adjusted independently of VPOS. The negative source driver is a buck-boost DC-DC converter that uses peak current-mode control with internal fixed-slope compensation to regulate the output voltage. There is an internal resistor-divider from POS to NEG. The center point of this divider is regulated to 0V by the control loop for the negative source driver. The negative source driver can be turned off completely by setting the resistor between SEQ and ground to  $140k\Omega$  or  $180k\Omega$ .

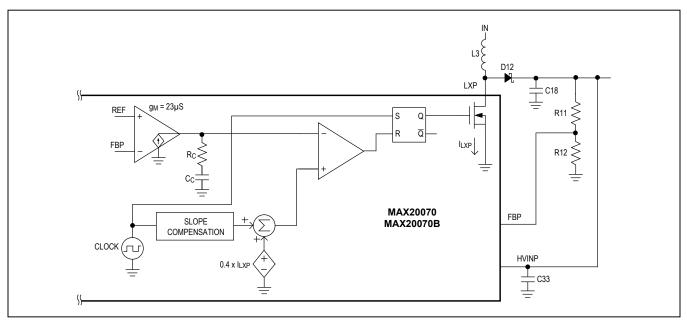

A simplified block diagram of the TFT boost converter is shown in Figure 6. There is an internal error amplifier with a  $g_M = 23\mu$ S that has FBP and REF = 1.25V as inputs.

Figure 6. TFT Boost Converter Simplified Block Diagram

There is an internal compensation network at the output of the error amplifier. Different values of the compensation network switch in and out depending on the connection to the FBP pin. If FBP is grounded, the circuit regulates the output voltage to 6.5V and the POS voltage is sensed by an internal resistor-divider (not shown). When FBP is not shorted to ground and is connected to the junction of the resistor-divider (R9 and R10), external feedback is used to control the POS voltage.

$C_C$  = 140pF,  $R_C$  = 490k $\Omega$  (when external feedback is used)

$C_C = 180 \text{pF}, R_C = 280 \text{k}\Omega$  (when internal feedback is used)

For the current loop, there is internal current sensing using a transresistance of  $R_T = 0.4$ V/A. The V<sub>CS</sub> (I\_inductor x  $R_T$ ) sensing voltage is added to the slope compensation. The slope-compensation signal has a slope of 590mV per microsecond.

The resulting  $V_{SUM} = V_{CS} + V_{SLOPE}$  is compared to the  $V_{COMP}$  (output of the error amplifier) at the input of the PWM comparator to regulate the LXP duty cycle.

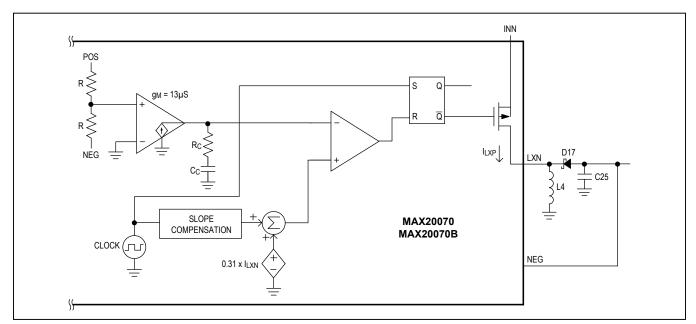

#### **Control-Loop Operation of the TFT Inverter Circuit**

A simplified block diagram of the TFT inverter circuit is shown in <u>Figure 7</u>. There is an internal error amplifier with a  $g_M = 13\mu$ S that has  $V_{REF} = 0V$  and the midpoint of an

## Integrated TFT Power Supplies and LED Backlight Drivers

internal resistor-divider (R-R), connected from POS to NEG, as inputs. At the output of the error amplifier, there is an internal compensation network:

#### $C_{C}$ = 140pF, $R_{C}$ = 360k $\Omega$

For the current loop, there is internal current sensing using a transresistance of  $R_T = 0.31V/A$ .

The V<sub>CS</sub> (I\_inductor x R<sub>T</sub>) sensing voltage is added to the slope compensation. The slope-compensation signal has a slope of 590mV per microsecond. The resulting V<sub>SUM</sub> = V<sub>CS</sub> + V<sub>SLOPE</sub> is compared to the V<sub>COMP</sub> (output of the error amplifier) at the input of the PWM comparator to regulate the LXN duty cycle.

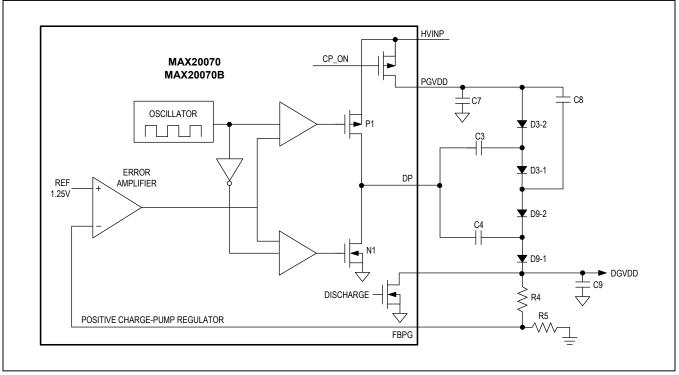

#### **Gate-Driver Power Supplies**

The positive gate-driver power supply (V<sub>GVDD</sub>) generates +22V (max) and the negative gate-driver power supply (V<sub>GVEE</sub>) generates -22V (max). Both supplies can supply up to 3mA current. The V<sub>GVDD</sub> and V<sub>GVEE</sub> regulation voltages are both set using the external resistor networks shown in <u>Figure 2</u>. Both charge-pump regulators use a 400kHz switching frequency. The charge pumps regulate the output voltage by controlling the current that flows into the flying capacitors.

Figure 7. TFT Inverter Circuit Simplified Block Diagram

#### **Operation of the Positive Charge Pump**

The positive charge-pump regulator is typically used to generate the positive supply rail for the TFT-LCD gatedriver ICs.

The output voltage is set with an external resistive voltagedivider from its output to GND, with the midpoint connected to FBPG. The number of charge-pump stages and the setting of the feedback-divider determine the output voltage of the positive charge-pump regulator. The charge pump includes a high-side p-channel MOSFET (P1) and a lowside n-channel MOSFET (N1) to control the power transfer (see Figure 8). The error amplifier compares the feedback signal (FBPG) with a 1.25V internal reference. If the feedback signal is below the reference, the charge-pump regulator turns on P1 and turns off N1 when the rising edge of the oscillator clock arrives, level shifting C3 and C4 by VPGVDD volts. If the voltage across C9 plus a diode drop (V<sub>DGVDD</sub> + V<sub>DIODE</sub>) is smaller than the level-shifted flyingcapacitor voltage (V<sub>C4</sub> + V<sub>PGVDD</sub>), charge flows from C4 to C9 until diode D9-1 turns off. Similarly, if the voltage at the D3-1 cathode plus a diode drop (VPGVDD - VC8 + V<sub>DIODF</sub>) is smaller than the level-shifted flying-capacitor voltage (V<sub>C3</sub> + V<sub>PGVDD</sub>), charge flows from C3 to C8 until diode D3-1 turns off. The falling edge of the oscillator clock

## Integrated TFT Power Supplies and LED Backlight Drivers

turns off P1 and turns on N1, allowing V<sub>PGVDD</sub> to charge up the flying capacitor C3 through D3-2 and C8 to charge C4 through diode D9-2. If the feedback signal is above the reference when the rising edge of the oscillator arrives, the regulator ignores this clock edge and keeps N1 on and P1 off. The charge-pump regulator also includes a discharge switch from DGVDD to ground, turned off to discharge the output capacitors during the sequential turn-off of the output voltage, as programmed by the resistor on the SEQ pin (R<sub>SEQ</sub>). The node PGVDD is internally connected through a switch to the HVINP voltage. See <u>Table 3</u> for the sequencing options.

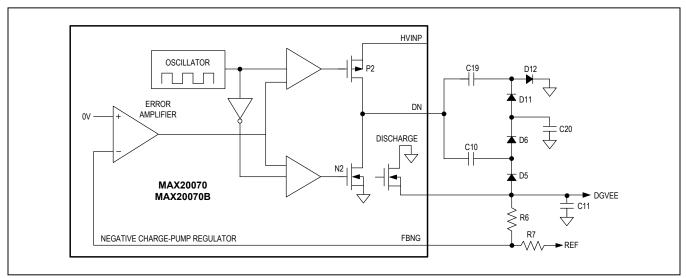

#### **Operation of the Negative Charge Pump**

The negative charge-pump regulator is typically used to generate the negative supply rail for the TFT-LCD gatedriver ICs. The output voltage is set with an external resistive voltage-divider from its output to REF, with the midpoint connected to FBNG. The number of charge-pump stages and the setting of the feedback-divider determine the output of the negative charge-pump regulator. The charge-pump controller includes a high-side p-channel MOSFET (P2) and a low-side n-channel MOSFET (N2) to control the power transfer (see Figure 9).

Figure 8. Positive Charge-Pump Block Diagram

## Integrated TFT Power Supplies and LED Backlight Drivers

Figure 9. Negative Charge-Pump Block Diagram

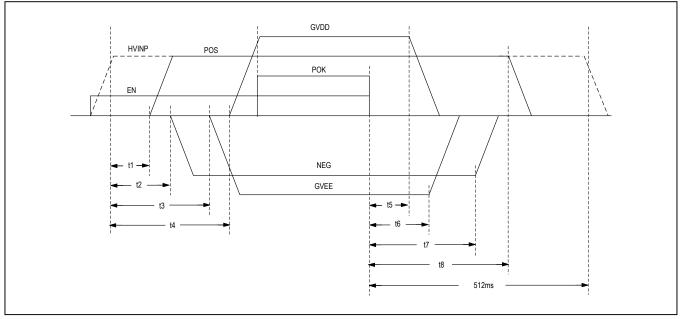

Figure 10. Sequencing Diagram

The error amplifier compares the feedback signal (FBNG) with a 0V internal reference. If the feedback signal is above the reference, the charge-pump regulator turns N2 on and P2 off when the rising edge of the oscillator clock arrives, level shifting C10 and C19. The falling edge of the oscillator clock turns N2 off and P2 on, allowing HVINP to charge up flying-capacitor C10 and C19. If the feedback signal is below the reference voltage of 0V when the rising edge of the oscillator arrives, the regulator ignores this clock edge and keeps P2 on and N2 off. In the Figure 9 diagram,

the negative charge pump uses a doubler configuration; however, in cases where the absolute value of the negative charge-pump voltage is low enough, eliminate diodes D11 and D12. In that case, C19 and C20 are not needed and the cathode of D6 can be connnected to ground. For sequencing of the output voltages at turn-off, a discharge switch is connected from DGVEE to ground. The desired sequence is programmable by a resistor on the SEQ pin. See <u>Table 3</u> for the sequencing options.

## Integrated TFT Power Supplies and LED Backlight Drivers

#### **Fault Protection on the TFT Section**

The devices have robust fault and overload protection. If any of the source-driver or gate-driver supplies fall below 80% (typ) of the programmed regulation voltage for more than 50ms (typ), all the outputs latch off and a fault condition is set. If a short condition occurs on any of the sourcedriver supplies for more than 10µs, all the outputs latch off and a fault condition is set. A short condition is detected when the output voltage falls below 40% of the intended regulation voltage. With MAX20070GTJA/V+ and MAX20070BGTJA/V+, a short condition is also detected when POS voltage falls below 73% of HVINP voltage. The output with the fault turns off immediately, while the other outputs follow the turn-off sequence programmed by the resistor on the SEQ pin. The LED driver section is not turned off during a TFT fault event. The fault condition is cleared when the EN pin or IN supply is cycled. In the case of a thermal fault, both the TFT power section and the LED drivers turn off immediately and remain latched off. EN pin cycling or input power cycling is required to unlatch the fault and restart switching.

#### **True Shutdown**

The devices completely disconnect the loads from the input (IN) when in shutdown mode. In most boost converters, the external rectifying diode and inductor form a DC current path from the battery to the output. If a load is connected to the boost-converter output, it can drain the battery even in shutdown. The devices have an internal switch at POS. When this switch turns off during shutdown, there is no DC path from the input to POS.

#### **Output Control**

The devices' source-driver and gate-driver outputs (V<sub>GVEE</sub>, NEG, POS, and V<sub>GVDD</sub>) can be controlled by the resistor value connected from SEQ to ground. All outputs are brought up with soft-start control to limit the inrush current. Table 3 lists the sequencing options that are programmable with a resistor on the SEQ pin.

| SEQ PIN<br>RESISTOR         | (t1-t4 IS TH         | E TIME FR            | PLY SEQUE<br>OM THE EXI<br>START PERI | PIRATION OF                              | POWER-OFF SUPPLY SEQUENCING<br>(REVERSE ORDER OF POWER-UP)<br>(t5–t8 IS THE TIME FROM WHEN EN IS DRIVEN LOW) |                      |                      |                      |  |

|-----------------------------|----------------------|----------------------|---------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------|----------------------|----------------------|--|

| (R <sub>SEQ</sub> )<br>(kΩ) | 1st<br>AFTER<br>t1ms | 2nd<br>AFTER<br>t2ms | 3rd<br>AFTER<br>t3ms                  | 4th<br>AFTER<br>t4ms                     | 1st<br>AFTER<br>t5ms                                                                                         | 2nd<br>AFTER<br>t6ms | 3rd<br>AFTER<br>t7ms | 4th<br>AFTER<br>t8ms |  |

| 20 ±1%                      | POS                  | NEG                  | V <sub>GVEE</sub>                     | V <sub>GVDD</sub>                        | V <sub>GVDD</sub>                                                                                            | V <sub>GVEE</sub>    | NEG                  | POS                  |  |

| 60 ±1%                      | POS                  | NEG                  | V <sub>GVDD</sub>                     | V <sub>GVEE</sub>                        | V <sub>GVEE</sub>                                                                                            | V <sub>GVDD</sub>    | NEG                  | POS                  |  |

| 100 ±1%                     | NEG                  | POS                  | V <sub>GVEE</sub>                     | V <sub>GVDD</sub>                        | V <sub>GVDD</sub>                                                                                            | V <sub>GVEE</sub>    | POS                  | NEG                  |  |

| 140 ±1%                     | POS                  | V <sub>GVEE</sub>    | V <sub>GVDD</sub>                     | No NEG<br>output                         | V <sub>GVDD</sub>                                                                                            | V <sub>GVEE</sub>    | POS                  | No NEG<br>output     |  |

| 180 ±1%                     | POS                  | V <sub>GVDD</sub>    | V <sub>GVEE</sub>                     | No NEG<br>output                         | V <sub>GVEE</sub>                                                                                            | V <sub>GVDD</sub>    | POS                  | No NEG<br>output     |  |

| 220 ±1%                     | POS NEG              |                      | —                                     | V <sub>GVDD</sub> ,<br>V <sub>GVEE</sub> | V <sub>GVDD</sub> ,<br>V <sub>GVEE</sub>                                                                     |                      | _                    | POS, NEG             |  |

| 260 ±1%                     | V <sub>GVEE</sub>    | V <sub>GVDD</sub>    | NEG                                   | POS                                      | POS                                                                                                          | NEG                  | V <sub>GVDD</sub>    | V <sub>GVEE</sub>    |  |

#### **Table 3. Power Sequencing**

Note: t1 = t5 = 15ms

t2 = t6 = 30ms

t3 = t7 = 45ms

t4 = t8 = 60ms

## Integrated TFT Power Supplies and LED Backlight Drivers

#### Power-Up/Power-Down Sequencing and Timing

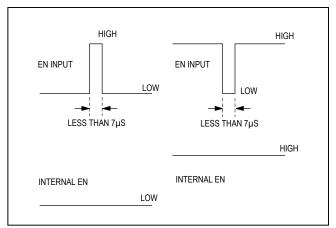

The devices allow for flexible power-up/power-down sequencing and timing of the source-driver and gate-driver power supplies ( $V_{GVEE}$ , NEG, POS, and  $V_{GVDD}$ ). Toggling the EN pin from low to high initiates an adjustable preset power-up sequence. Toggling the EN pin from high to low initiates an adjustable preset power-down sequence. The EN pin has an internal deglitching filter of 7µs (typ). Figure 11 shows a waveform of the internal EN signal, along with the EN input. **Note:** A glitch in the EN signal with a period less than 7µs is ignored by the internal enable circuitry.

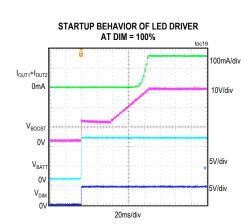

#### **LED Driver Section**

The MAX20070/MAX20070B also include a high-efficiency HB LED driver, which integrates all the features necessary to implement a high-performance backlight driver to power LEDs in small-to-medium-sized displays for automotive as well as general applications. The devices provide load-dump voltage protection up to 40V in automotive applications and incorporates a DC-DC controller with peak-current-mode control to implement a boost or SEPIC-type switched-mode power supply and a 2-channel LED driver with 20mA to 160mA constant-current-sink capability per channel.

The boost/SEPIC controller features constant-frequency peak-current-mode control with internal slope compensation to control the duty cycle of the PWM controller. The DC-DC converter generates the required supply voltage for the LED strings from a wide battery input supply range. Connect LED strings from the DC-DC converter output to the 2-channel constant-current sinks that control the current through the LED strings. A single resistor connected from ISET to ground sets the forward current through both LED strings.

The devices feature adaptive LED voltage control that adjusts the converter output voltage depending on the forward voltage of the LED strings. This feature minimizes the voltage drops across the constant-current sinks and reduces power dissipation in the device. The devices provide a very wide PWM dimming range where a dimming pulse as narrow as 0.5µs is possible at a 200Hz dimming frequency.

Figure 11. Power-Up/Power-Down Sequencing and Timing Waveform

The devices include output overvoltage protection that limits the converter output voltage to the programmed overvoltage threshold in the event of an open-LED condition, and also features an overtemperature protection that shuts down the controller if the die temperature exceeds +165°C. In addition, the devices have a shorted-LED string detection and an open-drain  $\overline{FLT}$  signal to indicate open-LED, shorted-LED, and overtemperature conditions.

#### **Current-Mode DC-DC Controller**

The MAX20070/MAX20070B use current-mode control to provide the required supply voltage for the LED strings. The internal MOSFET is turned on at the beginning of every switching cycle. The inductor current ramps up linearly until it is turned off at the peak current level set by the feedback loop. The peak inductor current is sensed from the voltage across the current-sense resistor (see R11 in Figure 1), connected from the source of the internal MOSFET to PGND. A PWM comparator compares the current-sense voltage plus the internal slope-compensation signal with the output of the transconductance error amplifier. The controller turns off the internal MOSFET when the voltage at CS exceeds the error amplifier's output voltage. This process repeats every switching cycle to achieve peak current-mode control.

#### **Error Amplifier**

The internal error amplifier compares an internal feedback (FB) signal with an internal reference voltage (V<sub>REF</sub>) and regulates its output to adjust the inductor current. An internal minimum string detector measures the minimum LED string cathode voltage with respect to GND. During normal operation, this minimum V<sub>OUT</sub> voltage is regulated to 0.75V through feedback. The resulting DC-DC converter output voltage is 0.75V above the maximum required total LED voltage.

The converter stops switching when LED strings turn off during PWM dimming. The error amplifier disconnects from the COMP output to retain the compensation capacitor charge. This allows the converter to settle to a steady-state level immediately when the LED strings turn on again. This unique feature provides fast dimming response without having to use large output capacitors. If the PWM dimming on-pulse is less than 25µs, the feedback controls the voltage on OVP, such that the converter output voltage regulates at 95% of the OVP threshold. This mode ensures that narrow PWM dimming pulses are not affected by the response time of the converter. During this mode, the error amplifier remains connected to the COMP output.

#### Adaptive-LED Voltage Control

The devices reduce power dissipation using an adaptive-LED voltage-control scheme. The adaptive-LED voltage control regulates the DC-DC converter output based on the operating voltage of the LED strings. The voltage at each of the current-sink outputs (OUT1, OUT2) is the difference between the DC-DC regulator output voltage (V<sub>LED</sub>) and the total forward voltage of the LED string connected to the output (OUT\_). The DC-DC converter then adjusts V<sub>LED</sub> until the output channel with the lowest voltage at OUT\_ is 0.75V relative to GND. As a result, the device minimizes power dissipation in the current sinks and still maintains LED current regulation. For efficient adaptive-control functionality, use an equal number of HB LEDs of the same forward-voltage rating in each string.

#### LED Current Control (ISET)

The devices feature two identical constant-current sinks used to drive multiple HB LED strings. The current through each of the channels is adjustable between 20mA and

## Integrated TFT Power Supplies and LED Backlight Drivers

160mA using an external resistor ( $R_{ISET}$ ) connected between ISET and GND. For single-channel operation, connect channel 1 (OUT1) and channel 2 (OUT2) together. When the OUT\_ pins are connected, the current in the LEDs will be twice the current programmed by the ISET pin. If only single-string operation is needed, the OUT\_ pin for the unused channel should be connected to ground. This disables the string at power-up.

#### **Current Limit**