Click here to ask an associate for production status of specific part numbers.

# 12-Switch Matrix Manager for Automotive Lighting

## **MAX20092**

#### **General Description**

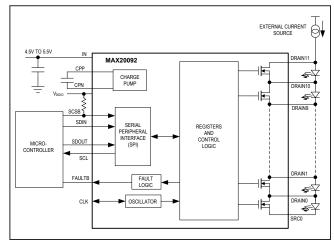

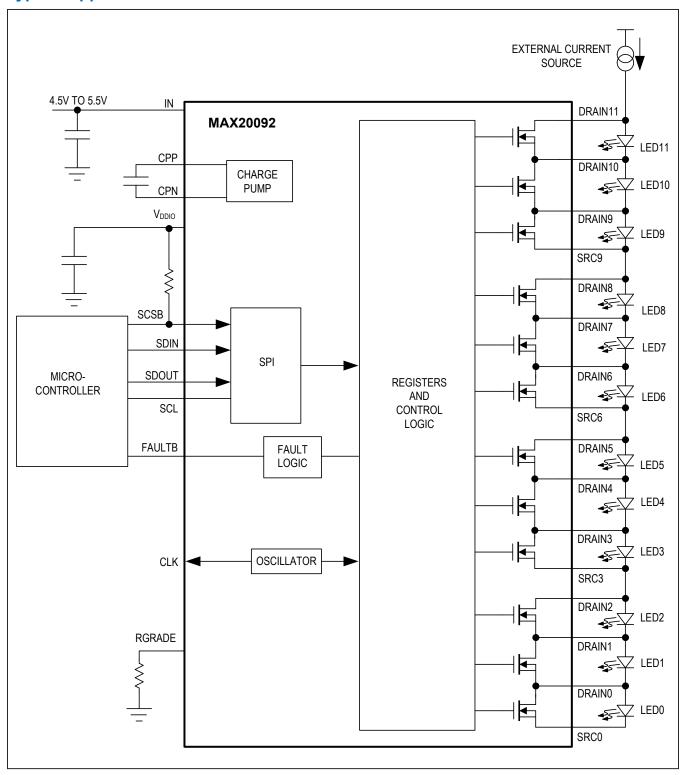

The MAX20092 12-switch matrix manager IC for automotive lighting applications includes a 12-switch array for bypassing individual LEDs in a single- or dual-string application. It features 12 individually controlled n-channel MOSFET switches rated for 10V with on-resistance of  $0.100\Omega$ . A single current source can be used to power all the LEDs connected in series. Individual LEDs can be dimmed by turning on and off the bypass switches across each LED, and can also be configured in 2 strings with 6 switches in series per string and 4 strings with 3 switches per string. A separate current source powers each string. Each switch can be connected across 1 or 2 LEDs in series. The IC also includes an internal charge pump that provides power for the gate drive of each of the LED bypass switches. The low on-resistance of the switches minimizes conduction loss and power dissipation.

The IC features a serial peripheral interface (SPI) for serial communication. The MAX20092 is a slave device that uses the SPI to communicate with an external microcontroller ( $\mu$ C), which is the master device. Each of the 12 switches can be independently programmed to bypass the LEDs across each of the switches in the string. Each switch can be turned fully on, fully off, or dimmed with or without fade-transition mode. The PWM frequency can be set by an internal oscillator or set to an external clock source. The IC features open-LED protection as well as open- and short-LED fault reporting through the SPI. The MAX20092 is available in a 32-pin (5mm x 5mm) sidewettable TQFN (SWTQFN) package with a thermally enhanced exposed pad.

### **Applications**

- Automotive Front-Light Systems

- Automotive Tail-Light Systems

- Automotive Matrix-Lighting Systems

#### **Benefits and Features**

- Automotive Ready: AEC-Q100 Qualified

- Flexible Configuration Allows the Use of the Same Device in Different Applications

- · Single-, Dual-, and Quad-String Configurations

- Up to 12 Switches in Series in Single-String Configurations

- Up to 6 Switches in Series in Dual-String Configurations

- Up to 3 Switches in Series in Quad-String Configurations

- · Up to 2 LEDs per Switch

- Optimal PWM Dimming Arrangement Provides Excellent Dimming Performance

- · Programmable 12-Bit PWM Dimming

- · Fade Transition Between PWM Dimming States

- Internal Clock Generator or External Clock for PWM Dimming

- Protection Features and Package Improve Reliability

- · Open-LED Protection

- Programmable Open-LED and Shorted-LED Threshold

- · Open- and Shorted-LED Fault Reporting

- Thermally Enhanced 32-Pin SWTQFN Package

Ordering Information appears at end of data sheet.

# **Simplified Block Diagram**

19-100310; Rev 1; 11/19

## **Absolute Maximum Ratings**

| IN, V <sub>DDIO</sub> to GND           | -0.3\/ to +6\/                     |

|----------------------------------------|------------------------------------|

|                                        |                                    |

| CPP to GND                             | 0.3V to +70V                       |

| CPN to GND                             | 0.3V to +65V                       |

| CPP to CPN                             | 0.3V to +16V                       |

| RGRADE to GND                          | 0.3V to $V_{IN}$ + 0.3V            |

| CPP to any DRAIN_ Pin                  | 0.3V to +70V                       |

| DRAIN11, DRAIN8, DRAIN5, and DRAIN2 to | GND0.3V to +56V                    |

| SRC0, SRC3, SRC6, SRC9 to GND          | 0.3V to +56V                       |

| DRAINx to DRAIN(x-1)                   | 0.3V to +14.0V                     |

| SDOUT, SCL, EN, CLK, ADDR2, ADDR1,     | ADDR0 SDIN,                        |

| SCSB, FAULTB to GND                    | $0.3V \text{ to } V_{DDIO} + 0.3V$ |

| Continuous Power Dissipation (Single-Lag        | yer Board)     |

|-------------------------------------------------|----------------|

| (T <sub>A</sub> = +70°C, derate 21.3mW/°C above | +70°C)1702.1mW |

| Continuous Power Dissipation (Multilayer        | Board)         |

| (T <sub>A</sub> = +70°C, derate 33.2mW°C above  | +70°C)2658mW   |

| Operating Temperature Range                     | 40°C to +125°C |

| Junction Temperature                            | +150°C         |

| Storage Temperature Range                       | 40°C to +150°C |

| Soldering Temperature (reflow)                  | +260°C         |

|                                                 |                |

|                                                 |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

#### 32-Pin (5mm x 5mm) SWTQFN

| PACKAGE CODE                           | T3255Y+10C       |

|----------------------------------------|------------------|

| Outline Number                         | <u>21-100210</u> |

| Land Pattern Number                    | 90-100092        |

| Thermal Resistance, Single-Layer Board |                  |

| Junction to Ambient (θ <sub>JA</sub> ) | 47°C/W           |

| Junction to Case (θ <sub>JC</sub> )    | 1.7°C/W          |

| Thermal Resistance, Four-Layer Board:  |                  |

| Junction to Ambient (θ <sub>JA</sub> ) | 30°C/W           |

| Junction to Case (θ <sub>JC</sub> )    | 1.6°C/W          |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

## **Electrical Characteristics**

(Input voltage and enable =  $V_{IN}$  =  $V_{EN}$  =  $V_{DDIO}$  = 5V,  $T_A$  =  $T_J$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 1)

| PARAMETER                                          | SYMBOL                  | CONDITIONS                                                   | MIN                         | TYP   | MAX                        | UNITS |  |

|----------------------------------------------------|-------------------------|--------------------------------------------------------------|-----------------------------|-------|----------------------------|-------|--|

| SUPPLY VOLTAGES                                    |                         |                                                              |                             |       |                            |       |  |

| Operating Supply Voltage<br>Range                  | V <sub>IN</sub>         |                                                              | 4.5                         |       | +5.5                       | V     |  |

| Input Operating Bias Current                       | I <sub>IN-Q</sub>       | No switching, SDIN, SDOUT, and SCL are idle and SCSB is high |                             | 2.3   |                            | mA    |  |

| Input POR Threshold                                | V <sub>IN-POR</sub>     | V <sub>IN</sub> rising                                       | 3.91                        | 4.2   | 4.475                      | V     |  |

| Input POR Hysteresis                               | POR <sub>VIN_HYST</sub> |                                                              |                             | 100   |                            | mV    |  |

| Charge-Pump Operating Voltage                      | V <sub>CPP</sub>        |                                                              |                             |       | 65                         | V     |  |

| CLK INTERNAL OSCILLATOR                            | OR EXTERNAL             | SYNC CLOCK SOURCE                                            |                             |       |                            |       |  |

| LED PWM-Dimming-Frequency Accuracy                 | fosc                    | Internal oscillator                                          | -10                         |       | +10                        | %     |  |

| Minimum LED PWM-Dimming Frequency                  |                         | DIV[1:0] = 0x3, internal oscillator                          | 225                         | 250   | 275                        | Hz    |  |

| CLK External Sync Input, Low                       | V                       | 2.2V < V <sub>DDIO</sub> < 5.5V                              |                             |       | 0.3 x<br>V <sub>DDIO</sub> | V     |  |

| Threshold                                          | V <sub>IL_CLK</sub>     | 1.7V < V <sub>DDIO</sub> < 2.2V                              |                             |       | 0.2 x<br>V <sub>DDIO</sub> | V     |  |

| CLK External Sync Input, High                      | V <sub>OH_CLK</sub>     | 2.2V < V <sub>DDIO</sub> < 5.5V                              | 0.7 x<br>V <sub>DDIO</sub>  |       |                            | V     |  |

| Threshold                                          | V <sub>IH_CLK</sub>     | 1.7V < V <sub>DDIO</sub> < 2.2V                              | 0.82 x<br>V <sub>DDIO</sub> |       |                            | V     |  |

| CLK External Sync Input, Clock Frequency           | f <sub>CLK</sub>        |                                                              | 0.30                        |       | 10.0                       | MHz   |  |

| CLK External Sync Input, Clock<br>Pulse-Width High | t <sub>CLKH</sub>       |                                                              | 30                          |       |                            | ns    |  |

| CLK External Sync Input, Clock<br>Pulse-Width Low  | tCLKL                   |                                                              | 30                          |       |                            | ns    |  |

| LED MATRIX SWITCHES                                |                         |                                                              |                             |       |                            |       |  |

| Single-Switch On-Resistance                        | R <sub>DS(ON)</sub>     | (Note 2)                                                     |                             | 0.070 |                            | Ω     |  |

| On-Resistance with Series<br>Switches 11–9 On      | R <sub>DS11-9(ON)</sub> | All series switches from 11–9 are on (Note 2)                |                             | 0.2   | 0.45                       | Ω     |  |

| On-Resistance with Series<br>Switches 8–6 On       | R <sub>DS8-6(ON)</sub>  | Series switches from 8–6 are all on (Note 2)                 |                             | 0.2   | 0.45                       | Ω     |  |

| On-Resistance with Series<br>Switches 5–3 On       | R <sub>DS5-3(ON)</sub>  | All series switches from 5–3 are on (Note 2)                 |                             | 0.2   | 0.45                       | Ω     |  |

| On-Resistance with Series<br>Switches 2–0 On       | R <sub>DS2-0(ON)</sub>  | All series switches from 2–0 are on (Note 2)                 |                             | 0.2   | 0.45                       | Ω     |  |

| Switch Leakage Current                             | I <sub>DS(OFF)</sub>    | V <sub>DS</sub> = 10V                                        |                             |       | 5                          | μΑ    |  |

| Open-LED Threshold                                 | V <sub>OTH</sub>        | Rising VDS                                                   | 9.0                         | 9.45  | 10.45                      | V     |  |

# **Electrical Characteristics (continued)**

(Input voltage and enable =  $V_{IN}$  =  $V_{EN}$  =  $V_{DDIO}$  = 5V,  $T_A$  =  $T_J$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 1)

| PARAMETER                                                                                        | SYMBOL                | CONDITIONS                                                  | MIN                         | TYP  | MAX                        | UNITS |

|--------------------------------------------------------------------------------------------------|-----------------------|-------------------------------------------------------------|-----------------------------|------|----------------------------|-------|

| Programmable Shorted-LED                                                                         | \/                    | V <sub>TH</sub> = 0V, rising V <sub>DS</sub>                | 0.80                        | 1    | 1.2                        | V     |

| Threshold                                                                                        | V <sub>STH</sub>      | V <sub>TH</sub> = 1, rising V <sub>DS</sub>                 | 4.3                         | 4.7  | 5.1                        | \ \ \ |

| Open-Trace Detect Minimum LED Current                                                            | I <sub>LED_MIN</sub>  |                                                             |                             |      | 230                        | mA    |

| LED MATRIX SWITCHES—LED                                                                          | SWITCH TIME           | NG                                                          | -                           |      |                            |       |

| LED Switch Open/Close Slew Accuracy                                                              | tslew_err             |                                                             | -33                         |      | +33                        | %     |

| LED Switch Open/Close Delay Variation                                                            | t <sub>SWDEL</sub>    | Variation of slew rate on any switch from the average value | -13.5                       |      | +13.5                      | %     |

| LED Slew-Rate Setting 0                                                                          | SR_LED_0              | 0 to 6V step, 10–90% rise/fall time,<br>LED_SLEW[2:0] = 0x0 |                             | 0.36 |                            | μs    |

| LED Slew-Rate Setting 1                                                                          | SR_LED_1              | 0 to 6V step, 10–90% rise/fall time,<br>LED_SLEW[2:0] = 0x1 |                             | 0.73 |                            | μs    |

| LED Slew-Rate Setting 2                                                                          | SR_LED_2              | 0 to 6V step, 10–90% rise/fall time,<br>LED_SLEW[2:0] = 0x2 |                             | 1.11 |                            | μs    |

| LED Slew-Rate Setting 3                                                                          | SR_LED_3              | 0 to 6V step, 10–90% rise/fall time,<br>LED_SLEW[2:0] = 0x3 |                             | 1.8  |                            | μs    |

| LED Slew-Rate Setting 4                                                                          | SR_LED_4              | 0 to 6V step, 10–90% rise/fall time,<br>LED_SLEW[2:0] = 0x4 |                             | 2.45 |                            | μs    |

| LED Slew-Rate Setting 5                                                                          | SR_LED_5              | 0 to 6V step, 10–90% rise/fall time,<br>LED_SLEW[2:0] = 0x5 |                             | 3.6  |                            | μs    |

| LED Slew-Rate Setting 6                                                                          | SR_LED_6              | 0 to 6V step, 10–90% rise/fall time,<br>LED_SLEW[2:0] = 0x6 |                             | 4.8  |                            | μs    |

| LED Slew-Rate Setting 7                                                                          | SR_LED_7              | 0 to 6V step, 10–90% rise/fall time,<br>LED_SLEW[2:0] = 0x7 |                             | 7.2  |                            | μs    |

| SPI ELECTRICAL CHARACTER                                                                         | RISTICS—POW           | /ER REQUIREMENTS                                            |                             |      |                            |       |

| I/O Supply Voltage                                                                               | V <sub>DDIO</sub>     |                                                             | 1.7                         |      | 5.5                        | V     |

| VDDIO UVLO Rising Threshold                                                                      | UVLO <sub>VDDIO</sub> |                                                             |                             |      | 1.65                       | V     |

| VDDIO UVLO Hysteresis                                                                            |                       |                                                             |                             | 50   |                            | mV    |

| Static I/O Supply Current                                                                        | I <sub>DDIO</sub>     | Static inputs, all outputs unloaded (Note 3)                |                             |      | 10                         | μA    |

| SPI ELECTRICAL CHARACTERISTICS—DIGITAL INPUT CHARACTERISTICS (ADDR0-ADDR2, SCLK, SDIN, SCSB, EN) |                       |                                                             |                             |      |                            |       |

| Innut High Volta                                                                                 | V                     | 2.2V < V <sub>DDIO</sub> < 5.5V                             | 0.7 x<br>V <sub>DDIO</sub>  |      |                            |       |

| Input High Voltage                                                                               | V <sub>IH</sub>       | 1.7V < V <sub>DDIO</sub> < 2.2V                             | 0.82 x<br>V <sub>DDIO</sub> |      |                            | V     |

| Input Low Voltors                                                                                | V                     | 2.2V < V <sub>DDIO</sub> < 5.5V                             |                             |      | 0.3 x<br>V <sub>DDIO</sub> | M     |

| Input Low Voltage                                                                                | V <sub>IL</sub>       | 1.7V < V <sub>DDIO</sub> < 2.2V                             |                             |      | 0.2 x<br>V <sub>DDIO</sub> | V     |

| Input Leakage Current                                                                            | I <sub>IN</sub>       | Input driven to 0V or V <sub>DDIO</sub> (Note 4)            |                             |      | ±1                         | μA    |

# **Electrical Characteristics (continued)**

(Input voltage and enable =  $V_{IN}$  =  $V_{EN}$  =  $V_{DDIO}$  = 5V,  $T_A$  =  $T_J$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 1)

| PARAMETER                                    | SYMBOL                 | CONDITIONS                                                                                                                                                                              | MIN                        | TYP  | MAX  | UNITS           |

|----------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------|------|-----------------|

| Internal Safety Impedance                    | R <sub>PD</sub>        | SDI, SCLK pulldown to GND (Note 5)                                                                                                                                                      | 40 100 160                 |      | 160  | kΩ              |

| internal Salety Impedance                    | I <sub>RPU_SCSB</sub>  | SFT_SCSB pullup resistance to V <sub>DDIO</sub>                                                                                                                                         | 40                         | 100  | 160  | K22             |

| Input Capacitance                            | C <sub>IN</sub>        |                                                                                                                                                                                         |                            | 10   |      | pF              |

| Hysteresis Voltage                           | V <sub>H</sub>         |                                                                                                                                                                                         |                            | 0.15 |      | V               |

| SPI ELECTRICAL CHARACTER                     | RISTICS—DIGI           | TAL OUTPUT CHARACTERISTICS (SDOUT                                                                                                                                                       | r, CLK)                    |      |      |                 |

| Output High Voltage                          | V <sub>OH</sub>        | V <sub>DDIO</sub> > 2.5V, I <sub>SOURCE</sub> = 5mA                                                                                                                                     | V <sub>DDIO</sub><br>- 0.4 |      |      | V               |

| output riigii voltago                        | VOH                    | V <sub>DDIO</sub> > 1.7V, I <sub>SOURCE</sub> = 2mA                                                                                                                                     | V <sub>DDIO</sub><br>- 0.4 |      |      |                 |

| Output Low Voltage                           | V <sub>OL</sub>        | V <sub>DDIO</sub> > 2.5V, I <sub>SINK</sub> = 5mA                                                                                                                                       |                            |      | 0.4  | V               |

| Output Low Voltage                           | VOL                    | V <sub>DDIO</sub> > 1.7V, I <sub>SINK</sub> = 2mA                                                                                                                                       |                            |      | 0.4  | V               |

| Output Three-State Leakage                   | loz                    | Output voltage between 0V and V <sub>DDIO</sub>                                                                                                                                         |                            |      | ±1   | μΑ              |

| Output Three-State<br>Capacitance            | C <sub>OZ</sub>        |                                                                                                                                                                                         |                            | 10   |      | pF              |

| SPI TIMING CHARACTERISTIC                    | S                      |                                                                                                                                                                                         |                            |      |      |                 |

| SCLK Frequency                               | f <sub>SCLK</sub>      |                                                                                                                                                                                         | 128                        |      | 4000 | kHz             |

| SPI SCSB Maximum Pulse<br>Width              | t <sub>MAX_</sub> SCSB | The maximum duration of an SPI packet; longer than this and the part times out the SPI packet and declares an SPI_ERR; internal clock frequency depends on PWM_IN_SEL register settings |                            |      | 2048 | Clock<br>Cycles |

| SCLK Pulse Width High                        | t <sub>CH</sub>        |                                                                                                                                                                                         | 87.5                       |      |      | ns              |

| SCLK Pulse Width Low                         | t <sub>CL</sub>        | (Note 6)                                                                                                                                                                                | 87.5                       |      |      | ns              |

| SCSB Fall to SCLK Rise Setup Time            | t <sub>CSS0</sub>      | To first SCLK rising edge (Note 6)                                                                                                                                                      | 50                         |      |      | ns              |

| SCSB Fall to SCLK Rise Hold Time             | t <sub>CSH0</sub>      | Applies to inactive rising edge preceding the first rising edge                                                                                                                         | 50                         |      |      | ns              |

| SCSB Rise to SCLK Rise Hold Time             | t <sub>CSH1</sub>      | Applies to 32nd rising edge                                                                                                                                                             | 50                         |      |      | ns              |

| SCSB Rise to SCLK Rise                       | t <sub>CSA</sub>       | Applies to 32nd rising edge, guarantees aborted (unqualified) sequence                                                                                                                  | 25                         |      |      | no              |

| SCSB RISE to SCLR RISE                       | t <sub>CSQ</sub>       | Applies to 33rd rising edge, guarantees qualified sequence                                                                                                                              | 25                         |      |      | ns              |

| SCSB Pulse Width High t <sub>CSPW</sub>      |                        |                                                                                                                                                                                         | 100                        |      |      | ns              |

| SDI to SCLK Rise Setup Time t <sub>DS</sub>  |                        |                                                                                                                                                                                         | 20                         |      |      | ns              |

| SDI to SCLK Rise Hold Time t <sub>DH</sub>   |                        |                                                                                                                                                                                         | 20                         |      |      | ns              |

| SCLK Fall to SDO Transition t <sub>DOT</sub> |                        | C <sub>LOAD</sub> = 20pF                                                                                                                                                                |                            |      | 80   | ns              |

|                                              |                        | C <sub>LOAD</sub> = 0pF                                                                                                                                                                 | 2                          |      |      | ns              |

| SCSB Fall to SDO Transition                  | t <sub>DOE</sub>       | C <sub>LOAD</sub> = 20pF                                                                                                                                                                |                            |      | 50   | ns              |

| SCSB Rise to SDO High Impedance              | t <sub>DOZ</sub>       | Disable time                                                                                                                                                                            |                            |      | 50   | ns              |

#### **Electrical Characteristics (continued)**

(Input voltage and enable =  $V_{IN}$  =  $V_{EN}$  =  $V_{DDIO}$  = 5V,  $T_A$  =  $T_J$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 1)

| PARAMETER                             | SYMBOL              | CONDITIONS                                                     | MIN  | TYP   | MAX  | UNITS |  |

|---------------------------------------|---------------------|----------------------------------------------------------------|------|-------|------|-------|--|

| FAULT STATUS OUTPUT                   |                     |                                                                |      |       |      |       |  |

| FAULTB Output Low Voltage             | V <sub>FAULTB</sub> | I <sub>FAULTB</sub> = 3mA                                      |      | 0.04  | 0.4  | V     |  |

| FAULTB Output High Leakage<br>Current | I <sub>FAULTB</sub> | V <sub>FAULTB</sub> = 5V                                       |      |       | 1.0  | μA    |  |

| GRADE SELECTION                       |                     |                                                                |      |       |      |       |  |

| RGRADE Output Current                 | I <sub>RGRADE</sub> |                                                                | 46.2 | 50.0  | 53.5 | μA    |  |

| RGRADE_0 Range                        |                     | RGRADE[2:0] = 0b000                                            |      |       | 8.1  | kΩ    |  |

| RGRADE_1 Range                        |                     | RGRADE[2:0] = 0b001                                            | 10.1 |       | 12.1 | kΩ    |  |

| RGRADE_2 Range                        |                     | RGRADE[2:0] = 0b010                                            | 14.8 |       | 16.2 | kΩ    |  |

| RGRADE_3 Range                        |                     | RGRADE[2:0] = 0b011                                            | 19.6 |       | 22.3 | kΩ    |  |

| RGRADE_4 Range                        |                     | RGRADE[2:0] = 0b100                                            | 26.5 |       | 30.5 | kΩ    |  |

| <b>R</b> GRADE_5 Range                |                     | RGRADE[2:0] = 0b101                                            | 36.0 |       | 42.6 | kΩ    |  |

| RGRADE_6 Range                        |                     | RGRADE[2:0] = 0b110                                            | 50.6 |       | 58.0 | kΩ    |  |

| RGRADE_7 Range                        |                     | RGRADE[2:0] = 0b111                                            | 70.0 |       |      | kΩ    |  |

| CHARGE PUMP                           |                     |                                                                |      |       |      |       |  |

| Charge-Pump Frequency                 | f <sub>CPP</sub>    |                                                                |      | 8.192 |      | MHz   |  |

| Charge-Pump Output Voltage            | Vo                  | V <sub>CPP</sub> - V <sub>CPN</sub> , I <sub>CPP</sub> = 250μA | 7.4  |       | 9    | V     |  |

| Charge-Pump Power-Good<br>Threshold   | V <sub>CPP_OK</sub> | Rising threshold                                               | 5.68 | 6.9   | 7.85 | V     |  |

| THERMAL SHUTDOWN                      |                     |                                                                |      |       |      |       |  |

| Thermal-Warning Threshold             | TH_WARN             | Rising temperature                                             |      | 150   |      | °C    |  |

| Thermal Shutdown                      | TH_SHDN             | Rising temperature                                             |      | 160   |      | °C    |  |

| Thermal-Shutdown Hysteresis           | HYS_SHDN            |                                                                |      | 20    |      | °C    |  |

- Note 1: Limits are 100% tested at  $T_A = +25$ °C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.

- Note 2: Excludes bond-wire resistance. Typical package bond-wire impedance =  $15m\Omega$  per pin.

- Note 3: Static logic inputs with  $V_{IL}$  = GND and  $V_{IH}$  =  $V_{DDIO}$  (Note 1). SCSB =  $V_{IH}$  (if pullup active).

- Note 4: No internal safety pullup/pulldown impedances active, input buffers only.

- Note 5: Internal safety pullup/pulldown impedances available, with enable function.

- Note 6: Applications must afford time for the device to drive data on the SDO bus and meet the  $\mu$ C setup time prior to the  $\mu$ C latching in the result on the following SCLK RE. In practice, this is determined by loading and  $\mu$ C characteristics, and the relevant  $t_{DOT}/t_{DOE}$ .

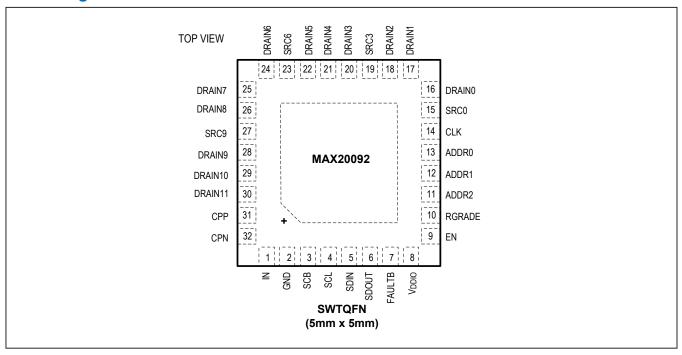

# **Pin Configuration**

## **Pin Description**

| PIN | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                             |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | IN     | 5V Power-Supply Input. Bypass with a 0.1µF (min) ceramic capacitor.                                                                                                                                                                                                                                                                                  |

| 2   | GND    | Ground Connection                                                                                                                                                                                                                                                                                                                                    |

| 3   | SCSB   | Chip-Select Pin for SPI. This pin is pulled low to enable the SPI.                                                                                                                                                                                                                                                                                   |

| 4   | SCL    | Clock Input Pin for SPI                                                                                                                                                                                                                                                                                                                              |

| 5   | SDIN   | Data Input Pin for SPI                                                                                                                                                                                                                                                                                                                               |

| 6   | SDOUT  | Data Output Pin for SPI                                                                                                                                                                                                                                                                                                                              |

| 7   | FAULTB | Fault Output for Fault-Condition Report. The FAULTB pin is asserted (pulled low) to indicate that a fault condition has been detected, as defined by the STAT_GEN register. The FAULTB pin is deasserted (released to high) after the part sends its fault response address successfully, or the fault condition is cleared by an SPI write command. |

| 8   | VDDIO  | Digital Interface Power-Supply Input                                                                                                                                                                                                                                                                                                                 |

| 9   | EN     | Enable Pin. Drive EN to V <sub>DDIO</sub> to enable the device; drive it to GND to reset the registers and stop switching.                                                                                                                                                                                                                           |

| 10  | RGRADE | Grade Selection Pin. This pin sets the REV_ID bits 5 to 7 in the NO_OP (0x00) register. Connect a $69.8k\Omega$ to $0\Omega$ resistor between RGRADE and GND, or drive with a voltage source between GND and IN capable of sinking $50\mu$ A to provide part grading information that can be read back from register NO_OP (0x00).                   |

| 11  | ADDR2  | SPI Interface Address Selection. Connect to V <sub>DDIO</sub> , GND, or SDI.                                                                                                                                                                                                                                                                         |

| 12  | ADDR1  | SPI Interface Address Selection. Connect to V <sub>DDIO</sub> , GND, or SDI.                                                                                                                                                                                                                                                                         |

| 13  | ADDR0  | SPI Interface Address Selection. Connect to V <sub>DDIO</sub> , GND, or SDI.                                                                                                                                                                                                                                                                         |

# **Pin Description (continued)**

| PIN | NAME    | FUNCTION                                                                                                   |

|-----|---------|------------------------------------------------------------------------------------------------------------|

| 14  | CLK     | External PWM Clock Input and Internal Oscillator Output Pin                                                |

| 15  | SRC0    | Source of Internal Switch 0                                                                                |

| 16  | DRAIN0  | Drain of Switch 0. Connect to anode of LED0 and cathode of LED1.                                           |

| 17  | DRAIN1  | Drain of Switch 1. Connect to anode of LED1 and cathode of LED2.                                           |

| 18  | DRAIN2  | Drain of Switch 2. Connect to anode of LED2 and cathode of LED3 (if LED3 in series with LED2).             |

| 19  | SRC3    | Source of Internal Switch 3                                                                                |

| 20  | DRAIN3  | Drain of Switch 3. Connect to anode of LED3 and cathode of LED4.                                           |

| 21  | DRAIN4  | Drain of Switch 4. Connect to anode of LED4 and cathode of LED5.                                           |

| 22  | DRAIN5  | Drain of Switch 5. Connect to anode of LED5. If LED6 in series with LED5, also connect to cathode of LED6. |

| 23  | SRC6    | Source of Internal Switch 6                                                                                |

| 24  | DRAIN6  | Drain of Switch 6. Connect this pin to anode of LED6.                                                      |

| 25  | DRAIN7  | Drain of Switch 7. Connect to anode of LED7 and cathode of LED8.                                           |

| 26  | DRAIN8  | Drain of Switch 8. Connect to anode of LED8 and (if LED9 in series with LED8) cathode of LED9.             |

| 27  | SRC9    | Source of Internal Switch 9                                                                                |

| 28  | DRAIN9  | Drain of Switch 9. Connect to anode of LED9 and cathode of LED10.                                          |

| 29  | DRAIN10 | Drain of Switch 10. Connect to anode of LED10 and cathode of LED11.                                        |

| 30  | DRAIN11 | Drain of Switch 11. Connect to anode of LED11.                                                             |

| 31  | CPP     | Charge-Pump Positive Terminal. Connect a 0.1µF ceramic capacitor from this pin to CPN.                     |

| 32  | CPN     | Charge-Pump Negative Voltage. Connect a 0.1µF ceramic capacitor from this pin to CPP.                      |

| _   | EP      | Exposed Pad. Connect EP to GND.                                                                            |

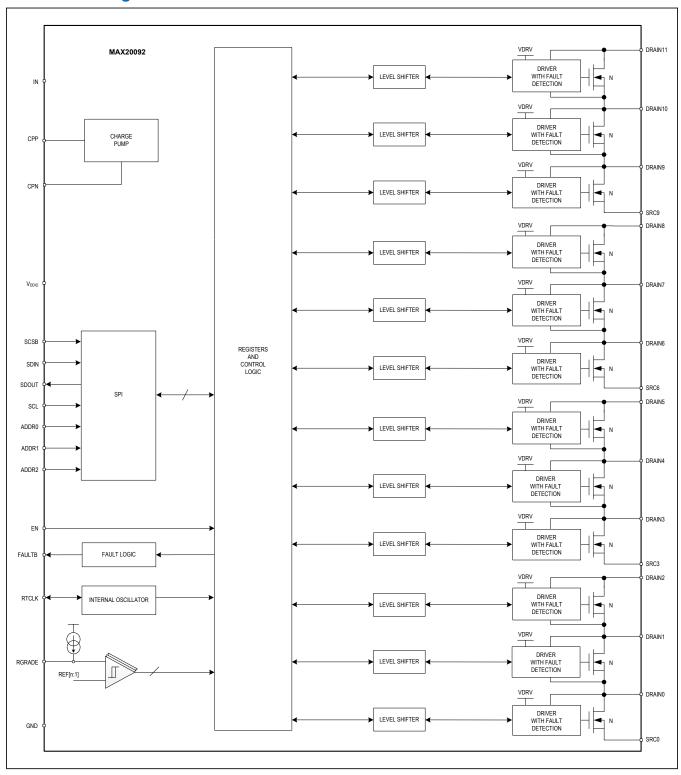

# **Functional Diagram**

#### **Detailed Description**

The MAX20092 12-switch matrix manager IC for automotive lighting includes a 12-switch array for bypassing individual LEDs in a single- or dual-string application. The IC features 12 individually controlled n-channel MOSFET switches rated for 10V with an on-resistance of  $0.100\Omega$ . A single current source can be used to power all the LEDs connected in series. Individual LEDs can be dimmed by turning on and off the bypass switches across each LED. The IC can also be configured in two strings with 6 switches in series per string or 4 strings with 3 switches per string. A separate current source powers each string. Each switch can be connected across one or two LEDs in series. The IC also includes an internal charge pump that provides the gate drive for each of the LED bypass switches. The low on-resistance of the switches minimizes conduction loss and power dissipation.

The IC features a serial peripheral interface (SPI) for serial communication. The IC is a slave device and uses the SPI to communicate with an external microcontroller which is the master. Each of the 12 switches can be independently programmed to bypass the LEDs across each of the switches in the string. Each switch can be turned fully on, fully off, or dimmed with or without a fade transition mode. The PWM frequency can be set by an internal oscillator or can also be set to an external clock source. The IC features open-LED protection, as well as open- and short-LED fault reporting through SPI. The IC is available in a 5mm x 5mm 32-pin side-wettable TQFN (SWTQFN) package with a thermally enhanced exposed pad. The SPI is capable of operating from 1.8V to 5.5V and is driven from the VDDIO supply.

Each switch has an individual driver, overvoltage-protection circuit, and a diagnostic circuit referenced to the source of that switch. This configuration allows for fully dynamic operation with the switches above it and below it. The IC monitors overvoltage conditions on each switch and automatically protects them in the event of an open-LED connection. The open-LED fault can be programmed at one of the two threshold levels: 4.5V or 9.0V. The short-LED fault can also be programmed at one of two threshold levels: 1.0V or 4.4V. When a shorted-LED fault is detected in a channel, the channel switch continues with what it is doing. The IC detects open-LED conditions as well as shorted-LED conditions and reports them through the fault-reporting network. The IC also detects and reports a thermal-warning condition. The FAULTB signal pulls low if thermal shutdown is activated.

#### **Power-On Reset**

Once the IC is powered, an internal power-on reset (POR) signal sets all the registers to their default states. All 12 switches are in the on state upon a POR (all LEDs are off). The LEDs remain off until a command is received by the SPI. To ensure reliable operation, the IN supply voltage (V<sub>IN</sub>) must be greater than V<sub>IN-POR</sub>. If V<sub>IN</sub> falls below V<sub>IN-POR</sub>, the registers reset to their default state. The IN voltage must be greater than V<sub>IN-POR</sub> and EN = 1 for SPI operation.

#### **Enable Function (EN)**

When the EN pin is low, all registers are reset to their default values and all the bypass switches are turned on.

When the EN pin is brought high, the IC is enabled and the SPI registers can be written to, as described in the <u>SPI Transactions</u> section. The bypass switches remain in their default on state until the SPI is used to enable LED dimming.

#### **Internal Switches**

Each switch connected between DRAINn and DRAINn-1 has a typical on-resistance of  $0.10\Omega$ . This measurement includes the on-resistance of the internal switch and the resistance of the bond wires to the DRAINn and DRAINn-1 pads. Each bypass switch, when driven to an off state, allows the string current to flow through the corresponding parallel-connected LED, turning the LEDs on. Driving the bypass switch to an on state shunts the current through the bypass switch and turns the LEDs off. Each bypass switch can have one or two LEDs in series across it.

#### **LED Fault Detection and Protection**

The IC is able to detect a shorted LED, open LED, and open trace between the device and the LED. To detect and report an LED fault, several conditions must be met. First, the LED switch must be operating, so SW\_GO\_EN and the EN pin should both be high. LED-open and LED-short detection requires the switch be open, so the duty cycle must be greater than zero. Conversely, open-fault detection requires the switch to be closed, so PWM duty cycle must be less than 100%. In general, it takes up to one dimming cycle to make sure these conditions have been met after a fault condition is applied. This period depends on the PWM dimming frequency.

#### **LED Open-Fault Detection and Protection**

An open-LED fault is triggered when the voltage between the individual LED switch DRAIN node and switch SOURCE node exceeds VOTH and is reported in register STAT\_OPEN\_LED (0x06). The switch is closed when an open-LED detection occurs and remains closed until the next PWM dimming open-switch request occurs. By default, the open fault results in the FAULTB pin being driven low; however, open faults can be masked by writing 0b1 to the MSK\_OPEN\_LED bit in the CNFG\_MSK (0x04) register. If an open-LED fault is detected multiple times, it is recommended that the OPEN\_OVRD (0x08) register be updated to force the corresponding LED switch to remain closed continuously to provide a bypass for the faulty LED.

#### **LED Short Detection**

A short-LED fault is triggered when the voltage between the switch DRAIN node and the switch SOURCE node is below V<sub>STH</sub> for an open switch condition, and is reported in the STAT\_SHRT (0x09) register. The LED short comparator is sampled at the end of each LED pulse to avoid false detects during the beginning of the pulse. No action is taken with the switch in response to detecting a short-LED fault, with it continuing to operate as programmed. The short fault, by default, results in FAULTB being driven low; however, short faults can be masked by writing 0b1 to MSK SHRT in the CFG MSK (0x04) register.

#### **Open-Trace Detection**

An open-trace fault is triggered when the current through the closed switch is less than  $I_{\mbox{\footnotesize LED\_MIN}}$  and is reported in the STAT\_OPEN\_TRACE (0x07) register. No action is taken with the channel switch in response to detecting an open trace, with it continuing to operate as programmed. By default, the open-trace fault results in the FAULTB pin being driven low; however, open-trace faults can be masked by writing 0b1 to MSK\_OPEN\_TRACE in the CFG\_MSK (0x04) register.

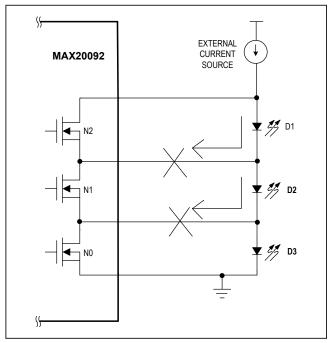

The open-trace fault is sampled before the rising PWM edge, which is the edge turning the switch off. If there is an open trace to the drain side of the switch, the switch above it has to be open during the PWM rising edge of the switch that is detecting the condition. For example, if there is an open trace on the drain side of N1 (see Figure 1), then N2 has to be open when N1 is turning on and similarly, for detecting an open-trace condition on the drain of N0 (N1 must be open when N0 is turning on). For the top-most-switch N2 drain connection, and the bottom-most-switch source connection, there is no constraint to detect the open-trace condition.

#### Thermal Shutdown

The IC features an on-chip temperature-protection circuit to prevent the device from overheating.

When the die temperature rises above the thermal-warning threshold (+150°C), the TH\_WARN bit is set, causing the FAULTB pin to be asserted if unmasked, but no action is taken with the switches. If asserted, the FAULTB pin remains asserted until the die temperature drops below the thermal-warning threshold, and a read of the STAT\_GEN (0x05) register has occurred. To clear the TH\_WARN bit, the die temperature must be below the thermal-warning threshold.

When the die temperature rises above the thermal-shutdown threshold (+160°C), the TH\_SHDN bit is set, causing the FAULTB pin to be asserted and all switches to either be closed (LEDs turned off) or opened (LEDs turned on), depending on the value of the CNFG\_MSK (0x04) register. Switches remain static and the FAULTB pin remains asserted until the die temperature drops below the thermal-warning threshold, and a read of the STAT\_GEN register has occurred.

When the device recovers from thermal shutdown, it resumes operation from where it was before the thermal shutdown. The TH\_WARN and TH\_SHDN bits are cleared on read.

Figure 1. Open-Trace Detection

#### **FAULTB Pin Operation**

The FAULTB pin is an active-low, open-drain output. The IC asserts a fault if any of the bits are set in the SPI STAT\_GEN register (0x05). See the STAT\_GEN register (0x05) in the *Register Map* section and the subsequent register table for more details on the definition of each bit. Once all the bits have been cleared by reading the appropriate SPI registers, the FAULTB pin is released. **Note:** If the conditions causing the fault bit(s) to be asserted persist, the bits are immediately set again. The FAULTB pin remains low.

# **PWM Clock and Synchronous Operation with Multiple Devices**

The PWM clock for the IC can be selected from the internal oscillator or from an external clock source driving the CLK pin. The CLK pin is bidirectional, allowing a single device to be the master clock, providing a common clock source to multiple devices. The PWM clock source and CLK pin direction are configured through PWM CLK[1:0] in the CNFG GEN (0x03) register. The default value is internal oscillator with the CLK pin disabled. For synchronous operation with multiple devices, use the PWM CLK SEL bits in the CNFG GEN (0x03) register to set the master with internal oscillator and CLK pin output, and the slave devices with external oscillator and CLK pin input.PWM dimming frequency is programmable by setting the value of the DIV[1:0] bits in the CNFG GEN (0x03) register, which sets the divide ratio for both the internal (8.192MHz) and external clock sources. When disabled, the CLK pin is high impedance with a  $100k\Omega$ pulldown resistor.

# Parallel Operation for Higher Current Applications

The switches in the IC can handle current up 1.6A (max); however, for applications that require higher currents, the switches can be configured in parallel. For example, if

the current capability needs to be doubled with 6 LEDs, connect switch SW0 in parallel to SW6, SW1 in parallel to SW7, and so on. Make sure the switches connected in parallel have the same phase shift and PWM dimming duty cycles.

#### **PWM Dimming**

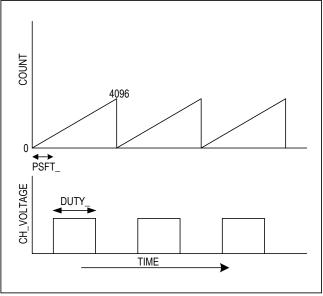

The IC provides 12-bit programmable dimming on each individual switch. An internal 12-bit counter (COUNT) is generated according to the clock settings. The switch turns off when COUNT is equal to the delay set by the corresponding PSFT register and stays off until the COUNT exceeds the sum of PSFT and PWM duty-control registers. In this way, the duty cycle and relative phase shift of the individual switches can be set independently (see Figure 2).

Figure 2. PWM Dimming

#### **Dimming With and Without Fade**

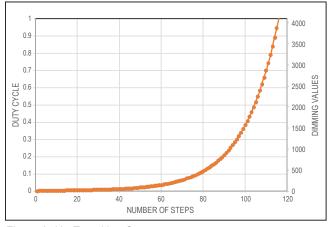

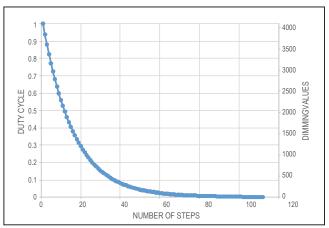

Each switch of the IC can be independently programmed to perform dimming without fade transition, or dimming with fade transition. For dimming without fade transition, the dimming changes from the initial value to the target value in one dimming cycle. For dimming with fade transition, the dimming changes transitionally step by step, starting from the initial value to the target value in multiple dimming cycles, following a predetermined exponential curve.

To enable dimming with fade transition, set the FADE bit to 1 and the DUTY bits to the target value for the specific switches. Each transitional step value is calculated using 12 bits according to the following formula:

DUTYnext = DUTYnow x CF

where DUTY is the duty cycle, and CF the constant factor.

CF = 1.0625 and CF = 0.9375 for an up transition and down transition, respectively.

DUTYnext continues to be updated according to the formula until DUTYnext reaches the target value. The transition period is defined by the TDIM\_ register for the switch. The number of transitional steps depends on the distance between the initial value and the target value. The maximum number of transitional steps from 1(/4095) to 4095(/4095) is 115 steps. See Figure 3 for the up-transition curve. The number of transitional steps depends on the distance between the initial value and the target value. The maximum number of transitional steps from 4095(/4095) to 1(/4095) is 111 steps. See Figure 4 for the down-transition curve.

Duty-cycle steps smaller than CF update in 1 step.

Each step runs TDIM PWM dimming cycles, and each dimming cycle consists of 4096 clock cycles; therefore Tstep = TDIM  $\times$  4096.

#### **Grade Selection**

The IC provides eight levels of detection between 0 and 4V on the RGRADE pin, which can be read back as part of the REV ID in the NO OP (0x00) register. The RGRADE pin sources 50µA, allowing the use of an external resistor between RGRADE and GND to set the voltage level. See Table 1 for threshold levels and recommended resistor values.

**Table 1. RGRADE Recommended Values**

| RGRADE[2:0] | RESISTOR VALUE<br>R <sub>RGRADE</sub> (KΩ, 1%) | RGRADE VOLTAGE (V) |

|-------------|------------------------------------------------|--------------------|

| 0b000       | 0 (Short to GND)                               | 0.0                |

| 0b001       | 11.3                                           | 0.565              |

| 0b010       | 15.8                                           | 0.790              |

| 0b011       | 21.0                                           | 1.05               |

| 0b100       | 28.7                                           | 1.435              |

| 0b101       | 40.2                                           | 2.01               |

| 0b110       | 54.9                                           | 2.745              |

| 0b111       | 75.0                                           | 3.75               |

Figure 3. Up-Transition Curve

Figure 4. Down-Transition Curve

Analog Devices | 13

#### 4-Wire Serial Interface

#### **General Description**

The IC recognizes transactions during which SCSB is low. The serial peripheral interface (SPI) latches SDI input data on SCLK's rising edge and executes commands on SCSB's rising edge, subject to qualification criteria. SDO is active when SCSB is low, and is held in three-state when SCSB is high. Star connections of up to 26 devices are supported. Internal pullup and pulldown resistors are included on all input pins to enhance safety in the event of a broken wire/trace. SPI\_ERR and CRC checks are offered for interface verification.

The following features are supported by the SPI:

- 32-Bit SPI Frame

- SCSB Active-Low Device Selection

- SCSB Rising-Edge Transaction Execution

- SDI Data Latched on SCLK Rising Edge

- 7-Bit Register Addressing with 13-Bit Data

- 128 Write/Read Accessible Registers (00–7F\h)

- Embedded CRC3 Checking

- SPI ERR Interface Error-Indicator Bit

- Configurable Internal Pullup/Pulldown Terminations on All Input Pins

- Star Connections of Up to 26 Devices Supported on Single SCSB Line

#### Overview

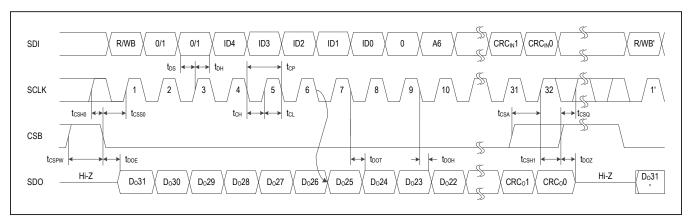

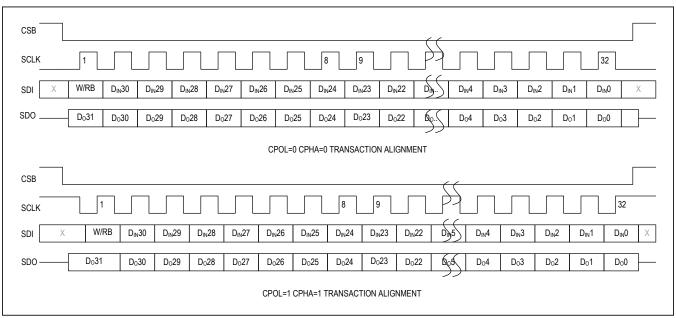

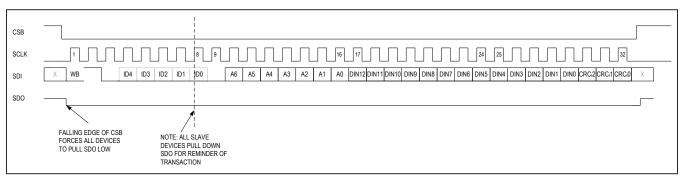

The MAX20092 interface is SPI, QSPI, Microwire, and DSP compatible. The operation and timing criteria of the SPI is shown in Figure 5. The device is programmed by a 32-cycle SPI instruction, framed by a low interval on SCSB. The start of the transaction is defined by the SCLK rising edge following the SCSB falling edge (subject to tosho and tosso timing criteria). Transactions including a number of SCLK rising edges not equal to 32 are not qualified for execution (also based on t<sub>CSA</sub>, t<sub>CSH1</sub>, and t<sub>CSO</sub> timing criteria). Qualified transactions are executed on the rising edge of SCSB. To abort a command sequence, the rise of SCSB must precede a qualified 32nd rising edge of SCLK (meeting the t<sub>CSA</sub> timing requirement).If SCLK stops toggling for more that 256µs while SCSB remains low, the device declares a SPI timeout error and asserts CLK ERR.

The SDI content of the SPI transaction consists of a leading read/writeB (R/WB) bit followed by device ID, address, input data information, and CRC. Data is latched into the registers on SCLK rising edges, subject to setup and hold criteria (t<sub>DS</sub>, t<sub>DH</sub>).

SDO is actively driven during intervals where SCSB is low. SDO is initially driven by the device when SCSB falls ( $t_{DOE}$  timing applies), presenting the MSB of the output data (the SPI\_ERR bit for all transactions). Following the initial SCLK rising edge, SDO is updated in response to SCLK falling edges, conforming to hold- and transition-time criteria ( $t_{DOH}$ ,  $t_{DOT}$ ), allowing the  $\mu$ C to latch the data on SCLK rising edges. When SCSB is high, the SDOUT line is high impedance, allowing other devices to access the SDO bus.

Figure 5. SPI Timing Diagram

#### **Device Connections**

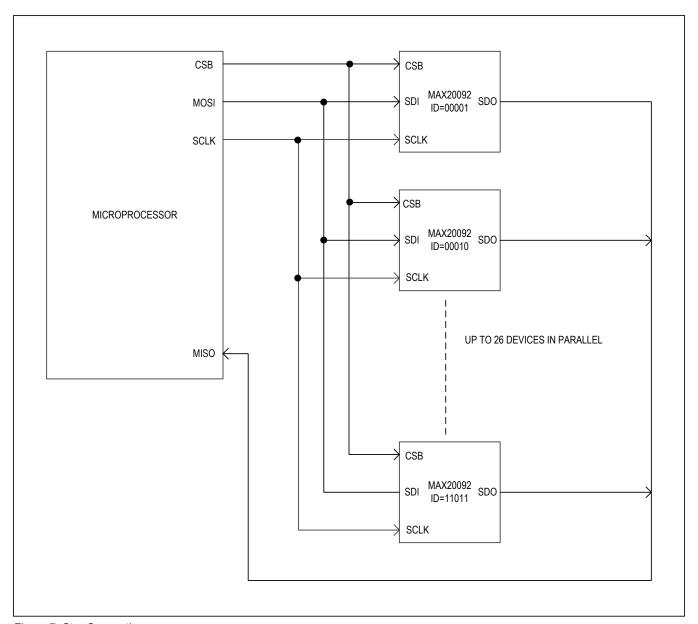

The SPI ensures compatible operation with standard microcontrollers ( $\mu$ Cs) from a variety of manufacturers. The  $\mu$ C always operates as the master, and is able to initiate read and write transactions to individual slave devices (using standard connections), or groups of slave devices in a star configuration. The device(s) always operate in the slave role when connected to a  $\mu$ C and cannot initiate a SPI transaction.

The SCLK line should be driven by the master and hooked up to all slave devices. Only the slave devices (or group of slave devices) with its SCSB line low will accept SCLK. SPI transactions to the slave devices are defined by SCLK rising edges. The MAX20092 can therefore sup-

port SPI formats with (CPOL=0, CPHA=0) or (CPOL=1, CPHA=1), see Figure 6 for alignment examples. The SDI line should be hooked up to a master-out/slave-in (MOSI) port. A single SDI line can be routed to all SPI slave devices sharing the interface, but only the slave device (or group of slave devices) with the SCSB line low will accept SDI data. The  $\mu$ C should update SDIN in response to SCLK falling edges so the slave can latch data in on SCLK rising edges. The SDO line should be hooked up to a master-in/slave-out (MISO) port. A single SDO line can be routed to all slave SPI devices sharing the interface, but only the slave device (or group of slave devices) with its SCSB line low can access and drive the shared SDO bus. The slave updates SDO in response to SCLK falling edges, so the  $\mu$ C can latch data in on SCLK rising edges.

Figure 6. SPI Transaction Format

#### **Star Device Connections**

The IC's SPI allows multiple devices to share the interface, with the active device for the transaction being selected by a predetermined device ID number. The SCSB, SCLK, SDI, and SDO lines are common to all devices. Transaction-qualification criteria remains in effect, and in

write mode the device executes the instructions present in the 32 bits of a qualified transaction. In read mode, the device returns the requested data through SDO during the read-mode transaction.

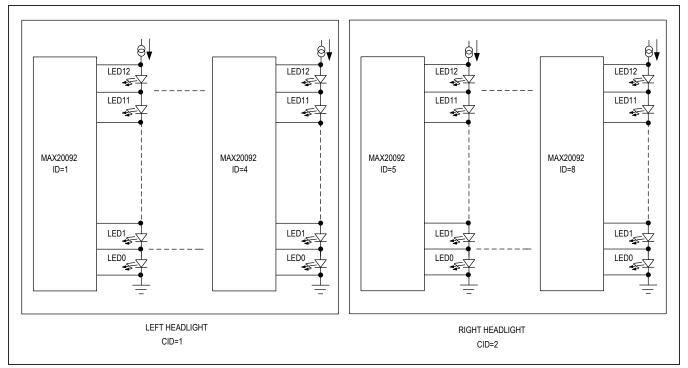

An example of a standard Star connection is shown in Figure 7.

Figure 7. Star Connections

#### **Device Identification Number**

Each device in the star connection is given a unique device ID number through hard-wiring pins ADDR2, ADDR1, and ADDR0. Each pin can be connected to

three different values ( $V_{DD}$ , GND, and SDI), for a total of 26 valid combinations. The combination of {GND, GND, GND} is reserved for a general-call ID and should not be used.

**Table 2. Device ID Mapping**

| ADDR2           | ADDR1           | ADDR0           | DEVICE_ID[4:0]                         |

|-----------------|-----------------|-----------------|----------------------------------------|

| GND             | GND             | GND             | Invalid, reserved for general-call ID. |

| GND             | GND             | SDI             | 00001                                  |

| GND             | GND             | V <sub>DD</sub> | 00010                                  |

| GND             | SDI             | GND             | 00011                                  |

| GND             | SDI             | SDI             | 00100                                  |

| GND             | SDI             | V <sub>DD</sub> | 00101                                  |

| GND             | V <sub>DD</sub> | GND             | 00110                                  |

| GND             | V <sub>DD</sub> | SDI             | 00111                                  |

| GND             | V <sub>DD</sub> | V <sub>DD</sub> | 01000                                  |

| SDI             | GND             | GND             | 01001                                  |

| SDI             | GND             | SDI             | 01010                                  |

| SDI             | GND             | V <sub>DD</sub> | 01011                                  |

| SDI             | SDI             | GND             | 01100                                  |

| SDI             | SDI             | SDI             | 01101                                  |

| SDI             | SDI             | V <sub>DD</sub> | 01110                                  |

| SDI             | V <sub>DD</sub> | GND             | 01111                                  |

| SDI             | $V_{DD}$        | SDI             | 10000                                  |

| SDI             | V <sub>DD</sub> | V <sub>DD</sub> | 10001                                  |

| $V_{DD}$        | GND             | GND             | 10010                                  |

| $V_{DD}$        | GND             | SDI             | 10011                                  |

| $V_{DD}$        | GND             | V <sub>DD</sub> | 10100                                  |

| $V_{DD}$        | SDI             | GND             | 10101                                  |

| $V_{DD}$        | SDI             | SDI             | 10110                                  |

| $V_{DD}$        | SDI             | V <sub>DD</sub> | 10111                                  |

| $V_{DD}$        | V <sub>DD</sub> | GND             | 11000                                  |

| V <sub>DD</sub> | V <sub>DD</sub> | SDI             | 11001                                  |

| $V_{DD}$        | V <sub>DD</sub> | $V_{DD}$        | 11010                                  |

#### Individual Call, Global Call, Cluster-Call Command

For the first 8 bits of the transaction, the master sends: {Read/write bit, CMD1, CMD0, ID4, ID3, ID2, ID1, ID0} Where CMD[1:0] is the Call-Type command. This field allows the master to access:

- A single device (individual call)

- Multiple devices (cluster call), or

- All devices (global call) on the shared SCSB line

#### Safety Pulldown Resistors

To guard against broken SPI connections, the IC includes internal safety terminations on all interface input ports. SCLK and SDI have internal pulldowns to GND. SCSB and RESETB (if present) have internal pullups to  $V_{DDIO}$ . All safety resistors are  $100k\Omega$  nominal.

The internal safety resistors can be individually enabled or disabled using SPI configuration bits (SFT\_CLK, SFT\_SDI, SFT\_SCSB) with a high state indicating the safety termination is enabled/engaged and a low state indicating it is disengaged. This allows the user to eliminate loading currents when the safety resistors are not needed.

#### **SPI Transactions**

#### **Write-Mode Transactions**

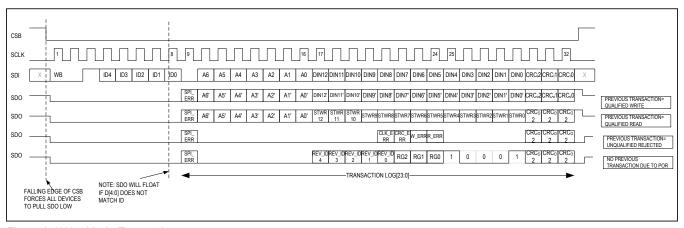

A properly constructed write-mode transaction is made up of 32-bit data frames. Each SDI data frame from the master (or the previous device in the chain) contains a R/WB bit, a 2-bit individual call command, a 5-bit device identification number, a 7-bit address, 13 bits of input data or instructions, and a 3-bit CRC. During a write-mode transaction, the device outputs data on the SDO line; both transaction log and repeated transaction data are transferred through SDO. The device only accepts and executes qualified SPI transactions based on the last 32 bits of data received. Details of write-mode transactions are explained below and summarized in Figure 8.

#### Write Bit - R/WB = 0 (DIN31):

Write-mode transactions are identified by R/WB = 0 in the MSB position of a 32-bit data frame.

# Individual Call Command - CMD[1:0] = 01 (DIN[30:29]):

Individual write transactions are identified by CMD[1:0] = 01 in the DIN[30:29] positions of the frame.

| Table 3. Call Type Command | Table 3 | . Call T | ype C | ommand |

|----------------------------|---------|----------|-------|--------|

|----------------------------|---------|----------|-------|--------|

| CMD1 | CMD0 | CALL TYPE         | DESCRIPTION                                       |

|------|------|-------------------|---------------------------------------------------|

| 0    | 0    | Invalid           | _                                                 |

| 0    | 1    | Individual        | One device accessed at a time                     |

| 1    | 0    | Global or Cluster | All or multiple devices accessed at the same time |

| 1    | 1    | Invalid           | _                                                 |

Figure 8. Write-Mode Transaction

#### Device ID - ID[4:0] (DIN[28:24]):

**Note:** After the 8th bit has been received (rising 8th SCLK edge), the selected slave continues to drive the SDO line with the contents of the transaction log for the remaining 24 bits. The other slaves release the SDO line such that only one slave is driving.

#### Address - A[6:0] (DIN[22:16]):

Write-mode transactions allow new information to be written to internal configuration registers within the device. The configuration register address to be written is indicated by A[6:0] within the data frame. In this format, up to 128 register addresses are supported (0\h thru 7F\h) for write-mode access.

Note: DIN23 must always be 0.

#### Input Data - DIN[12:0] (DIN[15:3]):

The next 13 bits of data in the 32-bit data frame represent data that will be written to the requested register, or describe internal operations to be executed.

#### SDI CRC Bit - CRCi[2:0] (DIN[2:0]):

Write-mode transactions are protected by a 3-bit cyclic redundancy check (CRC) on the SDI data frame. CRC is provided by the master on the last 3 bits on SDI.

CRC is calculated by applying the DIN[31:3] message (i.e., Address + Input Data) on polynomial 0x5 ( $x^3+ x^1+ x^0$ ) with a start value of binary 000.

The receiving device (slave) will calculate its own CRC using the same polynomial and starting value. The slave only accepts/executes the command if its own CRC matches the last 3 bits on SDI.

#### Output Data - DO[31:0] and LOG[23:0]:

During write-mode transactions, the device outputs data through the SDO line.

In write mode, the device pulls down SDO immediately following the falling edge of SCSB. The first 8 bits are always 0. The remaining 24 bits are the contents of the internal transaction log register (LOG[23:0]).

See the <u>Internal Transaction Log</u> section for a detailed explanation of content.

If further SCLK cycles are provided, SDO outputs 0 for the remainder of the transaction frame and CLK\_ERR is set. **Note:** This method also provides the  $\mu$ C an opportunity to check the SPI integrity, since the transaction log content of the previously qualified/executed transaction will be relayed back to the  $\mu$ C through SDO during each complete single or extended transaction.

#### Write-Mode Qualification Check (SPI\_ERR):

To qualify for write-mode execution, the following conditions must be met:

- SPI transaction must be exactly 32 bits in length (no CLK ERR recorded)

- SDI data frame CRC check must pass (no CRC\_ERR recorded)

- A[6:0] must select a valid write-accessible register or command (no W\_ERR recorded)

If the SPI transaction is qualified, the instruction is executed, any requested internal register contents are updated, and the Internal Transaction Log is updated to indicate the successful transaction.

If the SPI write transaction is not qualified, the instruction is not executed, the device's internal SPI\_ERR indicator and appropriate SPI diagnostic bit are set, and the Internal Transaction Log is updated to indicate the failed transaction. The SPI\_ERR bit is returned in response to later read and write-mode transactions, notifying the  $\mu C$  that the SPI interface may be compromised.

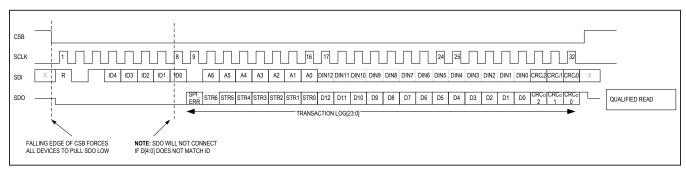

#### **Read-Mode Transactions:**

A properly constructed read-mode transaction is made up of 32-bit data frames. Each SDI data frame from the master contains a R/WB bit, a 2-bit Individual Call command, a 5-bit Device Identification number, a 7-bit address, 13 bits of data set to all zeros (000\h), and a 3-bit CRC.

During a read-mode transaction, the IC outputs data on the SDO line; the content of the SDO data frame is described in detail below. The MAX20092 only accepts qualified SPI transactions, based on the last 16 bits of data received. Details of read-mode transactions are explained below and summarized in Figure 9.

#### Read Bit - R/WB = 1 (DIN31):

Read-mode transactions are identified by R/WB = 1 in the MSB position of a 32-bit data frame.

# Individual Call Command - CMD[1:0] = 01 (DIN[30:29]):

Individual write transactions are identified by CMD[1:0] = 01 in the DIN[30:29] positions of the frame.

#### Device ID - ID[4:0] (DIN[28:24]):

**Note:** After the 8th bit has been received (rising 8th SCLK edge), the selected slave continues to drive the SDO line with the contents of the transaction log for the remaining 24 bits. The other slaves release the SDO line such that only one slave is driving.

#### Address - A[6:0] (DIN[22:16]):

Read-mode transactions allow new information to be read from internal registers within the device. The register address to be read back is indicated by A[6:0] within the data frame. In this format, up to 128 register addresses are supported (00\h thru 7F\h) for read-mode access. **Note:** DIN23 must always be 0.

#### Input Data - DIN[12:0] (DIN[15:3]):

The 13-bit input data in a read mode must be set to zero (000\h).

#### SDI CRC Bit - CRCi[2:0] (DIN[2:0]):

Read-mode transactions are protected by a 3-bit cyclic redundancy check (CRC) on the SDI data frame. CRC is provided by the master on the last 3 bits on SDI.

CRC is calculated by applying the DIN[31:3] message (i.e., Address + Input Data) on polynomial 0x5 ( $x^3 + x^1 + x^0$ ) with a start value of binary 000.

The receiving device (slave) calculates its own CRC using the same polynomial and starting value. The slave only accepts/executes the command if its own CRC matches the last 3 bits on SDI.

# Output Data - Current Status[6:0]+Data Requested[13:0]:

In a read operation, the device pulls down SDO immediately following the falling edge of SCSB. **Note:** The first 8 bits of the transaction are always 0.

The device then relays the SPI\_ERR status, up to 7 bits of general-status data (STR[6:0]), the 13 bits of data requested by A[6:0], and a calculated 3-bit CRC in direct response to an incoming read-mode transaction.

If further SCLK cycles are provided, SDO outputs 0 for the remainder of the transaction frame and CLK\_ERR is set.

#### SDO CRC Bits - CRCo[2:0] (DO[2:0]):

Read-mode transactions are protected by a 3-bit cyclic redundancy check (CRC) on the SDO data frame. CRC is provided by the slave on the last 3 bits on SDO.

CRC is calculated by applying the message DO[23:3] (i.e., ST + Data Requested) on polynomial 0x5 ( $x^3 + x^1 + x^0$ ) with a start value of binary 000.

The receiving device (master) calculates its own CRC using the same polynomial and starting value. The master only accepts/executes the command if its own CRC matches the last 3 bits on SDO.

#### Read-Mode Qualification Check (SPI\_ERR):

To qualify for read-mode execution, the following conditions must be met:

- SPI transaction must be exactly 32 bits in length (no CLK\_ERR recorded)

- SDI data frame CRC check must pass (no CRC ERR recorded)

- DIN[12:0] must be all zeros (no R ERR recorded)

- Individual call command CMD==01 received (no R\_ERR recorder)

If the SPI read transaction is qualified, any clear-on-read internal register contents are updated, and the Internal Transaction Log updated with the content requested by the successful transaction.

Figure 9. Read-Mode Transaction

If the SPI read transaction is not qualified, clear-on-read internal register contents are not updated, the device's internal SPI\_ERR indicator and appropriate SPI diagnostic bit are set, and the Internal Transaction Log updated to indicate the failed transaction. This SPI\_ERR bit is returned in response to later read- and write-mode transactions, notifying the  $\mu C$  that the SPI may be compromised.

**Note:** The output data is always driven onto SDO, regardless of whether the read transaction is qualified or not.

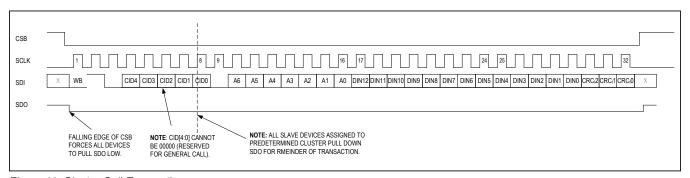

#### **General-Call Transactions:**

A general-call transaction is an extension of the write transaction (see Figure 10).

In large LED arrays where multiple MAX20092 devices are used, execute the same command across all devices to save time. For example, the master must have the ability set all LED1's PWM duty cycle to 50% for all 26 devices with a single 32-bit transaction.

**Note:** Only write transactions are legal for general-call transactions.

#### Write Bit - R/WB = 0 (DIN31):

Only write-mode transactions are legal. Write-mode transactions are identified by R/WB = 0 in the MSB position of a 32-bit data frame.

# General-Call Command - CMD[1:0] = 10 (DIN[30:29]):

General-call transactions are identified by CMD[1:0] = 10 in the DIN[30:29] positions of the frame.

#### Device ID - ID[4:0] = 00000 (DIN[28:24])

**Note:** After the 8th bit has been received (8th rising SCLK edge), all slave devices pull down SDO for the remainder of the transaction.

#### Address - A[6:0] (DIN[22:16]):

General-call transactions allow new information to be written to internal configuration registers within the device.

The configuration register address to be written is indicated by A[6:0] within the data frame. In this format, up to 128 register addresses are supported (0\h thru 7F\h) for write-mode access.**Note:** DIN23 must always be 0.

#### Input Data - DIN[12:0] (DIN[15:3]):

The next 13 bits of data in the 32-bit data frame represent data that will be written to the requested register, or describe the internal operations to be executed.

#### SDI CRC Bit - CRCi[2:0] (DIN[2:0]):