#### MAX20330

# Programmable OVP Controller with VBUS Short Detection

#### **General Description**

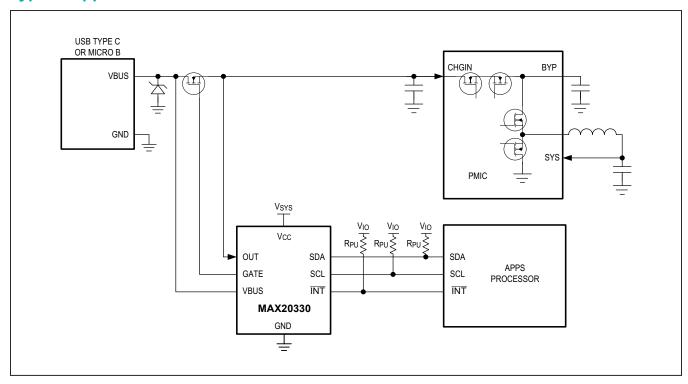

The MAX20330 is an overvoltage controller with the VBUS impedance detection function. The device drives an external low  $R_{ON}$  path for the device that requires a flexible and adjustable OVLO threshold. The VBUS impedance detection can detect the soft short on VBUS and warn the user about the potential connector overheating.

The MAX20330 is designed to drive a single or dual back-to-back external N-channel MOSFET with a low  $R_{ON}$  (10m $\Omega$  max). An external TVS can be used to protect the device from a high energy surge if necessary.

The device is available in an 8-bump (0.35mm pitch, 1.77mm x 1.03mm) wafer-level package (WLP) and operate over the -40°C to +85°C extended temperature range.

### **Applications**

- Smart Phones

- Tablets

- Phablets

- Desktops

#### **Benefits and Features**

- Protects High-Power Portable Devices

- Wide Operating Input Voltage Protection Range: 2.7V to 36V

- Ultra-Fast Turn-Off Time: 100nsec

- · Built-In Charge Pump to Drive External N-MOSFET

- Flexible Overvoltage Protection Design

- I<sup>2</sup>C Adjustable Overvoltage Protection Trip Level

- Wide Adjustable OVLO Threshold Range from 4V to 24V (168 steps)

- Preset Internal Accurate OVLO Thresholds: 6.8V±2%

- Additional Protection Features Increase System Reliability

- · VBUS Short Detection

- · Soft-Start to Minimize In-Rush Current

- · Internal 15ms Startup Debounce

- · Thermal Shutdown Protection

- Space-Saving

- 8 Bump 0.35mm Pitch 1.77mm x 1.03mm WLP

Ordering Information appears at end of data sheet.

### **Absolute Maximum Ratings**

| (All voltages referenced to GND.)                | Continuous Power Dissipation (T <sub>A</sub> = +70°C) |

|--------------------------------------------------|-------------------------------------------------------|

| VBUS to GND (Note 1)0.3V to +40V                 | WLP (derate 10.9mW/°C above +70°C)872mW               |

| GATE to GND0.3V to min (VBUS + 0.3V, 40V)        | Operating Temperature Range40°C to +85°C              |

| OUT to GND0.3V to min (GATE + 0.3V, 40V)         | Junction Temperature+150°C                            |

| GATE to OUT0.3V to +6V                           | Storage Temperature Range65°C to +150°C               |

| SDA, SCL, INT, V <sub>CC</sub> to GND0.3V to +6V | Soldering Temperature (reflow)+260°C                  |

| Continuous Current into all pins±0.1A            |                                                       |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note 1: The external TVS clamp voltage should be below the abs max of MAX20330.

### **Package Information**

| PACKAGE TYPE: 8 WLP                    |                                |

|----------------------------------------|--------------------------------|

| Package Code                           | W81B1+1                        |

| Outline Number                         | 21-100229                      |

| Land Pattern Number                    | Refer to Application Note 1891 |

| THERMAL RESISTANCE, FOUR-LAYER BOARD   |                                |

| Junction to Ambient (θ <sub>JA</sub> ) | 91.72°C/W                      |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

(V<sub>BUS</sub> = 2.7V to 36V, V<sub>CC</sub> = 2.6V to 5.5V,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at V<sub>CC</sub> = 3.3V,  $T_A$  = +25°C) (Note 2)

| PARAMETER                               | SYMBOL              | CONDITIONS                         | MIN | TYP              | MAX  | UNITS |

|-----------------------------------------|---------------------|------------------------------------|-----|------------------|------|-------|

| VBUS                                    |                     |                                    |     |                  |      |       |

| VBUS Startup Voltage                    | V <sub>BUS_ST</sub> |                                    |     | 2.7              | 2.75 | V     |

| VBUS Supply Current                     | I <sub>VBUS</sub>   | $V_{BUS} = 4.2V$ , $I_{OUT} = 0mA$ |     | 250              | 400  | μA    |

| VBUS Pull Down Resistor                 | R <sub>PD</sub>     | Enabled by I <sup>2</sup> C        | 0.5 | 1                | 2    | kΩ    |

| OUT PROGRAMMABLE PRO                    | OTECTION            |                                    |     |                  |      |       |

| VBUS OVLO Range                         |                     | Shutdown                           | 4   |                  | 24   | V     |

| Internal Overvoltage Trip<br>Level      | V <sub>OVLO_R</sub> | VBUS rising                        | -2  | Progra<br>mmable | +2   | %     |

| Internal Overvoltage Trip<br>Hysteresis | V <sub>OVLO_F</sub> | VBUS falling                       |     | 0.2              |      | %     |

|                                         |                     | 4V – 8V [63]                       |     | 63.5             |      |       |

| VBUS OVLO Resolution                    |                     | 8V – 16V [63]                      |     | 127              |      | mV    |

|                                         |                     | 12V – 24V [63]                     |     | 190.5            |      |       |

## **Electrical Characteristics (continued)**

$(V_{BUS} = 2.7V \text{ to } 36V, V_{CC} = 2.6V \text{ to } 5.5V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = 3.3V, T_A = +25^{\circ}\text{C})$  (Note 2)

| PARAMETER                        | SYMBOL                | CONE                                        | MIN                  | TYP  | MAX         | UNITS |     |

|----------------------------------|-----------------------|---------------------------------------------|----------------------|------|-------------|-------|-----|

| V <sub>CC</sub>                  | •                     |                                             |                      |      |             |       |     |

| V <sub>CC</sub> Voltage Range    | V <sub>CC</sub>       |                                             |                      | 2.6  | 3.3         | 5.5   | V   |

| V <sub>CC</sub> Supply Current   | l <sub>vcc</sub>      | $V_{CC}$ = 4.2V, manual ( $I_{SRC}$ = 0mA)  |                      | 125  | 200         | μA    |     |

| V <sub>CC</sub> Shutdown Current |                       | V <sub>CC</sub> = 4.2V, VBUS 1              | floating, ENb = 1    |      | 2.8         | 5     | μA  |

| GATE                             |                       |                                             |                      |      |             |       |     |

|                                  |                       | CATE external                               |                      | m    | in (VBUS, 5 | SV)   |     |

| Maximum Gate On Voltage          | $V_{GON}$             | GATE external leakage <1µA                  | VBUS = 2.75V         | 2.43 |             |       | V   |

|                                  |                       |                                             | VBUS = 5V, 23V       | 4.6  | -           | 5.4   |     |

| Gate Off                         | V <sub>GOFF</sub>     |                                             |                      |      |             | 0.5   | V   |

| Soft-Start Comparator            | V <sub>SS_THR</sub>   |                                             |                      | 220  | 300         | 380   | mV  |

| ID CURRENT SOURCE                |                       |                                             |                      |      |             |       |     |

| Current Source Accuracy          |                       |                                             |                      | -5   |             | +5    | %   |

| Current Source Open<br>Voltage   | V <sub>OVSO</sub>     | I <sub>ID</sub> = 2μΑ                       |                      |      |             | 2     | V   |

|                                  |                       |                                             |                      |      | 2           |       |     |

| Current Source                   |                       |                                             |                      |      | 6           |       |     |

|                                  |                       |                                             |                      |      | 18          |       | 1   |

|                                  | I <sub>ID</sub>       |                                             |                      |      | 54          |       | μA  |

|                                  |                       |                                             |                      |      | 162         |       | 1   |

|                                  |                       |                                             |                      |      | 2500        |       |     |

| Average Current Source           | I <sub>ID_AVG</sub>   | 162µA max current<br>ISRC_MAN = 0           | :, IS_PERIOD ≥ 130x, |      |             | 2     | μΑ  |

| ADC                              | 1                     | 1                                           |                      |      |             |       |     |

| Resolution                       |                       |                                             |                      |      | 8           |       | bit |

| Voltage step                     |                       |                                             |                      |      | 5.9         |       | mV  |

| Full-Scale Error                 |                       |                                             |                      | -2   |             | +2    | %   |

| Noise Filtering                  |                       |                                             |                      |      | 100         |       | μs  |

| Full Scale                       |                       |                                             |                      |      | 1.5         |       | V   |

| DIGITAL SIGNALS (SDA, SO         | CL, INT)              | •                                           |                      |      |             |       | 1   |

| Output Low Voltage               | V <sub>OL</sub>       | V <sub>IO</sub> = 3.3V, I <sub>SINK</sub> = | : 3mA                |      |             | 0.4   | V   |

| Leakage Current                  |                       | V <sub>IO</sub> = 2.6V, open-d              |                      |      |             | 1     | μA  |

| Input Logic-High                 | V <sub>IH</sub>       |                                             |                      | 1.3  |             |       | V   |

| Input Logic-Low                  | V <sub>IL</sub>       |                                             |                      |      |             | 0.4   | V   |

| Input Leakage Current            | I <sub>BUS_LEAK</sub> | V <sub>IN</sub> = 0V, V <sub>IN</sub> = 2.6 | SV .                 | -1   |             | +1    | μA  |

### **Electrical Characteristics (continued)**

$(V_{BUS} = 2.7V \text{ to } 36V, V_{CC} = 2.6V \text{ to } 5.5V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = 3.3V, T_A = +25^{\circ}\text{C}$ ) (Note 2)

| PARAMETER                                   | SYMBOL           | CONDITIONS                                                                                                  | MIN | TYP              | MAX | UNITS |  |  |  |  |

|---------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------|-----|------------------|-----|-------|--|--|--|--|

| TIMING CHARACTERISTICS                      |                  |                                                                                                             |     |                  |     |       |  |  |  |  |

| VBUS Debounce Time                          | t <sub>DEB</sub> | VBUS = 4.3V to charge pump on (OUT = 10% of VBUS), $R_{LOAD}$ = 100Ω, $C_{LOAD}$ = 10μF                     |     | Progra<br>mmable |     | ms    |  |  |  |  |

| VBUS Soft-Start Time                        | t <sub>SS</sub>  | IGATE = 4μA (typ)                                                                                           |     | 50               |     | ms    |  |  |  |  |

| VBUS Fast OVP Turn Off<br>Response Time     | tOFF             | From VBUS > V <sub>OVLO_R</sub> to<br>V <sub>GATE_TO_SOURCE</sub> = 0.5V,<br>C <sub>GATE_TO_OUT</sub> = 4nF |     | 100              |     | ns    |  |  |  |  |

| Programmable Time<br>Accuracy               |                  |                                                                                                             | -10 |                  | +10 | %     |  |  |  |  |

| I <sup>2</sup> C Maximum Clock<br>Frequency |                  |                                                                                                             |     | 400              |     | kHz   |  |  |  |  |

| THERMAL PROTECTION                          |                  |                                                                                                             |     |                  |     |       |  |  |  |  |

| Thermal Shutdown                            |                  |                                                                                                             |     | 125              |     | °C    |  |  |  |  |

| Thermal Shutdown<br>Hysteresis              |                  |                                                                                                             |     | 20               |     | °C    |  |  |  |  |

**Note 2:** All devices are 100% production tested at T<sub>A</sub> = +25°C. Specifications over the operating temperature range are guaranteed by design.

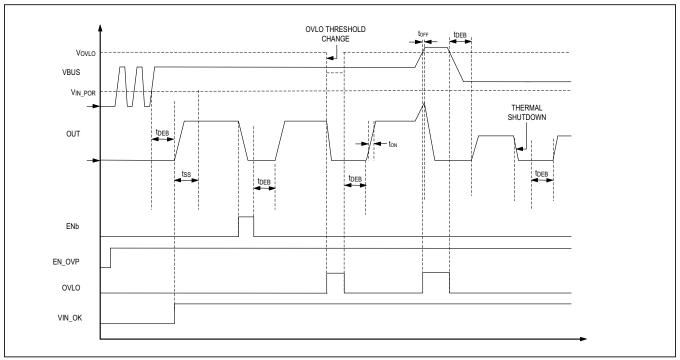

Figure 1. Timing Diagram

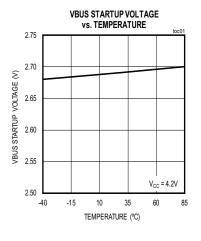

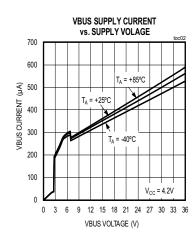

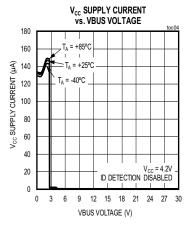

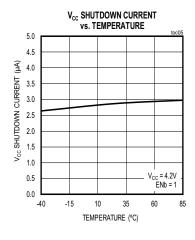

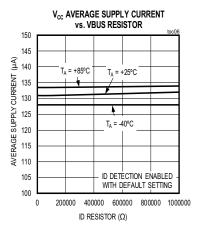

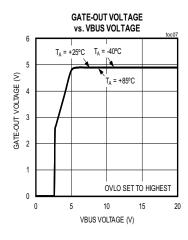

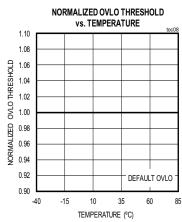

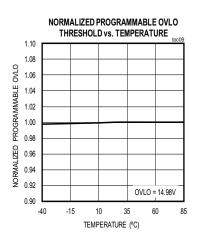

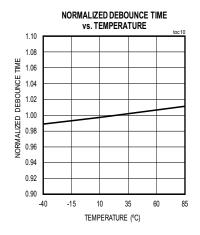

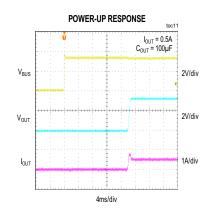

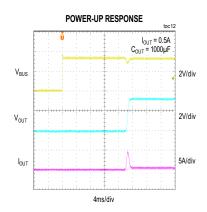

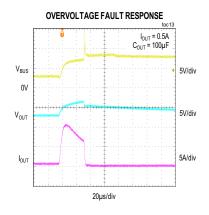

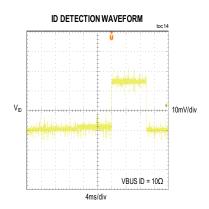

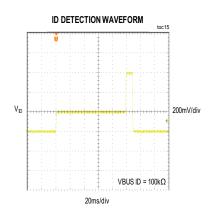

### **Typical Operating Characteristics**

$(V_{CC} = 4.2V, T_A = +25^{\circ}C, unless otherwise noted.)$

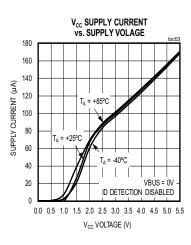

## **Typical Operating Characteristics (continued)**

( $V_{CC}$  = 4.2V,  $T_A$  = +25°C, unless otherwise noted.)

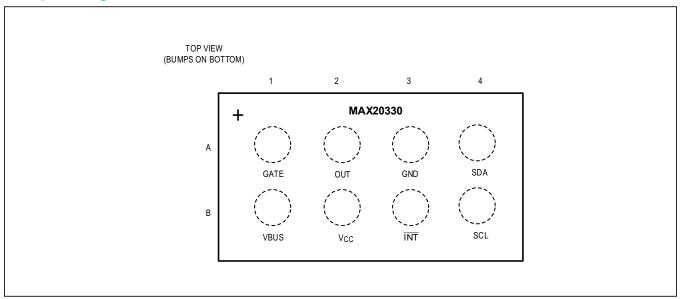

## **Bump Configuration**

## **Bump Description**

| BUMP | NAME            | FUNCTION                                                                                                                       |

|------|-----------------|--------------------------------------------------------------------------------------------------------------------------------|

| A1   | GATE            | Gate Drive Output for External N-FET                                                                                           |

| A2   | OUT             | Output Voltage to the Battery Terminal. Output of internal switch.                                                             |

| А3   | GND             | Ground                                                                                                                         |

| A4   | SDA             | I <sup>2</sup> C Data Line. Connect SDA to an external pullup resistor.                                                        |

| B1   | VBUS            | VBUS Input. For proper ESD and surge protection, place the external TVS and a 0.1µF capacitor on VBUS.                         |

| B2   | V <sub>CC</sub> | Supply for the $I^2C$ Digital Block. Bypass $V_{CC}$ to ground with a $0.1\mu F$ capacitor as close to the device as possible. |

| В3   | ĪNT             | Interrupt Output.                                                                                                              |

| B4   | SCL             | I <sup>2</sup> C Clock. Connect SCL to an external pullup resistor.                                                            |

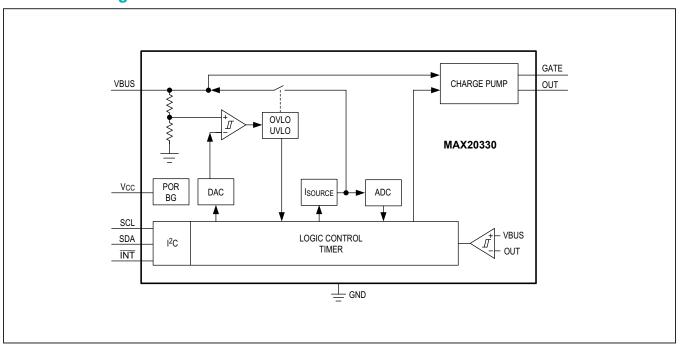

## **Functional Diagram**

**Table 1. Register Map**

| ADDRESS | NAME       | TYPE          | DEFAULT | DESCRIPTION                   |

|---------|------------|---------------|---------|-------------------------------|

| 0x00    | CHIP ID    | Read Only     | 0x00    | Device ID Register            |

| 0x01    | CONTROL 1  | RW            | 0x88    | System Control 1              |

| 0x02    | STATUS     | Read Only     | 0x00    | Status Register               |

| 0x03    | INTERRUPT  | Clear on Read | 0x00    | Interrupt Register            |

| 0x04    | MASK       | RW            | 0xFF    | Mask Register                 |

| 0x05    | SET_OVLO   | RW            | 0x2C    | OVLO Threshold                |

| 0x06    | I_SRC      | RW            | 0x01    | Current Source Threshold      |

| 0x07    | I_SRC_TMR  | RW            | 0x1B    | Current Source On-Timer       |

| 0x08    | CONTROL 2  | RW            | 0x3C    | System Control 2              |

| 0x0A    | ACCDET_REF | RW            | 0xF0    | Accessory Detection Threshold |

| 0x0B    | ISRC_ADC   | Read Only     | 0x00    | Current Source Output         |

| 0x0C    | VBUS_ADC   | Read Only     | 0x00    | Current Source Output         |

## **Table 2. Detailed Register Map**

| CHIP ID 0X00 (READ ON  | LY)           |                                                                                                                                                                          |                                                 |              | ,             |                |     |     |  |

|------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--------------|---------------|----------------|-----|-----|--|

| BIT                    | 7             | 6                                                                                                                                                                        | 5                                               | 4            | 3             | 2              | 1   | 0   |  |

| BIT NAME               |               | CHIP_ID CHIP_REV                                                                                                                                                         |                                                 |              |               |                |     |     |  |

| Reset Value            | 0             | 0                                                                                                                                                                        | 0                                               | 0            | 0             | 0              | 0   | 0   |  |

| Description            | Chip ID and   | Revision                                                                                                                                                                 |                                                 |              |               |                |     |     |  |

| CONTROL 1 0x01 (Read/V | Vrite)        |                                                                                                                                                                          |                                                 |              |               |                |     |     |  |

| BIT                    | 7             | 6                                                                                                                                                                        | 5                                               | 4            | 3             | 2              | 1   | 0   |  |

| BIT NAME               | EN_OVP        | EN_IS                                                                                                                                                                    | RFU                                             | VBUS         | S_DET         | VBUSADC<br>_EN | RFU | ENb |  |

| Reset Value MAX20330   | 1             | 0                                                                                                                                                                        | 0                                               | 0            | 1             | 0              | 0   | 0   |  |

| Reset Value MAX20330B  | 0             | 0                                                                                                                                                                        | 0                                               | 0            | 1             | 0              | 0   | 0   |  |

| EN_OVP                 | 0 = OVP dis   | sabled (MAX2                                                                                                                                                             | ind EN_IS cai<br>20330B defau<br>20330 default) | lt)          | it the same t | ime)           |     |     |  |

| EN_IS                  |               | irce (I_SRC)<br>disabled (defa<br>enabled                                                                                                                                |                                                 |              |               |                |     |     |  |

| RFU                    | Reserved for  | r future use                                                                                                                                                             |                                                 |              |               |                |     |     |  |

| VBUS_DET               |               | ounce Time (t<br>min time for<br>default)                                                                                                                                |                                                 |              |               |                |     |     |  |

| VBUSADC_EN             | one time AD   | One Time ADC for VBUS. The bit is cleared after the measurement. EN_OVP = 1 is required to run one time ADC for VBUS.  0 = VBUS ADC is disabled  1 = VBUS ADC is enabled |                                                 |              |               |                |     |     |  |

| ENb                    | 0 = device is | ve Low Enab<br>s in active mo<br>s in sleep mo                                                                                                                           | , ,                                             | BUS rising e | dge.          |                |     |     |  |

**Table 2. Detailed Register Map (continued)**

| STATUS 0x02 (Read Only | )                                                                               |                                          |       |        |             |                |              |      |

|------------------------|---------------------------------------------------------------------------------|------------------------------------------|-------|--------|-------------|----------------|--------------|------|

| BIT                    | 7                                                                               | 6                                        | 5     | 4      | 3           | 2              | 1            | 0    |

| BIT NAME               | VIN_OK                                                                          | RFU                                      | EOC   | TP_OUT | ACC_<br>DET | THERM_<br>SHDN | OUT_<br>SHRT | OVLO |

| Reset Value            | 0                                                                               | 0                                        | 0     | 0      | 0           | 0              | 0            | 0    |

| VIN_OK                 | 0 = VBUS is                                                                     | is above 2.7<br>below 2.7V<br>above 2.7V | (typ) |        |             |                |              |      |

| RFU                    | Reserved for                                                                    | r future use                             |       |        |             |                |              |      |

| EOC                    | 0 = no conv                                                                     | Conversion ersion since C data since     |       |        |             |                |              |      |

| TP_OUT                 | Timer Period 0 = timer period 1 = timer period                                  | riod not expi                            | red   |        |             |                |              |      |

| ACC_DET                | Accessory [<br>0 = no chan<br>1 = accesso                                       |                                          | tus   |        |             |                |              |      |

| THERM_SHDN             | Thermal Sh<br>0 = no therm<br>1 = thermal                                       | nal shutdown                             |       |        |             |                |              |      |

| OUT_SHRT               | OUT does not reach 90% of VBUS within Soft Start Time 0 = OUT ok 1 = OUT not ok |                                          |       |        |             |                |              |      |

| OVLO                   | Overvoltage Shutdown 0 = no OVP shutdown 1 = OVP shutdown                       |                                          |       |        |             |                |              |      |

## **Table 2. Detailed Register Map (continued)**

| INTERRUPT 0x03 (CI | ear on Read)                                  |                                                                                                                   |                |         |              |                 |               |       |

|--------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------|---------|--------------|-----------------|---------------|-------|

| BIT                | 7                                             | 6                                                                                                                 | 5              | 4       | 3            | 2               | 1             | 0     |

| BIT NAME           | VIN_OKi                                       | RFU                                                                                                               | EOCi           | TP_OUTi | ACC_<br>DETi | THERM_<br>SHDNi | OUT_<br>SHRTi | OVLOi |

| Reset Value        | 0                                             | 0                                                                                                                 | 0              | 0       | 0            | 0               | 0             | 0     |

| VIN_OKi            | VIN (VBUS)<br>0 = interrupt<br>1 = interrupt  | not occurre                                                                                                       | V (typ) interi | -upt    |              |                 |               |       |

| RFU                | Reserved fo                                   | r future use                                                                                                      |                |         |              |                 |               |       |

| EOCi               | ADC EOC ir<br>0 = interrupt<br>1 = interrupt  | not occurre                                                                                                       | d              |         |              |                 |               |       |

| TP_OUTi            | Timer Period 0 = interrupt 1 = interrupt      | not occurre                                                                                                       |                |         |              |                 |               |       |

| ACC_DETi           | Accessory D 0 = interrupt 1 = interrupt       | not occurre                                                                                                       |                |         |              |                 |               |       |

| THERM_SHDNi        | Thermal Sho<br>0 = interrupt<br>1 = interrupt | not occurre                                                                                                       |                |         |              |                 |               |       |

| OUT_SHRTi          | 0 = interrupt                                 | OUT does not reach 90% of VBUS within soft-start time interrupt 0 = interrupt not occurred 1 = interrupt occurred |                |         |              |                 |               |       |

| OVLOi              | 0 = interrupt                                 | Overvoltage shutdown interrupt 0 = interrupt not occurred 1 = interrupt occurred                                  |                |         |              |                 |               |       |

**Table 2. Detailed Register Map (continued)**

| MASK 0x04 (Read/Wr | ite)                                                     |                                                                                                                                                                                                                                              |              |                 |               |                 |               |       |  |  |

|--------------------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------|---------------|-----------------|---------------|-------|--|--|

| BIT                | 7                                                        | 6                                                                                                                                                                                                                                            | 5            | 4               | 3             | 2               | 1             | 0     |  |  |

| BIT NAME           | VIN_OKm                                                  | RFU                                                                                                                                                                                                                                          | EOCm         | TP_<br>OUTm     | ACC_<br>DETm  | THERM_<br>SHDNm | OUT_<br>SHRTm | OVLOm |  |  |

| Reset Value        | 1                                                        | 1                                                                                                                                                                                                                                            | 1            | 1               | 1             | 1               | 1             | 1     |  |  |

| VIN_OKm            | , , ,                                                    | VIN (VBUS) is above 2.7V (typ) interrupt 0 = not masked 1 = masked                                                                                                                                                                           |              |                 |               |                 |               |       |  |  |

| RFU                | Reserved for                                             | future use                                                                                                                                                                                                                                   |              |                 |               |                 |               |       |  |  |

| EOCm               | ADC EOC in<br>0 = not mask<br>1 = masked                 |                                                                                                                                                                                                                                              |              |                 |               |                 |               |       |  |  |

| TP_OUTm            | Timer Period<br>0 = not mask<br>1 = masked               |                                                                                                                                                                                                                                              | upt          |                 |               |                 |               |       |  |  |

| ACC_DETm           | Accessory D<br>0 = not mask<br>1 = masked                |                                                                                                                                                                                                                                              | errupt       |                 |               |                 |               |       |  |  |

| THERM_SHDNm        | Thermal Shu<br>0 = not mask<br>1 = masked                |                                                                                                                                                                                                                                              | rupt         |                 |               |                 |               |       |  |  |

| OUT_SHRTm          | OUT does no<br>0 = not mask<br>1 = masked                |                                                                                                                                                                                                                                              | % of VBUS wi | thin soft start | time interrup | t               |               |       |  |  |

| OVLOm              | Overvoltage<br>0 = not mask<br>1 = masked                |                                                                                                                                                                                                                                              | nterrupt     |                 |               |                 |               |       |  |  |

| SET_OVLO 0x05 (Rea | d/Write)                                                 |                                                                                                                                                                                                                                              |              |                 |               |                 |               |       |  |  |

| BIT                | 7                                                        | 6                                                                                                                                                                                                                                            | 5            | 4               | 3             | 2               | 1             | 0     |  |  |

| BIT NAME           |                                                          |                                                                                                                                                                                                                                              |              | SET_            | OVLO          |                 |               |       |  |  |

| Reset Value        | 0                                                        | 0                                                                                                                                                                                                                                            | 1            | 0               | 1             | 1               | 0             | 0     |  |  |

| SET_OVLO           | 0000,0000 -<br>0100,0000 -<br>1000,0000 -<br>1100,0000 - | OVLO Threshold Set (8 bit resolution) 0000,0000 – 0011, 1111: 4V-8V [63 steps] (1.59% resolution) 0100,0000 – 0111,1111: 8V-16V [63 steps] 1000,0000 – 1011,1111: 12V-24V [63 steps] 1100,0000 – 1111,1111: 12V-24V [63 steps] Default: 6.8V |              |                 |               |                 |               |       |  |  |

**Table 2. Detailed Register Map (continued)**

| I_SRC 0x06 (Read/W       | /rite)                                                                                                                              |                                                           |                                   | r                              |                                   |               |                                                           |             |  |  |  |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------|--------------------------------|-----------------------------------|---------------|-----------------------------------------------------------|-------------|--|--|--|--|

| BIT                      | 7                                                                                                                                   | 6                                                         | 5                                 | 4                              | 3                                 | 2             | 1                                                         | 0           |  |  |  |  |

| BIT NAME                 | RFU                                                                                                                                 | RFU I_SRC_MON RFU I_SRC_SET                               |                                   |                                |                                   |               |                                                           |             |  |  |  |  |

| Reset Value              | 0                                                                                                                                   | 0                                                         | 0                                 | 0                              | 0                                 | 0             | 0                                                         | 1           |  |  |  |  |

| RFU                      | Reserved for future use.                                                                                                            |                                                           |                                   |                                |                                   |               |                                                           |             |  |  |  |  |

| I_SRC_MON<br>(Read Only) | 110 = 2500µ                                                                                                                         | $000 = off$ $001 = 2\mu A$ $010 = 6\mu A$ $011 = 18\mu A$ |                                   |                                |                                   |               |                                                           |             |  |  |  |  |

| I_SRC_SET                |                                                                                                                                     | e, it is the rode, it is the refault)                     | naximum curre<br>ne fixed current |                                |                                   | alue, the au  | uto ID detection                                          | is skipped. |  |  |  |  |

| I_SRC_TMR 0x07 (R        | ead/Write)                                                                                                                          |                                                           |                                   |                                |                                   |               |                                                           |             |  |  |  |  |

| BIT                      | 7                                                                                                                                   | 6                                                         | 5                                 | 4                              | 3                                 | 2             | 1                                                         | 0           |  |  |  |  |

| BIT NAME                 | RF                                                                                                                                  | J                                                         | IS_PE                             | RIOD                           | IS_INIT_SET                       |               | IS_TDET                                                   |             |  |  |  |  |

| Reset Value              | 0                                                                                                                                   | 0                                                         | 0                                 | 1                              | 1                                 | 0             | 1                                                         | 1           |  |  |  |  |

| RFU                      | Reserved for                                                                                                                        | future use                                                | Э.                                |                                |                                   |               |                                                           |             |  |  |  |  |

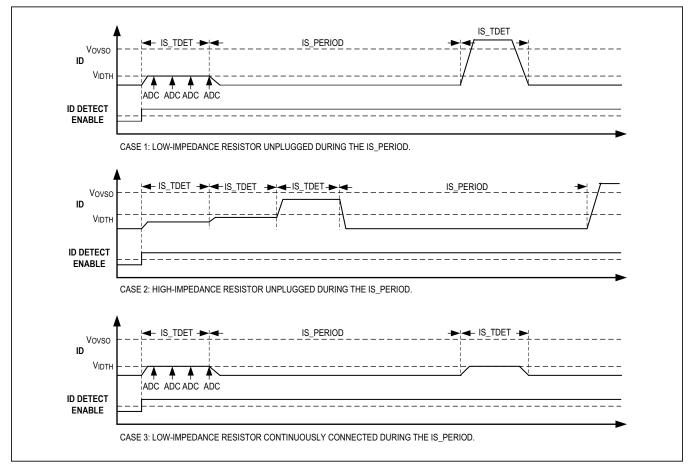

| IS_PERIOD                | Repeat period<br>00 = 4x<br>01 = 130x (d<br>10 = 250x<br>11 = 1600x                                                                 |                                                           | od                                |                                |                                   |               |                                                           |             |  |  |  |  |

| IS_INIT_SET              | 0 = use IS_PI<br>1 = use IS_PI                                                                                                      | ERIOD and<br>ERIOD = 00                                   | IS_TDET for th<br>O and IS_TDET   | e initial chec<br>= 101 as the | k (2µA)<br>e initial value. If th | ne current so | ction auto-mode<br>ource needs to in<br>a larger than 2µA | crease,     |  |  |  |  |

| IS_TDET                  | Current sour<br>000 = 2500µ<br>001 = 3500µ<br>010 = 4000µ<br>011 = 10000<br>100 = 40000<br>101 = 10000<br>110 = 40000<br>111 = 1sec | s<br>s<br>s<br>us (default<br>µs<br>0µs                   | for detection                     |                                |                                   |               |                                                           |             |  |  |  |  |

**Table 2. Detailed Register Map (continued)**

| CONTROL2 0x08 (Read | d/Write)                               |                                                                                                                                                                                                          |      |       |        |        |              |         |

|---------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------|--------|--------------|---------|

| BIT                 | 7                                      | 6                                                                                                                                                                                                        | 5    | 4     | 3      | 2      | 1            | 0       |

| BIT NAME            | RFU                                    | EN_<br>VBPD                                                                                                                                                                                              | VBPD | _TMR  | AUT_IS | RC_SCL | ISRC_<br>MAN | ISRC_ST |

| Reset Value         | 0                                      | 0                                                                                                                                                                                                        | 1    | 1     | 1      | 1      | 0            | 0       |

| RFU                 | Reserved for                           | Reserved for future use.                                                                                                                                                                                 |      |       |        |        |              |         |

| EN_VBPD             | 0 = pull dov                           | $1k\Omega$ VBUS pulldown enable bit. The bit is cleared after pull down time expires.<br>0 = pull down disabled (default)<br>1 = pull down enabled                                                       |      |       |        |        |              |         |

| VBPD_TMR            | 00 = 5ms<br>01 = 15ms<br>10 = 30ms     | 01 = 15ms                                                                                                                                                                                                |      |       |        |        |              |         |

| AUT_ISRC_SCL        | 00 = 10% o<br>01 = 20% o<br>10 = 30% o | Automatic scaling for impedance detection reference 00 = 10% of full ADC scale 01 = 20% of full ADC scale 10 = 30% of full ADC scale 11 = 30% of full ADC scale (default)                                |      |       |        |        |              |         |

| ISRC_MAN            | 0 = automa<br>1 = manual               | Current source manual detection 0 = automatic scaling for detection when ENb = 0 (default) 1 = manual detection when ENb = 0, fixed based on I_SRC and ISRC_TMR register values (register 0x06 and 0x07) |      |       |        |        |              |         |

| ISRC_ST             | 0 = disable                            | Current source manual start and ADC conversion. The bit is cleared after one impedance detection.  0 = disable (default)  1 = start one manual impedance detection                                       |      |       |        |        |              |         |

| ACCDET_REF 0x0A (R  | ead/Write)                             |                                                                                                                                                                                                          |      |       |        |        |              |         |

| BIT                 | 7                                      | 6                                                                                                                                                                                                        | 5    | 4     | 3      | 2      | 1            | 0       |

| BIT NAME            |                                        |                                                                                                                                                                                                          |      | ACC_D | ET_TH  |        |              |         |

| Reset Value         | 1                                      | 1                                                                                                                                                                                                        | 1    | 1     | 0      | 0      | 0            | 0       |

| ACC_DET_TH          |                                        | Accessory Detection Threshold Accessory is detected (ACC_DET = 1) if ADC_1 (0x0B) final reading is lower than ACC_DET_TH                                                                                 |      |       |        |        |              |         |

**Table 2. Detailed Register Map (continued)**

| ISRC_ADC 0x0B (Read Only) |                                                                                          |   |   |   |   |   |   |   |

|---------------------------|------------------------------------------------------------------------------------------|---|---|---|---|---|---|---|

| BIT                       | 7                                                                                        | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| BIT NAME                  | ADC_1                                                                                    |   |   |   |   |   |   |   |

| Reset Value               | 0                                                                                        | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| ADC_1                     | ID ADC: 0V to 1.5V<br>Voltage step 5.9mV (typ)                                           |   |   |   |   |   |   |   |

| VBUS_ADC 0x0C (Read Only) |                                                                                          |   |   |   |   |   | _ |   |

| BIT                       | 7                                                                                        | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| BIT NAME                  | ADC_2                                                                                    |   |   |   |   |   |   |   |

| Reset Value               | 0                                                                                        | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| ADC_2                     | VBUS ADC: 3V to 30V Voltage step 118mV (typ) Write 1 to VBUSADC_EN for one time VBUS ADC |   |   |   |   |   |   |   |

Figure 2. Current Source On-Time Timing Diagram (IS\_INIT\_SET = 0)

#### **Detailed Description**

The MAX20330 features the overvoltage protection to the charger input VBUS line when a travel adapter (TA) is used. The MAX20330 uses the external N-MOSFET with  $R_{ON}$  lower than  $10m\Omega$  and  $V_{DS}$  rating at or higher than +30V. The device protects the battery and low voltage systems against voltage faults up to  $40V_{DC}.$  The external TVS could be used to further protect the device from surges. If the input voltage exceeds the overvoltage threshold, the external N-FET is disconnected from the input to prevent damage to the protected components. In addition to the OVP controller function, the MAX20330 also provides the accessory ID detection as well as VBUS short detection when the device is not in OVP mode (EN\_OVP = 0).

#### **ENb Bit**

The MAX20330 is enabled by default. When disabled as VBUS is available, the part will remain enabled sinking current from VBUS.

#### 36VDC (40V Abs Max) Withstanding

The MAX20330 can withstand the DC voltage up to 40V. If 40V input is expected, it is recommended to use the external TVS that clamps the surge to 40V or below.

#### **OVLO**

OUT is connected to VBUS when VBUS is between UVLO threshold and OVLO threshold. When VBUS goes above overvoltage lockout threshold (SET\_OVLO 0x05), OUT is disconnected from VBUS, the OVLO bit is set high. When VBUS drops below SET\_OVLO threshold, the OVLO bit is deasserted and the debounce time starts counting. After the debounce time, OUT follows VBUS again.

#### **UVLO/POR**

The VBUS has min operating voltage of 2.7V. The ADC works when  $V_{CC}$  voltage is 2.6V or higher. The device disables the external FET unless VBUS is higher than UVLO threshold. When the device is operating with I<sup>2</sup>C ENb bit = 0 (default), if the UVLO happens, the device shuts down the switch immediately.

#### Safe Turn-On Protection

When the switch turns on, if the OUT is below V<sub>SS\_THR</sub> of VBUS after soft start time out, it shuts down the output.

#### **Fast Turn-Off Time**

The MAX20330 provides 100ns turn off response time and can switch off an external N-MOSFET.

#### **VBUS ID/Short Detection**

The MAX20330 can check the VBUS impedance with automatic scaling for the best resolution using the different current resources. The current source can be turned on only when the OVP function is disabled (EN\_OVP = 0). The ID open load voltage is 2V max. When the VBUS is soft shorted to ground, it can be detected and warn the user. Also, VBUS can be actively discharged by I<sup>2</sup>C command. This is useful when the OVP IC blocks the VBUS from discharged by the PMIC or by the USB type C controller during power down operation.

#### **Thermal Shutdown**

Thermal shutdown circuitry protects the devices from overheating. The switches turn off when the junction temperature exceeds +125°C (typ). The switches turn on again after the device temperature drops by approximately 20°C (typ).

### **Application Information**

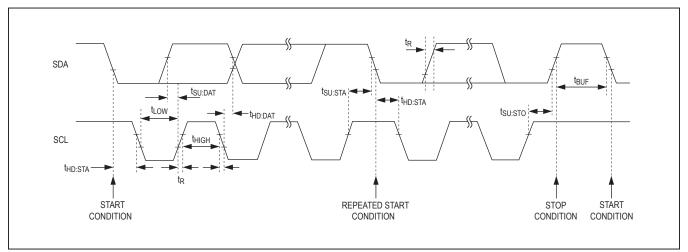

#### I<sup>2</sup>C Interface

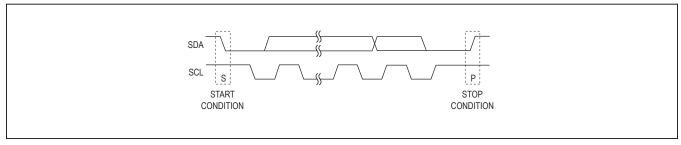

When in I<sup>2</sup>C mode, the MAX20330 operates as a slave device that sends and receives data through an I<sup>2</sup>C-compatible 2-wire interface. The interface uses a serial data line (SDA) and a serial clock line (SCL) to achieve bidirectional communication between master(s) and slave(s). A master (typically a microcontroller) initiates all data transfers to and from the MAX20330 and generates the SCL clock that synchronizes the data transfer. The SDA line operates as both an input and an open-drain output. A pullup resistor is required on SDA. The SCL line operates only as an input. A pullup resistor is required on SCL if there are multiple masters on the 2-wire interface, or

if the master in a single-master system has an open-drain SCL output. Each transmission consists of a START condition sent by a master, followed by the MAX20330 7-bit slave address plus R/W bit, a register address byte, one or more data bytes, and finally a STOP condition (Figure 3).

#### **Start and Stop Conditions**

Both SCL and SDA remain high when the interface is not busy. A master signals the beginning of a transmission with a START (S) condition by transitioning SDA from high-to-low while SCL is high (Figure 4). When the master has finished communicating with the slave, it issues a STOP (P) condition by transitioning SDA from low to high while SCL is high. The bus is then free for another transmission.

Figure 3. I<sup>2</sup>C Interface Timing Details

Figure 4. Start and Stop Conditions

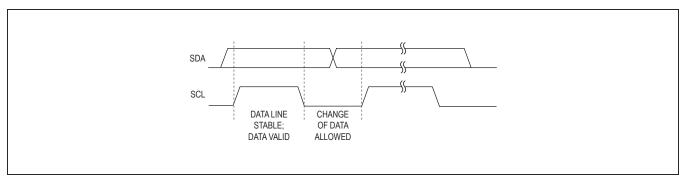

#### **Bit Transfer**

One data bit is transferred during each clock pulse (Figure 5). The data on SDA must remain stable while SCL is high. Changes in SDA while SCK is high and stable are considered control signals (see *Start and Stop Conditions*)

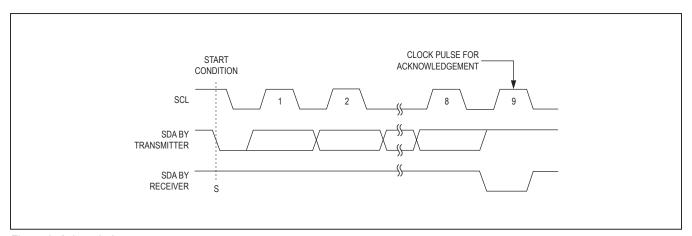

#### **Acknowledge**

The acknowledge bit is a clocked 9<sup>th</sup> bit (<u>Figure 6</u>), which the recipient uses to handshake receipt of each byte of data. Thus, each byte transferred effectively requires 9 bits. The master generates the 9<sup>th</sup> clock pulse, and the recipient pulls down SDA during the acknowledge clock pulse. The SDA line is stable low during the high period of the clock pulse. When the master is transmitting to the MAX20330, it generates the acknowledge bit because the

device is the recipient. When the device is transmitting to the master, the master generates the acknowledge bit because the master is the recipient. If the device did not pull SDA low, a not acknowledge is indicated.

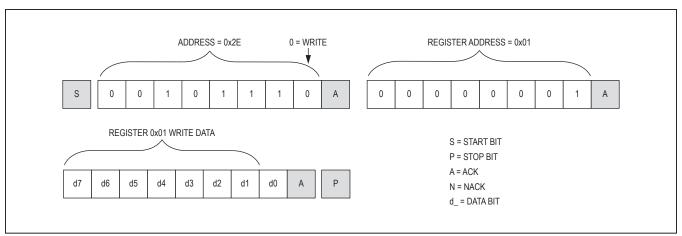

#### **Slave Address**

The MAX20330 features a 7-bit slave address: 0010 111. The bit following a 7-bit slave address is the  $R/\overline{W}$  bit, which is low for a write command and high for a read command.

#### **Bus Reset**

The MAX20330 resets the bus with the I<sup>2</sup>C start condition for reads. When the  $R/\overline{W}$  bit is set to 1, the device transmits data to the master, thus the master is reading from the device.

Figure 5. Bit Transfer

Figure 6. Acknowledge

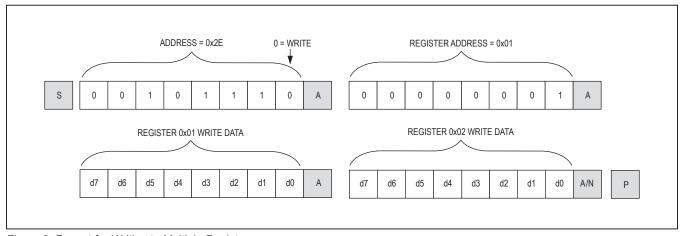

#### **Format for Writing**

A write to the MAX20330 comprises the transmission of the slave address with the  $R/\overline{W}$  bit set to zero, followed by at least 1 byte of information. The first byte of information is the register address or command byte. The register address determines which register of the device is to be written by the next byte, if received. If a STOP (P) condition is detected after the register address is received,

then the device takes no further action beyond storing the register address. Any bytes received after the register address are data bytes. The first data byte goes into the register selected by the register address and subsequent data bytes go into subsequent registers (Figure 7). If multiple data bytes are transmitted before a STOP condition, these bytes are stored in subsequent registers because the register addresses autoincrement (Figure 8).

Figure 7. Format for I<sup>2</sup>C Write

Figure 8. Format for Writing to Multiple Registers

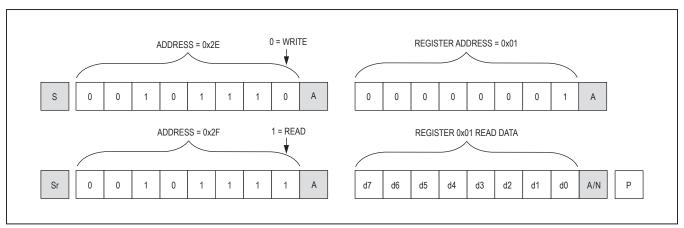

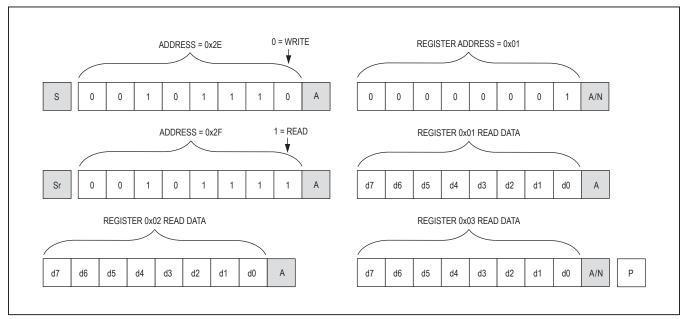

#### Format for Reading

The MAX20330 is read using the internally stored register address as an address pointer, the same way the stored register address is used as an address pointer for a write. The pointer autoincrements after each data byte is read using the same rules as for a write. Thus, a read is initiated

by first configuring the register address by performing a write (Figure 9). The master can now read consecutive bytes from the device, with the first data byte being read from the register addressed pointed by the previously written register address (Figure 10). Once the master sounds a NACK, the MAX20330 stops sending valid data.

Figure 9. Format for Reads (Repeated Start)

Figure 10. Format for Reading Multiple Registers

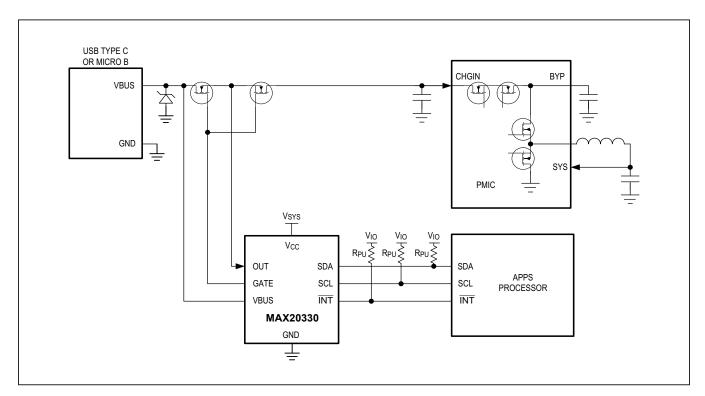

## **Typical Application Circuits**

## **Ordering Information**

| PART           | TOP<br>MARK | TEMP<br>RANGE  | PIN-<br>PACKAGE |

|----------------|-------------|----------------|-----------------|

| MAX20330EWA+T  | CA          | -40°C TO +85°C | 8 WLP           |

| MAX20330BEWA+T | CC          | -40°C TO +85°C | 8 WLP           |

<sup>+</sup> Denotes lead(Pb)-free/RoHS-compliant package.

# Chip Information PROCESS: BiCMOS

Maxim Integrated | 22 www.maximintegrated.com

T = Tape and reel.