## Spread-Spectrum Crystal Multiplier

### **General Description**

The MAX31180 is a low-jitter, crystal-based clock generator with an integrated phase-locked loop (PLL) to generate spread-spectrum clock outputs from 16MHz to 134MHz. The device is pin-programmable to select the clock multiplier rate as well as the dither magnitude. The MAX31180 has a spread-spectrum disable mode and a power-down mode to conserve power.

### **Applications**

- Automotive

- Cable Modems

- Cell Phones

- Computer Peripherals

- Copiers

- Infotainment

- PCs

- Printers

Ordering Information appears at end of data sheet.

### **Features**

- Generates Spread-Spectrum Clocks from 16MHz to 134MHz

- Selectable Clock Multiplier Rates of 1x, 2x, and 4x

- Center Spread-Spectrum Dithering

- Selectable Spread-Spectrum Modulation Magnitudes of ±0.5%, ±1.0%, and ±1.5%

- Spread-Spectrum Disable Mode

- Low Cycle-to-Cycle Jitter

- Power-Down Mode with High-Impedance Output

- Low Power Consumption

- 3.0V to 3.6V Single-Supply Operation

- -40°C to +125°C Operating Temperature Range

- Small 8-Pin µSOP Package

- AEC-Q100 Qualified (MAX31180AUA/V+ Only)

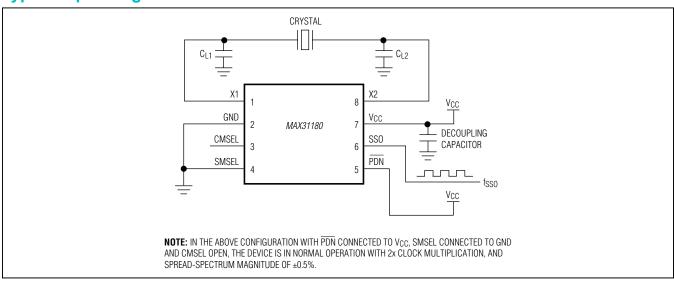

## **Typical Operating Circuit**

## Spread-Spectrum Crystal Multiplier

### **Absolute Maximum Ratings**

| (Voltages relative to GND.)            |                                   |

|----------------------------------------|-----------------------------------|

| Voltage Range on V <sub>CC</sub>       | 0.3V to +4.3V                     |

| Voltage Range on Any Pin               | 0.3V to (V <sub>CC</sub> + 0.3V), |

|                                        | not to exceed +4.3V               |

| Continuous Power Dissipation ( $T_A =$ | +70°C)                            |

| Operating Temperature Range       | 40°C to +125°C |

|-----------------------------------|----------------|

| Storage Temperature Range         | 55°C to +125°C |

| Lead Temperature (soldering, 10s) | +300°C         |

| Soldering Temperature (reflow)    | +260°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### µSOP-8

| U8+1           |

|----------------|

|                |

| <u>21-0036</u> |

| <u>90-0092</u> |

|                |

| 221°C/W        |

| 42°C/W         |

|                |

| 206.30/W       |

| 42°C/W         |

|                |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

# Spread-Spectrum Crystal Multiplier

## **Recommended Operating Conditions**

$(T_A = -40^{\circ}C \text{ to } + 125^{\circ}C, \text{ unless otherwise noted.})$

| PARAMETER                         | SYMBOL            | CONDITIONS                                      | MIN                       | ТҮР | МАХ                      | UNITS |

|-----------------------------------|-------------------|-------------------------------------------------|---------------------------|-----|--------------------------|-------|

| Supply Voltage                    | V <sub>CC</sub>   | (Note 1)                                        | 3.0                       |     | 3.6                      | V     |

| Input Logic 1                     | V <sub>IH</sub>   |                                                 | 0.8 x<br>V <sub>CC</sub>  |     | V <sub>CC</sub> +<br>0.3 | V     |

| Input Logic 0                     | V <sub>IL</sub>   |                                                 | V <sub>GND</sub> -<br>0.3 |     | 0.2 x<br>V <sub>CC</sub> | V     |

| Input Logic Open                  | I <sub>IF</sub>   | 0V < V <sub>IN</sub> < V <sub>CC</sub> (Note 2) |                           |     | Q1                       | FA    |

| Input Leakage                     | ١ <sub>١L</sub>   | 0V < V <sub>IN</sub> < V <sub>CC</sub> (Note 3) |                           |     | Q80                      | FA    |

|                                   |                   | f <sub>SSO</sub> < 67MHz                        |                           |     | 15                       |       |

| SSO Load                          | C <sub>SSO</sub>  | 67MHz P f <sub>SSO</sub> < 101MHz               |                           |     | 10                       | pF    |

|                                   |                   | 101MHz P f <sub>SSO</sub> < 134MHz              |                           |     | 7                        |       |

| Crystal or Clock Input Frequency  | f <sub>IN</sub>   |                                                 | 16.0                      |     | 33.4                     | MHz   |

| Crystal ESR                       | X <sub>ESR</sub>  |                                                 |                           |     | 90                       | I     |

| Clock Input Duty Cycle            | F <sub>INDC</sub> |                                                 | 40                        |     | 60                       | %     |

| Crystal Parallel Load Capacitance | CL                | (Note 4)                                        |                           |     | 18                       | pF    |

## **DC Electrical Characteristics**

(V\_{CC} = +3.0V to +3.6V, T\_A = -40°C to +125°C, unless otherwise noted.)

| PARAMETER                       | SYMBOL           | CONDITIONS                                         | MIN | ТҮР | МАХ | UNITS |

|---------------------------------|------------------|----------------------------------------------------|-----|-----|-----|-------|

| Supply Current                  | I <sub>CC1</sub> | C <sub>SSO</sub> = 15pF, f <sub>SSO</sub> = 16MHz  |     |     | 15  | mA    |

| Power-Down Current              | ICCQ             | $\overline{\text{PDN}}$ = GND, all input pins open |     |     | 200 | μA    |

| Output Leakage (SSO)            | I <sub>OZ</sub>  | PDN = GND                                          | -1  |     | +1  | μA    |

| Low-Level Output Voltage (SSO)  | V <sub>OL</sub>  | $I_{OL} = 4mA$                                     |     |     | 0.4 | V     |

| High-Level Output Voltage (SSO) | V <sub>OH</sub>  | I <sub>OH</sub> = -4mA                             | 2.4 |     |     | V     |

| Input Capacitance (X1/X2)       | C <sub>IN</sub>  | (Note 5)                                           |     | 5   |     | рF    |

# Spread-Spectrum Crystal Multiplier

### **AC Electrical Characteristics**

(V<sub>CC</sub> = +3.0 to +3.6V,  $T_A$  = -40°C to +125°C, unless otherwise noted.)

| PARAMETER                  | SYMBOL              | CONDITIONS                                                                         | MIN | ТҮР                  | MAX | UNITS |

|----------------------------|---------------------|------------------------------------------------------------------------------------|-----|----------------------|-----|-------|

|                            | 00000               | Measured at $V_{CC}/2$ , CMSEL = 0 or open                                         | 40  |                      | 60  | 0/    |

| SSO Duty Cycle             | SSODC               | Measured at $V_{CC}/2$ , CMSEL = 1                                                 | 30  |                      | 70  | %     |

| Rise Time                  | t <sub>R</sub>      | (Note 6)                                                                           |     | 1.6                  |     | ns    |

| Fall Time                  | t <sub>F</sub>      | (Note 6)                                                                           |     | 1.6                  |     | ns    |

| Peak Cycle-to-Cycle Jitter | tj                  | f <sub>SSO</sub> = 16MHz, T <sub>A</sub> = -40 to +85°C,<br>10,000 cycles (Note 5) |     | 75                   |     | ps    |

| Power-Up Time              | t <sub>POR</sub>    | PDN pin (Note 7)                                                                   |     |                      | 11  | ms    |

| Power-Down Time            | t <sub>PDN</sub>    | PDN pin (Note 8)                                                                   |     |                      | 100 | ns    |

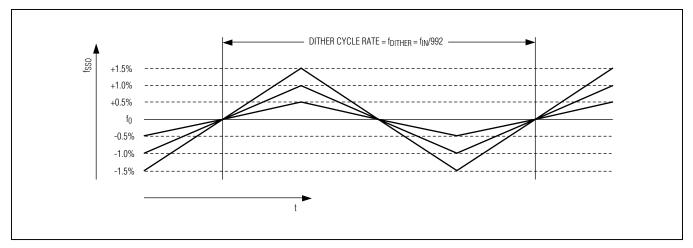

| Dither Rate                | f <sub>DITHER</sub> | (Note 9)                                                                           |     | f <sub>IN</sub> /992 |     |       |

Note 1: All voltages referenced to ground.

Note 2: Maximum source/sink current applied to input to be considered an open. Typical voltage range between 0.4 x V<sub>CC</sub> and  $0.55 \times V_{CC}$ .

Note 3: Applicable to pins CMSEL, SMSEL, and PDN.

Note 4: See information about  $C_{L1}$  and  $C_{L2}$  in the <u>Applications Information</u> section at the end of the data sheet.

Note 5: Not production tested.

Note 6: For 7pF load.

**Note 7:** Time between PDN deasserted to output active.

Note 8: Time between PDN asserted to output high impedance.

Note 9: Guaranteed by design.

# Spread-Spectrum Crystal Multiplier

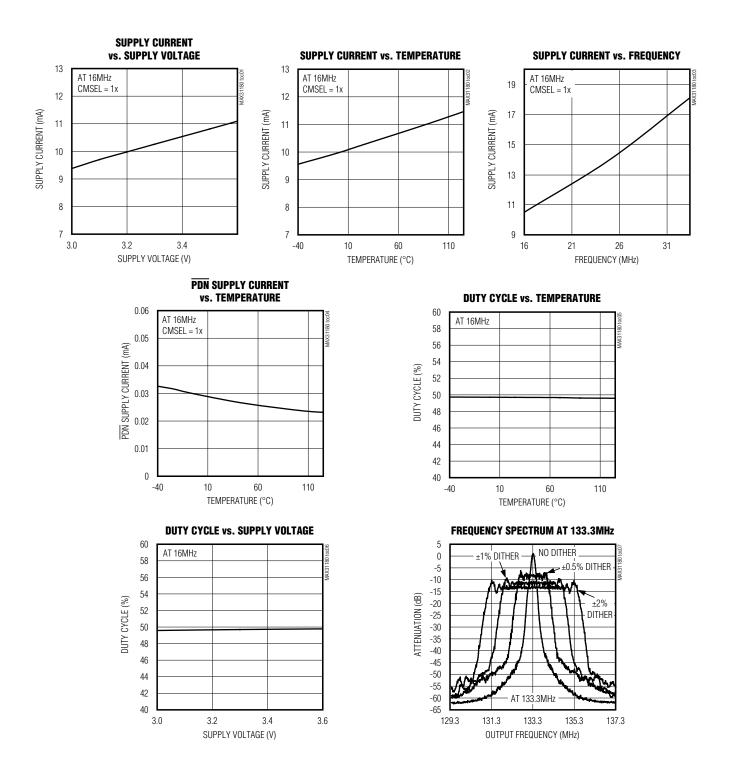

## **Typical Operating Characteristics**

(V<sub>CC</sub> = 3.3V, T<sub>A</sub> =  $+25^{\circ}$ C, unless otherwise noted.)

# Spread-Spectrum Crystal Multiplier

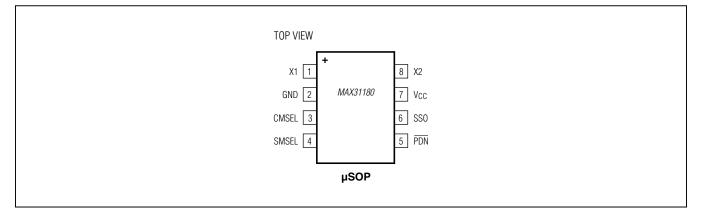

# **Pin Configuration**

# **Pin Description**

| PIN | NAME            | FUNCTION                                                                                                                                                                                       |

|-----|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | X1              | Crystal Drive/Clock Input. A crystal with the proper loading capacitors is connected across X1 and X2. Instead of a crystal, a clock can be applied at the X1 input.                           |

| 2   | GND             | Signal Ground                                                                                                                                                                                  |

| 3   | CMSEL           | Clock Multiplier Select. Tri-level digital input.<br>0 = 1x<br>Open = 2x<br>1 = 4x                                                                                                             |

| 4   | SMSEL           | Spread-Spectrum Magnitude Select. Tri-level digital input.<br>$0 = \pm 0.5\%$<br>Open = $\pm 1.0\%$<br>$1 = \pm 1.5\%$                                                                         |

| 5   | PDN             | Active-Low Power-Down/Spread-Spectrum Disable. Tri-level digital input.<br>0 = Power-Down/SSO Three-Stated<br>Open = Power-Up/Spread Spectrum Disabled<br>1 = Power-Up/Spread Spectrum Enabled |

| 6   | SSO             | Spread-Spectrum Clock Multiplier Output. Outputs a 1x, 2x, or 4x spread-spectrum version of the crystal or clock applied at the X1/X2 pins.                                                    |

| 7   | V <sub>CC</sub> | Supply Voltage                                                                                                                                                                                 |

| 8   | X2              | Crystal Drive Output. A crystal with the proper loading capacitors is connected across X1 and X2. If a clock is connected to X1, then X2 should be left open circuit.                          |

## Spread-Spectrum Crystal Multiplier

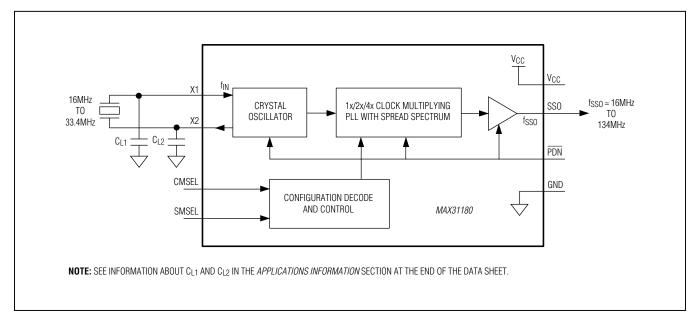

### **Block Diagram**

### **Detailed Description**

The MAX31180 is a crystal multiplier with center spreadspectrum capability. A 16MHz to 33.4MHz crystal is connected to the X1 and X2 pins. Alternately, a 16MHz to 33.4MHz clock can be applied to X1 in place of the crystal. In such applications, X2 would be left open circuit. Using the CMSEL input, the user selects whether the attached crystal or input clock is multiplied by 1, 2, or 4. The MAX31180 is capable of generating spread-spectrum clocks from 16MHz to 134MHz.

The PLL can dither the output clock about its center frequency at a user-selectable magnitude. Using the SMSEL input, the user selects the dither magnitude. The  $\overline{\text{PDN}}$ input can be used to place the device into a low-power standby mode where the SSO output is three-stated. If the  $\overline{\text{PDN}}$  pin is open, the SSO output is active but the spread-spectrum dithering is disabled. The spreadspectrum dither rate is fixed at  $f_{IN}/992$  to keep the dither rate above the audio frequency range. On power-up, the output clock (SSO) remains three-stated until the PLL reaches a stable frequency ( $f_{SSO}$ ) and dither ( $f_{DITHER}$ ).

### **Applications Information**

### **Crystal Selection**

The MAX31180 requires a parallel resonating crystal operating in the fundamental mode, with an ESR of less than  $90\Omega$ . The crystal should be placed very close to the device to minimize excessive loading due to parasitic capacitances.

### **Oscillator Input**

When driving the MAX31180 using an external oscillator clock, consider the input (X1) to be high impedance.

### Spread-Spectrum Crystal Multiplier

Figure 1. Spread-Spectrum Frequency Modulation

#### **Crystal Capacitor Selection**

The load capacitors  $C_{L1}$  and  $C_{L2}$  are selected based on the crystal specifications (from the data sheet of the crystal used). The crystal parallel load capacitance is calculated as follows:

$$C_L = \frac{C_{L1} \times C_{L2}}{C_{L1} + C_{L2}} + C_{IN} \qquad \qquad \text{Equation 1}$$

For the MAX31180 use  $C_{L1} = C_{L2} = C_{LX}$ . In this case, the equation then reduces to:

$$C_L = \frac{C_{LX}}{2} + C_{IN}$$

Equation 2

where  $C_{L1} = C_{L2} = C_{LX}$ .

Equation 2 is used to calculate the values of  $C_{L1}$  and  $C_{L2}$  based on values on  $C_L$  and  $C_{IN}$  noted in the Recommended Operating Conditions and <u>DC Electrical</u> Characteristics.

#### **Power-Supply Decoupling**

To achieve best results, it is highly recommended that a decoupling capacitor is used on the IC power-supply pins. Typical values of decoupling capacitors are  $0.001\mu$ F and  $0.1\mu$ F. Use a high-quality, ceramic, surface-mount capacitor, and mount it as close as possible to the V<sub>CC</sub> and GND pins of the IC to minimize lead inductance.

#### Layout Considerations

As noted earlier, the crystal should be placed very close to the device to minimize excessive loading due to parasitic capacitances. Care should also be taken to minimize loading on pins that could be open as a programming option (SMSEL and CMSEL). Coupling on inputs due to clocks should be minimized.

### **Ordering Information**

| PART            | TEMP RANGE      | PIN-PACKAGE |

|-----------------|-----------------|-------------|

| MAX31180AUA+    | -40°C to +125°C | 8 µSOP      |

| MAX31180AUA+T   | -40°C to +125°C | 8 µSOP      |

| MAX31180AUA/V+  | -40°C to +125°C | 8 µSOP      |

| MAX31180AUA/V+T | -40°C to +125°C | 8 µSOP      |

+Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape and reel.

/V denotes an automotive qualified part.