19-5182; Rev 1; 5/11

EVALUATION KIT AVAILABLE

## **1Gbps to 11.3Gbps, SFP+ Laser Driver** with Laser Impedance Mismatch Tolerance

#### **General Description**

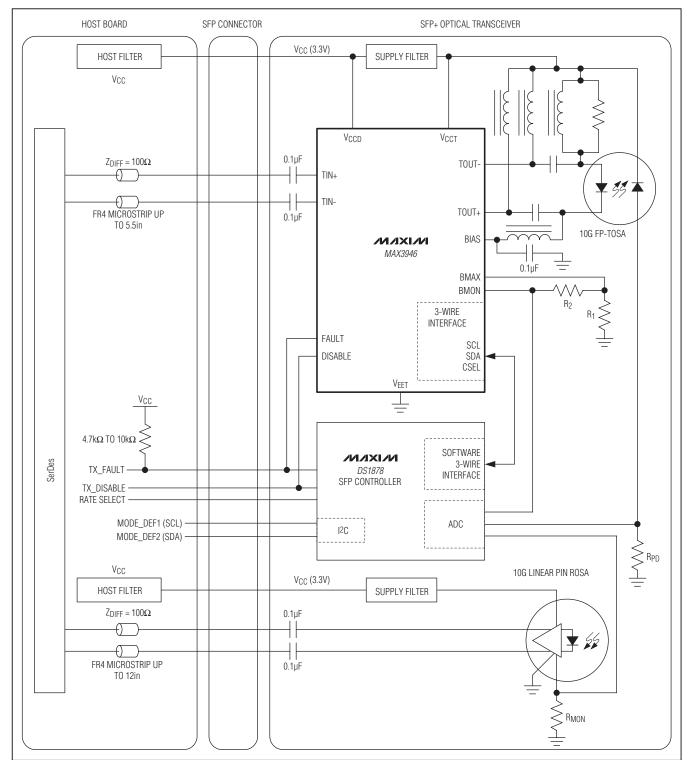

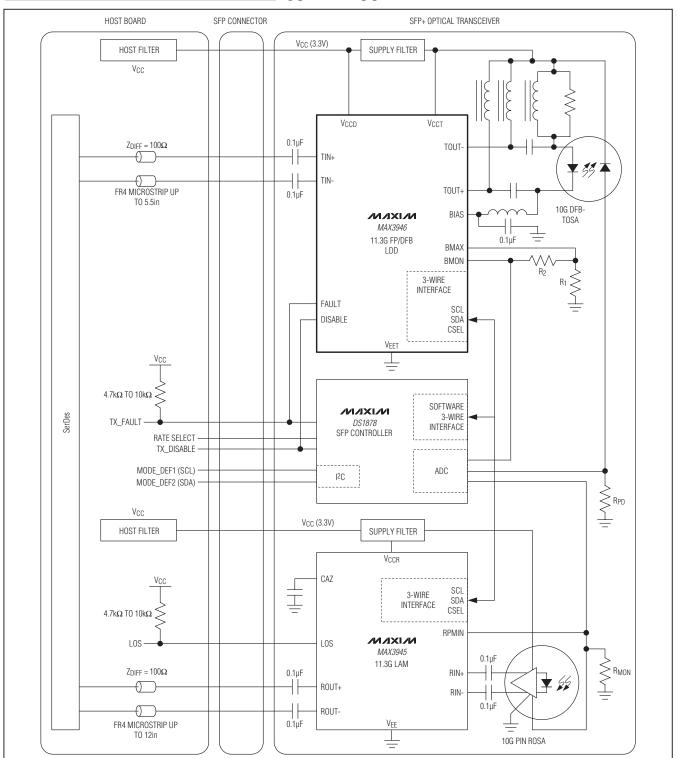

The MAX3946 is a +3.3V, multirate, low-power laser

diode driver designed for Ethernet and Fibre Channel

transmission systems at data rates up to 11.3Gbps.

This device is optimized to drive a differential transmit-

ter optical subassembly (TOSA) with a  $25\Omega$  flex circuit.

The unique design of the output stage enables use of

unmatched TOSAs, greatly reducing headroom limita-

The device receives differential CML-compatible signals

with on-chip line termination. It can deliver laser modulation current of up to 80mA, at an edge speed of 22ps

(20% to 80%), into a 5 $\Omega$  to 25 $\Omega$  external differential load.

The device is designed to have a symmetrical output

stage with on-chip back terminations integrated into

its outputs. A high-bandwidth, fully differential signal path is implemented to minimize deterministic jitter. An

equalization block can be activated to compensate for

the SFP+ connector. The integrated bias circuit provides

programmable laser bias current up to 80mA. Both the

laser bias generator and the laser modulator can be dis-

A 3-wire digital interface reduces the pin count and permits adjustment of input equalization, pulse-width

adjustment, Tx polarity, Tx deemphasis, modulation cur-

rent, and bias current without the need for external com-

ponents. The MAX3946 is available in a 4mm x 4mm,

4x/8x FC SFP+ Optical Transceivers

10GBASE-LR SFP+ Optical Transceivers

10GBASE-LRM SFP+ Optical Transceivers

OC192-SR XFP/SFP+ SDH/SONET Transceivers

10GFC SFP+ Optical Transceivers

**Applications**

tions and lowering power consumption.

\_Features

- 225mW Power Dissipation Enables < 1W SFP+ Modules

- Up to 100mW Power Consumption Reduction by Enabling the Use of Unmatched FP/DFB TOSAs

- Supports SFF-8431 SFP+ MSA and SFF-8472 Digital Diagnostic

- 225mW Power Dissipation at 3.3V (I<sub>MOD</sub> = 40mA, IBIAS = 60mA Assuming 25Ω TOSA)

- Single +3.3V Power Supply

- Up to 11.3Gbps (NRZ) Operation

- Programmable Modulation Current from 10mA to 100mA (5Ω Load)

- Programmable Bias Current from 5mA to 80mA

- Programmable Input Equalization

- Programmable Output Deemphasis

- ◆ 25Ω Output Back Termination at TOUT+ and TOUT-

- DJ Performance 7psp-p with Mismatched Differential Load (5Ω)

- DJ Performance 5psp-p with Mismatched Differential Load (25Ω)

- DJ Performance 5psp-p with 50Ω Differential Load

- Programmable Pulse Width

- Edge Transition Times of 22ps

- Bias Current Monitor

- Integrated Eye Safety Features

- ♦ 3-Wire Digital Interface

- ♦ -40°C to +95°C Operation

#### **Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE |

|-------------|----------------|-------------|

| MAX3946ETG+ | -40°C to +85°C | 24 TQFN-EP* |

**Note:** Parts are guaranteed by design and characterization to operate over the  $-40^{\circ}$ C to  $+95^{\circ}$ C ambient temperature range (T<sub>A</sub>) and are tested up to  $+85^{\circ}$ C.

+Denotes a lead(Pb)-free/RoHS-compliant package. \*EP = Exposed pad.

abled from a single pin.

24-pin TQFN package.

####

Maxim Integrated Products 1

n 5mA to 80mA n sis TOUT+ and

MAX3946

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

#### **ABSOLUTE MAXIMUM RATINGS**

| VCC, VCCT, VCCD                    | 0.3V to +4.0V              |

|------------------------------------|----------------------------|

| Current Into TOUT+ and TOUT        | +100mA                     |

| Current Into TIN+ and TIN          | 20mA to +20mA              |

| Voltage Range at TIN+, TIN-,       |                            |

| DISABLE, SDA, SCL, CSEL, FAULT,    |                            |

| BMAX, and BMON                     | 0.3V to (VCC + 0.3V)       |

| Voltage Range at BIAS              | -0.3V to VCC               |

| Voltage Range at TOUT+ and TOUT (V | CC - 1.3V) to (VCC + 1.3V) |

| Current into BIAS                                     | +130mA          |

|-------------------------------------------------------|-----------------|

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                 |

| TQFN (derate 27.8mW/°C above +70°C)                   | 2222mW          |

| Storage Temperature Range                             | -55°C to +150°C |

| Die Attach Temperature                                | +400°C          |

| Lead Temperature (soldering, 10s)                     | +300°C          |

| Soldering Temperature (reflow)                        | +260°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### PACKAGE THERMAL CHARACTERISTICS (Note 1)

TQFN

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a fourlayer board. For detailed information on package thermal considerations, refer to <u>www.maxim-ic.com/thermal-tutorial</u>.

#### **ELECTRICAL CHARACTERISTICS**

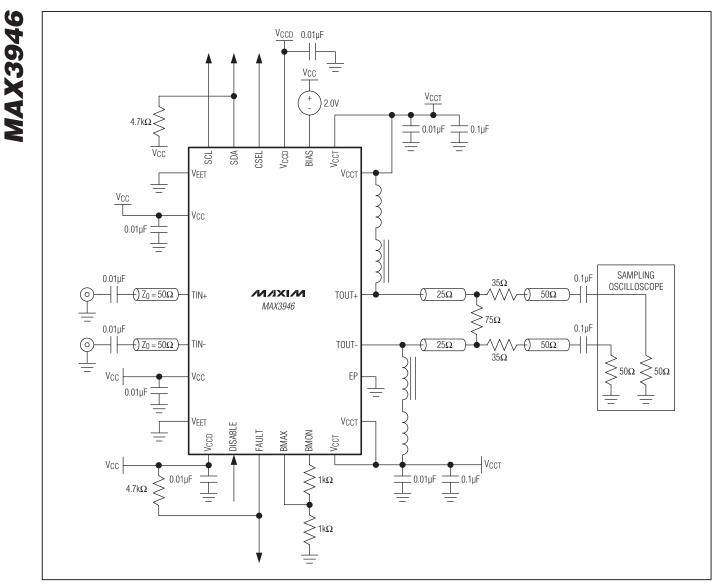

$(V_{CC} = +2.85V \text{ to } +3.63V, T_{A} = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ and Figure 1. Guaranteed by design and characterization from T_{A} = -40^{\circ}\text{C} \text{ to } +95^{\circ}\text{C}.$ Typical values are at V<sub>CC</sub> = +3.3V, I<sub>BIAS</sub> = 60mA, I<sub>MOD</sub> = 40mA, 25 $\Omega$  differential output load, and T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 2)

| PARAMETER                        | SYMBOL   | CONDITIONS                                                                  | MIN  | TYP  | MAX  | UNITS             |

|----------------------------------|----------|-----------------------------------------------------------------------------|------|------|------|-------------------|

| POWER SUPPLY                     |          |                                                                             |      |      |      |                   |

| Power-Supply Current             | Icc      | Excludes output current through the exter-<br>nal pullup inductors (Note 3) |      | 68   | 90   | mA                |

| Power-Supply Voltage             | Vcc      |                                                                             | 2.85 |      | 3.63 | V                 |

| Power Supply Noise               |          | DC to 10MHz                                                                 |      |      | 100  |                   |

| Power-Supply Noise               |          | 10MHz to 20MHz                                                              |      |      | 10   | mV <sub>P-P</sub> |

| POWER-ON RESET                   |          |                                                                             |      |      |      |                   |

| VCC for Enable High              |          |                                                                             |      | 2.55 | 2.75 | V                 |

| V <sub>CC</sub> for Enable Low   |          |                                                                             | 2.3  | 2.45 |      | V                 |

| DATA INPUT SPECIFICATION         |          |                                                                             |      |      |      |                   |

| Input Data Rate                  |          |                                                                             | 1    | 10   | 11.3 | Gbps              |

| Differential Input Voltage       | VIN      | TXEQ_EN = high, launch amplitude into FR4 transmission line $\leq 5.5$ in   | 0.19 |      | 0.7  | Vp-p              |

|                                  |          | TXEQ_EN = low                                                               | 0.15 |      | 1.0  |                   |

| Differential Input Resistance    | RIN      |                                                                             | 75   | 100  | 125  | Ω                 |

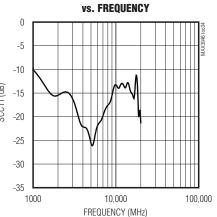

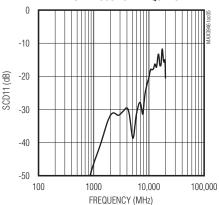

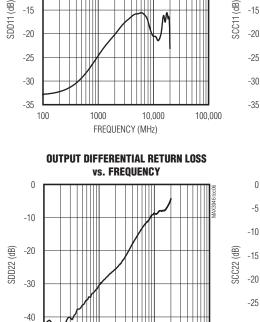

| Differential Input Return Loss   | SDD11    | Part powered on, $f \le 10GHz$                                              |      | 12   |      | dB                |

| Common-Mode Input Return<br>Loss | SCC11    | Part powered on, $1GHz \le f \le 10GHz$                                     |      | 10   |      | dB                |

| BIAS GENERATOR                   |          |                                                                             |      |      |      |                   |

| Maximum Bias Current             | IBIASMAX | Current into BIAS pin, DISABLE = low, and TX_EN = high                      | 80   |      |      | mA                |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +2.85V \text{ to } +3.63V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ and Figure 1. Guaranteed by design and characterization from T_A = -40^{\circ}\text{C} \text{ to } +95^{\circ}\text{C}.$ Typical values are at V<sub>CC</sub> = +3.3V, I<sub>BIAS</sub> = 60mA, I<sub>MOD</sub> = 40mA, 25 $\Omega$  differential output load, and T<sub>A</sub> = +25^{\circ}\text{C}, unless otherwise noted.) (Note 2)

| PARAMETER                                                     | SYMBOL    | CONDITIONS                                                                                                         | MIN          | TYP | MAX          | UNITS   |  |

|---------------------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------|--------------|-----|--------------|---------|--|

| Minimum Bias Current                                          | IBIASMIN  | Current into BIAS pin, DISABLE = low, and TX_EN = high                                                             |              |     | 5            | mA      |  |

| Bias-Off Current                                              | IBIAS-OFF | Current into BIAS pin, DISABLE = high or<br>TX_EN = low or SET_IBIAS[8:0] = H0x00;<br>BIAS pin voltage at $V_{CC}$ |              |     | 100          | μA      |  |

| Bias Current DAC Stability                                    |           | $5mA \le I_{BIAS} \le 80mA$ , $V_{BIAS} = V_{CC} - 1.5V$<br>(Notes 2, 4)                                           |              | 1   | 3            | %       |  |

| Instantaneous Compliance<br>Voltage at BIAS                   | VBIAS     |                                                                                                                    | 0.9          | 1.5 | 2.1          | V       |  |

| BMON Current Gain                                             | GBMON     | GBMON = IBMON/IBIAS, external resistor to ground defines voltage                                                   | 9            | 10  | 11           | mA/A    |  |

| Compliance Voltage at BMON                                    |           |                                                                                                                    | 0            |     | 1.8          | V       |  |

| BMON Current Gain Stability                                   |           | $5mA \le I_{BIAS} \le 80mA$ (Notes 2, 4)                                                                           |              | 1.2 | 4            | %       |  |

| LASER MODULATOR                                               |           |                                                                                                                    |              |     |              |         |  |

| TOUT+ and TOUT-<br>Instantaneous Output<br>Compliance Voltage |           |                                                                                                                    | VCC -<br>1.0 |     | VCC +<br>1.0 | V       |  |

| Maximum Modulation Current                                    | Imodmax   | Current into external $25\Omega$ differential termi-<br>nation, output common-mode<br>voltage = V <sub>CC</sub>    | 80           |     |              | - mAp-p |  |

|                                                               |           | Current into external $50\Omega$ differential termi-<br>nation, output common-mode<br>voltage = V <sub>CC</sub>    | 60           |     |              |         |  |

| Minimum Modulation Current                                    | IMODMIN   |                                                                                                                    |              |     | 10           | mAp-p   |  |

| Differential Output Resistance                                | 2 x Rout  |                                                                                                                    |              | 50  |              | Ω       |  |

| Modulation-Off Maximum Current                                | IMOD-OFF  | Current between TOUT+ and TOUT- when<br>DISABLE = high or TX_EN = low or<br>SET_IMOD[8:0] = H0x00                  |              |     | 100          | μA      |  |

| Modulation Current DAC Stability                              |           | $10\text{mA} \le I_{\text{MOD}} \le 80\text{mA}$ (Notes 2, 4)                                                      |              | 1.5 | 3            | %       |  |

| Modulation Current Edge Speed                                 |           | 20% to 80%, 20mA $\leq$ I_MOD $\leq$ 80mA                                                                          |              | 22  | 30           | ps      |  |

| (Note 2)                                                      | tR, tF    | 20% to 80%, 10mA $\leq$ I <sub>MOD</sub> $\leq$ 80mA, TXDE_MD[1:0] = 3d                                            |              | 22  | 30           |         |  |

|                                                               |           | $10mA \le I_{MOD} \le 60mA, \ 11.3Gbps, \ output \\ differential \ load = 50\Omega$                                |              | 5   | 12           |         |  |

|                                                               |           | $\begin{array}{l} 10mA \leq I_{MOD} \leq 80mA, \ 11.3Gbps, \ output \\ differential \ load = 25\Omega \end{array}$ |              | 5   | 12           | – psp-p |  |

| Deterministic Jitter (Notes 2, 5)                             | DJ        | $10mA \leq I_{MOD} \leq 80mA, 11.3Gbps, output differential load = 5\Omega$                                        |              | 7   |              |         |  |

|                                                               |           | $10\text{mA} \le I_{\text{MOD}} \le 60\text{mA}$ , 10.7Gbps, output differential load = $50\Omega$ (K28.5 pattern) |              | 5   | 10.5         |         |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +2.85V \text{ to } +3.63V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ and Figure 1. Guaranteed by design and characterization from T_A = -40^{\circ}\text{C} \text{ to } +95^{\circ}\text{C}.$ Typical values are at V<sub>CC</sub> = +3.3V, I<sub>BIAS</sub> = 60mA, I<sub>MOD</sub> = 40mA, 25 $\Omega$  differential output load, and T<sub>A</sub> = +25^{\circ}\text{C}, unless otherwise noted.) (Note 2)

| PARAMETER                            | SYMBOL     | CONDITIONS                                                                                                                                      | MIN          | ТҮР          | MAX          | UNITS |

|--------------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|--------------|-------|

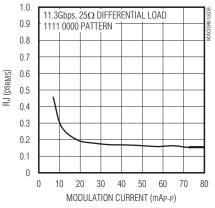

| Random Jitter                        | RJ         | $10mA \le I_{MOD} \le 80mA$ , output differential load = $25\Omega$ (Note 2)                                                                    |              | 0.19         | 0.55         | psRMS |

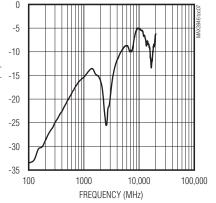

| Differential Output Peturn Less      | 20000      | Part powered on, $f \le 5GHz$                                                                                                                   |              | 8            |              | dD    |

| Differential Output Return Loss      | SDD22      | Part powered on, $f \le 10GHz$                                                                                                                  |              | 6            |              | dB    |

| SAFETY FEATURES                      |            |                                                                                                                                                 |              |              |              |       |

| Threshold Voltage at BMAX            | VBMAX      | FAULT always occurs for $V_{BMAX} \ge 1.3V$ ,<br>FAULT never occurs for $V_{BMAX} < 1.1V$<br>(Note 2, Figure 1)                                 | 1.1          | 1.2          | 1.3          | V     |

| Threshold Voltage at BIAS            | VBIAS      | FAULT never occurs for V <sub>BIAS</sub> $\geq$ 0.57V,<br>FAULT always occurs for V <sub>BIAS</sub> < 0.44V                                     | 0.44         | 0.48         | 0.57         | V     |

| Threshold Voltage at BMON            | VBMON      | Warning always occurs for V <sub>BMON</sub> ≥<br>V <sub>CC</sub> - 0.5V, warning never occurs for<br>V <sub>BMON</sub> < V <sub>CC</sub> - 0.7V | VCC -<br>0.7 | VCC -<br>0.6 | VCC -<br>0.5 | V     |

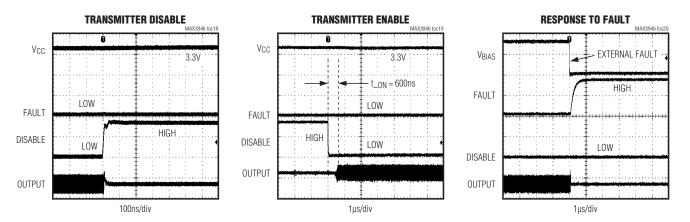

| SFP TIMING REQUIREMENTS              |            | L                                                                                                                                               |              |              |              |       |

| DISABLE Assert Time                  | t_OFF      | Time from rising edge of DISABLE input<br>signal to IBIAS < IBIAS-OFF and IMOD <<br>IMOD-OFF                                                    |              | 0.05         | 1            | μs    |

| DISABLE Negate Time                  | t_ON       | Time from falling edge of DISABLE to IBIAS<br>and IMOD at 90% of steady state                                                                   |              | 0.5          | 5            | μs    |

| FAULT Reset Time of Power-On<br>Time | t_INIT     | Time from power-on or negation of FAULT using DISABLE                                                                                           |              | 50           | 200          | μs    |

| FAULT Reset Time                     | t_FAULT    | Time from fault to FAULT on, CFAULT $\leq$ 20pF, RFAULT = 4.7k $\Omega$                                                                         |              | 0.5          | 2            | μs    |

| DISABLE to Reset                     |            | Time DISABLE must be held high to reset<br>FAULT                                                                                                | 0.5          |              |              | μs    |

| BIAS CURRENT DAC                     |            |                                                                                                                                                 |              |              |              |       |

| Full-Scale Current                   | IBIAS-FS   | SET_IBIAS[8:1] = HxFF                                                                                                                           | 80           | 100          |              | mA    |

| LSB Size                             |            |                                                                                                                                                 |              | 190          |              | μA    |

| Integral Nonlinearity                | INL        | $5\text{mA} \le I_{\text{BIAS}} \le 80\text{mA}$                                                                                                |              | ±0.5         |              | %FS   |

| Differential Nonlinearity            | DNL        | $5mA \le I_{BIAS} \le 80mA$ , guaranteed monotonic at 8-bit resolution SET_IBIAS[8:1]                                                           |              | ±0.5         |              | LSB   |

| MODULATION CURRENT DAC (2            | 25Ω DIFFER | ENTIAL LOAD)                                                                                                                                    |              |              |              |       |

| Full-Scale Current                   | IMOD-FS    | SET_IMOD[8:1] = HxFF                                                                                                                            | 80           | 105          |              | mA    |

| LSB Size                             |            |                                                                                                                                                 |              | 200          |              | μA    |

| Integral Nonlinearity                | INL        | $10\text{mA} \le \text{I}_{\text{MOD}} \le 80\text{mA}$                                                                                         |              | ±1           |              | %FS   |

| Differential Nonlinearity            | DNL        | $10mA \le I_{MOD} \le 80mA$ , guaranteed monotonic at 9-bit resolution SET_IMOD[8:0]                                                            |              | ±0.5         |              | LSB   |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +2.85V \text{ to } +3.63V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ and Figure 1. Guaranteed by design and characterization from T_A = -40^{\circ}\text{C} \text{ to } +95^{\circ}\text{C}.$ Typical values are at V<sub>CC</sub> = +3.3V, I<sub>BIAS</sub> = 60mA, I<sub>MOD</sub> = 40mA, 25 $\Omega$  differential output load, and T<sub>A</sub> = +25^{\circ}\text{C}, unless otherwise noted.) (Note 2)

| PARAMETER                                      | SYMBOL           | CONDITIONS                                                                     | MIN       | ТҮР | MAX  | UNITS |  |

|------------------------------------------------|------------------|--------------------------------------------------------------------------------|-----------|-----|------|-------|--|

| <b>CONTROL I/O SPECIFICATIONS</b>              |                  |                                                                                |           |     |      |       |  |

|                                                | Ιн               |                                                                                |           |     | 12   |       |  |

| DISABLE Input Current                          | ١ <sub>١</sub> ٢ | Depends on pullup resistance                                                   |           | 500 | 800  | - μΑ  |  |

| DISABLE Input High Voltage                     | VIH              |                                                                                | 1.8       |     | Vcc  | V     |  |

| DISABLE Input Low Voltage                      | VIL              |                                                                                | 0         |     | 0.8  | V     |  |

| DISABLE Input Resistance                       | Rpull            | Internal pullup resistor                                                       | 4.7       | 7.5 | 10   | kΩ    |  |

| 3-WIRE DIGITAL I/O SPECIFICA                   | TIONS (SDA       | , SCL, CSEL)                                                                   |           |     |      | ~     |  |

| Input High Voltage                             | Vih              |                                                                                | 2.0       |     | Vcc  | V     |  |

| Input Low Voltage                              | VIL              |                                                                                |           |     | 0.8  | V     |  |

| Input Hysteresis                               | VHYST            |                                                                                |           | 80  |      | mV    |  |

| Input Leakage Current                          | IIL, IIH         | $V_{IN} = 0V$ or $V_{CC}$ , internal pullup or pulldown is $75k\Omega$ typical |           |     | 150  | μA    |  |

| Output High Voltage                            | Vон              | External pullup is (4.7k $\Omega$ to 10k $\Omega$ ) to V <sub>CC</sub>         | VCC - 0.5 | 5   |      | V     |  |

| Output Low Voltage                             | Vol              | External pullup is (4.7k $\Omega$ to 10k $\Omega$ ) to V <sub>CC</sub>         |           |     | 0.4  | V     |  |

| <b>3-WIRE DIGITAL INTERFACE TII</b>            | MING CHAR        | ACTERISTICS (Figure 5)                                                         |           |     |      |       |  |

| SCL Clock Frequency                            | fscl             |                                                                                |           | 400 | 1000 | kHz   |  |

| SCL Pulse-Width High                           | tсн              |                                                                                | 0.5       |     |      | μs    |  |

| SCL Pulse-Width Low                            | tCL              |                                                                                | 0.5       |     |      | μs    |  |

| SDA Setup Time                                 | tDS              |                                                                                |           | 100 |      | ns    |  |

| SDA Hold Time                                  | tDН              |                                                                                |           | 100 |      | ns    |  |

| SCL Rise to SDA Propagation<br>Time            | tD               |                                                                                |           | 5   |      | ns    |  |

| CSEL Pulse-Width Low                           | tcsw             |                                                                                | 500       |     |      | ns    |  |

| CSEL Leading Time Before the<br>First SCL Edge | t∟               |                                                                                |           | 500 |      | ns    |  |

| CSEL Trailing Time After the Last SCL Edge     | t⊤               |                                                                                |           | 500 |      | ns    |  |

| SDA, SCL Load                                  | CB               | Total bus capacitance on one line with $4.7 \text{k}\Omega$ pullup to VCC      |           |     | 20   | pF    |  |

**Note 2:** Guaranteed by design and characterization ( $T_A = -40^{\circ}C$  to  $+95^{\circ}C$ ).

**Note 3:** BIAS is connected to 2.0V. TOUT+/TOUT- are connected through pullup inductors to a separate supply that is equal to V<sub>CCT</sub>. **Note 4:** Stability is defined as [(I\_measured) - (I\_reference)]/(I\_reference) over the listed current range, temperature, and V<sub>CC</sub> = V<sub>CCREF</sub> ±5%. V<sub>CCREF</sub> = 3.0V to 3.45V. Reference current measured at V<sub>CCREF</sub>, T<sub>A</sub> = +25°C.

Note 5: Measured with K28.5 data pattern at 10.7Gbps and with a (2<sup>7</sup> - 1 PRBS + 72 zeros + 2<sup>7</sup> - 1 PRBS (inverted) + 72 ones) pattern at 11.3Gbps.

Figure 1. AC Test Setup

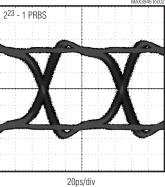

## **Typical Operating Characteristics**

$(V_{CC} = +3.3V, T_A = +25^{\circ}C, data pattern = 2^7 - 1 PRBS + 72 zeros + 2^7 - 1 PRBS (inverted) + 72 ones, unless otherwise noted.)$

#### 10.3Gbps OPTICAL EYE DIAGRAM MAX346 ted Verdens: 500 Verd

**10.3Gbps ELECTRICAL EYE DIAGRAM**

**INPUT COMMON-MODE RETURN LOSS**

INPUT DIFFERENTIAL TO COMMON-MODE Return LOSS vs. Frequency

RANDOM JITTER vs. MODULATION CURRENT (AT LOAD)

1000

FREQUENCY (MHz)

10.000

100.000

-50

100

0

-5

-10

#### **SUPPLY CURRENT vs. TEMPERATURE TOTAL CURRENT vs. TEMPERATURE** EYE CROSSING PERCENT (IMOD = 40mAp-p, IBIAS = 60mA)(IMOD AT LOAD = 40mAp-p, IBIAS = 60mA) vs. SET PWCTRL 100 220 75 CURRENT INTO $V_{CC},\,V_{CCT},\,\text{AND}\,\,V_{CCD}$ PINS PLUS MODULATION AND BIAS CURRENT CURRENT INTO VCC, VCCT, AND VCCD PINS 70 210 90 65 200 SUPPLY CURRENT (mA) SUPPLY CURRENT (mA) 60 190 CROSSING (%) 80 55 $25\Omega LOAD$ 180 50 70 45 170 40 160 $5\Omega LOAD$ 60 35 150 30 50 140 25 -40 -25 -10 5 20 35 50 65 80 95 -40 -25 -10 5 20 35 50 65 80 95 0011 0100 0101 0110 01110 0000 0001 0010 010 011 100 110 110 = TEMPERATURE (°C) TEMPERATURE (°C) SET PWCTRL[3:0] **BIAS CURRENT MODULATION CURRENT (AT LOAD) MODULATION CURRENT DEEMPHASIS** vs. DAC SETTING vs. MANUAL DEEMPHASIS SETTING vs. DAC SETTING 120 90 10 SET IMOD[8:0] = 230d 80 9 TXDE MD[1:0] = 2d100 $R_{IOAD} = 25\Omega$ MODULATION CURRENT (mAp-p) 8 70 DIFFERENTIAL 7 BIAS CURRENT (mA) 60 80 DEEMPHASIS (%) 6 50 60 5 40 4 $R_{LOAD}=50\Omega$ 40 30 DIFFERENTIAL 3 20 2 20 10 1 0 0 0 0 200 400 600 0 200 400 600 10 20 30 40 SET IBIAS[8:0] SET\_IMOD[8:0] SET\_TXDE[5:0] **BIAS MONITOR CURRENT** EDGE SPEED EDGE SPEED vs. TEMPERATURE vs. MODULATION CURRENT vs. DEEMPHASIS SETTING 700 40 40 25Ω LOAD, 20% TO 80% SET\_IMOD[8:0] = 230d 10Gbps, 11111 00000 PATTERN 25Ω LOAD, 20% TO 80% 600 35 35 10Gbps, 1111 0000 PATTERN IBIAS = 60mA 500 BMON CURRENT (µA) 30 30 EDGE SPEED (ps) EDGE SPEED (ps) 400 IBIAS = 30mA FALL TIME FALL TIME 25 25 300 20 20 200 I<sub>BIAS</sub> = 10mA **RISE TIME** N RISE TIME 15 15 100

10

0

20

40

IMOD (mA)

60

80

100

65 80 95

(V<sub>CC</sub> = +3.3V, T<sub>A</sub> = +25°C, data pattern = 2<sup>7</sup> - 1 PRBS + 72 zeros + 2<sup>7</sup> - 1 PRBS (inverted) +72 ones, unless otherwise noted.)

40

30

10

10

20

SET\_TXDE[5:0]

0

-40 -25 -10 5 20 35 50

TEMPERATURE (°C)

**MAX3946**

## **Typical Operating Characteristics (continued)**

$(V_{CC} = +3.3V, T_A = +25^{\circ}C, data pattern = 2^7 - 1 PRBS + 72 zeros + 2^7 - 1 PRBS (inverted) + 72 ones, unless otherwise noted.)$

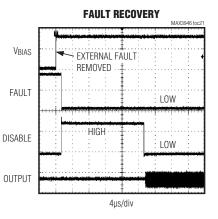

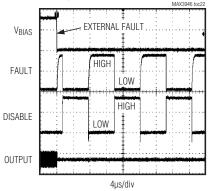

FREQUENT ASSERTION OF DISABLE

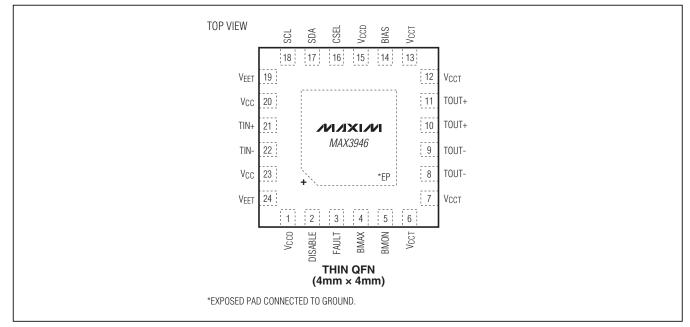

#### **Pin Configuration**

#### **Pin Description**

| PIN          | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                                                                             |

|--------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 15        | VCCD    | Power Supply. Provides supply voltage to the digital block.                                                                                                                                                                                                                                                                                                          |

| 2            | DISABLE | Disable Input, CMOS. Set to logic-low for normal operation. Logic-high or open disables both the modulation current and the bias current. Internally pulled up by a 7.5k $\Omega$ resistor to V <sub>CCD</sub> .                                                                                                                                                     |

| 3            | FAULT   | Fault Output, Open Drain. Logic-high indicates a fault condition. FAULT remains high even after the fault condition has been removed. A logic-low occurs when the fault condition has been removed and the fault latch has been cleared by toggling the DISABLE pin. FAULT should be pulled up to V <sub>CC</sub> by a $4.7$ k $\Omega$ to $10$ k $\Omega$ resistor. |

| 4            | BMAX    | Analog Laser Bias-Current Limit. A resistive voltage-divider connected among BMON, BMAX, and ground sets the maximum allowed laser bias current limit. The voltage at BMAX is internally compared to 1.2V bandgap reference voltage.                                                                                                                                 |

| 5            | BMON    | Bias Current-Monitor Output. Current out of this pin develops a ground-referenced voltage across external resistor(s) that is proportional to the laser bias current. The current sourced by this pin is typically 1/100th the BIAS pin current.                                                                                                                     |

| 6, 7, 12, 13 | VCCT    | Power Supply. Provides supply voltage to the output block.                                                                                                                                                                                                                                                                                                           |

| 8, 9         | TOUT-   | Inverted Modulation Current Output. Internally pulled up by a $25\Omega$ resistor to V <sub>CCT</sub> .                                                                                                                                                                                                                                                              |

| 10, 11       | TOUT+   | Noninverted Modulation Current Output. Internally pulled up by a $25\Omega$ resistor to V <sub>CCT</sub> .                                                                                                                                                                                                                                                           |

| 14           | BIAS    | Laser Bias Current Connection. This pin requires a $0.1\mu F$ capacitor to V <sub>EET</sub> for proper operation.                                                                                                                                                                                                                                                    |

| 16           | CSEL    | Chip-Select Input, CMOS. Setting CSEL to logic-high starts a cycle. Setting CSEL to logic-low ends the cycle and resets the control state machine. Internally pulled down by a $75k\Omega$ resistor to V <sub>EET</sub> .                                                                                                                                            |

| 17           | SDA     | Serial-Data Bidirectional Input, CMOS. Open-drain output. This pin has a $75k\Omega$ internal pullup, but it requires an external $4.7k\Omega$ to $10k\Omega$ pullup resistor. (Data line-collision protection is implemented.)                                                                                                                                      |

## Pin Description (continued)

**MAX3946**

| PIN    | NAME | FUNCTION                                                                                                                                                                             |

|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18     | SCL  | Serial-Clock Input, CMOS. This pin has a $75k\Omega$ internal pulldown.                                                                                                              |

| 19, 24 | VEET | Ground                                                                                                                                                                               |

| 20, 23 | Vcc  | Power-Supply Connections. Provides supply voltage to the core circuitry.                                                                                                             |

| 21     | TIN+ | Noninverted Data Input                                                                                                                                                               |

| 22     | TIN- | Inverted Data Input                                                                                                                                                                  |

| _      | EP   | Exposed Pad. Ground. Must be soldered to circuit board ground for proper thermal and electrical performance (see the <i>Exposed-Pad Package and Thermal Considerations</i> section). |

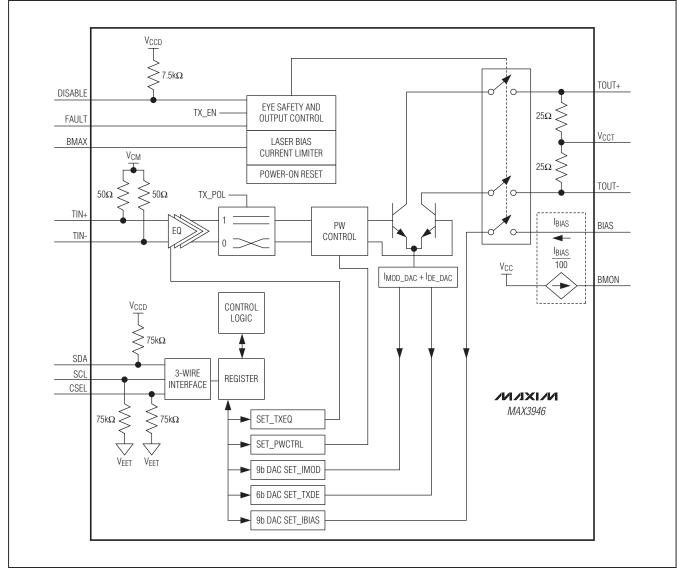

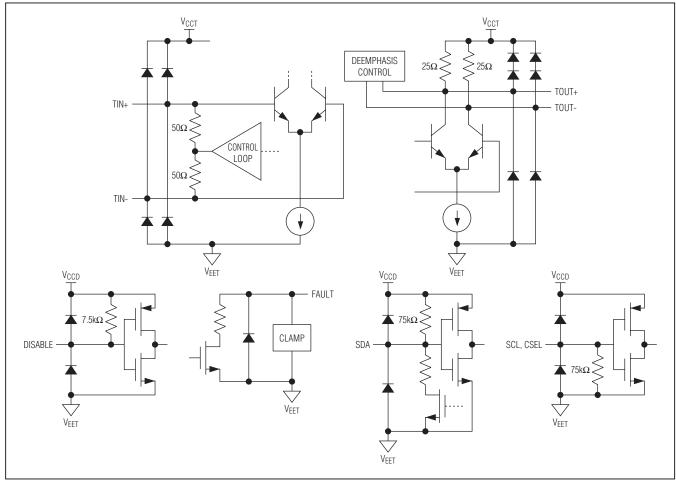

Figure 2. Functional Diagram

#### **Detailed Description**

The MAX3946 SFP+ laser driver is designed to drive  $5\Omega$  to  $50\Omega$  TOSAs from 1Gbps to 11.3Gbps. The device contains an input buffer with programmable equalization, pulse-width adjustment, bias current and modulation current DACs, output driver with programmable deemphasis, power-on reset circuitry, bias monitor, laser current limiter, and eye-safety circuitry. A 3-wire digital interface is used to control the transmitter functions. The registers that control the device's functionality are TXCTRL, SET\_IMOD, SET\_IBIAS, IMODMAX, IBIASMAX, MODINC, BIASINC, SET\_TXEQ, SET\_PWCTRL, and SET\_TXDE.

#### Input Buffer with Programmable Equalization

The input is internally biased and terminated with  $50\Omega$  to a common-mode voltage. The first amplifier stage features a programmable equalizer for high-frequency losses including SFP connector. Equalization is controlled by the SET\_TXEQ register and TXEQ\_EN bit, TXCTRL[3] (Table 1). The TX\_POL bit in the TXCTRL register controls the polarity of TOUT+ and TOUT- vs. TIN+ and TIN-. The SET\_PWCTRL register controls the output eye crossing (Table 5). A status indicator bit (TXED) monitors the presence of an AC input signal.

#### **Bias Current DAC**

The device's bias current is optimized to provide up to 80mA of bias current into a  $5\Omega$  to  $50\Omega$  laser load with 200µA resolution. The bias current is controlled through the 3-wire digital interface using the SET\_IBIAS, IBIASMAX, and BIASINC registers.

For laser operation, the laser bias current can be set using the 9-bit SET\_IBIAS DAC. The upper 8 bits are set by the SET\_IBIAS[8:1] register, commonly used during the initialization procedure after POR. The LSB (bit 0) of SET\_IBIAS is initialized to zero after POR and can be updated using the BIASINC register. The IBIASMAX register should be programmed to a desired maximum bias current value (up to 96mA) to protect the laser. The IBIASMAX register limits the maximum SET\_IBIAS[8:1] DAC code.

After initialization the value of the SET\_IBIAS DAC register should be updated using the BIASINC register to optimize cycle time and enhance laser safety. The BIASINC register is an 8-bit register where the first 5 bits contain the increment information in two's complement notation. Increment values range from -16 to +15 LSBs. If the updated value of SET\_IBIAS[8:1] exceeds IBIASMAX[7:0], the IBIASERR warning flag is set and SET\_IBIAS[8:0] remains unchanged.

#### **Modulation Current DAC**

The modulation current from the device is optimized to provide up to 80mA of modulation current into a 5 $\Omega$  to 25 $\Omega$  differential laser load (60mA for 50 $\Omega$  laser load) with 300µA to 200µA resolution. The modulation current is controlled through the 3-wire digital interface using the SET\_IMOD, IMODMAX, MODINC, and SET\_TXDE registers.

For laser operation, the laser modulation current can be set using the 9-bit SET\_IMOD DAC. The upper 8 bits are set by the SET\_IMOD[8:1] register, commonly used during the initialization procedure after POR. The LSB (bit 0) of SET\_IMOD is initialized to zero after POR and can be updated using the MODINC register. The IMODMAX register should be programmed to a desired maximum modulation current value (up to 96mA) to protect the laser. The IMODMAX register limits the maximum SET\_IMOD[8:1] DAC code.

Table 1. Input Equalization Control Register Settings

| TXCTRL[3] |               | (FO[0.1] | DESCRIPTION                                                                                      |

|-----------|---------------|----------|--------------------------------------------------------------------------------------------------|

| TXEQ_EN   | SET_TXEQ[2:1] |          | DESCRIPTION                                                                                      |

| 0         | X X           |          | 150mVP-P to 1000mVP-P differential input amplitude (default setting)                             |

| 1         | 0 0           |          | Optimized for 1 in to 4 in FR4, 190 mVP-P to 450 mVP-P differential launch amplitude from source |

| 1         | 0 1           |          | Optimized for 4in to 6in FR4, 190mVP-P to 450mVP-P differential launch amplitude from source     |

| 1         | 1             | 0        | Optimized for 1 in to 4 in FR4, 450 mVP-P to 700 mVP-P differential launch amplitude from source |

| 1         | 1             | 1        | Optimized for 4in to 6in FR4, 450mVP-P to 700mVP-P differential launch amplitude from source     |

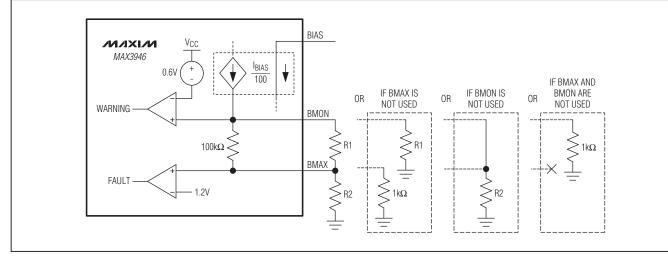

Figure 3. BMON and BMAX Circuitry

After initialization the value of the SET\_IMOD DAC register should be updated using the MODINC register to optimize cycle time and enhance laser safety. The MODINC register is an 8-bit register where the first 5 bits contain the increment information in two's complement notation. Increment values range from -16 to +15 LSBs. If the updated value of SET\_IMOD[8:1] exceeds IMODMAX[7:0], the IMODERR warning flag is set and SET\_IMOD[8:0] remains unchanged.

Modulation current sent to the laser is actually the combination of the current generated by the SET\_IMOD register and current subtracted from this by the SET\_TXDE register.

**Output Driver** The output driver is optimized for a 5 $\Omega$  to 50 $\Omega$  differential load. The output stage also features programmable deemphasis that can be set as a percentage of the modulation current. The deemphasis function is controlled by the TXDE\_MD[1] and TXDE\_MD[0] bits (TXCTRL[5:4]) and SET\_TXDE[5:0].

#### **Power-On Reset (POR)**

POR ensures that the laser is off until supply voltage has reached a specified threshold (2.75V). After POR, bias current and modulation current ramps are controlled to avoid overshoot. In the case of a POR, all registers are reset to their default values.

#### **BMON and BMAX Functions**

**MAX3946**

Current out of the BMON pin is typically 1/100th the value of the current at the BIAS pin. The total resistance to ground at BMON sets the voltage gain. An internal comparator at the BMAX pin latches a fault if the voltage on BMAX exceeds the value of 1.2V. The BMAX voltage-sense pin is connected by means of a voltage-divider to the BMON pin and ground. The full-scale range of the BMON voltage is  $1.2V \times (R1/R2 + 1)$  (Figure 3). The analog bias-current limit is determined by  $(1.2V/R2) \times 100$ .

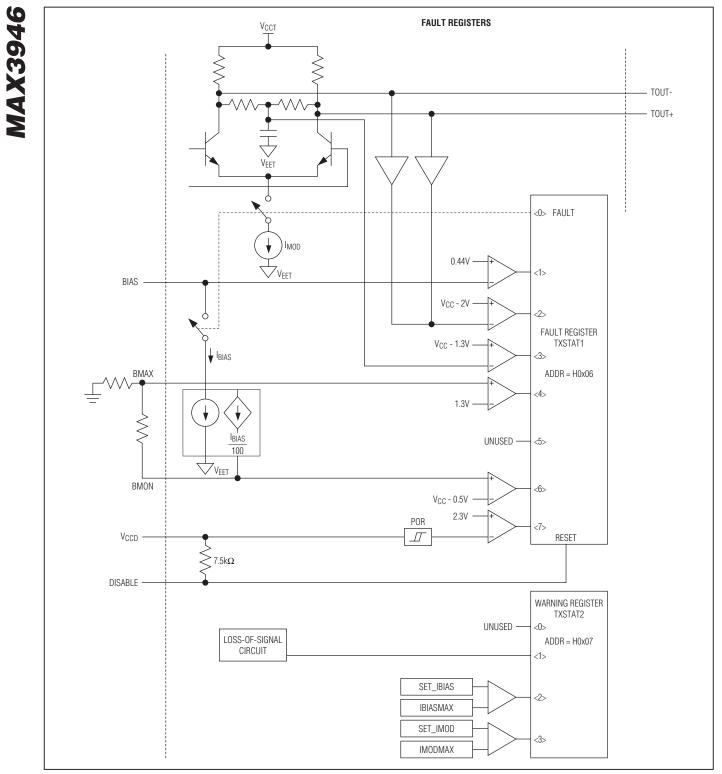

#### **Eye Safety and Output Control Circuitry**

The safety and output control circuitry includes the disable pin (DISABLE) and disable bit (TX\_EN), along with a fault indicator and fault detectors (Figure 4). The device has two types of faults, HARD FAULT and SOFT FAULT. A HARD FAULT triggers the FAULT pin, and the output to the laser is disabled. A SOFT FAULT operates as a warning, and the outputs are not disabled. Both types of faults are stored in the TXSTAT1 and TXSTAT2 registers.

The FAULT pin is a latched output that can be cleared by toggling the DISABLE pin. Toggling the DISABLE pin also clears the TXSTAT1 and TXSTAT2 registers. A single-point fault can be a short to V<sub>CC</sub> or ground. Table 2 shows the circuit response to various single-point faults.

MIXIM

Figure 4. Eye Safety Circuitry

| PIN | NAME    | SHORT TO VCC                                      | SHORT TO GROUND                                            | OPEN                           |

|-----|---------|---------------------------------------------------|------------------------------------------------------------|--------------------------------|

| 1   | VCCD    | Normal                                            | Disabled—HARD FAULT                                        | Normal (Note 3)—Redundant path |

| 2   | DISABLE | Disabled                                          | Normal (Note 1). Can only be dis-<br>abled by other means. | Disabled                       |

| 3   | FAULT   | Normal (Note 1)                                   | Normal (Note 1)                                            | Normal (Note 1)                |

| 4   | BMAX    | Disabled—HARD FAULT                               | Normal (Note 1)                                            | Disabled—HARD FAULT            |

| 5   | BMON    | Disabled—HARD FAULT                               | Normal (Note 1)                                            | Disabled—HARD FAULT            |

| 6   | VCCT    | Normal                                            | Disabled—Fault (external supply shorted) (Note 2)          | Normal (Note 3)—Redundant path |

| 7   | Vсст    | Normal                                            | Disabled—Fault (external supply shorted) (Note 2)          | Normal (Note 3)—Redundant path |

| 8   | TOUT-   | I <sub>MOD</sub> is reduced                       | Disabled—HARD FAULT                                        | I <sub>MOD</sub> is reduced    |

| 9   | TOUT-   | I <sub>MOD</sub> is reduced                       | Disabled—HARD FAULT                                        | I <sub>MOD</sub> is reduced    |

| 10  | TOUT+   | I <sub>MOD</sub> is reduced                       | Disabled—HARD FAULT                                        | I <sub>MOD</sub> is reduced    |

| 11  | TOUT+   | IMOD is reduced                                   | Disabled—HARD FAULT                                        | IMOD is reduced                |

| 12  | VCCT    | Normal                                            | Disabled—Fault (external supply shorted) (Note 2)          | Normal (Note 3)—Redundant path |

| 13  | VCCT    | Normal                                            | Disabled—Fault (external supply shorted) (Note 2)          | Normal (Note 3)—Redundant path |

| 14  | BIAS    | IBIAS is on—No fault                              | Disabled—HARD FAULT                                        | Disabled—HARD FAULT            |

| 15  | VCCD    | Normal                                            | Disabled—Fault (external supply shorted) (Note 2)          | Normal (Note 3)—Redundant path |

| 16  | CSEL    | Normal (Note 1)                                   | Normal (Note 1)                                            | Normal (Note 1)                |

| 17  | SDA     | Normal (Note 1)                                   | Normal (Note 1)                                            | Normal (Note 1)                |

| 18  | SCL     | Normal (Note 1)                                   | Normal (Note 1)                                            | Normal (Note 1)                |

| 19  | VEET    | Disabled—Fault (external supply shorted) (Note 2) | Normal                                                     | Normal (Note 3)—Redundant path |

| 20  | Vcc     | Normal                                            | Disabled—HARD FAULT (external supply shorted) (Note 2)     | Normal (Note 3)—Redundant path |

| 21  | TIN+    | SOFT FAULT                                        | SOFT FAULT                                                 | Normal (Note 1)                |

| 22  | TIN-    | SOFT FAULT                                        | SOFT FAULT                                                 | Normal (Note 1)                |

| 23  | VCC     | Normal                                            | Disabled—HARD FAULT (external supply shorted) (Note 2)     | Normal (Note 3)—Redundant path |

| 24  | VEET    | Disabled—Fault (external supply shorted) (Note 2) | Normal                                                     | Normal (Note 3)—Redundant path |

#### Table 2. Circuit Response to Single-Point Faults

Note 1: Normal—Does not affect laser power.

Note 2: Supply-shorted current is assumed to be primarily on the circuit board (outside this device), and the main supply is collapsed by the short.

Note 3: Normal in functionality, but performance could be affected.

Warning: Shorted to VCC or shorted to ground on some pins can violate the Absolute Maximum Ratings.

# **MAX3946**

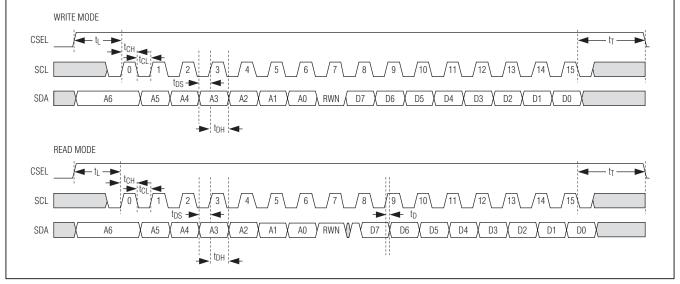

#### **3-Wire Interface**

The device implements a proprietary 3-wire digital interface. An external controller generates the clock. The 3-wire interface consists of an SDA bidirectional data line, an SCL clock signal input, and a CSEL chip-select input (active high). The external master initiates a data transfer by asserting the CSEL pin. The master starts to generate a clock signal after the CSEL pin has been set to a logic-high. All data transfers are most significant bit (MSB) first.

Protocol

Each operation consists of 16-bit transfers (15-bit address/data, 1-bit RWN). The bus master generates 16 clock cycles to SCL. All operations transfer 8 bits to the device. The RWN bit determines if the cycle is read or write. See Table 3.

**Register Addresses** The device contains 13 registers available for programming. Table 4 shows the registers and addresses.

#### Write Mode (RWN = 0)

The master generates 16 total clock cycles at SCL. The master outputs a total of 16 bits (MSB first) to the SDA line at the falling edge of the clock. The master closes the transmission by setting CSEL to 0. Figure 5 shows the interface timing.

. . . . . . . .

#### Read Mode (RWN = 1)

The master generates 16 total clock cycles at SCL. The master outputs a total of 8 bits (MSB first) to the SDA line at the falling edge of the clock. The SDA line is released after the RWN bit has been transmitted. The slave outputs 8 bits of data (MSB first) at the rising edge of the clock. The master closes the transmission by setting CSEL to 0. Figure 5 shows the interface timing.

#### Mode Control

Normal mode allows read-only instruction for all registers except MODINC and BIASINC. The MODINC and BIASINC registers can be updated during normal mode. Doing so speeds up the laser control update through the 3-wire interface by a factor of two. The normal mode is the default mode.

Setup mode allows the master to write unrestricted data into any register except the status (TXSTAT1, TXSTAT2) registers. To enter the setup mode, the MODECTRL register (address = H0x0E) must be set to H0x12. After the MODECTRL register has been set to H0x12, the next operation is unrestricted. The setup mode is automatically exited after the next operation is finished. This sequence must be repeated if further unrestricted settings are necessary.

|                                                                                                                                                               | BIT              |  |  |  |  |  |     |  |  |      |           |            |      |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|--|--|--|--|-----|--|--|------|-----------|------------|------|--|--|

| 15         14         13         12         11         10         9         8         7         6         5         4         3         2         1         0 |                  |  |  |  |  |  |     |  |  | 0    |           |            |      |  |  |

|                                                                                                                                                               | Register Address |  |  |  |  |  | RWN |  |  | Data | that is w | vritten or | read |  |  |

#### Table 4. Register Descriptions and Addresses

| ADDRESS | NAME       | FUNCTION                                      |

|---------|------------|-----------------------------------------------|

| H0x05   | TXCTRL     | Transmitter Control Register                  |

| H0x06   | TXSTAT1    | Transmitter Status Register 1                 |

| H0x07   | TXSTAT2    | Transmitter Status Register 2                 |

| H0x08   | SET_IBIAS  | Bias Current Setting Register                 |

| H0x09   | SET_IMOD   | Modulation Current Setting Register           |

| H0x0A   | IMODMAX    | Maximum Modulation Current Setting Register   |

| H0x0B   | IBIASMAX   | Maximum Bias Current Setting Register         |

| H0x0C   | MODINC     | Modulation Current Increment Setting Register |

| H0x0D   | BIASINC    | Bias Current Increment Setting Register       |

| H0x0E   | MODECTRL   | Mode Control Register                         |

| H0x0F   | SET_PWCTRL | Pulse-Width Control Register                  |

| H0x10   | SET_TXDE   | Deemphasis Control Register                   |

| H0x11   | SET_TXEQ   | Equalization Control Register                 |

Figure 5. Timing for 3-Wire Digital Interface

#### Transmitter Control Register (TXCTRL)

| Bit #         | 7 | 6 | 5          | 4          | 3       | 2       | 1      | 0     | ADDRESS |

|---------------|---|---|------------|------------|---------|---------|--------|-------|---------|

| Name          | Х | Х | TXDE_MD[1] | TXDE_MD[0] | TXEQ_EN | SOFTRES | TX_POL | TX_EN | H0x05   |

| Default Value | Х | Х | 0          | 0          | 0       | 0       | 1      | 1     | HUXUD   |

Bits 5 and 4: TXDE\_MD[1:0]. Controls the mode of the transmit output deemphasis circuitry.

00 = deemphasis is fixed at 6.25% of the modulation amplitude

01 = deemphasis is fixed at 3.125% of the modulation amplitude

10 = deemphasis is programmed by the SET\_TXDE register setting

11 = deemphasis is at its maximum of approximately 9%

Bit 3: TXEQ\_EN. Enables or disables the input equalization circuitry.

0 = disabled

1 = enabled

**Bit 2: SOFTRES.** Resets all registers to their default values (the DISABLE pin must be at a logic 1 during a write to SOFTRES for the registers to be set to their default values).

0 = normal

1 = reset

Bit 1: TX\_POL. Controls the polarity of the signal path.

0 = inverse

1 = normal

Bit 0: TX\_EN. Enables or disables the output circuitry.

0 = disabled

1 = enabled

MAX3946

Transmitter Status Register 1 (TXSTAT1)

Transmitter Status Register 2 (TXSTAT2)

| Bit #         | 7<br>(STICKY) | 6<br>(STICKY) | 5<br>(STICKY) | 4<br>(STICKY) | 3<br>(STICKY) | 2<br>(STICKY) | 1<br>(STICKY) | 0<br>(STICKY) | ADDRESS |

|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------|

| Name          | FST[7]        | FST[6]        | Х             | FST[4]        | FST[3]        | FST[2]        | FST[1]        | TX_FAULT      | H0x06   |

| Default Value | Х             | Х             | Х             | Х             | Х             | Х             | Х             | Х             | Πυχυσ   |

**Bit 7: FST[7].** When the V<sub>CCT</sub> supply voltage is below 2.3V, the POR circuitry reports a fault. Once the V<sub>CCT</sub> supply voltage is above 2.75V, the POR resets all registers to their default values and the fault is cleared.

Bit 6: FST[6]. When the voltage at BMON is above V<sub>CC</sub> - 0.5V, a SOFT FAULT is reported.

Bit 4: FST[4]. When the voltage at BMAX goes above 1.3V, a HARD FAULT is reported.

Bit 3: FST[3]. When the common-mode voltage at VTOUT± goes below VCC - 1.3V, a SOFT FAULT is reported.

Bit 2: FST[2]. When the voltage at VTOUT± goes below VCC - 0.8V, a HARD FAULT is reported.

Bit 1: FST[1]. When the BIAS voltage goes below 0.44V, a HARD FAULT is reported.

Bit 0: TX\_FAULT. Copy of a FAULT signal in FST[7:6] and FST[4:1]. A POR resets the FST bits to 0.

#### 3 2 1 0 Bit # 7 5 ADDRESS 6 4 (STICKY) (STICKY) (STICKY) (STICKY) Name Х Х Х Х IMODERR **IBIASERR** TXED Х H0x07 Х Х Default Value Х Х Х Х Х Х

**Bit 3: IMODERR.** Any attempt to modify SET\_IMOD[8:1] above IMODMAX[7:0] flags a warning at IMODERR. (See the *Programming Modulation Current* section.)

**Bit 2: IBIASERR.** Any attempt to modify SET\_IBIAS[8:1] above IBIASMAX[7:0] flags a warning at IBIASERR. (See the *Programming Bias Current* section.)

Bit 1: TXED. This indicates the absence of an AC signal at the transmit input.

|               |                        |                  |                  |                  |                  | Bias Curr        | ent Setting      | Register (       | SET_IBIAS) |

|---------------|------------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------|

| Bit #         | 7                      | 6                | 5                | 4                | 3                | 2                | 1                | 0                | ADDRESS    |

| Name          | SET_IBIAS<br>[8] (MSB) | SET_IBIAS<br>[7] | SET_IBIAS<br>[6] | SET_IBIAS<br>[5] | SET_IBIAS<br>[4] | SET_IBIAS<br>[3] | SET_IBIAS<br>[2] | SET_IBIAS<br>[1] | H0x08      |

| Default Value | 0                      | 0                | 0                | 0                | 0                | 0                | 0                | 1                |            |

**Bits 7 to 0: SET\_IBIAS[8:1].** The bias current DAC is controlled by a total of 9 bits. The SET\_IBIAS[8:1] bits are used to set the bias current with even denominations from 0 to 510 bits. The LSB (SET\_IBIAS[0]) is controlled by the BIASINC register and is used to set the odd denominations in the SET\_IBIAS[8:0]. Any direct write to SET\_IBIAS[8:1] resets the LSB.

#### Modulation Current Setting Register (SET\_IMOD)

| Bit #         | 7         | 6        | 5        | 4        | 3        | 2        | 1        | 0        | ADDRESS |

|---------------|-----------|----------|----------|----------|----------|----------|----------|----------|---------|

| Name          | SET_IMOD  | SET_IMOD | SET_IMOD | SET_IMOD | SET_IMOD | SET_IMOD | SET_IMOD | SET_IMOD |         |

| Name          | [8] (MSB) | [7]      | [6]      | [5]      | [4]      | [3]      | [2]      | [1]      | H0x09   |

| Default Value | 0         | 0        | 0        | 0        | 0        | 1        | 0        | 0        |         |

**Bits 7 to 0: SET\_IMOD[8:1].** The modulation current DAC is controlled by a total of 9 bits. The SET\_IMOD[8:1] bits are used to set the modulation current with even denominations from 0 to 510 bits. The LSB (SET\_IMOD[0]) is controlled by the MODINC register and is used to set the odd denominations in the SET\_IMOD[8:0]. Any direct write to SET\_IMOD[8:1] resets the LSB.

#### Maximum Modulation Current Setting Register (IMODMAX)

Maximum Bias Current Setting Register (IBIASMAX)

Modulation Current Increment Setting Register (MODINC)

| Bit #         | 7         | 6       | 5       | 4       | 3       | 2       | 1       | 0         | ADDRESS |

|---------------|-----------|---------|---------|---------|---------|---------|---------|-----------|---------|

| Nomo          | IMODMAX   | IMODMAX | IMODMAX | IMODMAX | IMODMAX | IMODMAX | IMODMAX | IMODMAX   |         |

| Name          | [7] (MSB) | [6]     | [5]     | [4]     | [3]     | [2]     | [1]     | [0] (LSB) | H0x0A   |

| Default Value | 0         | 0       | 1       | 0       | 0       | 0       | 0       | 0         |         |

**Bits 7 to 0: IMODMAX[7:0].** The IMODMAX register is an 8-bit register that can be used to limit the maximum modulation current. IMODMAX[7:0] is continuously compared to SET\_IMOD[8:1]. Any attempt to modify SET\_IMOD[8:1] above IMODMAX[7:0] is ignored and flags a warning at IMODERR.

|               |           |          |          |          |          |          |          | ,         |         |

|---------------|-----------|----------|----------|----------|----------|----------|----------|-----------|---------|

| Bit #         | 7         | 6        | 5        | 4        | 3        | 2        | 1        | 0         | ADDRESS |

| Name          | IBIASMAX  | IBIASMAX | IBIASMAX | IBIASMAX | IBIASMAX | IBIASMAX | IBIASMAX | IBIASMAX  |         |

| Name          | [7] (MSB) | [6]      | [5]      | [4]      | [3]      | [2]      | [1]      | [0] (LSB) | H0x0B   |

| Default Value | 0         | 0        | 1        | 0        | 0        | 0        | 0        | 0         |         |

**Bits 7 to 0: IBIASMAX[7:0].** The IBIASMAX register is an 8-bit register that can be used to limit the maximum bias current. IBIASMAX[7:0] is continuously compared to SET\_IBIAS[8:1]. Any attempt to modify SET\_IBIAS[8:1] above IBIASMAX[7:0] is ignored and flags a warning at IBIASERR.

|               |                       |   |   |                     |               |               |               | 5 5                 | ( = -/  |

|---------------|-----------------------|---|---|---------------------|---------------|---------------|---------------|---------------------|---------|

| Bit #         | 7                     | 6 | 5 | 4                   | 3             | 2             | 1             | 0                   | ADDRESS |

| Name          | SET_IMOD<br>[0] (LSB) | Х | Х | MODINC<br>[4] (MSB) | MODINC<br>[3] | MODINC<br>[2] | MODINC<br>[1] | MODINC<br>[0] (LSB) | H0x0C   |

| Default Value | 0                     | 0 | 0 | 0                   | 0             | 0             | 0             | 0                   |         |

Bit 7: SET\_IMOD[0]. This is the LSB of the SET\_IMOD[8:0] bits. This bit can only be updated by the use of MODINC[4:0].

**Bits 4 to 0: MODINC[4:0].** This string of bits is used to increment or decrement the modulation current. When written to, the SET\_IMOD[8:0] bits are updated. MODINC[4:0] are a two's complement string.

MAX3946

| Bias Current Increment Setting Register (BIASINC) |

|---------------------------------------------------|

|---------------------------------------------------|

| Bit #         | 7                      | 6 | 5 | 4                    | 3              | 2              | 1              | 0                    | ADDRESS |

|---------------|------------------------|---|---|----------------------|----------------|----------------|----------------|----------------------|---------|

| Name          | SET_IBIAS<br>[0] (LSB) | Х | Х | BIASINC<br>[4] (MSB) | BIASINC<br>[3] | BIASINC<br>[2] | BIASINC<br>[1] | BIASINC<br>[0] (LSB) | H0x0D   |

| Default Value | 0                      | 0 | 0 | 0                    | 0              | 0              | 0              | 0                    |         |

Bit 7: SET\_IBIAS[0]. This is the LSB of the SET\_IBIAS[8:0] bits. This bit can only be updated by the use of BIASINC[4:0].

**Bits 4 to 0: BIASINC[4:0].** This string of bits is used to increment or decrement the bias current. When written to, the SET\_IBIAS[8:0] bits are updated. BIASINC[4:0] are a two's complement string.

#### Mode Control Register (MODECTRL)

| Bit #         | 7         | 6        | 5        | 4        | 3        | 2        | 1        | 0         | ADDRESS |

|---------------|-----------|----------|----------|----------|----------|----------|----------|-----------|---------|

| Nomo          | MODECTRL  | MODECTRL | MODECTRL | MODECTRL | MODECTRL | MODECTRL | MODECTRL | MODECTRL  |         |

| Name          | [7] (MSB) | [6]      | [5]      | [4]      | [3]      | [2]      | [1]      | [0] (LSB) | H0x0E   |

| Default Value | 0         | 0        | 0        | 0        | 0        | 0        | 0        | 0         |         |

**Bits 7 to 0: MODECTRL[7:0].** The MODECTRL register enables the user to switch between normal and setup modes. The setup mode is achieved by setting this register to H0x12. MODECTRL must be updated before each write operation. Exceptions are MODINC and BIASINC, which can be updated in normal mode.

#### Pulse-Width Control Register (SET\_PWCTRL)

| Bit #         | 7 | 6 | 5 | 4 | 3                       | 2                 | 1                 | 0                       | ADDRESS |

|---------------|---|---|---|---|-------------------------|-------------------|-------------------|-------------------------|---------|

| Name          | Х | Х | Х | Х | SET_PWCTRL<br>[3] (MSB) | SET_PWCTRL<br>[2] | SET_PWCTRL<br>[1] | SET_PWCTRL<br>[0] (LSB) | H0x0F   |

| Default Value | Х | Х | Х | Х | 0                       | 0                 | 0                 | 0                       |         |

Bits 3 to 0: SET\_PWCTRL[3:0]. This is a 4-bit register used to control the eye crossing by adjusting the pulse width.

#### Deemphasis Control Register (SET\_TXDE)

| Bit #         | 7 | 6         | 5        | 4        | 3        | 2        | 1         | 0        | ADDRESS |

|---------------|---|-----------|----------|----------|----------|----------|-----------|----------|---------|

| Name          | X | X         | SET_TXDE | SET_TXDE | SET_TXDE | SET_TXDE | SET_TXDE  | SET_TXDE |         |

|               | ~ | [5] (MSB) | [4]      | [3]      | [2]      | [1]      | [0] (LSB) | H0x10    |         |

| Default Value | Х | Х         | 0        | 0        | 0        | 0        | 0         | 1        |         |

**Bits 5 to 0: SET\_TXDE[5:0].** This is a 6-bit register used to control the amount of deemphasis on the transmitter output. When calculating the total modulation current, the amount of deemphasis must be taken into account. The deemphasis is set as a percentage of modulation current.

|               |   |   |   |   |   | Equalizati      | on Control      | Register ( | SET_TXEQ) |

|---------------|---|---|---|---|---|-----------------|-----------------|------------|-----------|

| Bit #         | 7 | 6 | 5 | 4 | 3 | 2               | 1               | 0          | ADDRESS   |

| Name          | Х | Х | Х | Х | Х | SET_TXEQ<br>[2] | SET_TXEQ<br>[1] | Х          | H0x11     |

| Default Value | Х | Х | Х | Х | Х | 0               | 0               | Х          |           |

**Bits 2 to 1: SET\_TXEQ[2:1].** These 2 bits are used to control the amount of equalization on the transmitter input. See Table 1 for more information.

#### \_Design Procedure

#### **Programming Bias Current**

- 1) IBIASMAX[7:0] = Maximum\_Bias\_Current\_Value

- 2) SET\_IBIAS<sub>i</sub>[8:1] = Initial\_Bias\_Current\_Value

**Note:** The total bias current is calculated using the SET\_IBIAS[8:0] DAC value. SET\_IBIAS[8:1] are the bits that can be manually written. SET\_IBIAS[0] can only be updated using the BIASINC register.

When implementing an APC loop it is recommended to use the BIASINC register, which guarantees the fastest bias current update.

- 3) BIASINC<sub>i</sub>[4:0] = New\_Increment\_Value

- 4) If (SET\_IBIAS\_i[8:1]  $\leq$  IBIASMAX[7:0]), then (SET\_IBIAS\_i[8:0] = SET\_IBIAS\_{i-1}[8:0] + BIASINC\_i[4:0])

- 5) Else (SET\_IBIAS<sub>i</sub>[8:0] = SET\_IBIAS<sub>i</sub>-1[8:0])

The total bias current can be calculated as follows:

6)  $I_{BIAS} = [SET_IBIAS_i[8:0] + 16] \times 200 \mu A$

#### **Programming Modulation Current**

- 1) IMODMAX[7:0] = Maximum\_Modulation\_Current\_Value

- 2) SET\_IMODi[8:1] = Initial\_Modulation\_Current\_Value x 1.06

**Note:** The total modulation laser current is calculated using the SET\_IMOD[8:0] DAC value and the SET\_TXDE register value. SET\_IMOD[8:1] are the bits that can be manually written. SET\_IMOD[0] can only be updated using the MODINC register.

When implementing modulation compensation, it is recommended to use the MODINC register, which guarantees the fastest modulation current update.

- 3) MODINC<sub>i</sub>[4:0] = New\_Increment\_Value

- 4) If (SET\_IMODi[8:1]  $\leq$  IMODMAX[7:0]), then (SET\_IMOD\_i[8:0] = SET\_IMOD\_i-1[8:0] + MODINCi[4:0])

- 5) Else (SET\_IMOD<sub>i</sub>[8:0] = SET\_IMOD<sub>i</sub>-1[8:0])

The following equations give the modulation current (peak-to-peak) seen at the laser when driven differentially. REXTD is the differential load impedance of the laser plus any added series resistance.

$$I_{MOD} = \begin{bmatrix} 0.3mA(SET\_IMOD[8:0]+16) \\ -0.15mA(SET\_IMOD[8:3]+2) \end{bmatrix} \times \frac{50\Omega}{50\Omega + R_{LD}}$$

6b) TXDE\_MD[1:0] = 01, then

$$I_{MOD} = \begin{bmatrix} 0.3 \text{mA}(\text{SET}_{IMOD}[8:0] + 16) \\ -0.15 \text{mA}(\text{SET}_{IMOD}[8:4] + 1) \end{bmatrix} \times \frac{50\Omega}{50\Omega + R_{LD}}$$

6c) TXDE\_MD[1:0] = 10, then set SET\_TXDE[5:0] can be set to any value ≥ SET\_IMOD[8:4] and

$$I_{MOD} = \begin{bmatrix} 0.3 \text{mA}(\text{SET}_{IMOD}[8:0] + 16) \\ -0.15 \text{mA}(\text{SET}_{TXDE}[5:0] + 1) \end{bmatrix} \times \frac{50\Omega}{50\Omega + R_{LD}}$$

When SET\_TXDE[5:0] is increased, the deemphasis current increases and the overall peak-to-peak modulation current decreases. This effect saturates when SET\_TXDE[5:0] =  $0.2 \times (SET_IMOD[8:0] + 16) - 1$ , and further increases to SET\_TXDE[5:0] do not increase the deemphasis current.

6d) TXDE\_MD[1:0] = 11, then

$$I_{MOD} = 0.9 \times \left[ 0.3 \text{mA} \left( \text{SET}_{IMOD} \left[ 8:0 \right] + 16 \right) \right] \times \frac{50\Omega}{50\Omega + R_{LD}}$$

**Note:** When TXDE\_MD[1:0] = 10 and the SET\_TXDE register is set by the user, the minimum allowed deemphasis is 3% and the maximum is 10%. These limits are internally set by the MAX3946.

#### **Programming Transmit Output Deemphasis**

- 1) TXDE\_MD[1:0] = Transmit\_Deemphasis\_Mode

- 2) SET\_TXDE[5:0] = Transmit\_Deemphasis\_Value. If TXDE\_MD[1:0] = 00, 01, or 11, the value of SET\_TXDE is automatically set by the device and there is no need to enter data to SET\_TXDE.

For Transmit\_Deemphasis\_Mode:

00 = deemphasis is fixed at 6% of the modulation amplitude (the device controls the SET\_TXDE value), default setting

01 = deemphasis is fixed at 3% of the modulation amplitude (the device controls the SET\_TXDE value)

10 = deemphasis is programmed by the SET\_TXDE register setting

11 = deemphasis is at its maximum of approximately 9% (the device controls the SET\_TXDE value)

#### **Programming Pulse-Width Control**

The eye crossing at the Tx output can be adjusted using the SET\_PWCTRL register. Table 5 shows these settings. The sign of the number specifies the direction of

# Table 5. Eye-Crossing Settings forSET\_PWCTRL

| SET_PWCTRL[3:0] | PWD | SET_PWCTRL[3:0] | PWD |

|-----------------|-----|-----------------|-----|

| 1000            | -7  | 0111            | 8   |

| 1001            | -6  | 0110            | 7   |

| 1010            | -5  | 0101            | 6   |

| 1011            | -4  | 0100            | 5   |

| 1100            | -3  | 0011            | 4   |

| 1101            | -2  | 0010            | 3   |

| 1110            | -1  | 0001            | 2   |

| 1111            | 0   | 0000            | 1   |

#### pulse-width distortion. The code of 1111 corresponds to a balanced state for differential output. The pulse-width distortion is bidirectional around the balanced state (see the *Typical Operating Characteristics* section).

#### **Applications Information**

#### Laser Safety and IEC 825

Using the MAX3946 laser driver alone does not ensure that a transmitter design is compliant with IEC 825. The entire transmitter circuit and component selections must be considered. Each user must determine the level of fault tolerance required by the application, recognizing that Maxim products are neither designed nor authorized for use as components in systems intended for surgical implant into the body, for applications intended to support or sustain life, or for any other application in which the failure of a Maxim product could create a situation where personal injury or death could occur.

| REGISTER<br>FUNCTION/<br>ADDRESS | REGISTER<br>NAME | NORMAL<br>MODE | SETUP<br>MODE | BIT<br>NUMBER/<br>TYPE | BIT NAME   | DEFAULT<br>VALUE | NOTES                                                         |

|----------------------------------|------------------|----------------|---------------|------------------------|------------|------------------|---------------------------------------------------------------|

|                                  |                  | R              | RW            | 5                      | TXDE_MD[1] | 0                | MSB deemphasis mode                                           |

|                                  |                  | R              | RW            | 4                      | TXDE_MD[0] | 0                | LSB deemphasis mode                                           |

| Transmitter                      |                  | R              | RW            | 3                      | TXEQ_EN    | 0                | Input equalization<br>0: disabled, 1: enabled                 |

| Control Register<br>Address =    | TXCTRL           | R              | RW            | 2                      | SOFTRES    | 0                | Global digital reset                                          |

| H0x05                            |                  | R              | RW            | 1                      | TX_POL     | 1                | Tx polarity<br>0: inverse, 1: normal                          |

|                                  |                  | R              | RW            | 0                      | TX_EN      | 1                | Tx control<br>0: disabled, 1: enabled                         |

|                                  | TXSTAT1          | R              | R             | 7 (sticky)             | FST[7]     | Х                | TX_POR→TX_VCC low-<br>limit violation                         |

|                                  |                  | R              | R             | 6 (sticky)             | FST[6]     | Х                | BMON open/shorted to VCC                                      |

| Transmitter                      |                  | R              | R             | 4 (sticky)             | FST[4]     | X                | BMAX current exceeded<br>or open/short to ground              |

| Status Register 1<br>Address =   |                  | R              | R             | 3 (sticky)             | FST[3]     | X                | VTOUT+/ common-mode<br>low-limit                              |

| H0x06                            |                  | R              | R             | 2 (sticky)             | FST[2]     | Х                | VTOUT+/- low-limit violation                                  |

|                                  |                  | R              | R             | 1 (sticky)             | FST[1]     | X                | BIAS open or shorted to ground                                |

|                                  |                  | R              | R             | 0 (sticky)             | TX_FAULT   | Х                | Copy of FAULT signal<br>in case POR bits 6 to 1<br>reset to 0 |

#### Table 6. Register Summary

#### Table 6. Register Summary (continued)

| REGISTER<br>FUNCTION/<br>ADDRESS        | REGISTER<br>NAME | NORMAL<br>MODE         | SETUP<br>MODE | BIT<br>NUMBER/<br>TYPE | BIT NAME     | DEFAULT<br>VALUE | NOTES                                  |

|-----------------------------------------|------------------|------------------------|---------------|------------------------|--------------|------------------|----------------------------------------|

| Transmitter                             |                  | R                      | R             | 3 (sticky)             | IMODERR      | х                | Warning increment result<br>> IMODMAX  |

| Status Register 2<br>Address =<br>H0x07 | TXSTAT2          | R                      | R             | 2 (sticky)             | IBIASERR     | Х                | Warning increment result<br>> IBIASMAX |

|                                         |                  | R                      | R             | 1 (sticky)             | TXED         | Х                | Tx edge detection                      |

|                                         |                  | R                      | RW            | 7                      | SET_IBIAS[8] | 0                | MSB bias DAC                           |

|                                         |                  | R                      | RW            | 6                      | SET_IBIAS[7] | 0                |                                        |