### MAX40075/MAX40088

# 10MHz/42MHz Low-Noise, Low-Bias Op Amps

### **General Description**

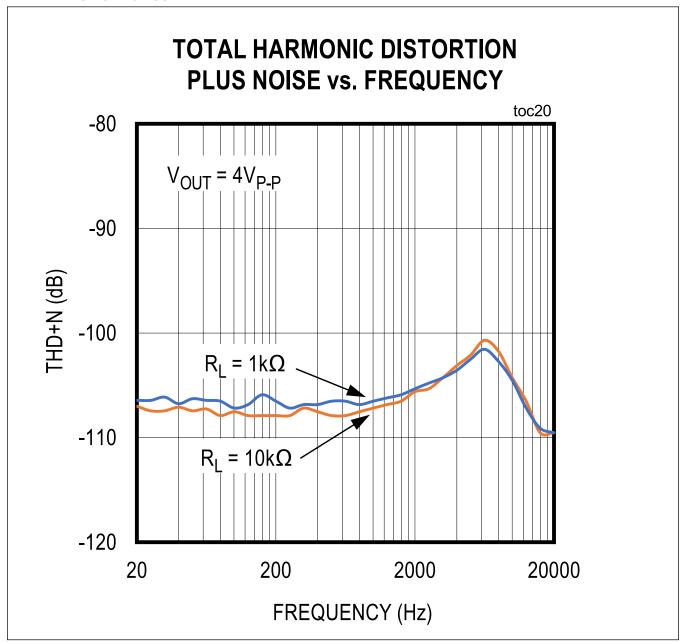

The MAX40075/MAX40088 are wideband, low-noise, low-input bias current operational amplifiers offering rail-to-rail outputs and single-supply operation down to 2.7V. They draw 2.2mA of quiescent supply current per amplifier when enabled and have ultra-low distortion (0.0002% THD+N), as well as low input voltage-noise density (4.2nV/ $\sqrt{\rm Hz}$ ) and low input current-noise density (0.5fA/ $\sqrt{\rm Hz}$ ). The low input bias current and low noise together with the wide bandwidth suit transimpedance amplifiers and imaging applications.

For power conservation, the MAX40075/MAX40088 offer a low-power shutdown mode that reduces supply current to 0.1µA and places the amplifiers outputs into a high impedance state. These amplifiers have outputs which swing rail-to-rail and their input common-mode voltage range includes ground. The MAX40075 is unity-gain stable with a gain-bandwidth product of 10MHz. The MAX40088 is gain-of-5 stable with a gain-bandwidth product of 42MHz.

## **Applications**

- ADC Buffers

- DAC Output Amplifiers

- Low-Noise Microphone/Preamplifiers

- Digital Scales

- Strain Gauges/Sensor Amplifiers

- Transimpedance Amplifiers

- Medical Instrumentation

- Automotive Power Train

#### **Benefits and Features**

- Low Input Voltage-Noise Density: 4.2nV/√Hz at 30kHz

- Low Input Current-Noise Density: 0.5fA/√Hz

- Low Input Bias Current: <1pA (typ)</li>

- Low Distortion: 0.00035% or -109dB THD+N (1kΩ Load)

- Single-Supply Operation from +2.7V to +5.5V

- Input Common-Mode Voltage Range Includes Ground

- Rail-to-Rail Output Swings with a 1kΩ Load

- 10MHz GBW Product, Unity-Gain Stable (MAX40075 Only)

- 42MHz GBW Product, Gain ≥ 5V/V (MAX40088 Only)

- Excellent DC Characteristics: Input V<sub>OS</sub> ≤ 30µV

- Low-Power Shutdown Mode: Reduces Supply Current to ≤1µA

- Available in Space-Saving 6-Bump WLP and 6-Pin SOT23 Packages

- AEC-Q100 Qualified, See <u>Ordering Information</u>

Ordering Information appears at end of data sheet.

## **THD+N Performance**

## **Absolute Maximum Ratings**

| Input Differential Voltage                                 |                               |

|------------------------------------------------------------|-------------------------------|

| MAX40075/MAX40088 (continuous)                             |                               |

| MAX40075/MAX40088 (transient, 10s)                         | 6V to +6V                     |

| Power-Supply Voltage (V <sub>DD</sub> to V <sub>SS</sub> ) | 0.3V to +6V                   |

| Analog Input Voltage (IN+, IN-)VSS -0                      | 0.3V to V <sub>DD</sub> +0.3V |

| SHDN Input Voltage (SHDN)                                  | V <sub>SS</sub> 0.3V to +6V   |

| Continuous Input Current (IN+, IN-)                        | ±20mA                         |

| Output Short-Circuit Duration to Either Supply.            | Continuous                    |

| Operating Temperature Range Continuous Power Dissipation |                |

|----------------------------------------------------------|----------------|

| 6-Pin SOT23 (derate 8.7mW/°C at +70°C)                   |                |

| 6-Bump WLP (derate 10.19mW/°C at +70°C)                  | 815mW          |

| Storage Temperature Range                                | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                        | +300°C         |

| Soldering Temperature (reflow)                           | +260°C         |

|                                                          |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

### **6 SOT23**

| Package Code                           | U6+1, U6+1A    |

|----------------------------------------|----------------|

| Outline Number                         | <u>21-0058</u> |

| Land Pattern Number                    | <u>90-0175</u> |

| THERMAL RESISTANCE, SINGLE-LAYER BOARD |                |

| Junction to Ambient (θ <sub>JA</sub> ) | N/A            |

| Junction to Case (θ <sub>JC</sub> )    | 80°C/W         |

| THERMAL RESISTANCE, FOUR-LAYER BOARD   |                |

| Junction to Ambient (θ <sub>JA</sub> ) | 115°C/W        |

| Junction to Case (θ <sub>JC</sub> )    | 80°C/W         |

### 6 WLP

| Package Code                           | N60F1+1                        |  |  |  |

|----------------------------------------|--------------------------------|--|--|--|

| Outline Number                         | <u>21-100174</u>               |  |  |  |

| Land Pattern Number                    | Refer to Application Note 1891 |  |  |  |

| THERMAL RESISTANCE, SINGLE-LAYER BOARD |                                |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 98.06°C/W                      |  |  |  |

| Junction to Case (θ <sub>JC</sub> )    | N/A                            |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

### **Electrical Characteristics**

$(V_{DD} = +5V, V_{SS} = 0V, V_{CM} = 2.5V, \overline{SHDN} = V_{DD}, V_{OUT} = V_{DD}/2, R_L = tied to V_{DD}/2, T_A = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ . (Note 1)

| PARAMETER            | SYMBOL   | CONDITIONS              | MIN | TYP | MAX | UNITS |

|----------------------|----------|-------------------------|-----|-----|-----|-------|

| Supply Voltage Range | $V_{DD}$ | Guaranteed by PSRR test | 2.7 |     | 5.5 | V     |

# **Electrical Characteristics (continued)**

$(V_{DD} = +5V, V_{SS} = 0V, V_{CM} = 2.5V, \overline{SHDN} = V_{DD}, V_{OUT} = V_{DD}/2, R_L = tied to V_{DD}/2, T_A = -40^{\circ}C to +125^{\circ}C, unless otherwise noted.$  Typical values are at  $T_A = +25^{\circ}C$ . (Note 1)

| PARAMETER                                   | SYMBOL                                | CONDITIONS                                                                | MIN  | TYP  | MAX                      | UNITS |  |

|---------------------------------------------|---------------------------------------|---------------------------------------------------------------------------|------|------|--------------------------|-------|--|

| Quiescent Supply                            |                                       | V <sub>DD</sub> = 3.3V                                                    |      | 2.2  | 3.0                      | A     |  |

| Current, per Amplifier                      | l <sub>DD</sub>                       | V <sub>DD</sub> = 5V                                                      |      | 2.5  | 3.3                      | mA    |  |

| Power-Up Time                               |                                       | V <sub>DD</sub> = 0 to 5V step, V <sub>OUT</sub> = 2.5V ±1%               |      | 13   |                          | μs    |  |

| Shutdown Supply<br>Current                  | ISHDN                                 | Over temperature, to +125°C                                               |      | 0.4  | 1.7                      | μA    |  |

| Input Offset Voltage                        | V <sub>OS</sub>                       | At +25°C                                                                  |      | 30   | 150                      | μV    |  |

| input Onset voltage                         | VOS                                   | Over the full temperature range                                           |      |      | 450                      | μν    |  |

| Input Offset Drift                          | V <sub>OS</sub> -TC                   | Over temperature, to +125°C                                               |      | 0.3  | 3                        | μV/°C |  |

| Input Bias Current ( <i>Note</i> <u>2</u> ) | Ι <sub>Β</sub>                        |                                                                           |      | 1    | 2300                     | pA    |  |

| Input Offset Current (Note 2)               | los                                   |                                                                           |      | 0.2  | 500                      | pA    |  |

| Differential Input<br>Resistance            | R <sub>IN</sub>                       |                                                                           |      | 1000 |                          | GΩ    |  |

| Input Capacitance                           | C <sub>IN</sub>                       | Either input, over entire CMIR                                            |      | 10   |                          | pF    |  |

| Input Common-Mode                           | V <sub>IN+</sub> , V <sub>IN-</sub>   | Guaranteed by CMRR test, at +25°C                                         | -0.2 |      | V <sub>DD</sub> -<br>1.5 |       |  |

| Range                                       |                                       | Guaranteed by CMRR test, full temperature range                           | -0.1 |      | V <sub>DD</sub> -<br>1.5 | V     |  |

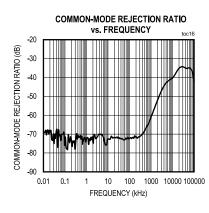

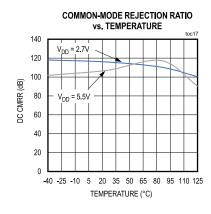

| Common-Mode                                 | CMRR                                  | DC, -0.2V < CMIR < V <sub>DD</sub> - 1.5V, at +25°C                       | 90   | 109  |                          | 4D    |  |

| Rejection Ratio                             |                                       | DC, -0.1V < CMIR < V <sub>DD</sub> - 1.5V, full temperature range         | 89   |      |                          | - dB  |  |

| Common-Mode<br>Rejection Ratio, AC          | CMRR                                  | 100mV <sub>P-P</sub> 1MHz, with DC in 0V to V <sub>DD</sub> - 2V range    |      | 60   |                          | dB    |  |

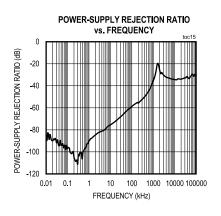

| Power-Supply Rejection Ratio, DC            | PSRR                                  | DC, 2.7V < V <sub>DD</sub> < 5.5V                                         | 90   | 107  |                          | dB    |  |

| Power-Supply Rejection Ratio, AC            | PSRR                                  | AC, 100mV <sub>P-P</sub> 1MHz, superimposed on V <sub>DD</sub>            |      | 40   |                          | dB    |  |

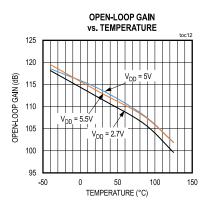

|                                             | oop Gain A <sub>OL</sub>              | $R_L$ = 10kΩ to $V_{DD}/2$ , $V_{OUT}$ = 200mV to $V_{DD}$ -250mV         | 93   | 114  |                          |       |  |

| Open-Loop Gain                              |                                       | $R_L$ = 1k $\Omega$ to $V_{DD}/2$ , $V_{OUT}$ = 200mV to $V_{DD}$ -250mV  | 87   | 109  |                          | dB    |  |

|                                             |                                       | $R_L$ = 500 $\Omega$ to $V_{DD}/2$ , $V_{OUT}$ = 200mV to $V_{DD}$ -250mV | 85   | 107  |                          |       |  |

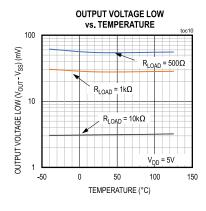

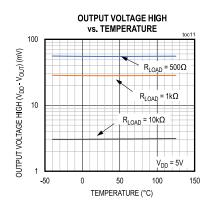

| Output Voltage Swing<br>High                | ving V <sub>DD</sub> -V <sub>OH</sub> | $R_L = 10k\Omega$ to $V_{DD}/2$ , $V_{DD} - V_{OH}$                       |      | 3    | 10                       | mV    |  |

|                                             |                                       | $R_L = 1k\Omega$ to $V_{DD}/2$ , $V_{DD} - V_{OH}$                        |      | 30   | 60                       |       |  |

|                                             |                                       | $R_L = 500\Omega$ to $V_{DD}/2$ , $V_{DD} - V_{OH}$                       |      | 60   | 120                      |       |  |

| 0.45.417/5/6                                |                                       | $R_L$ = 10k $\Omega$ to $V_{DD}/2$ , $V_{DD}$ - $V_{SS}$                  |      | 3    | 10                       |       |  |

| Output Voltage Swing Low                    | ge Swing V <sub>OL</sub>              | $R_L = 1k\Omega$ to $V_{DD}/2$ , $V_{OL} - V_{SS}$                        |      | 30   | 60                       | mV    |  |

|                                             |                                       | $R_L = 500\Omega$ to $V_{DD}/2$ , $V_{OL} - V_{SS}$                       |      | 60   | 120                      |       |  |

# **Electrical Characteristics (continued)**

$(V_{DD} = +5V, V_{SS} = 0V, V_{CM} = 2.5V, \overline{SHDN} = V_{DD}, V_{OUT} = V_{DD}/2, R_L = tied \ to \ V_{DD}/2, T_A = -40^{\circ}C \ to \ +125^{\circ}C, unless \ otherwise \ noted.$  Typical values are at  $T_A = +25^{\circ}C$ . (Note 1)

| PARAMETER                                | SYMBOL            | CONDITIONS                                                                       | MIN                      | TYP  | MAX                      | UNITS             |  |

|------------------------------------------|-------------------|----------------------------------------------------------------------------------|--------------------------|------|--------------------------|-------------------|--|

| Short-Circuit Current                    | I <sub>SC</sub>   | Shorted to either power supply                                                   |                          | 48   |                          | mA                |  |

| Output Leakage Current<br>When Shut Down |                   | V <sub>SS</sub> < V <sub>OUT</sub> < V <sub>DD</sub>                             |                          | 0.01 | 1                        | μA                |  |

| Shutdown Input Low<br>Level              |                   |                                                                                  |                          |      | 0.3 x<br>V <sub>DD</sub> | V                 |  |

| Shutdown Input High<br>Level             |                   |                                                                                  | 0.7 x<br>V <sub>DD</sub> |      |                          | V                 |  |

| Shutdown Input Bias                      |                   |                                                                                  |                          | 0.01 | 1                        | μA                |  |

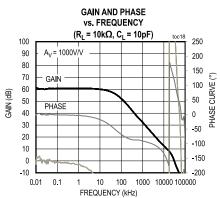

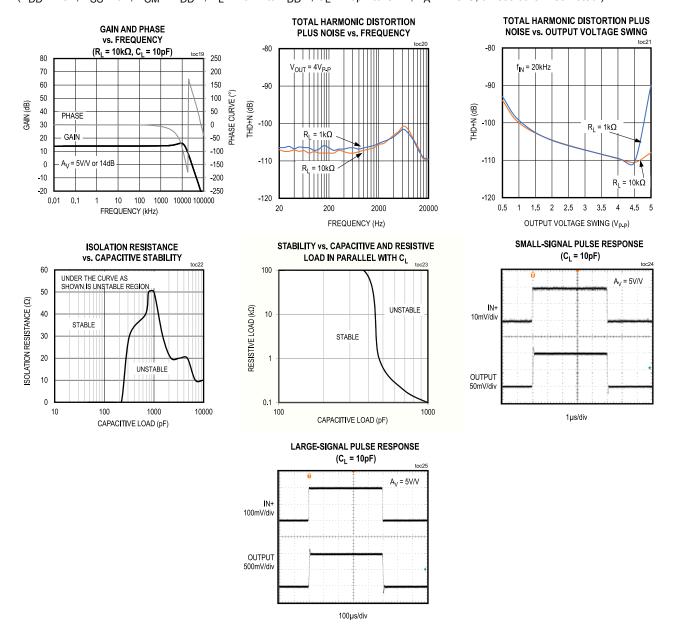

| -3dB Bandwidth (BW)                      |                   | Unity-gain version, A <sub>V</sub> = +1                                          |                          | 10   |                          | MHz               |  |

| -Sub balluwlutii (bvv)                   |                   | Gain of 5 stable, A <sub>V</sub> = +5                                            |                          | 42   |                          | IVITZ             |  |

| Dhoop Morgin                             | Φ.                | Unity-gain version, A <sub>V</sub> = +1                                          |                          | 70   |                          | 0                 |  |

| Phase Margin                             | Φ <sub>m</sub>    | Gain of 5 stable, A <sub>V</sub> = +5                                            | 80                       |      |                          |                   |  |

| Gain Margin                              | GM                |                                                                                  |                          | 12   |                          | dB                |  |

| Slew Rate                                | SR                | Unity-gain version, A <sub>V</sub> = +1                                          | 3                        |      | \//u0                    |                   |  |

| Siew Rate                                |                   | Gain of 5 stable, A <sub>V</sub> = +5                                            |                          | 10   |                          | V/µs              |  |

| Cottling Time                            |                   | Unity-gain version, A <sub>V</sub> = +1, to 0.01%,<br>V <sub>OUT</sub> = 2V step |                          | 2    |                          |                   |  |

| Settling Time                            |                   | Gain of 5 stable, $A_V = +5$ , to 0.01%, $V_{OUT} = 2V$ step                     |                          | 2    |                          | μs                |  |

| Stable Capacitive Load                   | C <sub>LOAD</sub> | Guaranteed stability over all conditions                                         |                          | 50   |                          | pF                |  |

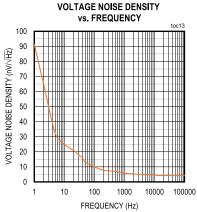

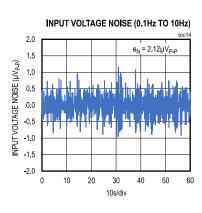

| Integrated 1/f Input<br>Voltage Noise    |                   | 0.1Hz to 10Hz                                                                    |                          | 1.7  |                          | μV <sub>P-P</sub> |  |

| Input Voltage Noise<br>Density           |                   | f = 10Hz                                                                         |                          | 260  |                          |                   |  |

|                                          | $V_N$             | f = 1kHz                                                                         |                          | 5.5  |                          | nV/√Hz            |  |

|                                          |                   | f = 30kHz                                                                        | 4.2                      |      |                          | 7                 |  |

| Input Current Noise<br>Density           | I <sub>N</sub>    | f = 1kHz                                                                         |                          | 0.5  |                          | fA/√Hz            |  |

# **Electrical Characteristics (continued)**

$(V_{DD}$  = +5V,  $V_{SS}$  = 0V,  $V_{CM}$  = 2.5V,  $\overline{SHDN}$  =  $V_{DD}$ ,  $V_{OUT}$  =  $V_{DD}/2$ ,  $R_L$  = tied to  $V_{DD}/2$ ,  $T_A$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C. (<u>Note 1</u>))

| PARAMETER                                          | SYMBOL | CONDITIONS                                                                             | MIN            | TYP    | MAX | UNITS |  |

|----------------------------------------------------|--------|----------------------------------------------------------------------------------------|----------------|--------|-----|-------|--|

| Total Harmonic Distortion + Noise  THD+N           |        | Unity-gain version, $A_V = +1$ ,<br>$V_{OUT} = 4V_{P-P}$ , $10k\Omega$ to GND, $1kHz$  |                | -114.0 |     |       |  |

|                                                    |        | Unity-gain version, $A_V = +1$ ,<br>$V_{OUT} = 4V_{P-P}$ , $10k\Omega$ to GND, $20kHz$ |                | -103.1 |     |       |  |

|                                                    |        | Unity-gain version, $A_V = +1$ ,<br>$V_{OUT} = 4V_{P-P}$ , $1k\Omega$ to GND, $1kHz$   |                | -114.0 |     |       |  |

|                                                    | THD+N  | Unity-gain version, $A_V = +1$ , $V_{OUT} = 4V_{P-P}$ , $1k\Omega$ to GND, $20kHz$     | -100.0         |        |     | dBc   |  |

|                                                    | HIDIN  | Gain of 5 version, $A_V = +5$ , $V_{OUT} = 4V_{P-P}$ , $10k\Omega$ to GND, $1kHz$      |                | -108.0 |     | dbc   |  |

|                                                    |        | Gain of 5 version, $A_V = +5$ ,<br>$V_{OUT} = 4V_{P-P}$ , $10k\Omega$ to GND, $20kHz$  |                | -110   |     |       |  |

|                                                    |        | Gain of 5 version, $A_V = +5$ , $V_{OUT} = 4V_{P-P}$ , $1k\Omega$ to GND, $1kHz$       | -106.0<br>-110 |        |     | _     |  |

|                                                    |        | Gain of 5 version, $A_V = +5$ , $V_{OUT} = 4V_{P-P}$ , $1k\Omega$ to GND, $20kHz$      |                |        |     |       |  |

| Electromagnetic<br>Interference Rejection<br>Ratio | EMIRR  | V <sub>RF PP</sub> = 100mV, f = 900MHz to 2400MHz                                      | 55             |        | dB  |       |  |

Note 1: Limits are 100% tested at  $T_A$  = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.

Note 2: Guaranteed by design and bench characterization.

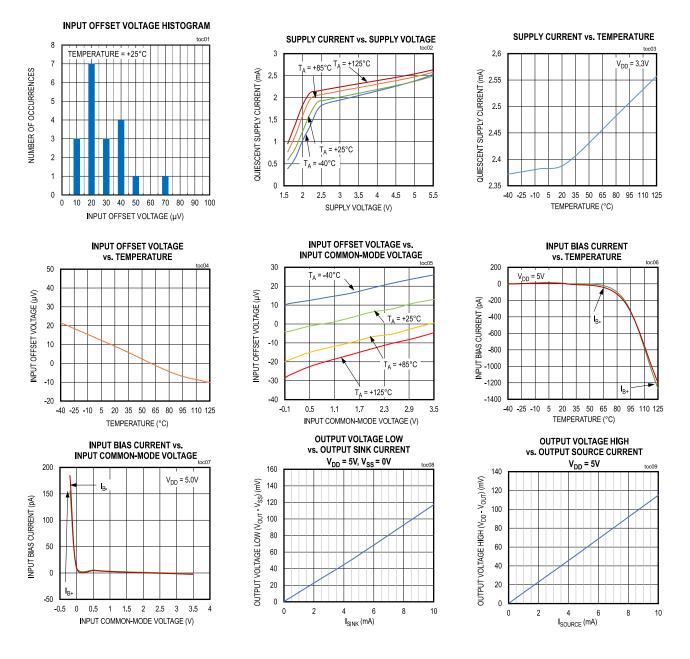

# **Typical Operating Characteristics**

$(V_{DD}$  = +5V,  $V_{SS}$  = 0V,  $V_{CM}$  =  $V_{DD}/2$ ,  $R_L$  = 10k $\Omega$  to  $V_{DD}/2$ ,  $C_L$  = 10pF to GND,  $T_A$  = +25°C, unless otherwise noted.)

# **Typical Operating Characteristics (continued)**

$(V_{DD}$  = +5V,  $V_{SS}$  = 0V,  $V_{CM}$  =  $V_{DD}/2$ ,  $R_L$  = 10k $\Omega$  to  $V_{DD}/2$ ,  $C_L$  = 10pF to GND,  $T_A$  = +25°C, unless otherwise noted.)

## **Typical Operating Characteristics (continued)**

$(V_{DD}$  = +5V,  $V_{SS}$  = 0V,  $V_{CM}$  =  $V_{DD}/2$ ,  $R_L$  = 10k $\Omega$  to  $V_{DD}/2$ ,  $C_L$  = 10pF to GND,  $T_A$  = +25°C, unless otherwise noted.)

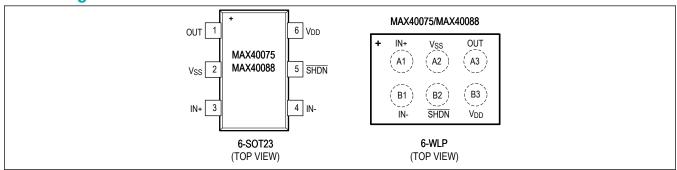

# **Pin Configurations**

# **Pin Description**

| Р       | IN    | NAME            | FUNCTION                                                                                   |  |  |

|---------|-------|-----------------|--------------------------------------------------------------------------------------------|--|--|

| 6 SOT23 | 6 WLP | NAIVIE          | FUNCTION                                                                                   |  |  |

| 1       | A3    | OUT             | Amplifier Output                                                                           |  |  |

| 2       | A2    | V <sub>SS</sub> | Negative Supply. Connect to ground for single-supply operation.                            |  |  |

| 3       | A1    | IN+             | Non-Inverting Amplifier Input                                                              |  |  |

| 4       | B1    | IN-             | Inverting Amplifier Input                                                                  |  |  |

| 5       | B2    | SHDN            | Shutdown, Active Low. Connect to V <sub>DD</sub> for normal operation (amplifier enabled). |  |  |

| 6       | В3    | $V_{DD}$        | Positive Supply. Connect 0.1µF and 4.7µF from V <sub>DD</sub> to V <sub>SS</sub> .         |  |  |

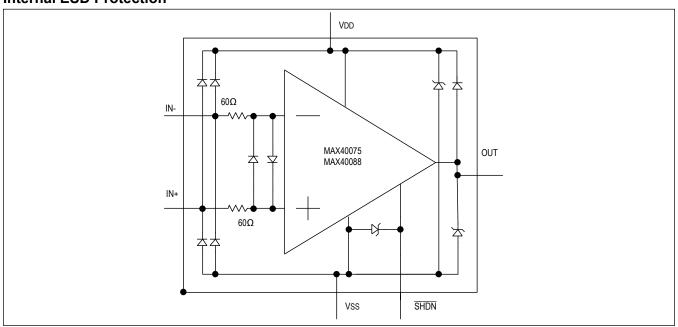

# **Functional Diagrams**

### **Internal ESD Protection**

## **Detailed Description**

The MAX40075/MAX40088 single-supply operational amplifiers feature ultra-low noise and distortion. Their low distortion and low noise make them ideal for use as pre-amplifiers in wide dynamic range applications, such as 16-bit analog-to-digital converters. Their high input impedance and low noise are also useful for signal conditioning of high-impedance sources, such as piezoelectric transducers.

These devices have true rail-to-rail output operation, drive output resistive loads as low as  $1k\Omega$  while maintaining DC accuracy and can drive capacitive loads up to 200pF without any oscillation. The input common-mode voltage range extends from 0.2V below  $V_{SS}$  to  $(V_{DD}$  - 1.5V). The push-pull output stage maintains excellent DC characteristics, while delivering up to  $\pm 20$  mA of source/sink output current.

The MAX40075 is unity-gain stable, while the MAX40088 is a decompensated version that has higher slew rate and is stable for gain  $\geq$  5V/V. Both devices feature a low-power shutdown mode, which reduces the supply current to 0.1µA and places amplifiers outputs into a high-impedance state.

#### **Low Noise**

The amplifiers input-referred voltage noise density is dominated by flicker noise (also known as 1/f noise) at lower frequencies and by thermal noise at higher frequencies. Overall thermal noise contribution is affected by the parallel combination of resistive feedback network ( $R_F||R_G$ ) depicted in Figure 1. These resistors should be reduced in cases where system bandwidth is large and thermal noise is dominant. Noise contribution factor can be reduced with increased gain settings.

For example, the input noise voltage density  $(e_N)$  of the circuit with  $R_F = 100k\Omega$ ,  $R_G = 10k\Omega$  (in Figure 1) with gain = 10V/V. The non-inverting configuration is  $e_N = 12nV/\sqrt{Hz}$ .  $e_N$  can be reduced to  $6nV/\sqrt{Hz}$  by choosing  $R_F = 10k\Omega$ ,  $R_G = 1k\Omega$  (in Figure 1) with gain = 10V/V, as before, but at the expense of higher current consumption and higher distortion. Having a gain of 100V/V with  $R_F = 100k\Omega$ ,  $R_G = 1k\Omega$  (in Figure 1), input referred voltage noise density is still a low  $6nV/\sqrt{Hz}$ .

#### **Low Distortion**

Many factors can affect the noise and distortion performance of the amplifier based on the design choices made. The following guidelines offer valuable information on the impact of design choices on total harmonic distortion (THD). Choosing correct feedback and gain resistor values for a particular application can be a very important factor in reducing THD. In general, the smaller the closed-loop gain, the smaller the THD generated, especially when driving heavy resistive loads (e.g., smaller resistive load with higher output current). Operating the device near or above the full-power bandwidth significantly degrades distortion.

Referencing the load to either supply also improves the amplifier distortion performance, because only one of the MOSFETs of the push-pull output stage drives the output. Referencing the load to mid-supply increases the amplifier distortion for a given load and feedback setting (see the *Total Harmonic Distortion vs. Frequency* graph in *Typical Operating Characteristics*).

For gains ≥ 5V/V, the decompensated MAX40088 delivers the best distortion performance as it has a higher slew rate and provides a higher amount of loop gain for a given closed-loop gain setting. Capacitive loads below 100pF do not significantly affect distortion results. Distortion performance is relatively constant over supply voltages.

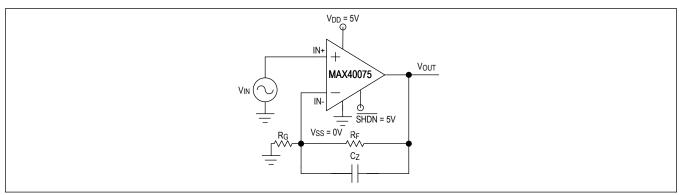

### Using a Feed-Forward Compensation Capacitor, CZ

The amplifier's input capacitance is 10pF, and if the resistance seen by the inverting input is large (in <u>Figure 1</u>) as a result of the feedback network, this resistance and capacitance combination can introduce a pole within the amplifier's bandwidth resulting in reduced phase margin. Compensate the reduced phase margin by introducing a feed-forward capacitor ( $C_Z$ ) between the inverting input and the output (shown in <u>Figure 1</u>). This effectively cancels the pole from the inverting input of the amplifier. Choose the value of  $C_Z$  as follows:

$$C_Z = 10 \times (R_F / R_G)[pF]$$

In the unity-gain stable MAX40075, the use of the correct  $C_7$  is most important for closed-loop non-inverting gain  $A_V =$

+2V/V and inverting gain  $A_V = -1V/V$ .

In the decompensated MAX40088,  $C_Z$  is most important for closed-loop gain  $A_V$  = +10V/V.

Using a slightly smaller  $C_Z$  than suggested by the formula above achieves a higher bandwidth at the expense of reduced phase and gain margin. As a general guideline, consider using  $C_Z$  for cases where  $R_G||R_F|$  is greater than  $20k\Omega$  (for the MAX40075) and greater than  $5k\Omega$  (for the MAX40088).

Figure 1. Adding Feed-Forward Compensation

## **Applications Information**

The MAX40075/MAX40088 combine good driving capability with ground-sensing input and rail-to-rail output operation. With their low distortion and low noise, these devices are ideal for use in ADC buffers, DAC output buffers, medical instrumentation systems, and other noise-sensitive applications.

### **Ground-Sensing and Rail-to-Rail Outputs**

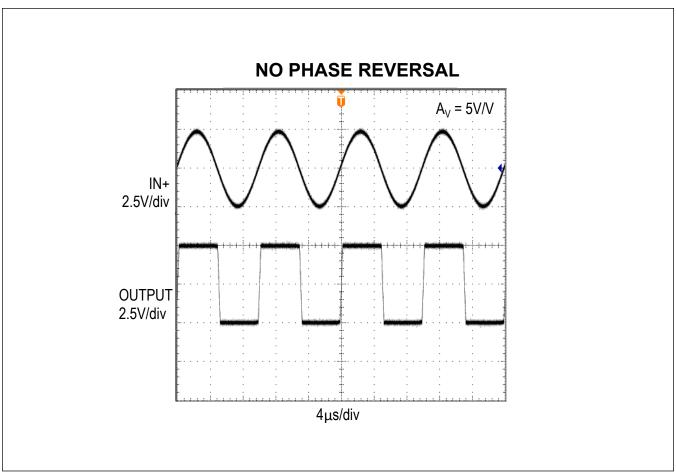

The common-mode input range of these devices extends below ground over temperature that offers excellent common-mode rejection and can be used in low-side current sensing applications. These devices are guaranteed not to undergo phase reversal when the input is overdriven over input common-mode voltage range as shown in <u>Figure 2</u>.

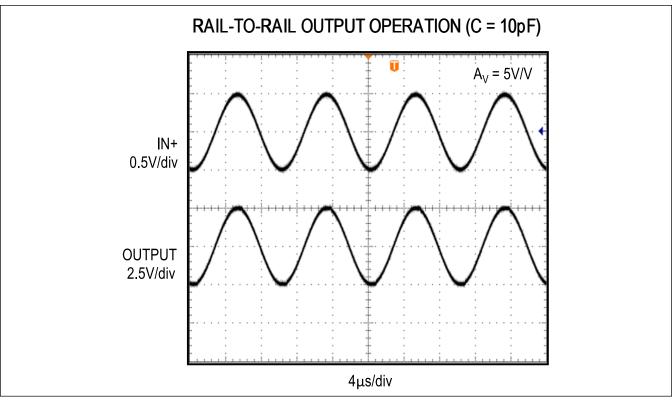

<u>Figure 3</u> showcases the true rail-to-rail output operation of the amplifier, configured with  $A_V = 5V/V$ . The output swings to within 8mV of the supplies with a 10k $\Omega$  load, making the devices ideal in low-supply voltage applications.

### **Power Supplies and Layout**

The MAX40075/MAX40088 operate from a single  $\pm 2.7V$  to  $\pm 5.5V$  power supply or from dual supplies of  $\pm 1.35V$  to  $\pm 2.75V$ . For single-supply operation, bypass the  $V_{DD}$  power supply pin with a  $0.1\mu F$  ceramic capacitor placed close to the  $V_{DD}$  pin. If operating from dual supplies, bypass both of the  $V_{DD}$  and  $V_{SS}$  supply pins with a  $0.1\mu F$  ceramic capacitor to ground. If additional decoupling is needed, add another  $4.7\mu F$  or  $10\mu F$  where the supply voltage is applied on the PCB.

Good layout improves performance by decreasing the amount of stray capacitance and noise at the op amp inputs and output. To decrease stray capacitance, minimize PC board trace lengths and resistor leads, and place external components close to the op amp's pins.

### **Typical Application Circuit**

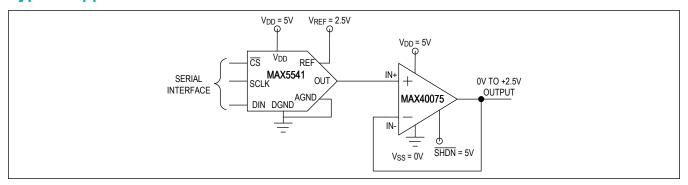

The <u>Typical Application Circuit</u> shows a single MAX40075 configured as an output buffer for the MAX5541 16-bit DAC. Because the MAX5541 has an unbuffered voltage output, the input bias current of the op amp used must be less than 6nA to maintain 16-bit accuracy. This family of amplifiers has an input bias current of only 2.3nA (max) over temperature, virtually eliminating this as a source of error. In addition, the MAX40075 has excellent open-loop gain and common-mode rejection, making this an excellent output buffer amplifier.

Figure 2. Scope Plot Showing Overdriven Input with No Phase Reversal

Figure 3. Rail-to-Rail Output Operation with  $10k\Omega$  and  $A_V = 5V/VI$

## **Chip Information**

PROCESS: BICMOS

# **Typical Application Circuit**

# **Ordering Information**

| PART NUMBER     | TEMP RANGE      | PIN-PACKAGE | STABLE GAIN (V/V) | BW (MHz) | TOP MARK |

|-----------------|-----------------|-------------|-------------------|----------|----------|

| MAX40075AUT/V+T | -40°C to +125°C | 6 SOT23     | 1                 | 10       | ACVK     |

| MAX40075ANT+T   | -40°C to +125°C | 6 WLP       | 1                 | 10       | _        |

| MAX40075AUT+T   | -40°C to +125°C | 6 SOT23     | 1                 | 10       | ACVD     |

| MAX40088ANT+T   | -40°C to +125°C | 6 WLP       | 5                 | 42       | _        |

| MAX40088AUT+T   | -40°C to +125°C | 6 SOT23     | 5                 | 42       | ACVE     |

<sup>+</sup> Denotes a lead(Pb)-free/RoHS-compliant package.

T Denotes tape-and-reel.

N denotes an automotive qualified part.