#### **MAX40100**

# Precision, Low-Power and Low-Noise Op Amp with RRIO

### **General Description**

The MAX40100 is a low-power, zero-drift operational amplifier available in a space-saving, 6-bump, wafer-level package (WLP).

Designed for use in portable consumer, medical, and industrial applications, the MAX40100 features rail-to-rail CMOS inputs and outputs, a 1.5MHz GBW at just  $66\mu A$  supply current, and  $10\mu V$  (max) "zero-drift" input voltage offset over time and temperature.

The zero-drift feature of the MAX40100 reduces the high 1/f noise typically found in CMOS input operational amplifiers, making it useful for a wide variety of low-frequency measurement applications.

The MAX40100 is available in a space-saving, 1.1  $\times$  0.76mm, 6-bump WLP with 0.35mm bump pitch.

The MAX40100 is specified over the -40°C to +125°C extended automotive operating temperature range.

### **Applications**

- Cell Phones

- Sensor Interfaces

- Loop-Powered Systems

- Portable Medical Devices

- · Battery-Powered Devices

#### **Benefits and Features**

- Low 66µA Quiescent Current

- Low Input Noise:

- 42nV/√Hz at 1kHz

- $0.42\mu V_{P-P}$  from 0.1Hz to 10Hz

- Rail-to-Rail Inputs and Outputs (RRIO)

- 1.5MHz GBW

- Ultra-Low 10pA Input Bias Current

- Single 1.6V to 5.5V Supply Voltage Range

- Unity Gain Stable

- Power-Saving Shutdown Mode

- Tiny, 1.1mm x 0.76mm, 6-bump WLP

Ordering Information appears at end of data sheet.

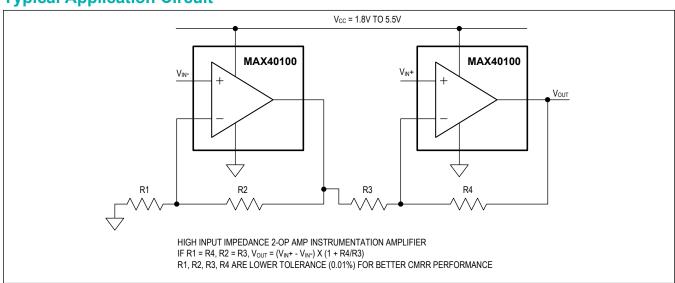

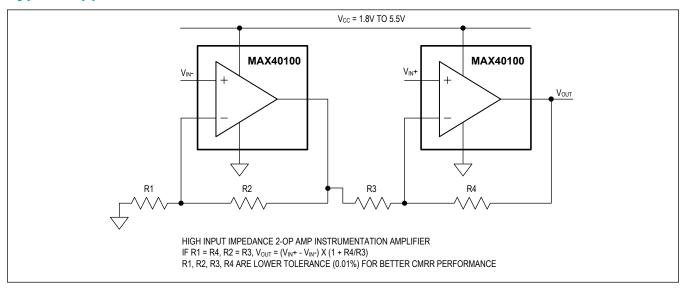

## **Typical Application Circuit**

### **Absolute Maximum Ratings**

| IN+, IN-, Supply Voltage, SHDN (V <sub>DD</sub> to | o GND)0.3V to +6V                 |

|----------------------------------------------------|-----------------------------------|

| OUT(GN                                             | D - $0.3V$ ) to $(V_{DD} + 0.3V)$ |

| Short-Circuit Duration to Either Supply I          | Rail,                             |

| OUT, OUTA, OUTB                                    | 10s                               |

| Continuous Input Current (Any Pins)                | ±20mA                             |

| Continuous Power Dissipation ( $T_A = +7$          | 0°C)                              |

| 6-Bump WLP (Derate 10.19mW/°C abo                  |                                   |

|                                                    |                                   |

| Package Thermal Characteristics (multilayer board) |                                  |  |  |  |  |

|----------------------------------------------------|----------------------------------|--|--|--|--|

| Junction-to-Ambient Thermal Resistan               | ice (θ <sub>JA</sub> ) 98.06°C/W |  |  |  |  |

| Operating Temperature Range                        | 40°C to +125°C                   |  |  |  |  |

| Junction Temperature                               | +150°C                           |  |  |  |  |

| Storage Temperature Range                          | 65°C to +150°C                   |  |  |  |  |

| Lead Temperature (soldering 10s)                   | +300°C                           |  |  |  |  |

|                                                    |                                  |  |  |  |  |

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial.">www.maximintegrated.com/thermal-tutorial.</a>

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

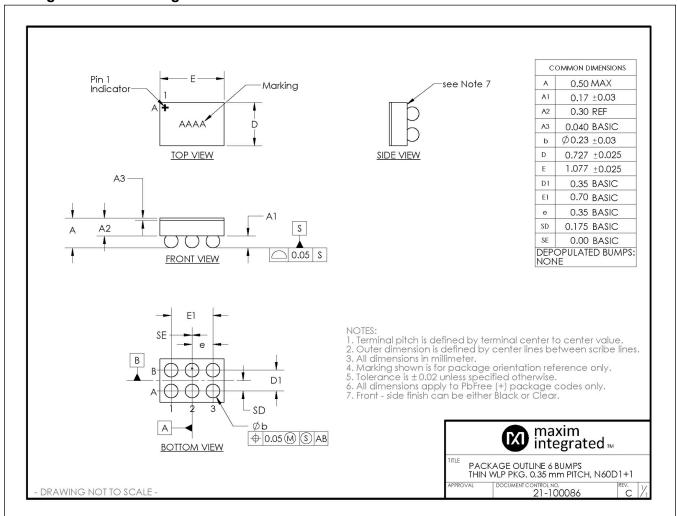

### **Package Information**

#### 6 WLP

| Package Code        | N60D1+1                        |

|---------------------|--------------------------------|

| Outline Number      | <u>21-100086</u>               |

| Land Pattern Number | Refer to Application Note 1891 |

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

### **Package Outline Drawing**

### **Electrical Characteristics**

$(V_{DD} = +3.3V,~GND = 0,~A_V = 1V/V,~V_{OUT} = V_{DD}/2,~C_L = 20pF,~R_L = 100k\Omega~to~V_{DD}/2,~V_{\overline{SHDN}} = V_{DD},~T_A = -40^{\circ}C~to~+125^{\circ}C~unless~otherwise~noted.~Typical~values~are~at~+25^{\circ}C)~(\underline{Note~2})$

| PARAMETER                                   | SYMBOL           | COND                                                                                                                                       | MIN                                | TYP  | MAX    | UNITS                     |       |

|---------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------|--------|---------------------------|-------|

| POWER SUPPLY                                |                  | -                                                                                                                                          |                                    |      |        |                           |       |

| -                                           |                  | Guaranteed by PSRR, 0°C ≤ T <sub>A</sub> ≤ +70°C                                                                                           |                                    | 1.6  |        | 5.5                       |       |

| Supply Voltage Range                        | $V_{DD}$         | Guaranteed by PSRR, -40°C ≤ T <sub>A</sub> ≤ +125°C                                                                                        |                                    | 1.8  |        | 5.5                       | V     |

| Quiescent Supply                            |                  | T <sub>A</sub> = +25°C                                                                                                                     |                                    |      | 66     | 92                        | μA    |

| Current                                     | I <sub>DD</sub>  |                                                                                                                                            | -40°C ≤ T <sub>A</sub> ≤ +125°C    |      |        | 124                       |       |

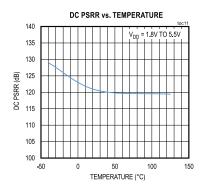

|                                             |                  |                                                                                                                                            | T <sub>A</sub> = +25°C             | 116  | 135    |                           | dB    |

| Power-Supply Rejection Ratio                | PSRR             | V <sub>DD</sub> = 1.8V to 5.5V                                                                                                             | -40°C ≤ T <sub>A</sub> ≤<br>+125°C | 107  |        |                           |       |

|                                             |                  | 0°C ≤ T <sub>A</sub> ≤ +70°C, V                                                                                                            | <sub>DD</sub> = 1.6V to 5.5V       | 107  |        |                           |       |

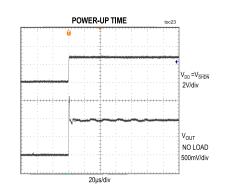

| Power-Up Time                               | t <sub>ON</sub>  | $V_{DD}$ = 0 to 3V step,                                                                                                                   | A <sub>V</sub> = 1V/V              |      | 20     |                           | μs    |

| Shutdown Supply<br>Current                  | ISHDN            |                                                                                                                                            |                                    |      |        | 300                       | nA    |

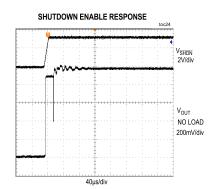

| Turn-On Time from<br>Shutdown               | t <sub>OSD</sub> | $V_{DD}$ = 3.3V, $V_{\overline{SHDN}}$ = 0 to 3.3V step in < 1 $\mu$ s                                                                     |                                    |      | 50     |                           | μs    |

| DC SPECIFICATIONS                           |                  |                                                                                                                                            |                                    |      |        |                           |       |

| land Offeet Veltere                         | V <sub>OS</sub>  | T <sub>A</sub> = +25°C                                                                                                                     |                                    |      | 0.8    | 10                        | μV    |

| Input Offset Voltage                        |                  | -40°C ≤ T <sub>A</sub> ≤ +125°C                                                                                                            |                                    |      |        | 25                        |       |

| Input Offset Voltage Drift                  | ΔV <sub>OS</sub> |                                                                                                                                            |                                    |      | 5      |                           | nV/°C |

|                                             |                  | T <sub>A</sub> = +25°C                                                                                                                     |                                    |      | ±0.031 | ±0.160                    | nA    |

| Input Bias Current ( <u>Note</u> <u>3</u> ) | Ι <sub>Β</sub>   | -40°C ≤ T <sub>A</sub> ≤ +85°C                                                                                                             |                                    |      |        | ±4.6                      |       |

| ⊆/                                          |                  | -40°C ≤ T <sub>A</sub> ≤ +125°C                                                                                                            |                                    |      |        | ±28                       |       |

| Input Offset Current                        | Ios              |                                                                                                                                            |                                    |      | ±0.005 |                           | nA    |

| Input Common-Mode                           | V <sub>CM</sub>  | Guaranteed by<br>CMRR test                                                                                                                 | T <sub>A</sub> = +25°C             | -0.1 |        | V <sub>DD</sub> +<br>0.1  | - V   |

| Range                                       |                  |                                                                                                                                            | -40°C ≤ T <sub>A</sub> ≤<br>+125°C | -0.1 |        | V <sub>DD</sub> +<br>0.05 |       |

| Common-Mode                                 |                  | $-0.1 \le V_{CM} \le V_{DD} + 0.1, T_A = +25^{\circ}C$<br>$-0.1 \le V_{CM} \le V_{DD} + 0.05,$<br>$-40^{\circ}C \le T_A \le +125^{\circ}C$ |                                    | 122  | 135    |                           |       |

| Rejection Ratio                             | CMRR             |                                                                                                                                            |                                    | 116  |        |                           | dB    |

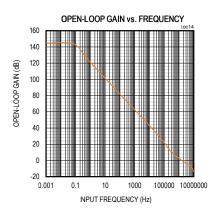

| Open-Loop Gain                              | AV <sub>OL</sub> | $20\text{mV} \le V_{OUT} \le V_{DD} - 20\text{mV},$<br>$R_L = 100\text{k}\Omega \text{ to } V_{DD}/2$                                      |                                    | 120  | 138    |                           | - dB  |

|                                             |                  | 150mV $\leq$ V <sub>OUT</sub> $\leq$ V <sub>DD</sub> - 150mV,<br>R <sub>L</sub> = 5k $\Omega$ to V <sub>DD</sub> /2                        |                                    | 123  | 160    |                           |       |

| Input Resistance                            | P                | Differential                                                                                                                               |                                    |      | 50     |                           | ΜΩ    |

| input ixesistance                           | R <sub>IN</sub>  | Common-mode                                                                                                                                |                                    |      | 200    |                           | IVILL |

## **Electrical Characteristics (continued)**

$(V_{DD} = +3.3V,~GND = 0,~A_V = 1V/V,~V_{OUT} = V_{DD}/2,~C_L = 20pF,~R_L = 100k\Omega~to~V_{DD}/2,~V_{\overline{SHDN}} = V_{DD},~T_A = -40^{\circ}C~to~+125^{\circ}C~unless~otherwise~noted.~Typical~values~are~at~+25^{\circ}C)~(\underline{Note~2})$

| PARAMETER                         | SYMBOL                           | CONDITIONS                         |                                 | MIN | TYP  | MAX | UNITS             |

|-----------------------------------|----------------------------------|------------------------------------|---------------------------------|-----|------|-----|-------------------|

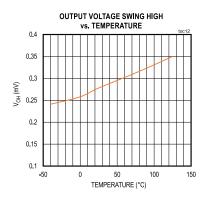

|                                   | V <sub>ОН</sub>                  | V <sub>DD</sub> - V <sub>OUT</sub> | $R_L$ = 100kΩ to $V_{DD}/2$     |     |      | 12  | _ mV              |

|                                   |                                  |                                    | $R_L$ = 50kΩ to $V_{DD}/2$      |     |      | 22  |                   |

|                                   |                                  |                                    | $R_L = 600\Omega$ to $V_{DD}/2$ |     | 50   |     |                   |

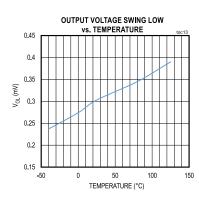

| Output Voltage Swing              |                                  | V <sub>OUT</sub>                   | $R_L$ = 100kΩ to $V_{DD}/2$     |     |      | 11  |                   |

|                                   | V <sub>OL</sub>                  |                                    | $R_L$ = 50kΩ to $V_{DD}/2$      |     |      | 18  |                   |

|                                   |                                  |                                    | $R_L = 600\Omega$ to $V_{DD}/2$ |     | 50   |     |                   |

| Short-Circuit Current             | I <sub>SC</sub>                  |                                    |                                 |     | 50   |     | mA                |

| AC SPECIFICATIONS                 |                                  | •                                  |                                 | •   |      |     |                   |

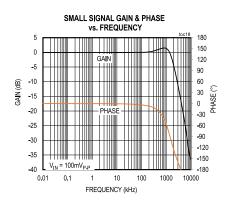

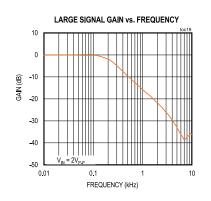

| Gain-Bandwidth Product            | GBWP                             |                                    |                                 |     | 1.5  |     | MHz               |

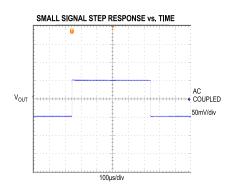

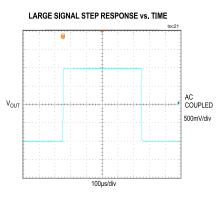

| Slew Rate                         | SR                               | 0 ≤ V <sub>OUT</sub> ≤ 2V          |                                 |     | 0.7  |     | V/µs              |

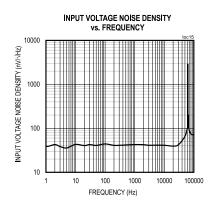

| Input Voltage Noise<br>Density    | En                               | f <sub>SW</sub> = 1kHz             |                                 |     | 42   |     | nV/√Hz            |

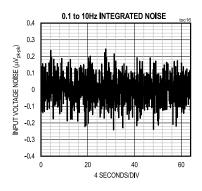

| Input Voltage Noise               |                                  | 0.1Hz ≤ f <sub>SW</sub> ≤ 10Hz     |                                 |     | 0.42 |     | μV <sub>P-P</sub> |

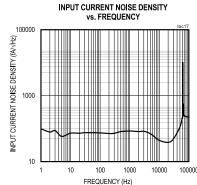

| Input Current Noise<br>Density    |                                  | f <sub>SW</sub> = 1kHz             |                                 |     | 100  |     | fA/√Hz            |

| Phase Margin                      |                                  | C <sub>L</sub> = 20pF              |                                 |     | 60   |     | ٥                 |

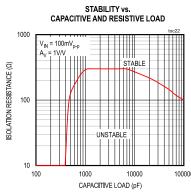

| Capacitive Loading                | CL                               | No sustained osc                   | cillation, AV = 1V/V            |     | 400  |     | pF                |

| LOGIC INPUT                       |                                  |                                    |                                 |     |      |     |                   |

| Shutdown Input Low                | V <sub>IL</sub>                  |                                    |                                 |     |      | 0.5 | V                 |

| Shutdown Input High               | V <sub>IH</sub>                  |                                    |                                 | 1.3 |      |     | V                 |

| Shutdown Input<br>Leakage Current | I <sub>IL</sub> /I <sub>IH</sub> |                                    |                                 |     |      | 100 | nA                |

**Note 2:** Specifications are 100% tested at  $T_A = +25^{\circ}C$  (exceptions noted). All temperature limits are guaranteed by design.

Note 3: Guaranteed by design.

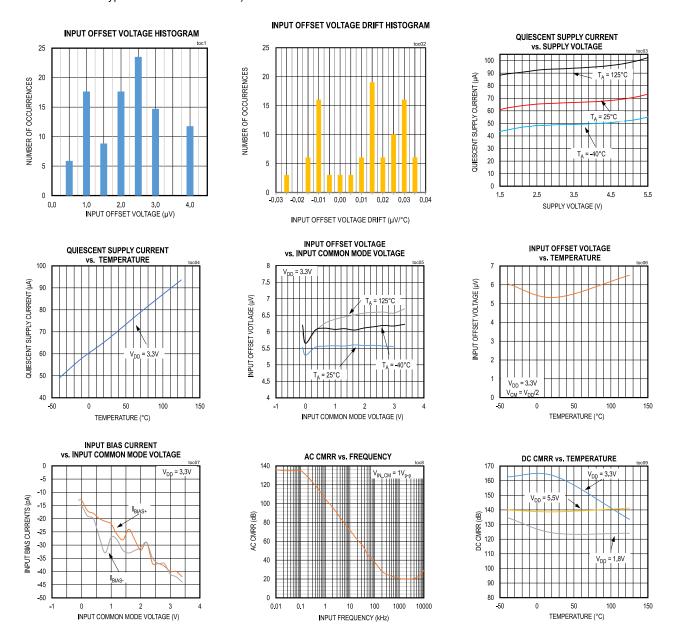

## **Typical Operating Characteristics**

$(V_{DD}$  = +3.3V, GND = 0,  $A_V$  = 1V/V,  $V_{OUT}$  =  $V_{DD}/2$ ,  $C_L$  = 20pF,  $R_L$  = 100k $\Omega$  to  $V_{DD}/2$ ,  $V_{\overline{SHDN}}$  =  $V_{DD}$ ,  $T_A$  = -40°C to +125°C unless otherwise noted. Typical values are at +25°C)

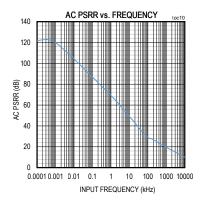

## **Typical Operating Characteristics (continued)**

$(V_{DD}$  = +3.3V, GND = 0,  $A_V$  = 1V/V,  $V_{OUT}$  =  $V_{DD}/2$ ,  $C_L$  = 20pF,  $R_L$  = 100k $\Omega$  to  $V_{DD}/2$ ,  $V_{\overline{SHDN}}$  =  $V_{DD}$ ,  $T_A$  = -40°C to +125°C unless otherwise noted. Typical values are at +25°C)

## **Typical Operating Characteristics (continued)**

$(V_{DD}$  = +3.3V, GND = 0,  $A_V$  = 1V/V,  $V_{OUT}$  =  $V_{DD}/2$ ,  $C_L$  = 20pF,  $R_L$  = 100k $\Omega$  to  $V_{DD}/2$ ,  $V_{\overline{SHDN}}$  =  $V_{DD}$ ,  $T_A$  = -40°C to +125°C unless otherwise noted. Typical values are at +25°C)

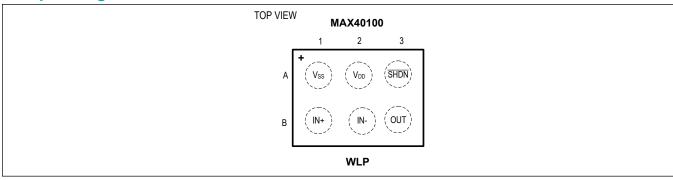

## **Bump Configuration**

## **Bump Descriptions**

| PIN | NAME            | FUNCTION                                                       |

|-----|-----------------|----------------------------------------------------------------|

| A1  | V <sub>SS</sub> | Negative Supply Voltage                                        |

| A2  | V <sub>DD</sub> | Positive Supply Voltage. Bypass to GND with a 0.1µF capacitor. |

| A3  | SHDN            | Shutdown. Pull to V <sub>SS</sub> to activate shutdown mode.   |

# **Bump Descriptions (continued)**

| PIN | NAME | FUNCTION       |

|-----|------|----------------|

| B1  | IN+  | Positive Input |

| B2  | IN-  | Negative Input |

| В3  | OUT  | Output         |

### **Detailed Description**

The MAX40100 is a precision, low-power op-amps ideal for signal processing applications. This device use an innovative auto-zero technique that allows precision and low-noise with a minimum amount of power. The low input offset voltage, CMOS inputs, and the absence of 1/f noise allows for optimization of active-filter designs.

The MAX40100 achieves rail-to-rail performance at the input through the use of a low-noise charge pump. This ensures a glitch-free, common-mode input voltage range extending from the negative supply rail up to the positive supply rail, eliminating cross over distortion common to traditional N-channel/P-channel CMOS pair inputs, reducing harmonic distortion at the output.

The device features a shutdown mode that greatly reduces guiescent current while the device is not operational.

#### **Auto-Zero**

The MAX40100 features an auto-zero circuit that allows the device to achieve less than  $10\mu V$  of input offset voltage and eliminates the 1/f noise.

#### **Internal Charge Pump**

An internal charge pump provides an internal supply typically 1V beyond the upper rail. This internal rail allows the MAX40100 to achieve true rail-to-rail inputs and outputs, while providing excellent common-mode rejection, power-supply rejection ratios, and gain linearity.

The charge pump requires no external components, and in most applications is entirely transparent to the user. The operating frequency is well beyond the unity-gain frequency of the amplifier, avoiding aliasing or other signal integrity issues in sensitive applications.

#### **Shutdown Operation**

The device features an active-low shutdown mode that lowers the quiescent current to less than  $1\mu$ A. In shutdown mode the inputs and output are high impedance. This allows multiple devices to be multiplexed onto a single line without the use of external buffers. Pull SHDN high for normal operation.

The shutdown high  $(V_{IH})$  and low  $(V_{IL})$  threshold voltages are designed for ease of integration with digital controls like microcontroller outputs. These thresholds are independent of supply, eliminating the need for external pulldown circuitry.

### **Applications Information**

The MAX40100 is a low-power, low-noise, precision operational amplifier designed for applications in the portable medical (such as ECG and Pulse Oximetry), portable consumer, and industrial markets.

The MAX40100 is also ideal for loop-powered systems that interface with pressure sensors or strain-gauges.

#### **Capacitive Load Stability**

Driving large capacitive loads can cause instability in many op amps. MAX40100 is stable with capacitive loads up to 400pF. Stability with higher capacitive loads can be improved by adding an isolation resistor in series with the opamp output. This resistor improves the circuit's phase margin by isolating the load capacitor from the amplifier's output. The graph in the <u>Typical Operating Characteristics</u> gives the stable operation region for capacitive load versus isolation resistors.

#### **Power Supplies and Layout**

The MAX40100 operate either with a single supply from +1.6V to +5.5V with respect to ground or with dual supplies from  $\pm 0.8$ V to  $\pm 2.75$ V. When used with dual supplies, bypass both supplies with their own  $0.1\mu$ F capacitor to ground. When used with a single supply, bypass  $V_{DD}$  with a  $0.1\mu$ F capacitor to ground.

Careful layout technique helps optimize performance by decreasing the amount of stray capacitance at the op amp's inputs and outputs. To decrease stray capacitance, minimize trace lengths by placing external components close to the op amp's pins.

## **Typical Application Circuit**

### **Ordering Information**

| PART TEMP RANGE |                 | PIN-PACKAGE |

|-----------------|-----------------|-------------|

| MAX40100ANT+    | -40°C to +125°C | 6 WLP       |

<sup>+</sup>Denotes lead(Pb)-free/RoHS compliant package.