#

## +48V, Single-Port Network Power Switch For Power-Over-LAN

### **General Description**

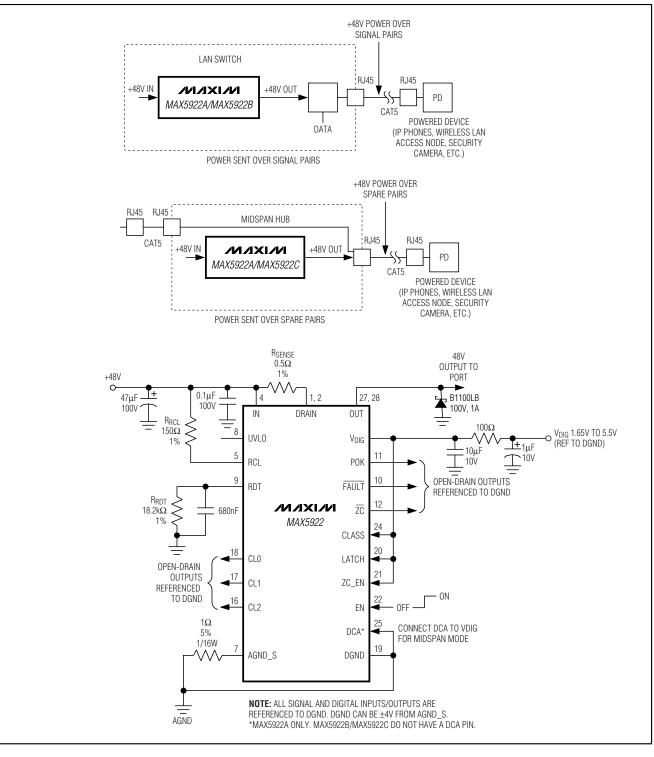

The MAX5922A/B/C is a single-port network power controller with an integrated power MOSFET, operating from a +32V to +60V supply rail. The device is specifically designed for power-sourcing equipment (PSE) in powerover-LAN applications and is fully compliant to the IEEE 802.3af standard. The MAX5922 provides power devices (PD) discovery, classification, current limit, and other necessary functions for an IEEE 802.3af compliant PSE.

The MAX5922 is suitable for PSE function in both switch/router systems where the power is delivered to the load through the signal pairs, and in midspan systems where the power is delivered to the load through the spare pairs. In midspan mode, a detection collision avoidance circuit (MAX5922A/C only) provides the necessary back-off timing to prevent fault detections that happen when two different PSEs try to detect and power the same PD. The MAX5922B/C have a detection disable input that can be connected high to disable the detection/classification functions or connected low to enable them.

The MAX5922 features a programmable undervoltage lockout (UVLO) that keeps the device in shutdown until the input voltage exceeds a certain threshold, set to 38V (MAX5922A) or 28V (MAX5922B/C) internally. After successfully discovering and classifying a PD, the MAX5922 enters startup mode. During startup, the MAX5922 limits the output voltage and current slew rate to minimize EMI (electromagnetic interference). The MAX5922 has an integrated 0.45 $\Omega$  N-channel power MOSFET that provides efficient operation and simplified system design. The MAX5922 monitors and provides current-limit protection to the load at all times. The current limit is programmable using an external current-sensing resistor. The MAX5922 features current-limit foldback and duty-cycle limit to ensure robust operation during load-fault and short-circuit conditions. Fault management allows the part to either latch-off or autorestart after a fault.

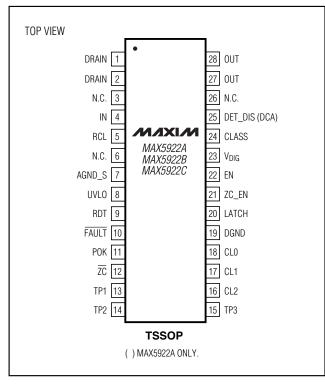

The MAX5922 provides POK,  $\overline{ZC}$ , and  $\overline{FAULT}$  status signals to indicate output power is good, zero-current fault, and other faults (overcurrent, overtemperature), respectively. The MAX5922 is available in a 28-pin TSSOP package and is rated over the extended -40°C to +85°C temperature range.

### **Features**

- ♦ IEEE 802.3af Compliant

- +32V to +60V Wide Operating Input Range

- ♦ 0.45Ω Integrated Power Switch

- Power Device (PD) Detection and Classification

- ♦ 100µA PD Leakage Detection Tolerant

- Programmable Current Limit

- ♦ Zero-Current Detection with Status Output

- Detection Collision Avoidance Option for Midspan Application

- Input Logic Signals Compatible with 1.8V to 5V CMOS Logic

- Separate Analog and Digital Grounds with Up to ±4V Offset

- Power-Good Status Output

- Overcurrent and Overtemperature Protection with Status Outputs

- Current-Limit Foldback with Timeout and Duty-Cycle Control

- Latch or Autorestart Fault Management

### **Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE |

|-------------|----------------|-------------|

| MAX5922AEUI | -40°C to +85°C | 28 TSSOP    |

| MAX5922BEUI | -40°C to +85°C | 28 TSSOP    |

| MAX5922CEUI | -40°C to +85°C | 28 TSSOP    |

### **Applications**

Power-Sourcing Equipment (PSE)

Power-Over-LAN/Power-Over-MDI (Media-Dependent Interface)

Computer Telephony

Single-Port Power Injector/Adapter

Midspan Power Injector

Switches/Routers with In-Line Power

**MAX5922**

Typical Application Circuits, Selector Guide, and Pin Configuration appear at end of data sheet.

###

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

| (All voltages with respect to AGND_S, unless otherwise noted.)<br>IN0.3V to +76V<br>UVLO0.3V to +6V<br>V <sub>DIG</sub> to DGND0.3V to +6V<br>OUT0.3V to (V <sub>DRAIN</sub> + 0.3V)<br>DRAIN0.3V to (V <sub>IN</sub> + 0.3V)<br>RDT0.3V to (V <sub>IN</sub> + 0.3V)<br>RDT0.3V to +12V<br>RCL to IN10V to +0.3V<br>EN, DET_DIS, DCA, CLASS, ZC_EN,<br>and LATCH to DGND0.3V to +6V | POK, $\overline{ZC}$ , CL0, CL1, CL2, and $\overline{FAULT}$ to DGND0.3V to +6V<br>DGND5V to +5V<br>Maximum Current into Drain |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = 48V, V_{DIG} = 3.3V, AGND\_S = AGND = DGND = 0V, R_{SENSE} = 0.5\Omega \pm 1\%, UVLO = open, EN = V_{DIG}, R_{RCL} = 150\Omega \pm 1\%, R_{RDT} = 18.2k\Omega \pm 1\%, T_A = -40^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at T\_A = +25°C.) (Note 1)

| PARAMETER                                                                     | SYMBOL                | CONDITIONS                                                              |                      |      | ТҮР  | MAX  | UNITS |

|-------------------------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------|----------------------|------|------|------|-------|

| Analog Input Voltage Range                                                    | VIN                   |                                                                         |                      |      |      | 60   | V     |

| Analog Input Supply Current                                                   | lin                   | V <sub>IN</sub> = 60V, measured at AGND after OUT has stopped slewing   |                      |      | 1    | 1.6  | mA    |

| Digital Input Voltage Range                                                   | VDIG                  |                                                                         |                      | 1.65 |      | 5.50 | V     |

| Digital Input Supply Current                                                  | IDIG                  | $V_{DIG} = 5V$                                                          |                      |      | 0.05 | 0.1  | mA    |

| DGND to AGND Operating<br>Voltage Range                                       |                       |                                                                         |                      | -4   |      | +4   | V     |

| Current-Limit Response Time                                                   |                       | OUT shorted to AGN                                                      | D (Note 2)           |      | 1    |      | μs    |

| OUT Current-Limit Foldback<br>Voltage                                         | VFBSTOP               | (Note 3)                                                                |                      |      | 18   |      | V     |

| Current-Limit Sense Voltage                                                   | VILIM                 | Maximum voltage across R <sub>SENSE</sub> at V <sub>OI</sub><br>VFBSTOP |                      | 198  | 212  | 223  | mV    |

| (VIN - VDRS) (Note 4)                                                         |                       | 0°C to +70°C                                                            | 203                  | 212  | 221  |      |       |

| Current-Limit Sense Foldback<br>Voltage (V <sub>IN</sub> - V <sub>DRS</sub> ) | V <sub>ILIM_fb</sub>  | V <sub>OUT</sub> = 0V                                                   |                      | 64   | 70   | 76   | mV    |

| Overcurrent Timeout                                                           | toc                   | OUT shorted to AGND (Note 5)                                            |                      | 50   | 60   | 75   | ms    |

| Duras On Registeres                                                           |                       | $T_A = +25^{\circ}C$                                                    |                      | 0.45 |      | Ω    |       |

| D <sub>MOS</sub> On-Resistance                                                | R <sub>DSON</sub>     | 1001 = 10000                                                            | $T_A = +85^{\circ}C$ |      |      | 0.75 | 52    |

| Power-Off OUT Sink Current                                                    |                       | $EN = DGND, V_{OUT} =$                                                  | 48V                  |      |      | 15   | μA    |

| Maximum Output Voltage Slew<br>Rate                                           | dV <sub>OUT</sub> /dt | V <sub>OUT</sub> rising, no load                                        |                      |      | 100  |      | V/ms  |

| Maximum Output Current Slew<br>Rate                                           | dl <sub>OUT</sub> /dt | $V_{OUT}$ rising, $C_{LOAD} = 100 \mu F$                                |                      |      | 35   |      | A/ms  |

|                                                                               |                       | V <sub>OUT</sub> rising, POK from low to high                           |                      | 650  | 750  | 850  | mV    |

| Power-OK Threshold (V <sub>IN</sub> - V <sub>OUT</sub> )                      | Vthpok                | Hysteresis                                                              |                      |      | 10   |      | %     |

| POK Output Low Voltage                                                        | VPOK_LOW              | I <sub>POK</sub> = 3mA                                                  |                      |      |      | 0.4  | V     |

| POK Output Leakage Current                                                    |                       | V <sub>POK</sub> = 3.3V                                                 |                      |      | 0.05 | 1    | μA    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 48V, V_{DIG} = 3.3V, AGND_S = AGND = DGND = 0V, R_{SENSE} = 0.5\Omega \pm 1\%, UVLO = open, EN = V_{DIG}, R_{RCL} = 150\Omega \pm 1\%, R_{RDT} = 18.2k\Omega \pm 1\%, T_A = -40^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                                                                         | SYMBOL                                               | CONDITIONS                                              |                       |               | ТҮР  | МАХ                       | UNITS    |

|-----------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------|-----------------------|---------------|------|---------------------------|----------|

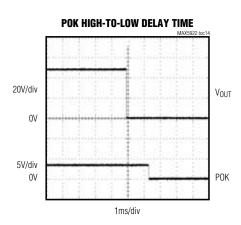

|                                                                                   | (Noto 6) TPOK_LOW POK from high to low, VOUT falling |                                                         | 1.0                   | 1.4           | 1.8  |                           |          |

| POK Output Delay (Note 6)                                                         | <sup>t</sup> POK_HIGH                                | POK from low to high, V <sub>OUT</sub> rising           |                       | 74            | 88   | 102                       | ms       |

| Zero-Current Detection Threshold<br>Voltage (V <sub>IN</sub> - V <sub>DRS</sub> ) | V <sub>ZCTH</sub>                                    | (Note 4)                                                |                       | 2.7           | 3.75 | 4.8                       | mV       |

| ZC Output Low Voltage                                                             | VZC_LOW                                              | $I_{\overline{ZC}} = 3mA$                               |                       |               |      | 0.4                       | V        |

| ZC Output Leakage Current                                                         |                                                      | $V\overline{ZC} = 3.3V$                                 |                       |               | 0.05 | 1                         | μA       |

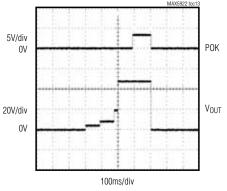

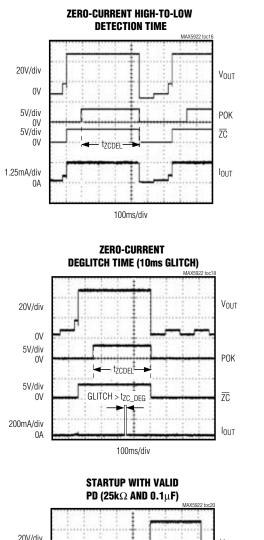

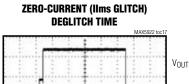

| Zero-Current Detection Delay                                                      | <b>t</b> ZCDEL                                       | ZC from high to low, IOUT fa                            | alling (Note 7)       | 300           | 350  | 400                       | ms       |

| Zero-Current Deglitch Time                                                        | tzc_deg                                              | IOUT rising                                             |                       |               | 10   |                           | ms       |

|                                                                                   |                                                      | Temperature rising                                      |                       |               | 150  |                           | °C       |

| Thermal Shutdown                                                                  |                                                      | Hysteresis                                              |                       |               | 30   |                           | °C       |

| Shutdown Autorestart Time                                                         | <sup>t</sup> RESTART                                 | LATCH = low (Note 8)                                    |                       | 1.60          | 1.92 | 2.24                      | S        |

| UNDERVOLTAGE LOCKOUT                                                              |                                                      | ·                                                       |                       |               |      |                           |          |

|                                                                                   |                                                      |                                                         | MAX5922A              | 36            | 38   | 40                        |          |

| Default V <sub>IN</sub> UVLO                                                      | UVLOTH                                               | UVLO floating, V <sub>IN</sub> rising                   | MAX5922B/<br>MAX5922C | 26            | 28   | 30                        | V        |

|                                                                                   |                                                      |                                                         | MAX5922A              |               | 4.4  |                           |          |

|                                                                                   |                                                      | Hysteresis                                              | MAX5922B/C            |               | 2.5  |                           | 1        |

|                                                                                   | VREF                                                 | Referenced to AGND_S,<br>V <sub>UVLO</sub> rising       | MAX5922A              | 1.36          | 1.38 | 1.41                      | V        |

|                                                                                   |                                                      |                                                         | MAX5922B/<br>MAX5922C | 1.31          | 1.33 | 1.36                      |          |

| UVLO Comparator Threshold                                                         |                                                      |                                                         | MAX5922A              |               | 160  |                           |          |

|                                                                                   |                                                      | Hysteresis MAX5922B/<br>MAX5922C                        |                       |               | 120  |                           | mV       |

| UVLO Input Resistance                                                             |                                                      |                                                         |                       | 50            |      |                           | kΩ       |

| LOGIC SIGNALS                                                                     |                                                      | 1                                                       |                       |               |      |                           | 1        |

| EN, LATCH, DCA, DET_DIS<br>CLASS, and ZC_EN Input High<br>Voltage                 | V <sub>IH</sub>                                      | 1.65V < V <sub>DIG</sub> < 5.5V                         |                       | 0.7 ×<br>VDIG |      |                           | V        |

| EN, LATCH, DCA, DET_DIS<br>CLASS, and ZC_EN Input Low                             | $1 103 V \le V 1 V \le 2 U V$                        |                                                         |                       |               |      | 0.3 ×<br>V <sub>DIG</sub> | V        |

| Voltage                                                                           |                                                      | 2.0V < V <sub>DIG</sub> < 5.5V                          |                       |               |      | 0.8                       | <u> </u> |

| EN, LATCH, DCA, DET_DIS<br>CLASS, and ZC_EN Input Current                         |                                                      |                                                         |                       | -1            |      | +1                        | μA       |

| EN Low Pulse Width                                                                |                                                      |                                                         |                       | 3             |      |                           | μs       |

| FAULT, CL0, CL1 and CL2,<br>Output Low Voltage                                    | V <sub>OL</sub>                                      | I <sub>SINK</sub> = 3mA                                 |                       |               |      | 0.4                       | V        |

| FAULT, CL0, CL1 and CL2,<br>Output Leakage Current                                |                                                      | $V_{FAULT} = V_{CL0} = V_{CL1} = V_{CL3}$<br>CLASS = 0V |                       | 0.05          | 1    | μA                        |          |

### ELECTRICAL CHARACTERISTICS (continued)

$(V_{IN} = 48V, V_{DIG} = 3.3V, AGND_S = AGND = DGND = 0V, R_{SENSE} = 0.5\Omega \pm 1\%, UVLO = open, EN = V_{DIG}, R_{RCL} = 150\Omega \pm 1\%, R_{RDT} = 18.2k\Omega \pm 1\%, T_A = -40^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                                                  | SYMBOL                | CONDITIONS                                             | MIN  | ТҮР  | MAX  | UNITS |  |  |  |

|------------------------------------------------------------|-----------------------|--------------------------------------------------------|------|------|------|-------|--|--|--|

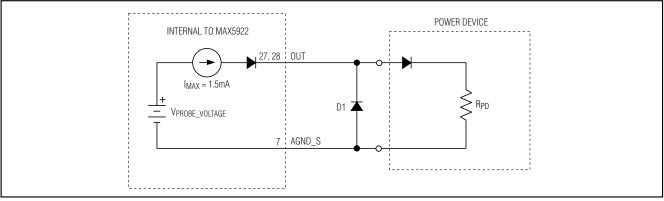

| PD DETECTION (See Figure 3, <i>PD Detection</i> Section)   |                       |                                                        |      |      |      |       |  |  |  |

| Detection Probe Voltage Phase I                            | V <sub>PBI</sub>      | $R_{PD} = 19k\Omega$ to $26.5k\Omega$                  | 3.6  | 4    | 4.4  | V     |  |  |  |

| Detection Probe Voltage Phase II                           | VPBII                 | $R_{PD} = 19k\Omega$ to 26.5k $\Omega$                 | 7.2  | 8    | 8.8  | V     |  |  |  |

| Detection Short-Circuit Current                            | ISC_DET               | OUT shorted to AGND                                    | 0.68 |      | 1.50 | mA    |  |  |  |

| Valid PD Detected Lower-Limit<br>Threshold                 | R <sub>PDL</sub>      | (Note 9)                                               | 15   |      | 19   | kΩ    |  |  |  |

| Valid PD Detected Upper-Limit<br>Threshold                 | R <sub>PDH</sub>      | (Note 9)                                               | 26.5 |      | 33.0 | kΩ    |  |  |  |

| Total Detection Time                                       | t <sub>det</sub>      |                                                        |      | 170  | 196  | ms    |  |  |  |

| Reject Capacitance During<br>Detection                     | Сррн                  | $R_{PD}$ = 19k $\Omega$ to 26.5k $\Omega$              | 6    |      |      | μF    |  |  |  |

| Allowable Capacitance During<br>Detection                  | C <sub>PDL</sub>      | $R_{PD} = 19k\Omega$ to 26.5k $\Omega$                 |      |      | 0.6  | μF    |  |  |  |

| PD CLASSIFICATION (See PD CI                               | assification          | Mode Section)                                          |      |      |      |       |  |  |  |

| Classification Broke Voltage                               |                       | $I_{OUT} = 0.5 \text{mA} \text{ to } 45 \text{mA}$     | 15   |      | 20   | V     |  |  |  |

| Classification Probe Voltage                               | VCLASS                | No load                                                |      |      | 28   | V     |  |  |  |

| Classification Short-Circuit<br>Current                    | I <sub>SC_CLASS</sub> | Shorted to AGND                                        | 48   |      | 65   | mA    |  |  |  |

| Classification Time Duration                               | <b>t</b> CLASS        | From detection completion                              | 15   | 21.3 | 26   | ms    |  |  |  |

| Total Detection and Classification Delay Time              | tтот                  | From channel-enabled to power delivered at the OUT pin |      | 191  | 230  | ms    |  |  |  |

| Class 0 to Class 1 Threshold                               | ICLASS_1L             |                                                        | 5.5  | 6.5  | 7.5  | mA    |  |  |  |

| Class 1 to Class 2 Threshold                               | ICLASS_1-2            |                                                        | 13   | 14.5 | 16   | mA    |  |  |  |

| Class 2 to Class 3 Threshold                               | ICLASS_2-3            |                                                        | 21   | 23   | 25   | mA    |  |  |  |

| Class 3 to Class 4 Threshold                               | ICLASS_3-4            |                                                        | 31   | 33   | 35   | mA    |  |  |  |

| Default To Class 0 High-Current<br>Lower-Limit Threshold   | ICLASS_4-0            |                                                        | 43   | 46.5 |      | mA    |  |  |  |

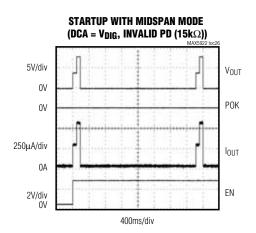

| Collision Detection Delay Time<br>(MAX5922A/MAX5922C Only) | <sup>t</sup> DCA      | DCA = high, $R_{PD}$ = 15k $\Omega$                    | 2.38 | 2.8  | 3.22 | S     |  |  |  |

Note 1: All specifications are 100% production tested at  $T_A = +25^{\circ}C$ , unless otherwise noted. All temperature limits are guaranteed by design.

Note 2: This is the time from an output overcurrent or short-circuit condition until the output goes into regulated current limit.

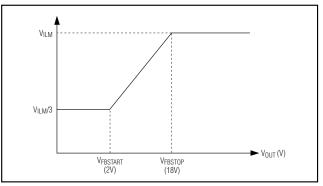

Note 3: OUT voltage above which the output current limit is at its full value (see Figure 8).

**Note 4:** To be consistent with the IEEE 802.3af standard, choose  $R_{SENSE} = 0.5\Omega \pm 1\%$ .

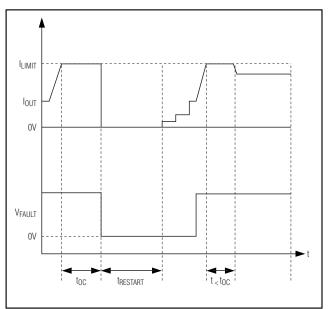

Note 5: This is the time the part stays in current-limit mode during overload condition. After t<sub>OC</sub> elapses (or when the junction temperature hits +150°C) the part shuts down.

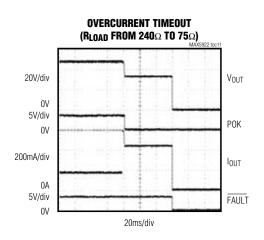

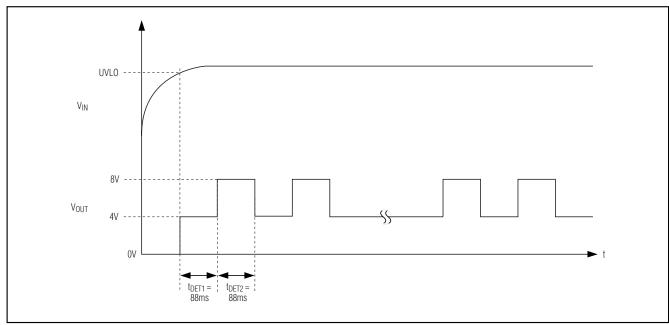

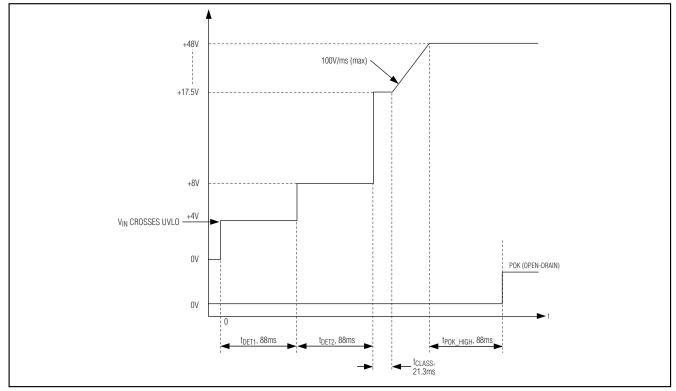

Note 6: See the Typical Operating Characteristics and Figure 6.

Note 7: This is the delay from I<sub>OUT</sub> falling below the zero-current threshold until ZC goes low and the IC shuts down (see the *Zero-Current Detection* section).

Note 8: See the Fault Management section.

Note 9: PD is detected by the procedures specified by the IEEE 802.3af standard. A probe voltage V<sub>PBI</sub> (+4V typically) is forced at OUT and the current I<sub>S1</sub> is measured after t<sub>DET</sub>/2. A second probe voltage V<sub>PBI</sub> (+8V typically) is then forced and I<sub>S2</sub> measured after t<sub>DET</sub> / 2 again. The voltage increment is then divided by the difference of the two currents (I<sub>S2</sub> - I<sub>S1</sub>). This is the PD resistance value.

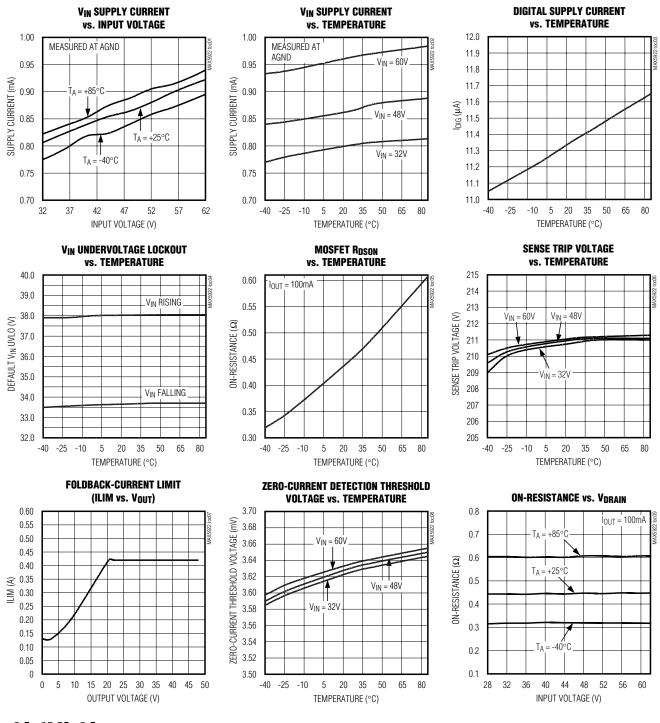

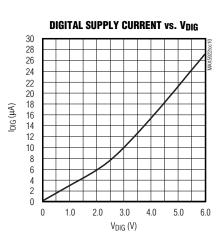

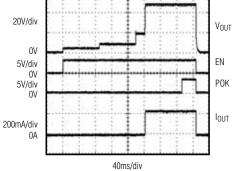

### **Typical Operating Characteristics**

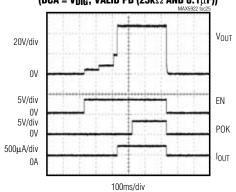

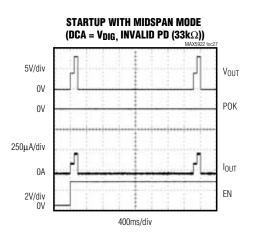

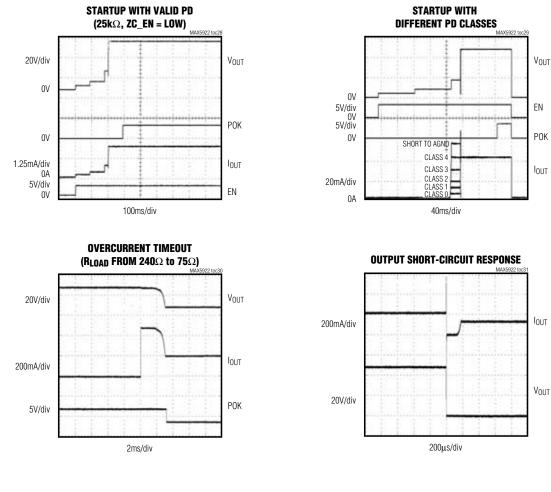

(MAX5922A, V<sub>IN</sub> = 48V, V<sub>DIG</sub>, EN, LATCH, CLASS, and ZC\_EN = 3.3V, DCA, AGND\_S = AGND = DGND = 0V, R<sub>SENSE</sub> =  $0.5\Omega \pm 1\%$ , UVLO floating, R<sub>RCL</sub> =  $150k\Omega$ , R<sub>RDT</sub> =  $18.2k\Omega$ , T<sub>A</sub> =  $+25^{\circ}$ C, unless otherwise noted.)

M/IXI/M

### **Typical Operating Characteristics (continued)**

(MAX5922A, V<sub>IN</sub> = 48V, V<sub>DIG</sub>, EN, LATCH, CLASS, and ZC\_EN = 3.3V, DCA, AGND\_S = AGND = DGND = 0V, R<sub>SENSE</sub> =  $0.5\Omega \pm 1\%$ , UVLO floating, R<sub>RCL</sub> =  $150k\Omega$ , R<sub>RDT</sub> =  $18.2k\Omega$ , T<sub>A</sub> =  $+25^{\circ}$ C, unless otherwise noted.)

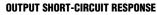

SHORT-CIRCUIT RESPONSE TIME

20V/div

### **Typical Operating Characteristics (continued)**

(MAX5922A, V<sub>IN</sub> = 48V, V<sub>DIG</sub>, EN, LATCH, CLASS, and ZC\_EN = 3.3V, DCA, AGND\_S = AGND = DGND = 0V, R<sub>SENSE</sub> =  $0.5\Omega \pm 1\%$ , UVLO floating, R<sub>RCL</sub> =  $150k\Omega$ , R<sub>RDT</sub> =  $18.2k\Omega$ , T<sub>A</sub> =  $+25^{\circ}$ C, unless otherwise noted.)

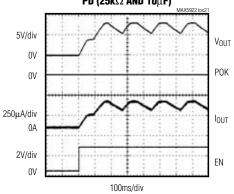

100ms/div

STARTUP WITH INVALID PD (25k $\Omega$  AND 10 $\mu$ F)

### **Typical Operating Characteristics (continued)**

(MAX5922A, V<sub>IN</sub> = 48V, V<sub>DIG</sub>, EN, LATCH, CLASS, and ZC\_EN = 3.3V, DCA, AGND\_S = AGND = DGND = 0V, R<sub>SENSE</sub> =  $0.5\Omega \pm 1\%$ , UVLO floating, R<sub>RCL</sub> =  $150k\Omega$ , R<sub>RDT</sub> =  $18.2k\Omega$ , T<sub>A</sub> =  $+25^{\circ}$ C, unless otherwise noted.)

STARTUP WITH OUTPUT SHORTED TO AGND

STARTUP WITH MIDSPAN MODE (DCA = VDIG, VALID PD (25k $\Omega$  AND 0.1 $\mu$ F))

MIXIM

### **Typical Operating Characteristics (continued)**

(MAX5922A, V<sub>IN</sub> = 48V, V<sub>DIG</sub>, EN, LATCH, CLASS, and ZC\_EN = 3.3V, DCA, AGND\_S = AGND = DGND = 0V, R<sub>SENSE</sub> =  $0.5\Omega \pm 1\%$ , UVLO floating, R<sub>RCL</sub> =  $150k\Omega$ , R<sub>RDT</sub> =  $18.2k\Omega$ , T<sub>A</sub> =  $+25^{\circ}$ C, unless otherwise noted.)

Pin Description

| PIN      | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| *        | AGND   | Analog Ground. This is the return of analog power input. AGND can vary ±4V from DGND. AGND and DGND must be connected together at a single point in the system.                                                                                                                                                                                                                                                         |  |  |  |  |

| 1, 2     | DRAIN  | Drain connection for the integrated MOSFET. Connect a sense resistor, R <sub>SENSE</sub> , from DRAIN to IN. These pins are also the current-sense resistor negative terminal. R <sub>SENSE</sub> sets the overcurrent-limit and open-circuit detection threshold. These two pins must be connected together.                                                                                                           |  |  |  |  |

| 3, 6, 26 | N.C.   | No Connection. Not internally connected. Leave pins 6 and 26 open. Pins 6 and 26 are left unconnected to provide additional spacing between the high-voltage pins and other pins.                                                                                                                                                                                                                                       |  |  |  |  |

| 4        | IN     | Input Voltage. Connect to a positive voltage source between +32V to +60V from IN to AGND. This is the current-sense resistor positive terminal. Bypass to AGND with a 47 $\mu$ F, 100V electrolytic capacitor and a 0.1 $\mu$ F, 100V ceramic capacitor. Place the ceramic capacitor close to this pin.                                                                                                                 |  |  |  |  |

| 5        | RCL    | Classification Sense Resistor. Connect a $150\Omega \pm 1\%$ resistor from RCL to IN for sensing the classification current. Leave RCL floating when the PD classification function is not used.                                                                                                                                                                                                                        |  |  |  |  |

| 7        | AGND_S | Analog Ground Sense. Connect a $1\Omega$ resistor from AGND_S to AGND. This resistor protects the IC during an output short-circuit condition.                                                                                                                                                                                                                                                                          |  |  |  |  |

| 8        | UVLO   | Undervoltage Lockout Adjustment Input. Referenced to AGND. Connect to the center point of a resistive-divider from IN to AGND to adjust the UVLO threshold. Leave open for default value.                                                                                                                                                                                                                               |  |  |  |  |

| 9        | RDT    | Detection Sense Resistor. Connect an $18.2k\Omega \pm 1\%$ resistor from RDT to AGND for sensing the detection current. Add a 680nF capacitor in parallel to this resistor to filter out the power-line no Connect RDT to AGND when the PD detection function is not used.                                                                                                                                              |  |  |  |  |

| 10       | FAULT  | <ul> <li>Fault Signal Open-Drain Logic Output. Reference to DGND. FAULT is latched low when:</li> <li>1. An overtemperature condition occurs and/or,</li> <li>2. An overcurrent condition that has lasted for more than t<sub>OC</sub>.</li> </ul>                                                                                                                                                                      |  |  |  |  |

| 11       | РОК    | Power-OK, Open-Drain Logic Output. Reference to DGND. POK goes open drain a time $t_{POK_HIGH}$ after $V_{OUT}$ raises to within $V_{THPOK}$ from $V_{IN}$ . POK goes low a time $t_{POK_LOW}$ after $V_{OUT}$ falls out of the $V_{THPOK}$ from $V_{IN}$ .                                                                                                                                                             |  |  |  |  |

| 12       | ZC     | Zero-Current Fault Signal. Open-drain logic output. Reference to DGND. $\overline{ZC}$ is latched low when there is a zero-current condition lasting longer than t <sub>ZCDEL</sub> . $\overline{ZC}$ is open-drain otherwise. The zero-current detection circuit is enabled immediately after the POK signal goes high. The $\overline{ZC}$ is unlatched after a valid PD has been detected and eventually classified. |  |  |  |  |

| 13       | TP1    | Must be Left Open or Connected to AGND                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 14       | TP2    | Must be Left Open or Connected to AGND                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 15       | TP3    | Must be Left Open or Connected to AGND                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 16       | CL2    | Classification Report Logic Output Bit 2. See the PD Classification section (Table 2).                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 17       | CL1    | Classification Report Logic Output Bit 1. See the PD Classification section (Table 2).                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 18       | CL0    | Classification Report Logic Output Bit 0. See the PD Classification section (Table 2).                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 19       | DGND   | Digital Ground. DGND can vary ±4V from AGND. DGND and AGND must to be connected together at a single point in the system.                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 20       | LATCH  | Fault Management Selection Digital Input. Referenced to DGND. Connect to a logic high to latch off after a fault condition. Connect to a logic low for automatic restart after a fault condition (see the <i>Fault Management</i> section).                                                                                                                                                                             |  |  |  |  |

\*This is not a device pin.

### Pin Description (continued)

| PIN    | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|--------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 21     | ZC_EN            | Zero-Current-Detection Enable Logic Input. Referenced to DGND. Connect ZC_EN to a logic high to enable the zero-current detection circuitry. Connect ZC_EN to a logic low to disable this function.                                                                                                     |  |  |  |  |  |  |

| 22     | EN               | ON/OFF Control-Logic Input. Referenced to DGND. Connect to a logic high to enable the device. Connect to a logic low to disable the device and reset a latched-off condition.                                                                                                                           |  |  |  |  |  |  |

| 23     | V <sub>DIG</sub> | Digital Supply Voltage. V <sub>DIG</sub> is the supply voltage for the internal digital logic circuity. EN, LATCH, CLASS, DET_DIS, DCA, and ZC_EN input logic thresholds are automatically scaled to the voltage on V <sub>DIG</sub> . See the <i>Typical Application Circuit</i> for proper filtering. |  |  |  |  |  |  |

| 24     | CLASS            | Classification Enable Digital Input. Connect to DGND to disable the classification function. Connect $V_{DIG}$ to enable the classification function.                                                                                                                                                   |  |  |  |  |  |  |

| 25     | DET_DIS          | PD Detection Disable Logic Input. When DET_DIS is connected to a logic high, the part skips the detection and classification (regardless of the status of CLASS) phases and powers on immediately after EN = high (MAX5922B/MAX5922C only).                                                             |  |  |  |  |  |  |

| DCA    |                  | Detection Collision Avoidance Logic Input. Connect to a logic high to activate the detection collision avoidance circuitry for midspan system. Connect to DGND to disable this function. (MAX5922A only). See the <i>Detection Collision Avoidance</i> section.                                         |  |  |  |  |  |  |

| 27, 28 | OUT              | Output Voltage                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

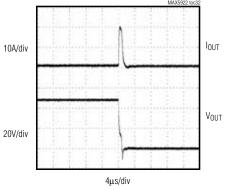

Figure 1. MAX5922 Block Diagram

### **Detailed Description**

The MAX5922 is a single-port network power controller with an integrated power MOSFET, operating from a +32V to +60V supply rail. The device is specifically designed for PSE in power-over-LAN applications and is fully compliant to the IEEE 802.3af standard. The MAX5922 provides PD discovery, classification, current limit, and other necessary functions for an IEEE 802.3af compliant PSE.

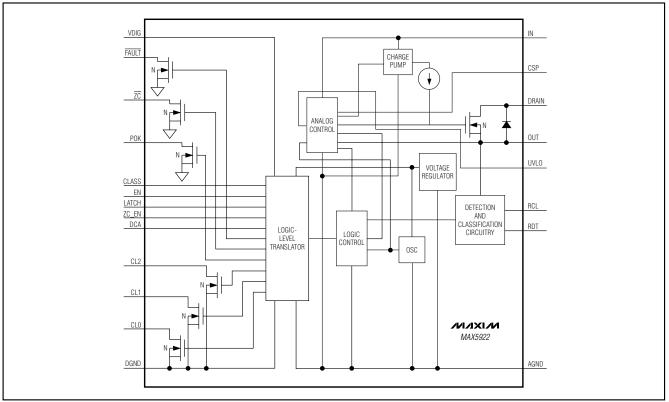

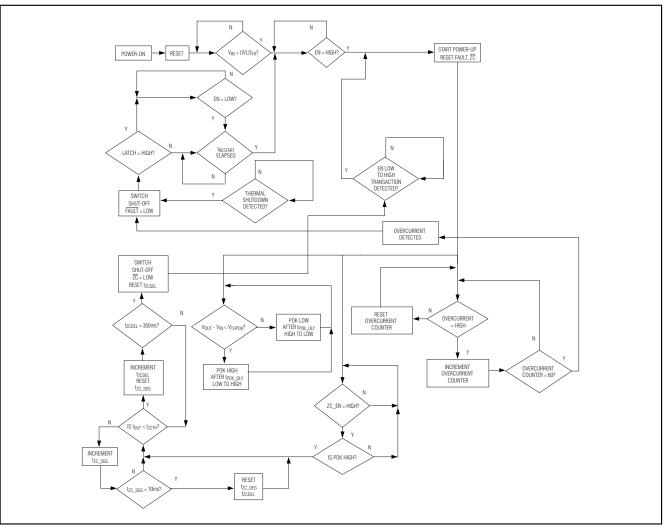

The MAX5922 operates in three different modes: PD detection mode, PD classification mode, and power mode. Figures 2 and 4 illustrates the device's functional operation.

#### **PD Detection Mode**

Once powered up and enabled, the MAX5922 probes the output for a valid PD. A valid PD should have a  $25k\Omega$ discovery signature characteristic as specified in the IEEE 802.3af standard. Table 1 shows the IEEE 802.3af specification for a PSE detection of PDs (see the *Typical Application Circuit* and Figure 3 (MAX5922 startup sequence)).

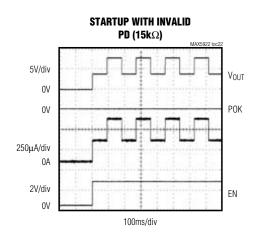

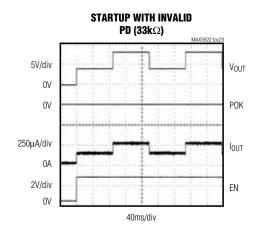

The MAX5922 performs the PD detection by forcing a probe voltage ( $V_{PBI} = 4V$ ) at the OUT pin and senses the current out of this pin. The sensed current is sampled and held theta (88ms) after the probing voltage is sent. The probe voltage is then switched to VPBII = 8V. At the end of another tDFT period, the ratio of the difference of the two test voltages and sensed currents  $(\Delta V/\Delta I)$  is calculated to determine the PD resistance. The MAX5922 PD detection circuitry checks for a valid PD resistive signature between  $19k\Omega$  and  $26.5k\Omega$ , with a parallel capacitance of up to 0.6µF. The MAX5922 PD detection circuit rejects all PDs showing resistive signature of less than  $15k\Omega$  or greater than  $33k\Omega$ , and/or a capacitive signature greater than 6 $\mu$ F. Any resistive signature between 15k $\Omega$ to  $19k\Omega$ , or between  $26.5k\Omega$  to  $33k\Omega$ , and/or a capacitance between 0.6µF to 6µF can produce unpredictable detection results. If the MAX5922 does not detect a valid PD signature, it continually sends the probe voltages to the output indefinitely (see Figure 5).

The detection current reference is set by an external resistor (R<sub>RDT</sub>)) connected from the RDT pin to AGND. This resistor should be an 18.2k $\Omega$  ±1%, with an optional 680nF capacitor in parallel for filtering out power-line

#### NON-VALID VALID PD DETECTION PD DETECTION PARAMETER SIGNATURE SIGNATURE $19k\Omega < R_{PD} <$ $15k\Omega > R_{PD}$ or V/I (Slope) $26.5 k\Omega$ $R_{RD} > 33k\Omega$ C<sub>PD</sub> < 0.6µF Input Capacitance $C_{PD} > 6\mu F$ Up to 2.0V Offset Voltage \_\_\_\_ Current Offset Up to 12µA

#### Table 1. IEEE802.3af PD Specification

noise. An internal diode in series with the detection voltage source and OUT is provided to restrict PD detection to the 1st quadrant as specified by the IEEE standard 802.3af (see Figure 3). To prevent damage to non-PD devices and to protect itself from output short circuit, the MAX5922 limits the current out of the OUT pin during PD detection to 1.5mA (max).

For midspan systems where power is delivered to the PD through the spare pairs, the detection collision avoidance must be activated. In this mode, after every failed PD detection cycle, the MAX5922A/MAX5922C enter a back-off mode where they drive the OUT pin into high impedance for t<sub>DCA</sub> (2.8s). The DCA pin must be connected high (MAX5922A) to activate the detection collision avoidance circuitry (if connected low, the detection collision avoidance circuitry is disabled). The MAX5922C has the detection collision avoidance circuitry is disabled). The MAX5922C has the detection collision avoidance circuitry permanently enabled (see the *Typical Application Circuit*). After t<sub>DCA</sub>, the MAX5922A (with DCA high) and the MAX5922B has the detection collision avoidance circuitry permanently disabled.

#### **Detection Enable/Disable**

The MAX5922A has the PD detection mode permanently enabled. The MAX5922B/MAX5922C are equipped with a DET\_DIS pin, which provides the option of enabling or disabling the power-device detection phase. With the DET\_DIS pin connected high, the PD detection and classification phases are disabled regardless of the status of the class pin. With the DET\_DIS pin connected low, the PD detection is enabled.

Figure 2. Operational Flow Chart (MAX5922A and MAX5922B/MAX5922C with DET\_DIS Connected Low)

Figure 3. PSE Detection Source

Figure 4. Operational Flow Chart (MAX5922B/MAX5922C with DET\_DIS Connected High)

Figure 5. PD Detection with an Invalid PD Signature

#### **Table 2. PD Classification Threshold Limits**

| SENSED CURRENT (mA)                                          | CL2 | CL1 | CL0 | CLASS TYPES                                                     |

|--------------------------------------------------------------|-----|-----|-----|-----------------------------------------------------------------|

| 0.5 to 4 or above 43                                         | 0   | 0   | 0   | Class 0                                                         |

| 9 to 12                                                      | 0   | 0   | 1   | Class 1                                                         |

| 17 to 20                                                     | 0   | 1   | 0   | Class 2                                                         |

| 26 to 30                                                     | 0   | 1   | 1   | Class 3                                                         |

| 36 to 42                                                     | 1   | 0   | 0   | Class 4                                                         |

| N/A                                                          | 1   | 0   | 1   | Not used                                                        |

| N/A                                                          | 1   | 1   | 0   | Successful detection (classification disabled or DET_DIS = low) |

| Power device not detected yet<br>or CLASS pin connected low. | 1   | 1   | 1   | Detection ongoing                                               |

#### PD Classification Mode (PD Classification)

Following a valid PD detection, and if the CLASS pin is high, the MAX5922 enters the PD classification mode. If the CLASS pin is low, the PD classification mode is skipped and the MAX5922 goes directly from PD detection to the power mode. During the PD classification mode, the MAX5922 forces a probe voltage (17.5V) at the OUT pin and measures the current out of this pin. The measured current determines the class of the PD. The classification results are reported at the classification logic outputs CL0, CL1, CL2. Table 2 shows the classification threshold limits and the corresponding logic outputs CL0, CL1, and CL2. Connect an external 150 $\Omega$  ±1% resistor (R<sub>RCL</sub>) from RCL to IN to set the classification current reference. If the PD classification function is not used, RCL can be left floating. For the MAX5922B/MAX5922C, the DET\_DIS pin must be connected low to enable the classification phase. If DET\_DIS is connected high, the classification phase is disabled regardless of the state of the CLASS pin. After the classification phase, the MAX5922 enters power-up.

#### **Power-Up Mode**

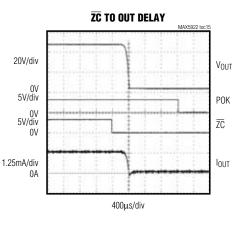

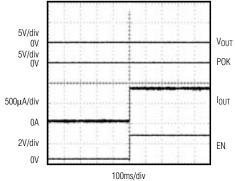

After the PD is successfully detected and classified, the MAX5922 enters power-up mode. During this mode, the MAX5922 gradually turns on the integrated N-channel MOSFET. To minimize EMI, the MAX5922 limits the

Figure 6. Startup Sequence

output voltage slew rate at the OUT pin to  $dV_{OUT}/dt = 100V/ms$  (max) and the output-current slew rate out of the OUT pin to  $dI_{OUT}/dt = 35A/ms$  (max).

The MAX5922 has an integrated 0.45 $\Omega$  N-channel power MOSFET. The MOSFET's drain is connected to the DRAIN pin and its source is connected to the OUT pin. The MAX5922 monitors and provides current-limit protection to the load at all times. The current limit is programmable using an external current-sensing resistor connected from IN to DRAIN. To be compatible with the IEE802.3af standard, use a 0.5 $\Omega$  ±1%, 50ppm/°C resistor. The MAX5922 features current-limit foldback and duty-cycle limit to ensure robust operation during load-fault and short-circuit conditions (see the *Overcurrent Protection* section).

When V<sub>OUT</sub> is within 750mV of V<sub>IN</sub> for more than t<sub>POK\_HIGH</sub>, POK goes open drain. Figure 6 shows a typical startup sequence.

After POK is asserted, the MAX5922 activates the zerocurrent detection function. This function monitors the output for an undercurrent condition and eventually turns off the power to the output if the PD is disconnected (see the *Zero-Current Detection* section).

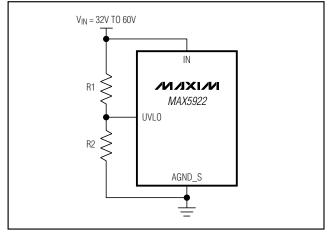

#### **Undervoltage Lockout (UVLO)**

The MAX5922 operates from a +32V to +60V supply voltage range and has a default UVLO set at +38V (MAX5922A) or +28V (MAX5922B/MAX5922C). The UVLO threshold is adjustable using a resistive-divider connected to the UVLO pin (see Figure 7). When the input voltage is below the UVLO threshold, all operation stops and the MOSFET is held off. When the input voltage is above the UVLO threshold and EN is high, the MAX5922 goes into operation. See Figures 2 and 4 for the operational flow charts.

To adjust the UVLO threshold, connect an external resistive-divider from IN to UVLO and then from UVLO to AGND. Use the following equation to calculate the new UVLO threshold:

$$V_{UVLO_TH} = V_{REF} \left( 1 + \frac{R1}{R2} \right)$$

VREF is typically 1.38V (MAX5922A) or 1.33V (MAX5922B/MAX5922C). The UVLO pin input resistance is  $50k\Omega$  (min), keep the R1 and R2 parallel combination value at least 20 times smaller than  $50k\Omega$  to minimize the new UVLO threshold error.

Figure 7. Setting Undervoltage Lockout with an External Resistive-Divider

#### **Digital Logic**

V<sub>DIG</sub> is the input supply for the internal logic circuitry. The logic input thresholds of EN, LATCH, CLASS, DCA (MAX5922A), DET\_DIS (MAX5922B/MAX5922C), and ZC\_EN are CMOS compatible and are determined by the voltage at V<sub>DIG</sub> which can range from 1.65V to 5.5V. The POK, ZC, CL0, CL1, CL2, and FAULT outputs are open drain. V<sub>DIG</sub> and all logic inputs and outputs are referenced to DGND. DGND is not connected to AGND internally and must be connected externally at a single point in the system to AGND. The maximum allowable difference in the voltage between DGND and AGND is ±4V.

**Enable (EN)** EN is a logic input to enable the MAX5922. Bringing EN low halts all operations and turns off the internal power MOSFET. When EN is high and the input voltage is above the UVLO threshold, the MAX5922 begins operating. Enable is also used to unlatch the part after a latched fault condition. This is done by toggling EN low and high again after a fault condition.

#### **Overcurrent Protection**

The MAX5922 provides a sophisticated overcurrent protection circuitry to ensure the device's robustness under output-current transient and current fault conditions. The current protection circuitry employs a constant current limit, a current foldback, and an overcurrent timeout. The device monitors the voltage drop, VSENSE (VSENSE = VIN - VDRAIN) to determine the load current.

#### **Constant Current Limit**

The MAX5922 monitors V<sub>SENSE</sub> at all times during power mode and regulates the current through the power MOSFET as necessary to keep V<sub>SENSE</sub> (max) to the current-limit sense voltage (V<sub>ILIM</sub> = 212mV). The load-current limit, I<sub>LIM</sub>, is programmed by the currentsense resistor, R<sub>SENSE</sub>, connected from IN to DRAIN (I<sub>LIM</sub> = V<sub>ILIM</sub>/R<sub>SENSE</sub>). When the load current is less than I<sub>LIM</sub>, the MOSFET is fully on. When the load is trying to draw more than I<sub>LIM</sub>, the OUT pin works like a constant current source, limiting the output current to I<sub>LIM</sub>. If I<sub>OUT</sub> is at I<sub>LIM</sub> for greater than the current-limit timeout, a current-limit fault is generated and the power MOSFET is turned off (see the *Overcurrent Timeout* and *Fault Management* sections).

#### **Current Foldback**

While in current-limit condition, the voltage at the OUT pin drops. As the load resistance reduces (more loading), the output voltage reduces accordingly to maintain a constant load current. The power dissipation in the power MOSFET is (VDRAIN - VOUT) × ILIM. As the output voltage drops lower, more power is dissipated across the power MOSFET. To reduce this power dissipation, the MAX5922 offers a current foldback feature where it linearly reduces the VILIM value when VOUT drops below the OUT current-limit foldback voltage (VFBSTOP = 18V). Figure 8 illustrates this current foldback limit behavior.

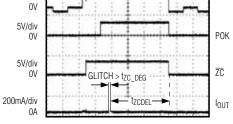

#### **Overcurrent Timeout**

The MAX5922 keeps track of the time it is in current limit. An internal digital counter begins incrementing its count at 1count/ms when V<sub>SENSE</sub> exceeds its limit (either V<sub>ILIM</sub> or V<sub>ILIM</sub> foldback in foldback mode). The counter is reset to zero if the current falls back below the current limit. When the cumulative count reaches 60, an overcurrent fault is generated. After an overcurrent fault condition, the switch is turned off and the FAULT signal goes low (see Figure 9).

Figure 8. Current Foldback Characteristic

This overcurrent timeout enables the MAX5922 to operate in a periodic overcurrent condition without causing a fault (see Figure 9).

#### Power-OK (POK)

POK goes open-drain tPOK\_HIGH (88ms) after VOUT rises to within VTHPOK (0.75V) from VIN. POK goes low tPOK\_LOW (1.4ms) after VOUT drops 0.82V below VIN.

#### **Zero-Current Detection**

Zero-current detection is enabled if ZC\_EN is high and only after the startup period has finished (indicated by POK going high). When VSENSE falls below the zerocurrent threshold (V<sub>ZCTH</sub>) for a continuous t<sub>ZCDEL</sub> = 350ms, a zero-current fault is generated. The MOSFET is turned off and  $\overline{ZC}$  is latched low. The MAX5922A and the MAX5922B/MAX5922C (with DET\_DIS = low) immediately begin a PD detection sequence, regardless of the status of the LATCH input.  $\overline{ZC}$  is unlatched and goes high impedance after a PD is detected.  $\overline{ZC}$  is also high impedance during initial power-up. When DET\_DIS is high (MAX5922B/MAX5922C), a zero-current fault shuts down the MOSFET and the EN pin needs to be toggled to unlatch the fault.

At any time during a zero-current condition, if VSENSE goes above VZCTH for the zero-current deglitch time ( $t_{ZC}$ \_DEG = 10ms), the zero-current counter resets to zero and a zero-current fault is not generated. Bring ZC\_EN low to disable the zero-current detection function.  $\overline{ZC}$  stays high impedance in this mode.

Figure 9. Overcurrent Response

#### Thermal Shutdown

If the MAX5922 die temperature reaches +150°C, an overtemperature fault is generated. The MOSFET turns off and FAULT goes low. The MAX5922 die temperature must cool down below 120°C before the overtemperature fault condition is removed (see *Fault Management* section).

#### Fault Report (FAULT)

FAULT goes low when there is an overcurrent fault and/or an overtemperature fault. FAULT is open-drain otherwise. After a fault, the FAULT signal is latched low. FAULT is unlatched at the beginning of the next power mode.

#### Fault Management

The MAX5922 offers either latched-off or auto-retry fault management configurable by the LATCH input. Bringing LATCH high puts the device into latch mode while pulling LATCH low selects the autoretry option.

In latch mode, the MAX5922 turns the MOSFET off and keeps it off after an overcurrent fault or an over-temperature fault. After the fault condition goes away, recycle the power supplies or toggle the EN pin low and high again to unlatch the part. However, the part waits a tRESTART period (1.92s) before recovering from a fault condition and resuming normal operation.

In autoretry mode, the MAX5922 turns the MOSFET off after an overcurrent or overtemperature fault. After the fault condition is removed, the device waits a tRESTART period (1.92s) and then automatically restarts and enters the PD detection mode (MAX5922A and MAX5922B/MAX5922C with DET\_DIS low). If DET\_DIS is high (MAX5922B/MAX5922C), the MAX5922B/MAX5922C automatically restart into the power-up mode after tRESTDRT. If the fault was due to an overtemperature condition, the MAX5922 waits for its die temperature to cool down below the hysteresis level before starting the tRESTART time.

#### **Detection Collision Avoidance**

Detection collision avoidance is enabled by connecting the DCA pin directly to VDIG and disabled by connecting it to DGND. When DCA is high, the MAX5922A activates a back-off time, tDCA (2.8s), after every failed detection during PD detection mode. During this backoff time, the MAX5922A turns off the MOSFET and drives the OUT pin to high impedance. This function is required by the IEEE 802.3af standard if the PSE resides in a midspan system. After tDCA, the MAX5922A starts a PD detection sequence. The MAX5922B has this function internally disabled and the MAX5922C has this function internally enabled.

### Selector Guide

| PART        | PIN-PACKAGE | DETECTION COLLISION AVOIDANCE | PD DETECTION DISABLE |

|-------------|-------------|-------------------------------|----------------------|

| MAX5922AEUI | 28 TSSOP    | Selectable                    |                      |

| MAX5922BEUI | 28 TSSOP    | Disabled                      | Selectable           |

| MAX5922CEUI | 28 TSSOP    | Enabled                       | Selectable           |

### \_Chip Information

TRANSISTOR COUNT: 8687 PROCESS: BICMOS

### Pin Configuration

\_Typical Application Circuits